OTIS Outer Tracker Time Information System A TDC

- Slides: 18

OTIS (Outer Tracker Time Information System) A TDC for LHCb 8 th Workshop on Electronics for LHC Experiments September 9 – 13, 2002 Colmar, France OTIS Group, University Heidelberg: Harald Deppe Uwe Stange Ulrich Trunk Ulrich Uwer Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 1

Contents ¢ Overview Outer Tracker, Front End Electronics & OTIS ¢ OTIS Chip Concept Components of the OTIS Chip ¢ OTIS 1. 0 Prototype Measurements ¢ Summary Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 2

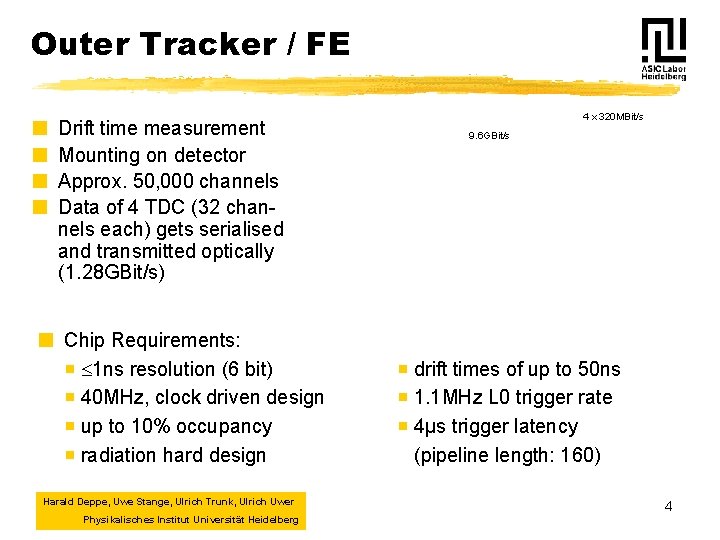

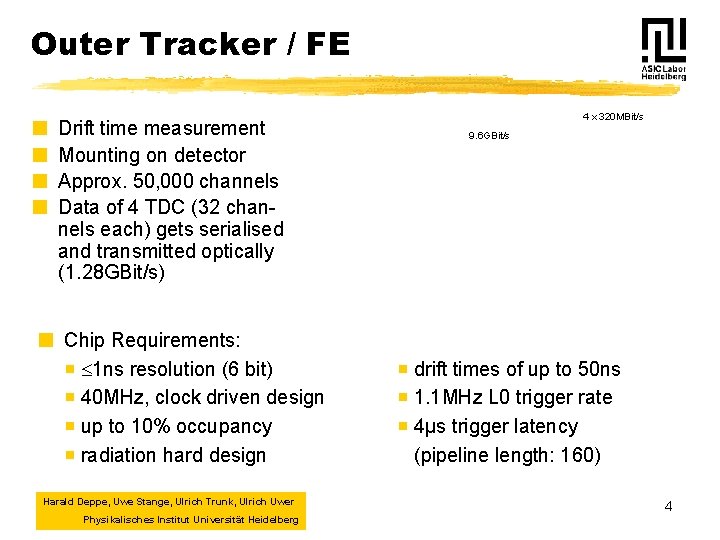

Outer Tracker / FE ¢ ¢ Drift time measurement Mounting on detector Approx. 50, 000 channels Data of 4 TDC (32 channels each) gets serialised and transmitted optically (1. 28 GBit/s) ¢ Chip Requirements: 1 ns resolution (6 bit) 40 MHz, clock driven design up to 10% occupancy radiation hard design Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 4 x 320 MBit/s 9. 6 GBit/s drift times of up to 50 ns 1. 1 MHz L 0 trigger rate 4µs trigger latency (pipeline length: 160) 4

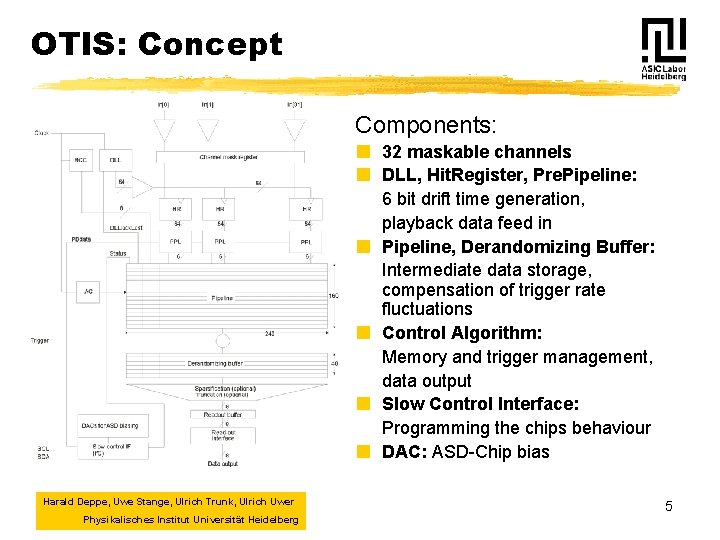

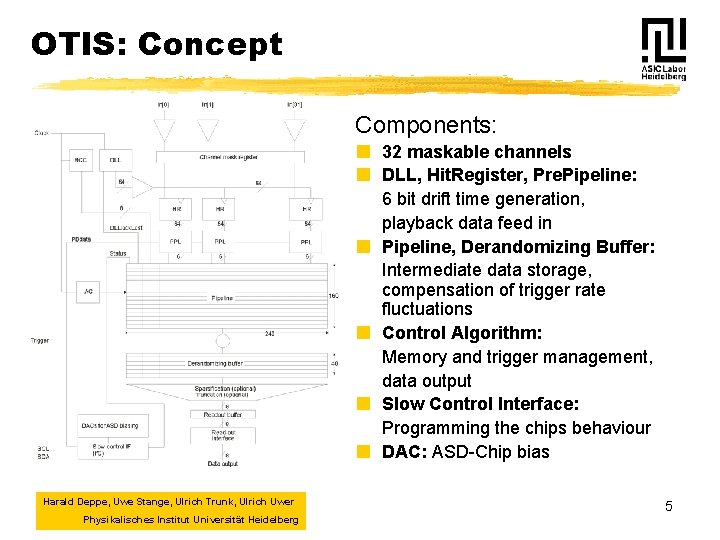

OTIS: Concept Components: ¢ 32 maskable channels ¢ DLL, Hit. Register, Pre. Pipeline: 6 bit drift time generation, playback data feed in ¢ Pipeline, Derandomizing Buffer: Intermediate data storage, compensation of trigger rate fluctuations ¢ Control Algorithm: Memory and trigger management, data output ¢ Slow Control Interface: Programming the chips behaviour ¢ DAC: ASD-Chip bias Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 5

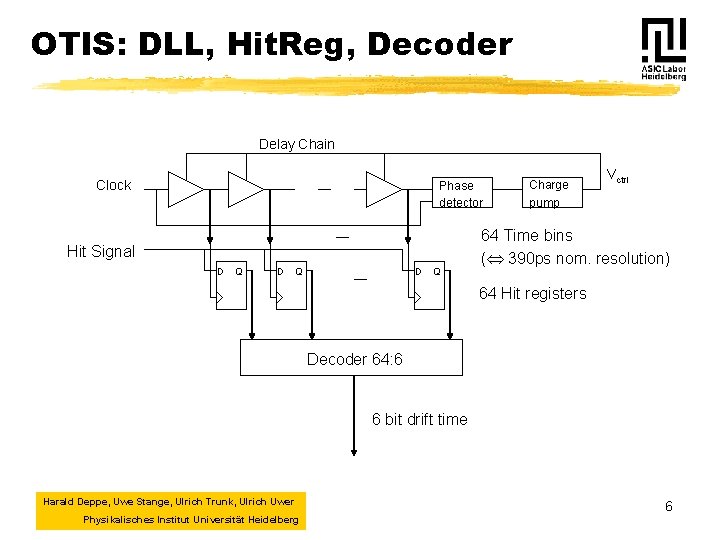

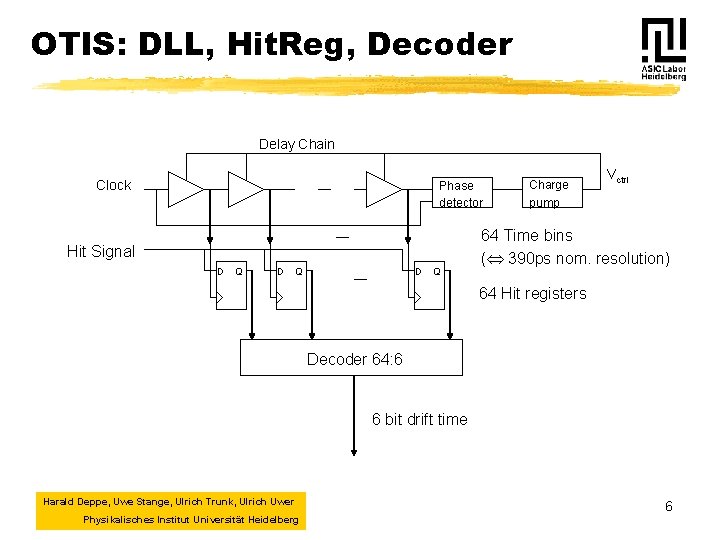

OTIS: DLL, Hit. Reg, Decoder Delay Chain Clock Phase detector Hit Signal D Q D Q Charge pump Vctrl 64 Time bins ( 390 ps nom. resolution) 64 Hit registers Decoder 64: 6 6 bit drift time Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 6

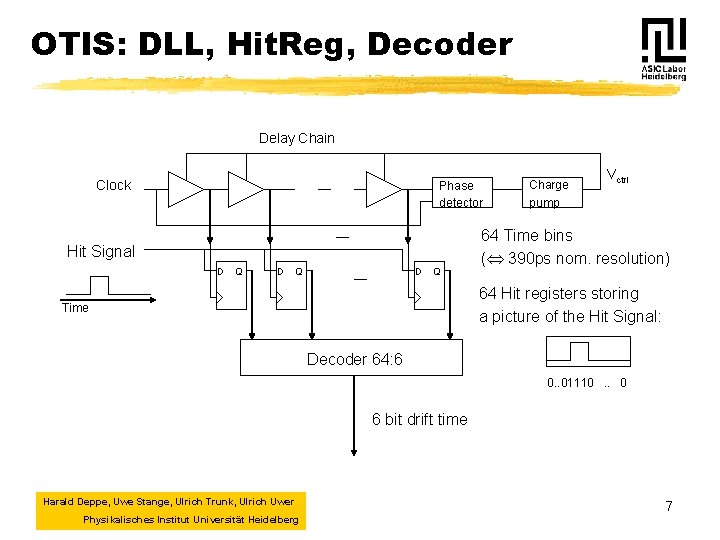

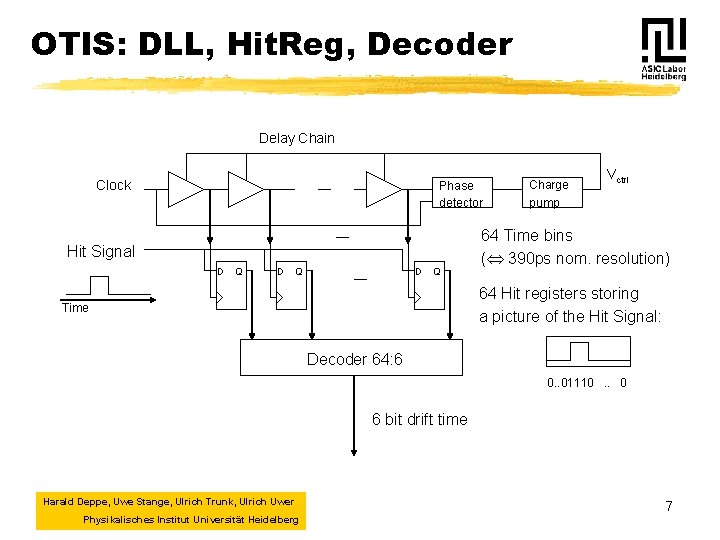

OTIS: DLL, Hit. Reg, Decoder Delay Chain Clock Phase detector Hit Signal D Q D Q Charge pump Vctrl 64 Time bins ( 390 ps nom. resolution) 64 Hit registers storing a picture of the Hit Signal: Time Decoder 64: 6 0. . 01110. . 0 6 bit drift time Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 7

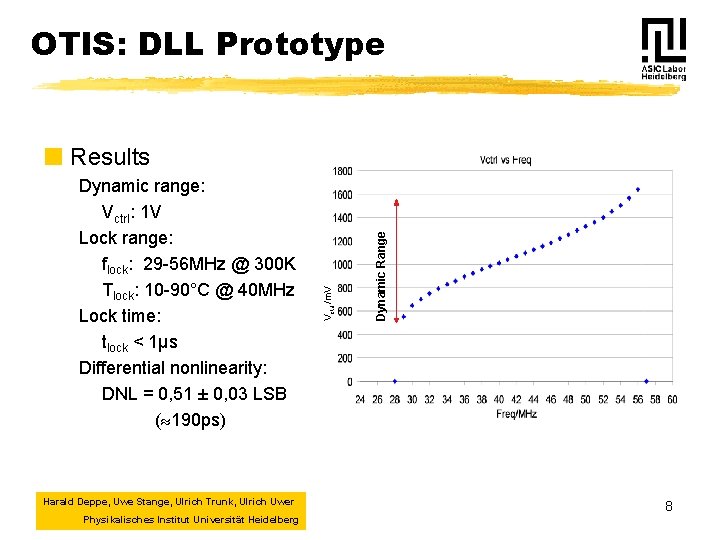

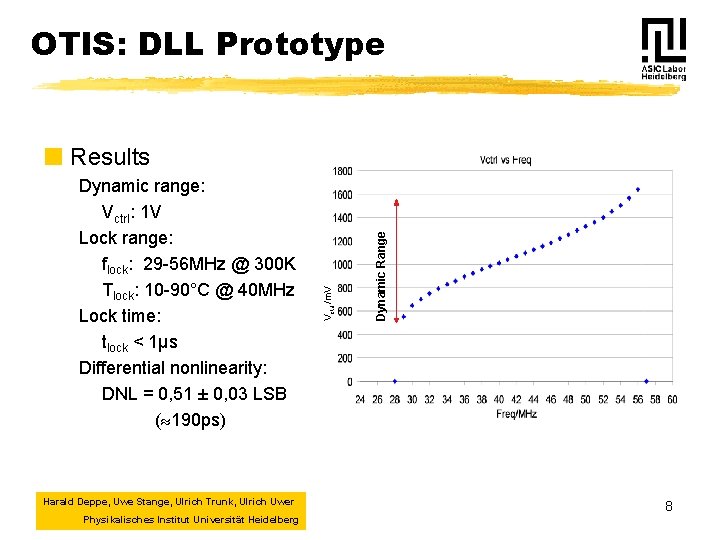

OTIS: DLL Prototype Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg Dynamic Range Dynamic range: Vctrl: 1 V Lock range: flock: 29 -56 MHz @ 300 K Tlock: 10 -90°C @ 40 MHz Lock time: tlock < 1µs Differential nonlinearity: DNL = 0, 51 ± 0, 03 LSB ( 190 ps) Vctrl /m. V ¢ Results 8

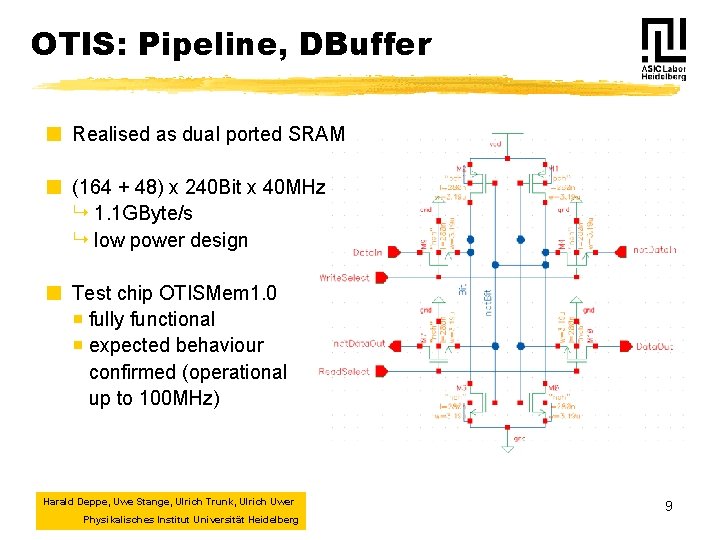

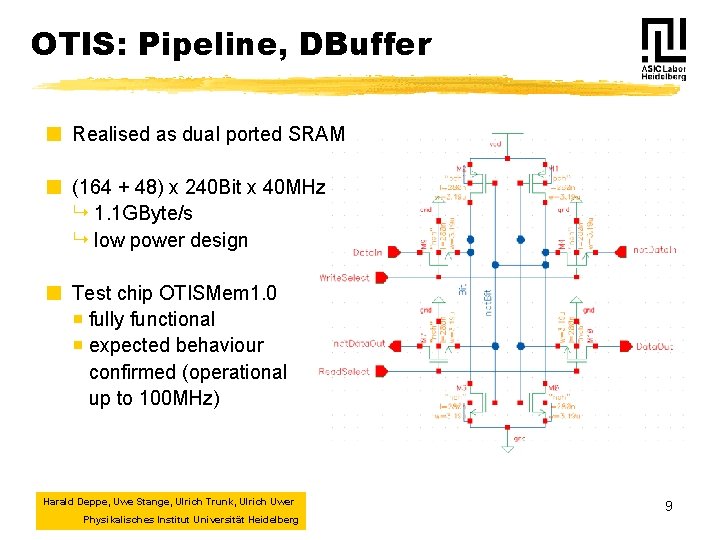

OTIS: Pipeline, DBuffer ¢ Realised as dual ported SRAM ¢ (164 + 48) x 240 Bit x 40 MHz 1. 1 GByte/s low power design ¢ Test chip OTISMem 1. 0 fully functional expected behaviour confirmed (operational up to 100 MHz) Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 9

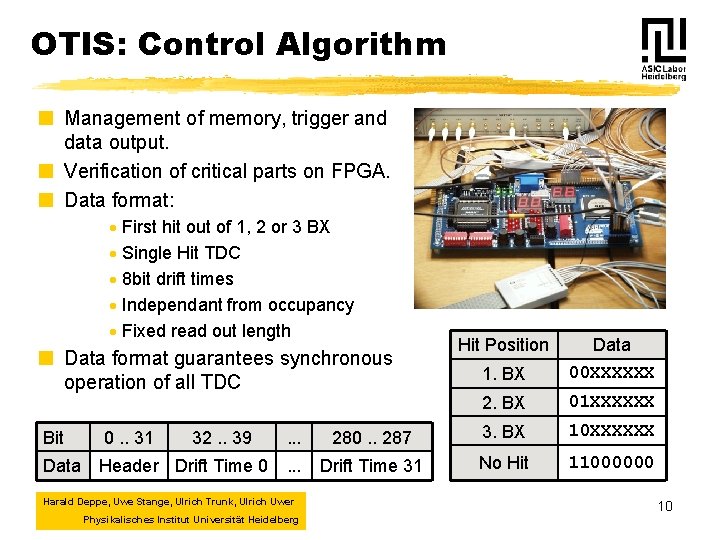

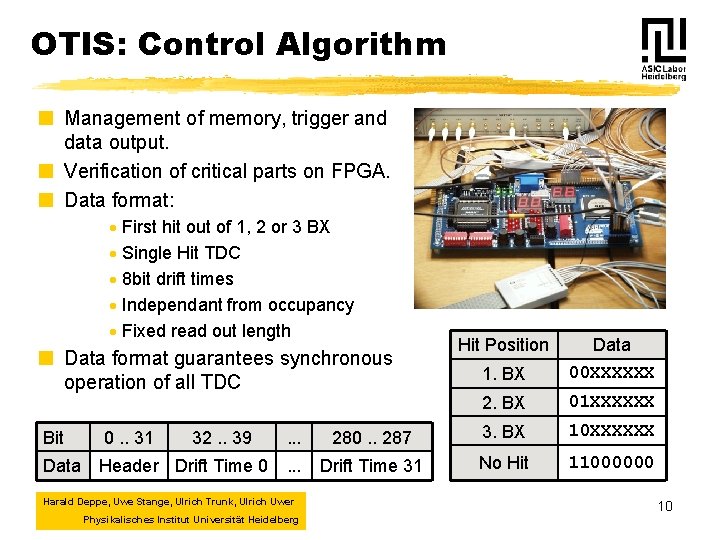

OTIS: Control Algorithm ¢ Management of memory, trigger and data output. ¢ Verification of critical parts on FPGA. ¢ Data format: First hit out of 1, 2 or 3 BX Single Hit TDC 8 bit drift times Independant from occupancy Fixed read out length ¢ Data format guarantees synchronous operation of all TDC Bit 0. . 31 32. . 39 Data Header Drift Time 0 Hit Position Data 1. BX 00 XXXXXX 2. BX 01 XXXXXX . . . 280. . 287 3. BX 10 XXXXXX . . . Drift Time 31 No Hit 11000000 Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 10

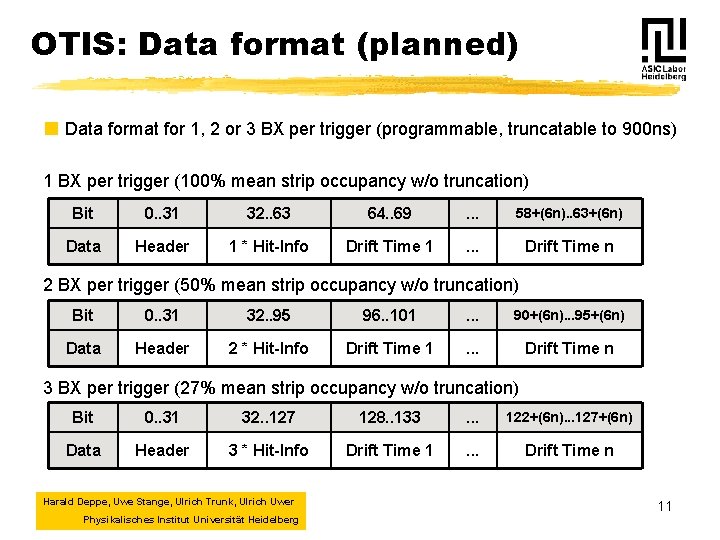

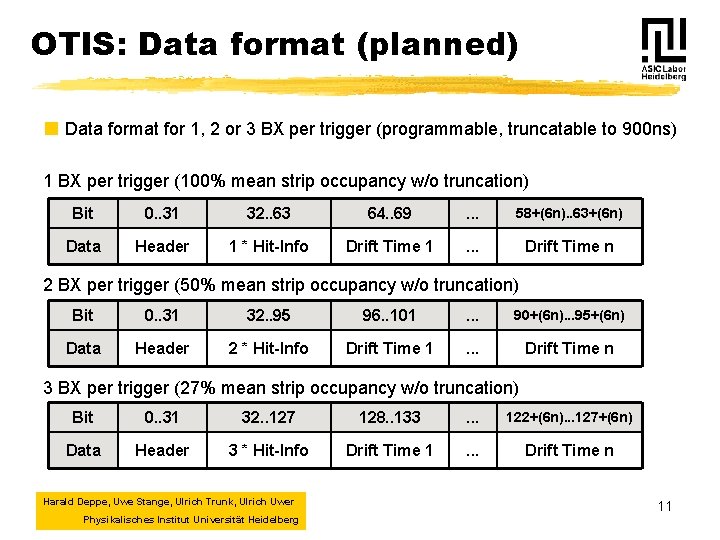

OTIS: Data format (planned) ¢ Data format for 1, 2 or 3 BX per trigger (programmable, truncatable to 900 ns) 1 BX per trigger (100% mean strip occupancy w/o truncation) Bit 0. . 31 32. . 63 64. . 69 . . . 58+(6 n). . 63+(6 n) Data Header 1 * Hit-Info Drift Time 1 . . . Drift Time n 2 BX per trigger (50% mean strip occupancy w/o truncation) Bit 0. . 31 32. . 95 96. . 101 . . . 90+(6 n). . . 95+(6 n) Data Header 2 * Hit-Info Drift Time 1 . . . Drift Time n 3 BX per trigger (27% mean strip occupancy w/o truncation) Bit 0. . 31 32. . 127 128. . 133 . . . 122+(6 n). . . 127+(6 n) Data Header 3 * Hit-Info Drift Time 1 . . . Drift Time n Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 11

Contents ¢ Overview Outer Tracker, Front End Electronics & OTIS ¢ OTIS Chip Concept Components of the OTIS Chip ¢ OTIS 1. 0 Prototype Measurements ¢ Summary Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 12

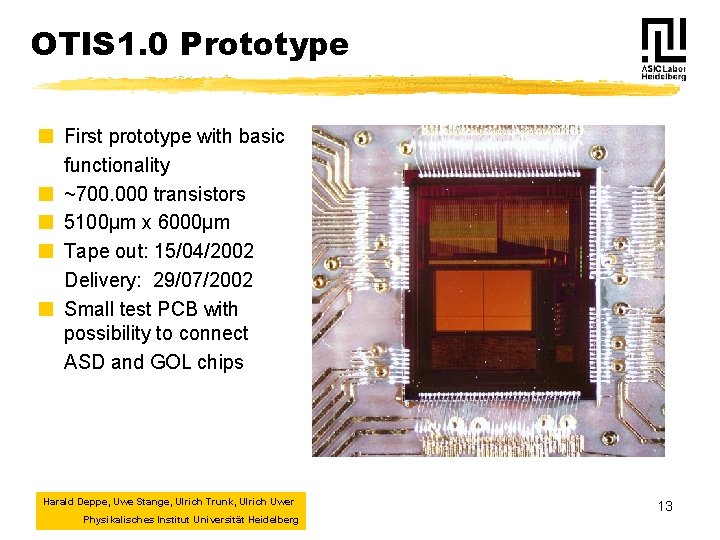

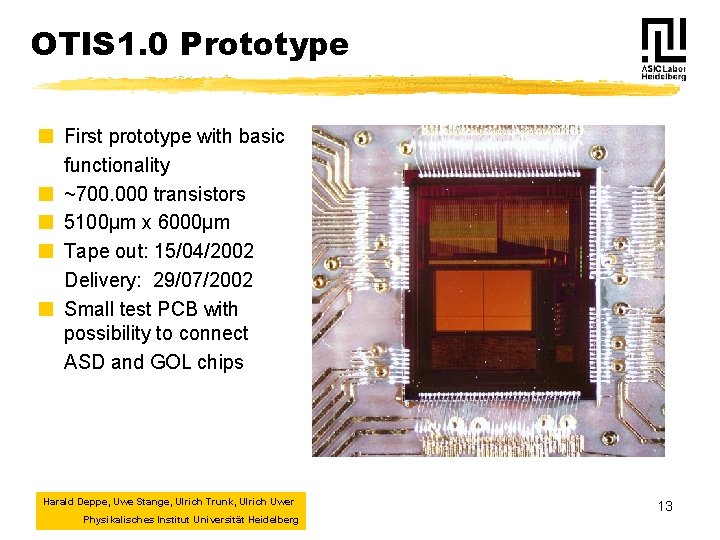

OTIS 1. 0 Prototype ¢ First prototype with basic functionality ¢ ~700. 000 transistors ¢ 5100µm x 6000µm ¢ Tape out: 15/04/2002 Delivery: 29/07/2002 ¢ Small test PCB with possibility to connect ASD and GOL chips Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 13

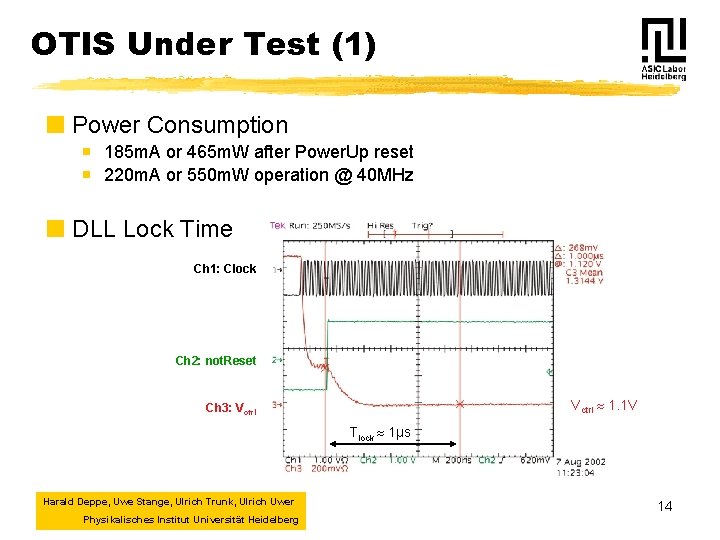

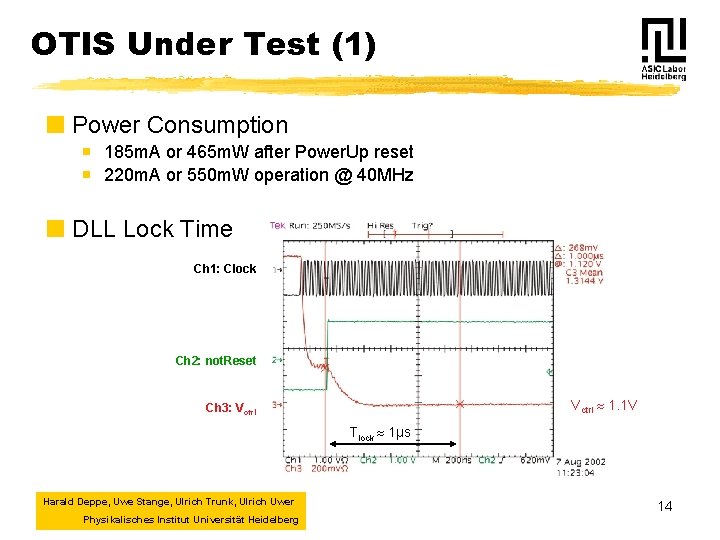

OTIS Under Test (1) ¢ Power Consumption 185 m. A or 465 m. W after Power. Up reset 220 m. A or 550 m. W operation @ 40 MHz ¢ DLL Lock Time Ch 1: Clock Ch 2: not. Reset Vctrl 1. 1 V Ch 3: Vctrl Tlock 1µs Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 14

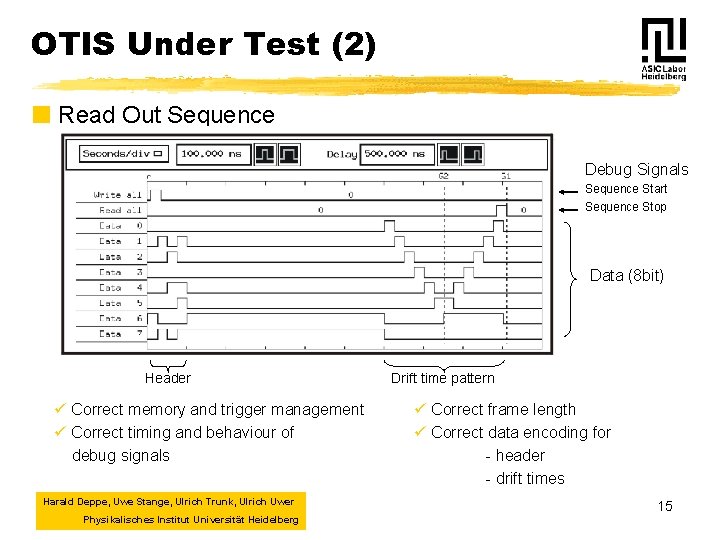

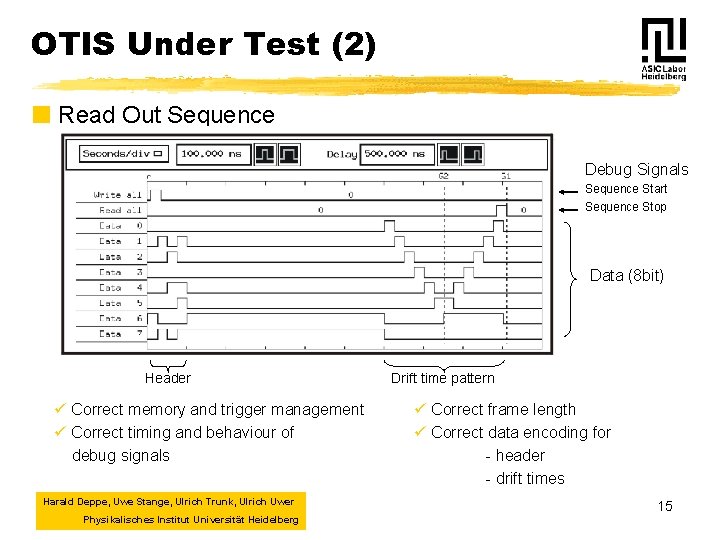

OTIS Under Test (2) ¢ Read Out Sequence Debug Signals Sequence Start Sequence Stop Data (8 bit) Header Correct memory and trigger management Correct timing and behaviour of debug signals Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg Drift time pattern Correct frame length Correct data encoding for - header - drift times 15

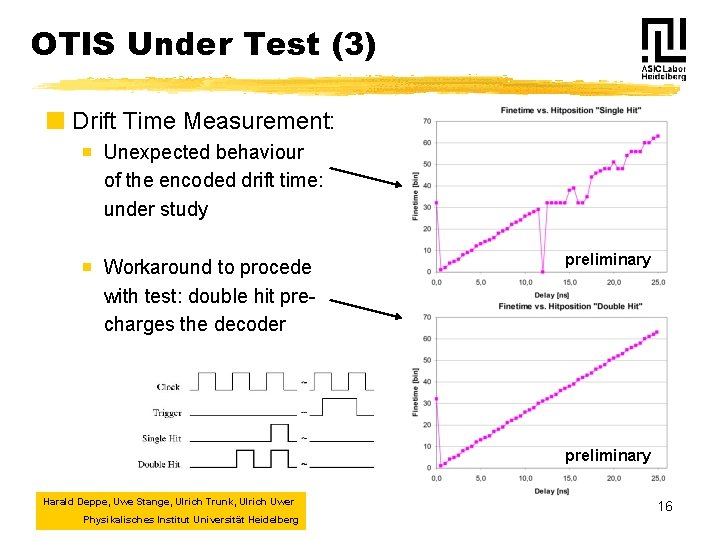

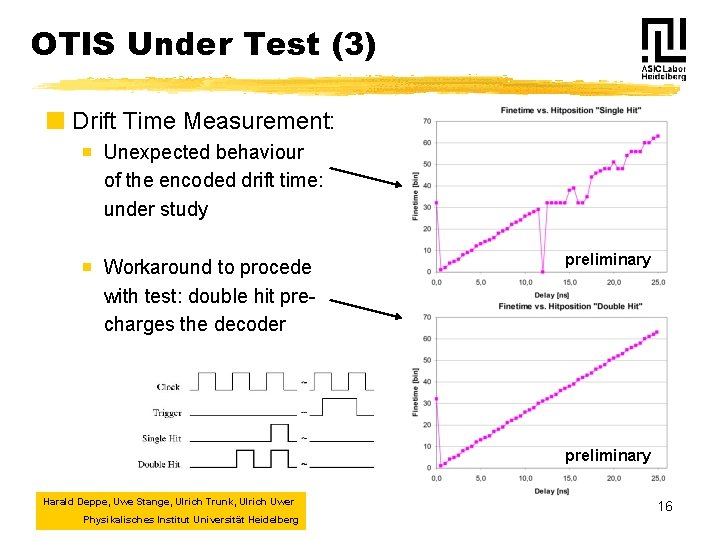

OTIS Under Test (3) ¢ Drift Time Measurement: Unexpected behaviour of the encoded drift time: under study Workaround to procede with test: double hit precharges the decoder preliminary Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 16

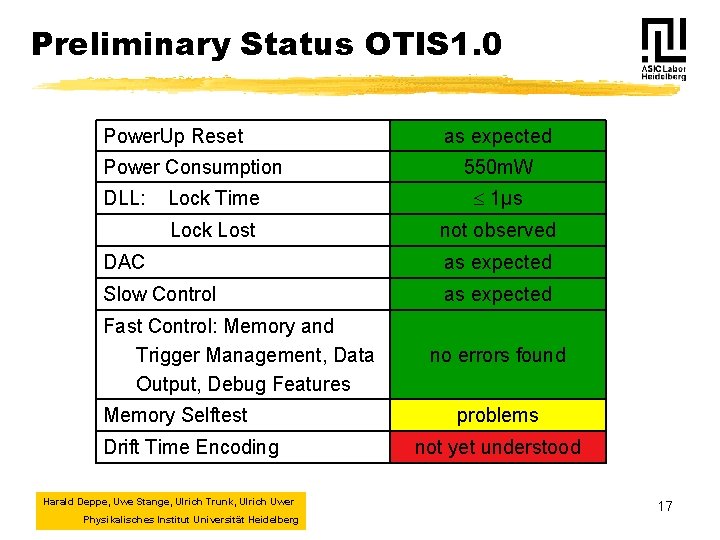

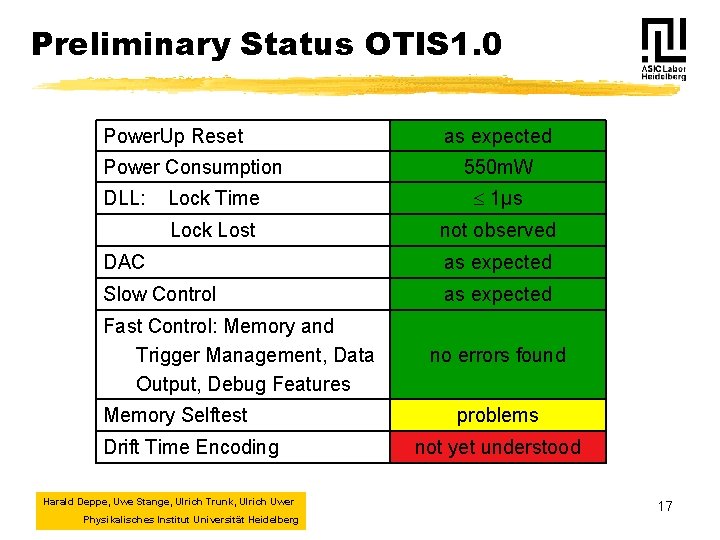

Preliminary Status OTIS 1. 0 Power. Up Reset Power Consumption DLL: as expected 550 m. W Lock Time 1µs Lock Lost not observed DAC as expected Slow Control as expected Fast Control: Memory and Trigger Management, Data Output, Debug Features Memory Selftest Drift Time Encoding Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg no errors found problems not yet understood 17

Outlook ¢ Further investigations concerning drift time encoding ¢ Study more chips, performance tests, random trigger tests, . . . ¢ Operation with detector prototype ¢ Commissioning of the read out chain including TTCrx Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 18

Summary ¢ OTIS TDC Chip: 32 channel TDC, 6 Bit drift time resolution 40 MHz, clock driven architecture 160 events deep pipeline 1. 1 MHz trigger rate radiation hard ¢ Prototype OTIS 1. 0 at hand since 6 weeks: almost fully functional Harald Deppe, Uwe Stange, Ulrich Trunk, Ulrich Uwer Physikalisches Institut Universität Heidelberg 19