Other Data Path designs Microprogrammed and pipelined datapaths

- Slides: 11

Other Data. Path designs: Microprogrammed and pipelined datapaths Laxmikant Kale http: //charm. cs. uiuc. edu Parallel Programming Laboratory Department of Computer Science University of Illinois at Urbana Champaign 1/15/2022 cs 231 Kale 1

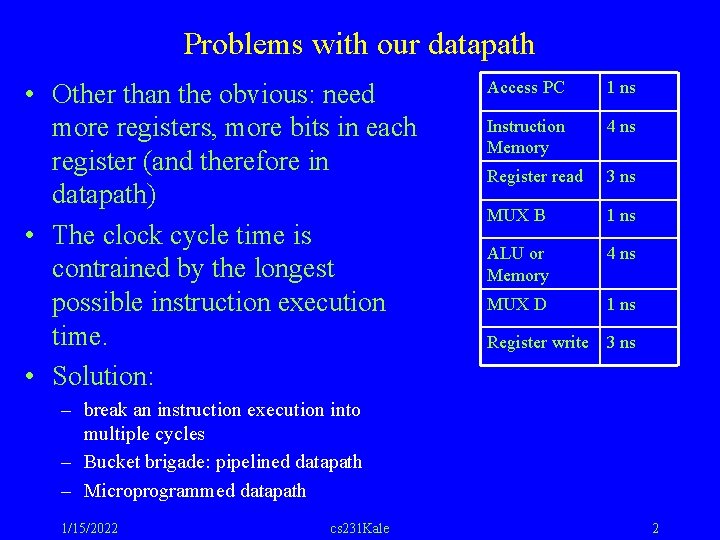

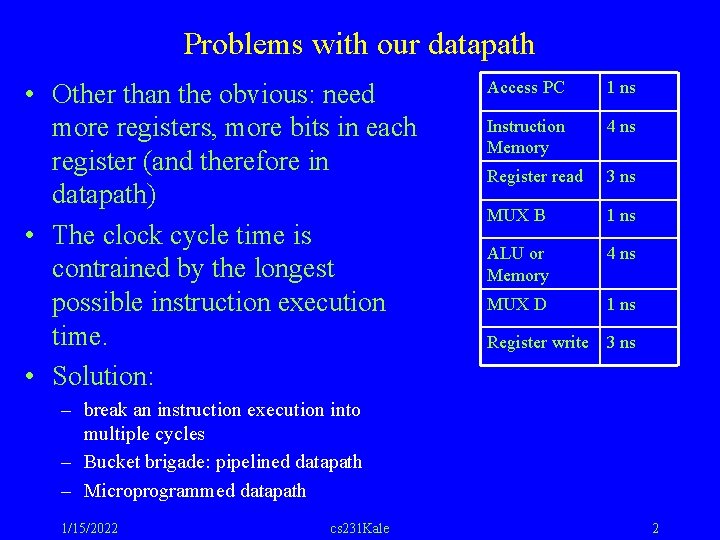

Problems with our datapath • Other than the obvious: need more registers, more bits in each register (and therefore in datapath) • The clock cycle time is contrained by the longest possible instruction execution time. • Solution: Access PC 1 ns Instruction Memory 4 ns Register read 3 ns MUX B 1 ns ALU or Memory 4 ns MUX D 1 ns Register write 3 ns – break an instruction execution into multiple cycles – Bucket brigade: pipelined datapath – Microprogrammed datapath 1/15/2022 cs 231 Kale 2

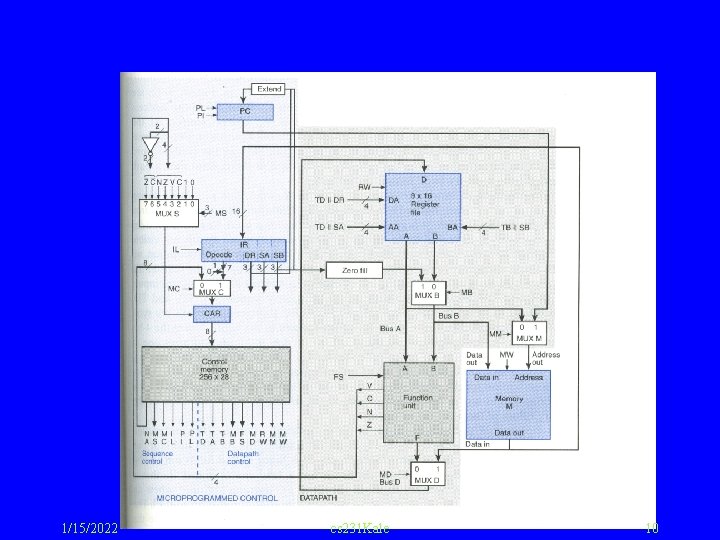

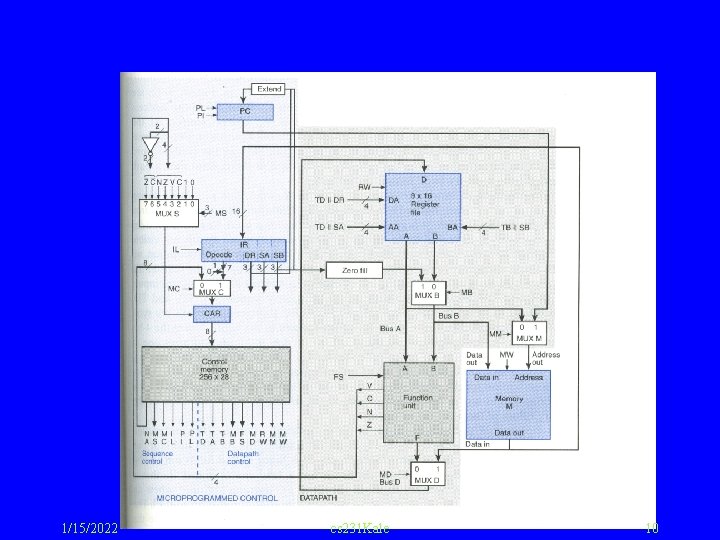

A Microprogrammed Datapath • The datapath we worked with for the past few weeks was just an example • We will look at another datapath today – To emphasize that alternate designs are possible – To show an example where each instruction takes multiple cycles to finish – To show a different way of generating control signals • Material is not based on the book – Used to be in the older version. . – For the exam: • Basic understanding of the slides, and • section 8 -7 (of the 3 rd edition) • Follow the web link there if you are interested 1/15/2022 cs 231 Kale 3

Why multiple cycles? • Wouldn’t it be slower? – Not necessarily: if each clock cycle can be made shorter – Variable number of cycles for instructions (some 2, some 5) 1/15/2022 cs 231 Kale 4

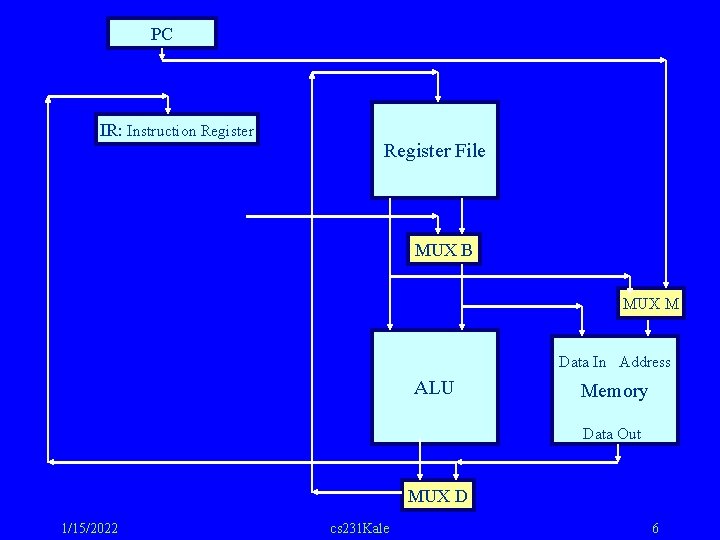

New Datapath • Let us use one memory module – for both data and instructions • Allow for multiple cycles for each instruction 1/15/2022 cs 231 Kale 5

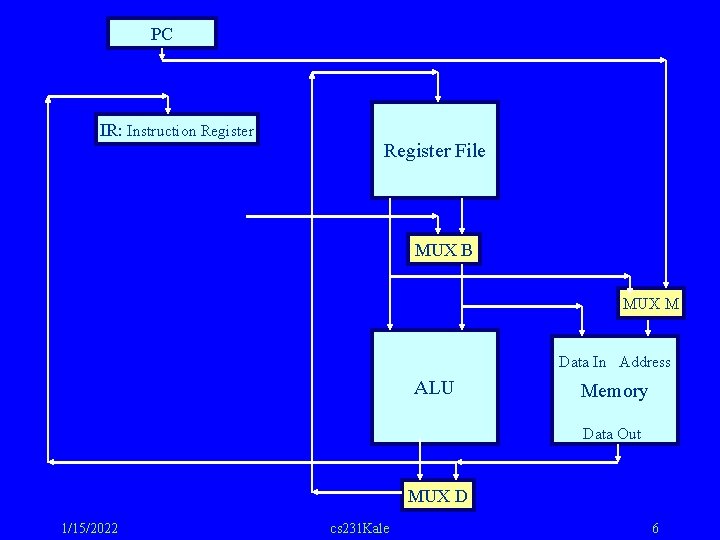

PC IR: Instruction Register File MUX B MUX M Data In Address ALU Memory Data Out MUX D 1/15/2022 cs 231 Kale 6

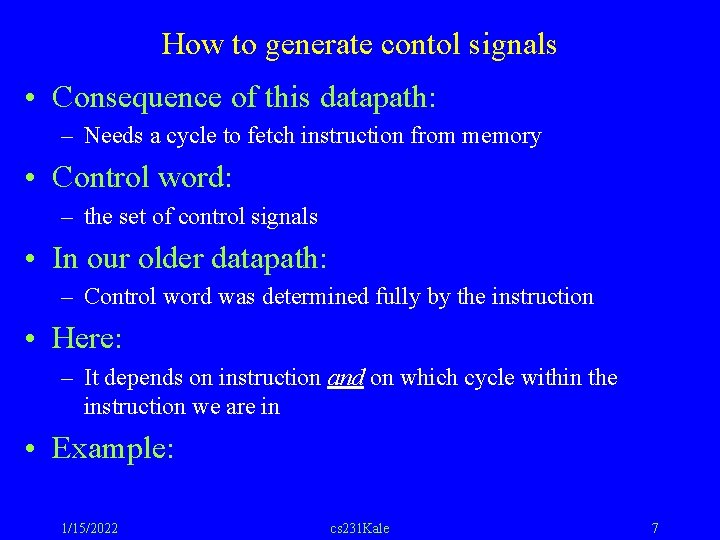

How to generate contol signals • Consequence of this datapath: – Needs a cycle to fetch instruction from memory • Control word: – the set of control signals • In our older datapath: – Control word was determined fully by the instruction • Here: – It depends on instruction and on which cycle within the instruction we are in • Example: 1/15/2022 cs 231 Kale 7

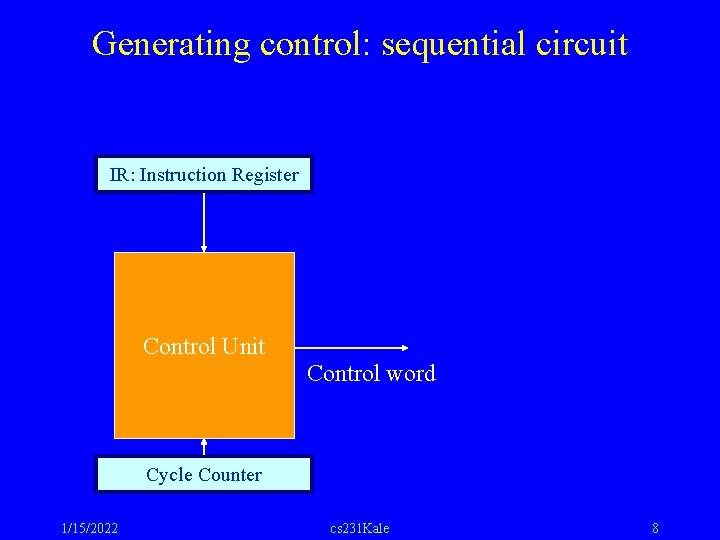

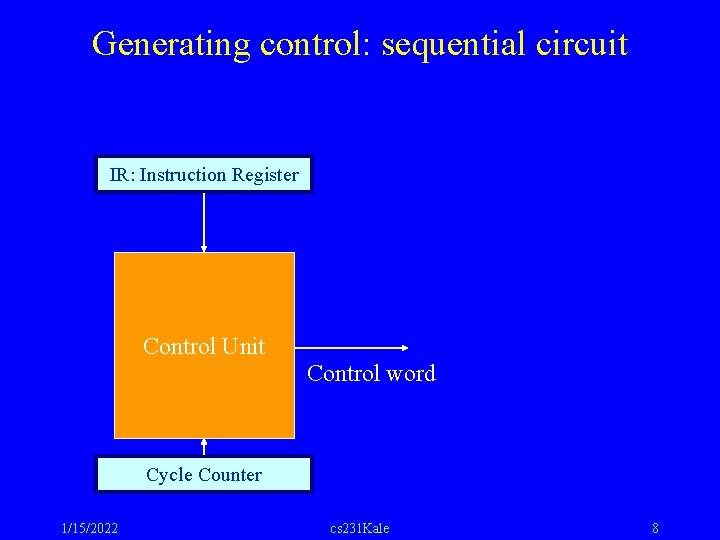

Generating control: sequential circuit IR: Instruction Register Control Unit Control word Cycle Counter 1/15/2022 cs 231 Kale 8

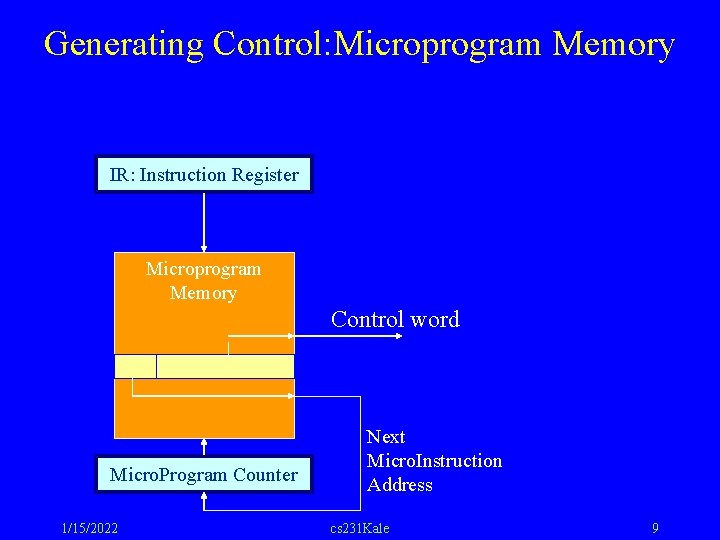

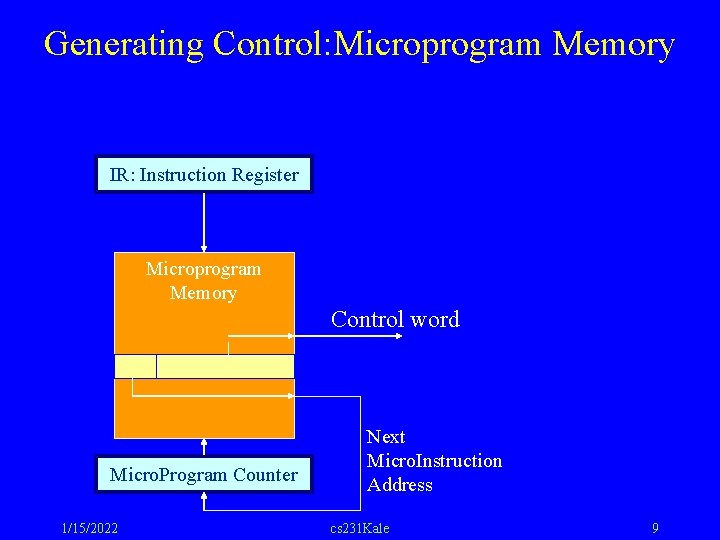

Generating Control: Microprogram Memory IR: Instruction Register Microprogram Memory Control word Micro. Program Counter 1/15/2022 Next Micro. Instruction Address cs 231 Kale 9

1/15/2022 cs 231 Kale 10

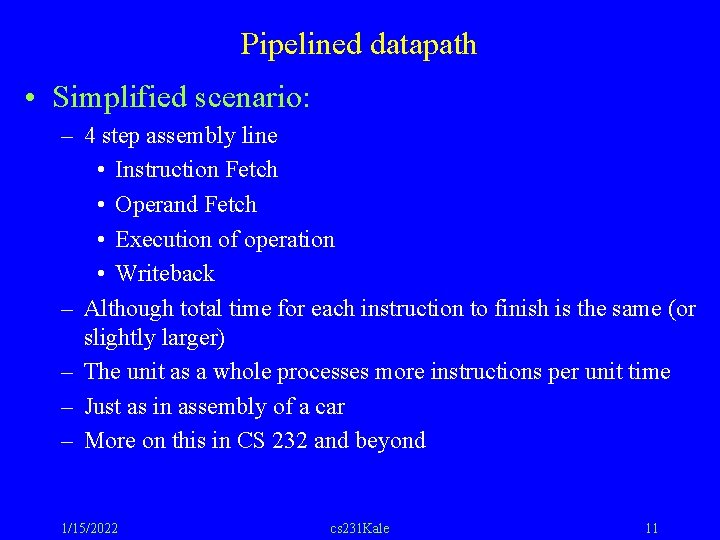

Pipelined datapath • Simplified scenario: – 4 step assembly line • Instruction Fetch • Operand Fetch • Execution of operation • Writeback – Although total time for each instruction to finish is the same (or slightly larger) – The unit as a whole processes more instructions per unit time – Just as in assembly of a car – More on this in CS 232 and beyond 1/15/2022 cs 231 Kale 11