Oscar Ignacio Botero H DIAGRAMA EN BLOQUE SECUENCIA

Oscar Ignacio Botero H.

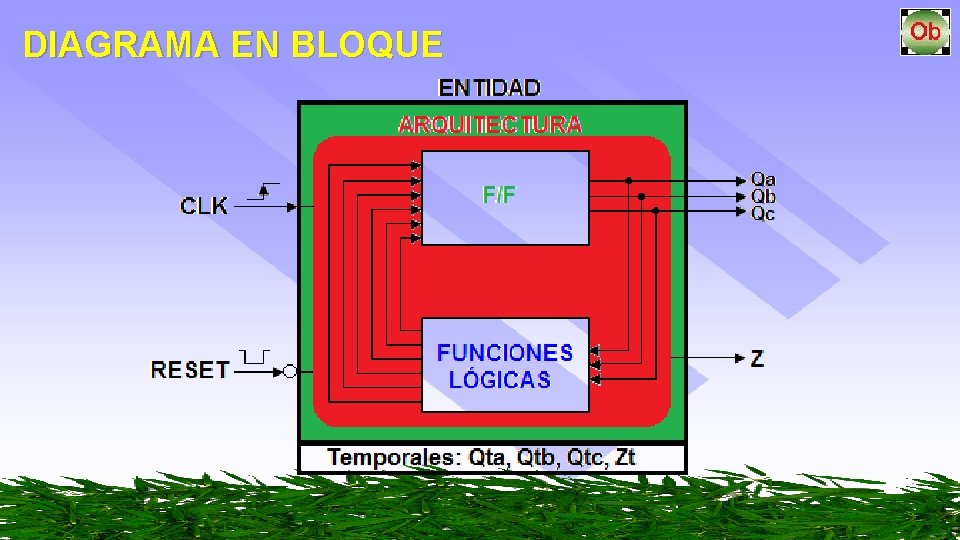

DIAGRAMA EN BLOQUE

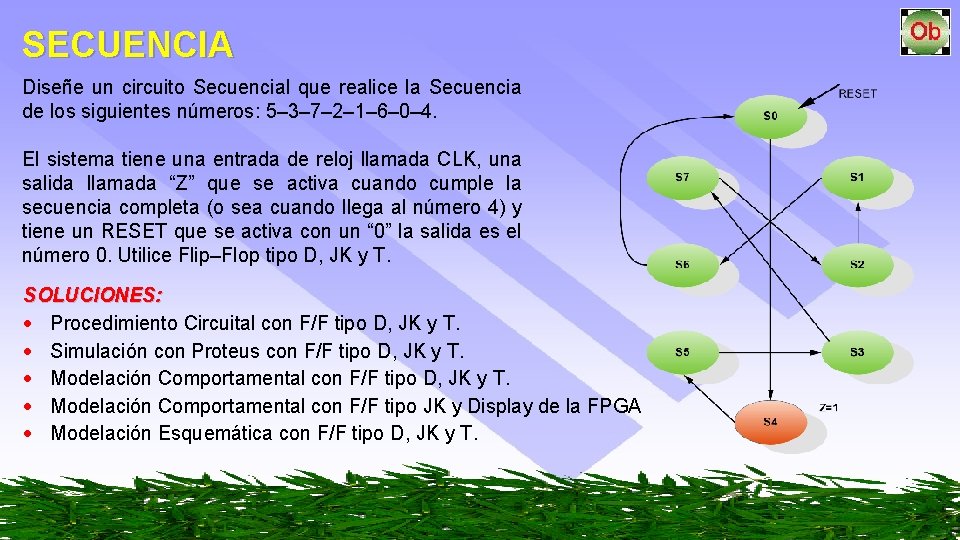

SECUENCIA Diseñe un circuito Secuencial que realice la Secuencia de los siguientes números: 5– 3– 7– 2– 1– 6– 0– 4. El sistema tiene una entrada de reloj llamada CLK, una salida llamada “Z” que se activa cuando cumple la secuencia completa (o sea cuando llega al número 4) y tiene un RESET que se activa con un “ 0” la salida es el número 0. Utilice Flip–Flop tipo D, JK y T. SOLUCIONES: Procedimiento Circuital con F/F tipo D, JK y T. Simulación con Proteus con F/F tipo D, JK y T. Modelación Comportamental con F/F tipo JK y Display de la FPGA Modelación Esquemática con F/F tipo D, JK y T.

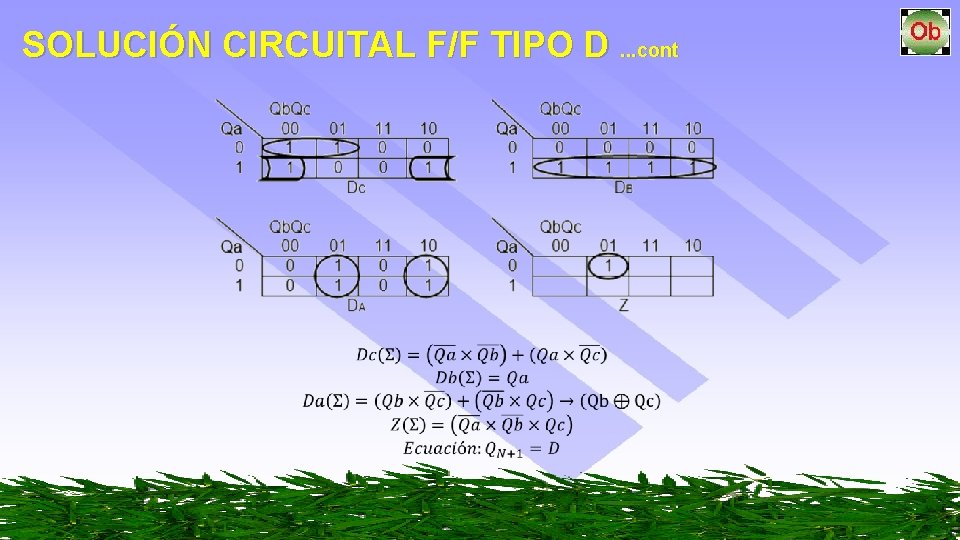

SOLUCIÓN CIRCUITAL F/F TIPO D ü Entradas a los F/F tipo D = Da, Db, Dc ü Salidas de los F/F tipo D = Qa, Qb, Qc ü Salida que visualiza el cumplimiento de la secuencia = Z S 0 S 1 S 2 S 3 S 4 S 5 S 6 S 7 ESTADO ACTUAL Qc Qb Qa 0 0 0 1 1 1 0 0 1 1 1 ESTADO SIGUIENTE Qc Qb Qa 1 0 0 1 1 0 0 0 1 1 1 0 0 1 0 ENTRADAS A LOS F/F TIPO D Dc Db Da 1 0 0 1 1 0 0 0 1 1 1 0 0 1 0 SAL Z 0 0 1 0 0 0 Observe que los valores de las entradas D de los F/F son iguales a los de los estados siguientes.

SOLUCIÓN CIRCUITAL F/F TIPO D. . . cont

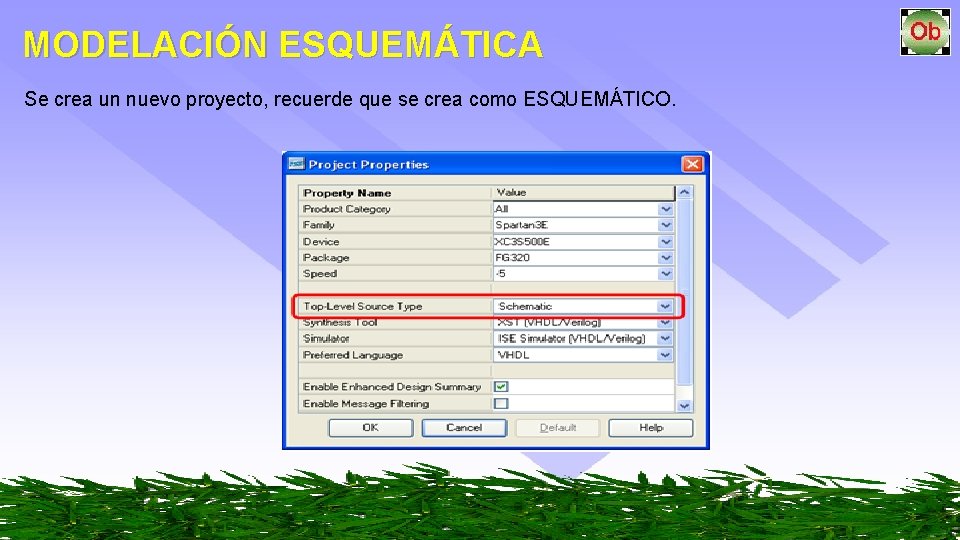

MODELACIÓN ESQUEMÁTICA Se crea un nuevo proyecto, recuerde que se crea como ESQUEMÁTICO.

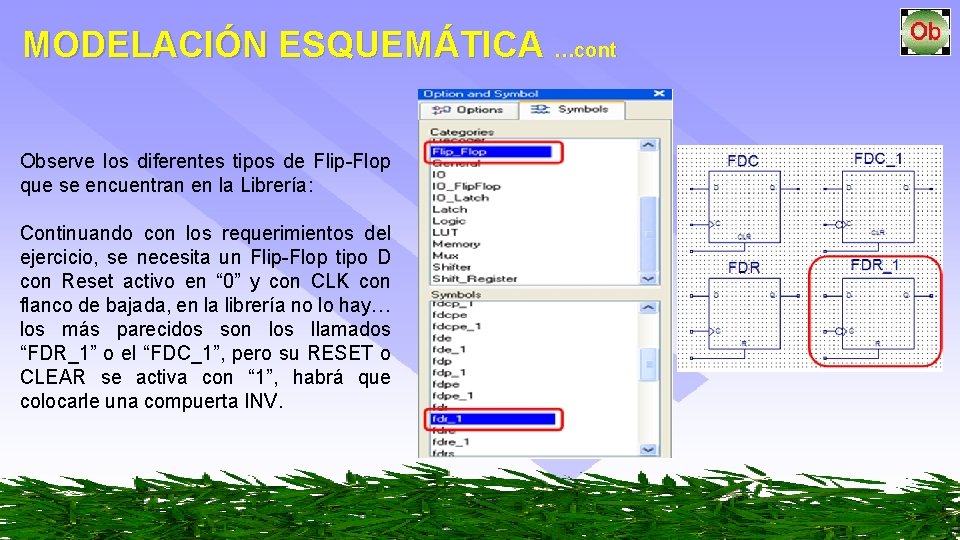

MODELACIÓN ESQUEMÁTICA …cont Observe los diferentes tipos de Flip-Flop que se encuentran en la Librería: Continuando con los requerimientos del ejercicio, se necesita un Flip-Flop tipo D con Reset activo en “ 0” y con CLK con flanco de bajada, en la librería no lo hay… los más parecidos son los llamados “FDR_1” o el “FDC_1”, pero su RESET o CLEAR se activa con “ 1”, habrá que colocarle una compuerta INV.

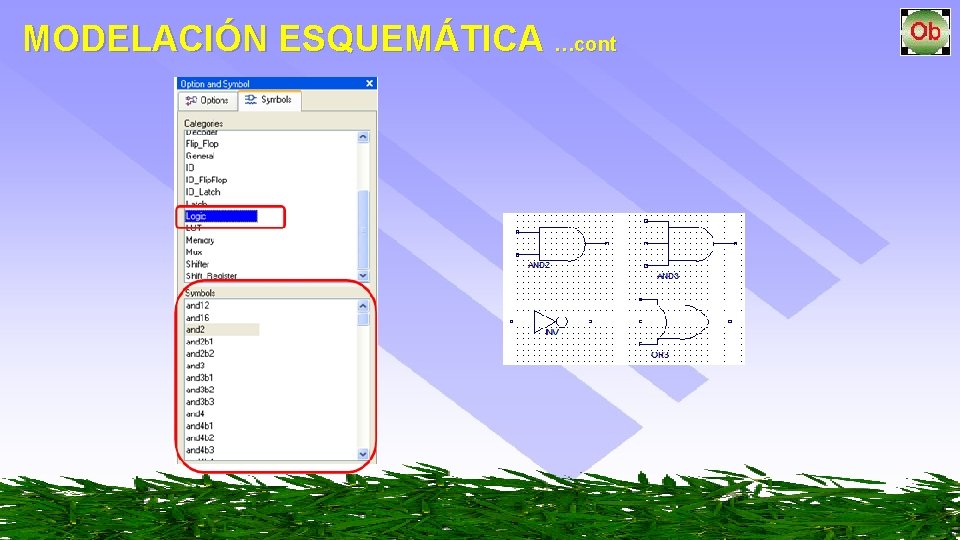

MODELACIÓN ESQUEMÁTICA …cont

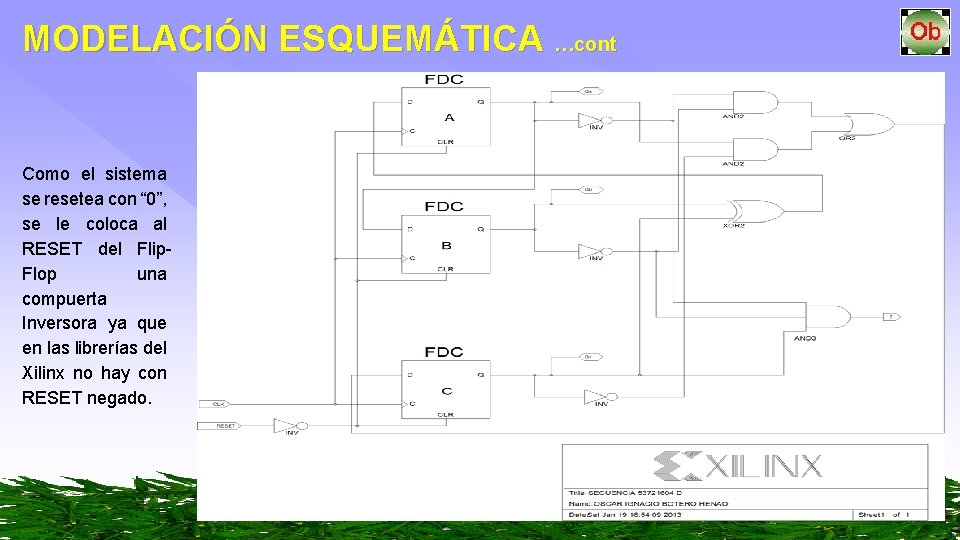

MODELACIÓN ESQUEMÁTICA …cont Como el sistema se resetea con “ 0”, se le coloca al RESET del Flip. Flop una compuerta Inversora ya que en las librerías del Xilinx no hay con RESET negado.

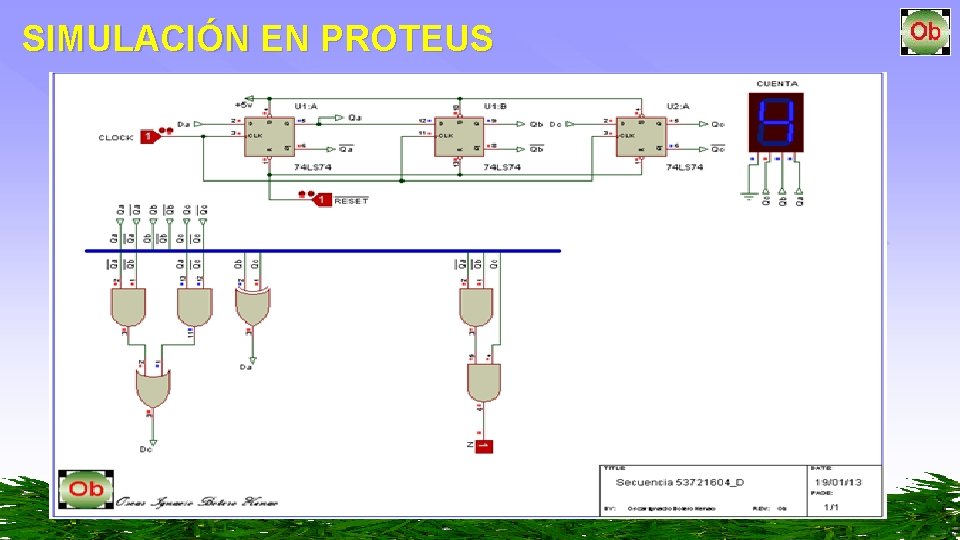

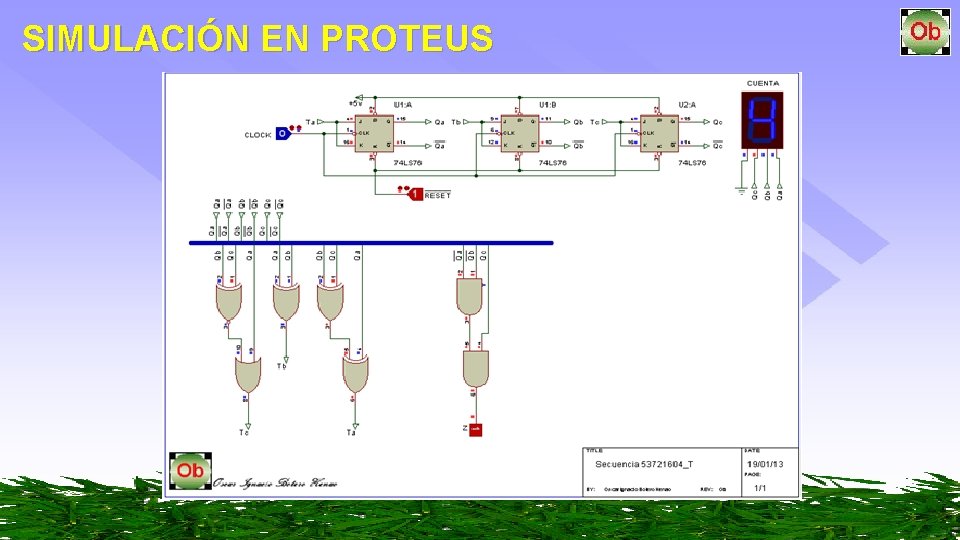

SIMULACIÓN EN PROTEUS

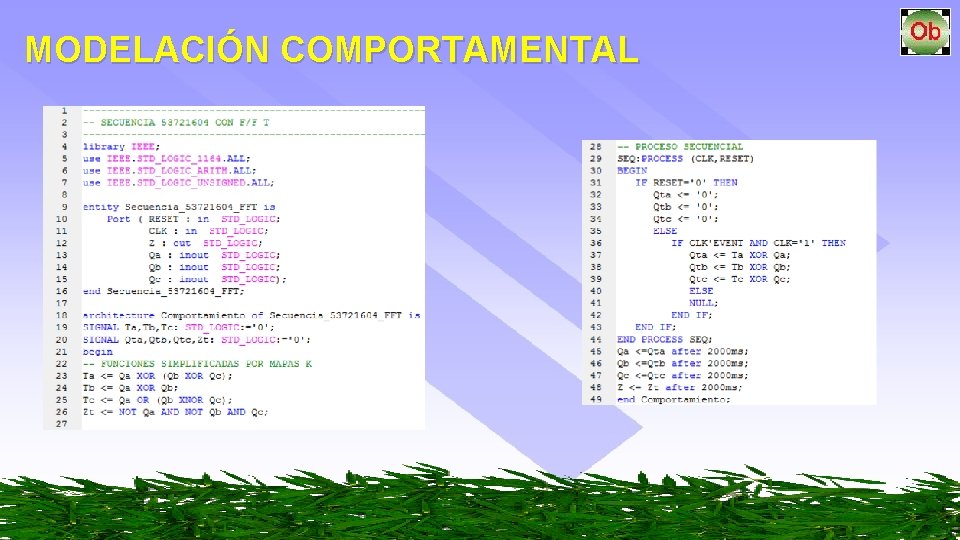

MODELACIÓN COMPORTAMENTAL

SOLUCIÓN CIRCUITAL F/F TIPO JK ü Entradas a los F/F tipo JK = Ja, Ka, Jb, Kb, Jc, Kc ü Salidas de los F/F tipo JK = Qa, Qb, Qc ü Salida que visualiza el cumplimiento de la secuencia = Z ESTADO ACTUAL S 0 S 1 S 2 S 3 S 4 S 5 S 6 S 7 Qc 0 0 1 1 Qb 0 0 1 1 Qa 0 1 0 1 ESTADO SIGUIENTE Qc Qb Qa 1 0 0 1 1 0 0 0 1 1 1 0 0 1 0 ENTRADAS A LOS F/F TIPO JK Jc Kc Jb Kb Ja Ka 1 X 0 X 1 X X 1 0 X X 1 1 X X 0 X 0 0 X 1 X X 1 1 X X 0 X 1 0 X X 1 X 0 X 1 Sal Z 0 0 1 0 0 0

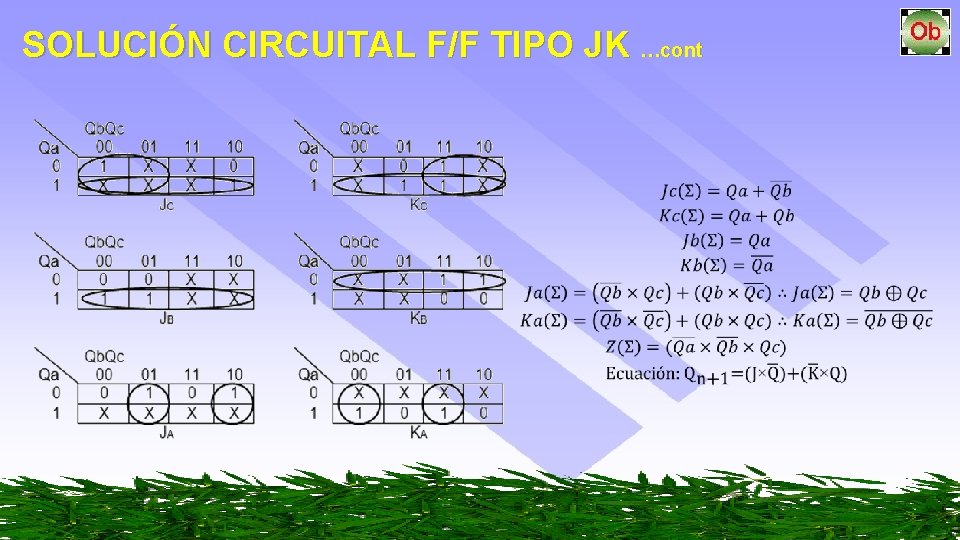

SOLUCIÓN CIRCUITAL F/F TIPO JK …cont

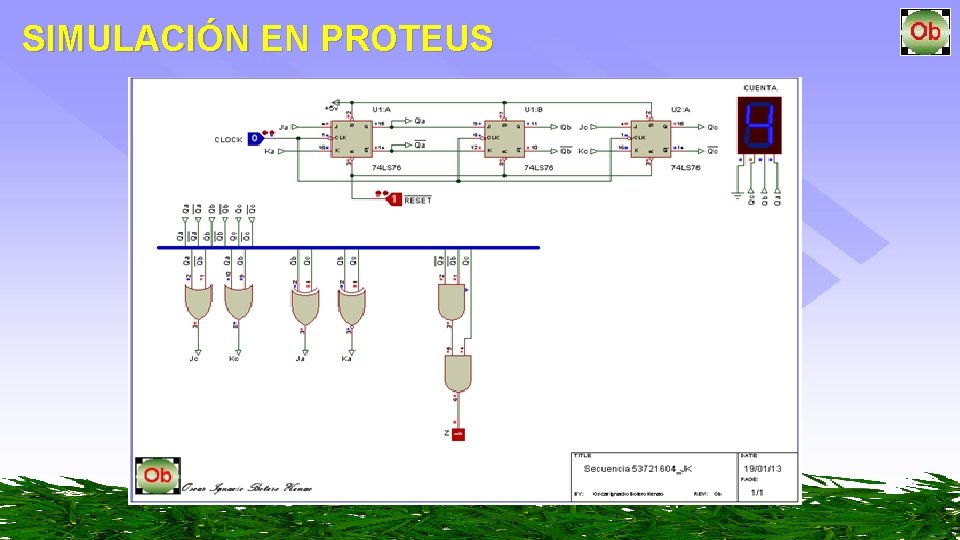

SIMULACIÓN EN PROTEUS

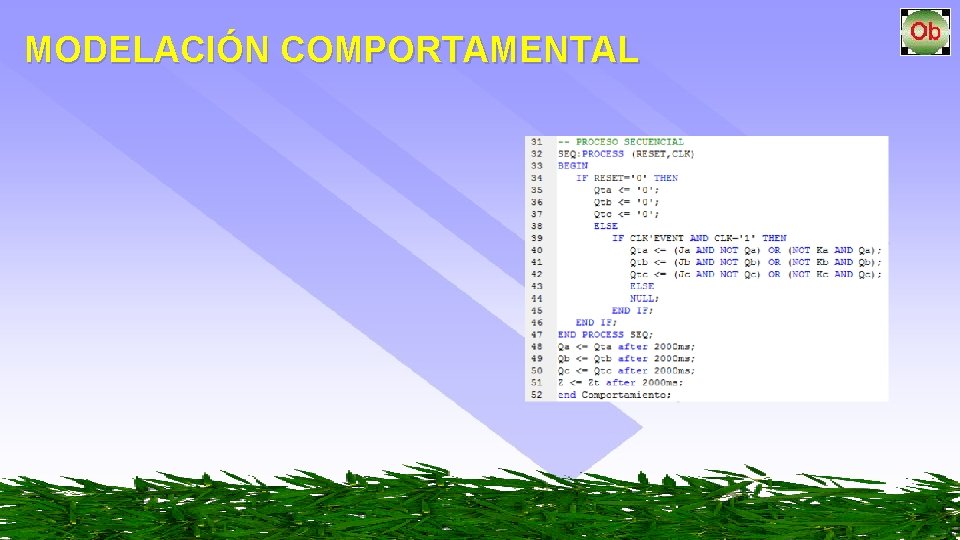

MODELACIÓN COMPORTAMENTAL

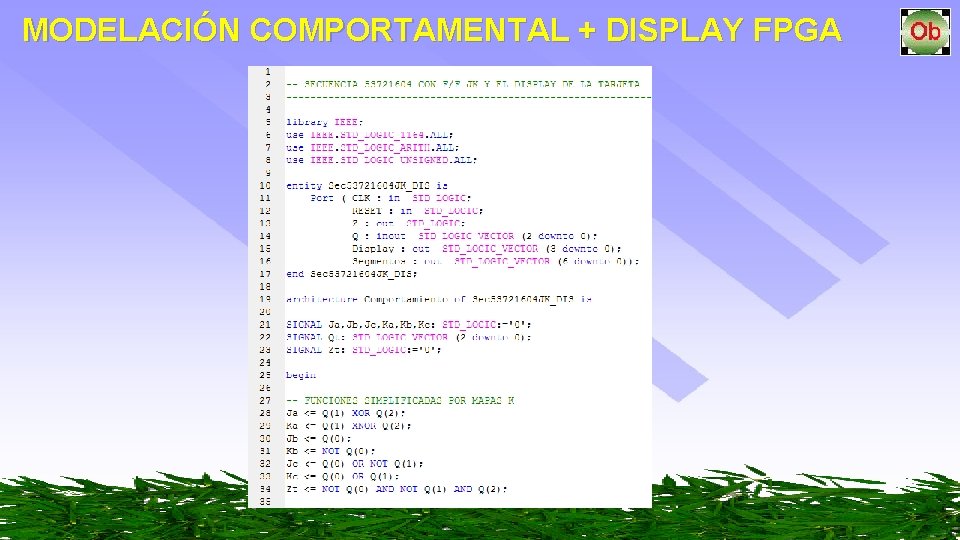

MODELACIÓN COMPORTAMENTAL + DISPLAY FPGA

MODELACIÓN COMPORTAMENTAL + DISPLAY FPGA …cont

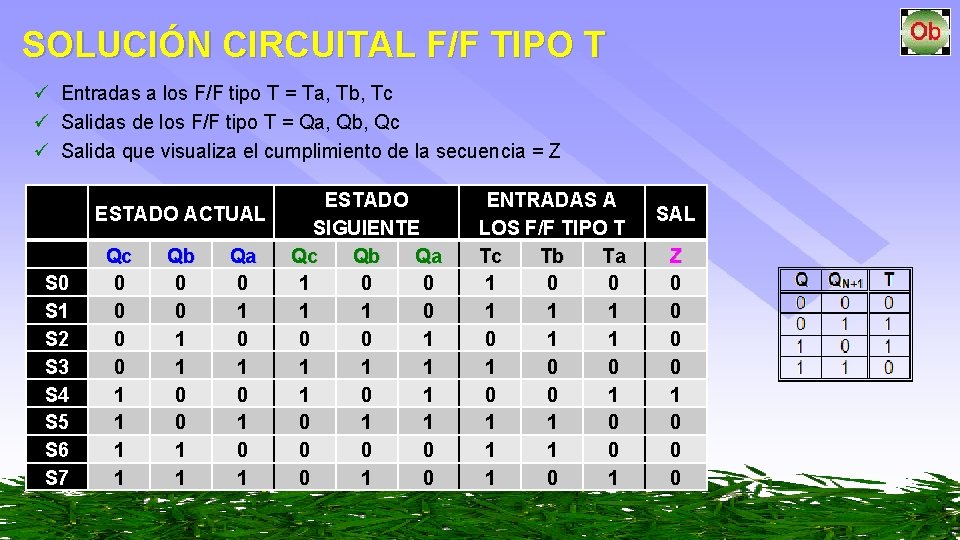

SOLUCIÓN CIRCUITAL F/F TIPO T ü Entradas a los F/F tipo T = Ta, Tb, Tc ü Salidas de los F/F tipo T = Qa, Qb, Qc ü Salida que visualiza el cumplimiento de la secuencia = Z S 0 S 1 S 2 S 3 S 4 S 5 S 6 S 7 ESTADO ACTUAL Qc 0 0 1 1 Qb 0 0 1 1 Qa 0 1 0 1 ESTADO SIGUIENTE Qc Qb Qa 1 0 0 1 1 0 0 0 1 1 1 0 0 1 0 ENTRADAS A LOS F/F TIPO T Tc Tb Ta 1 0 0 1 1 1 0 1 0 1 SAL Z 0 0 1 0 0 0

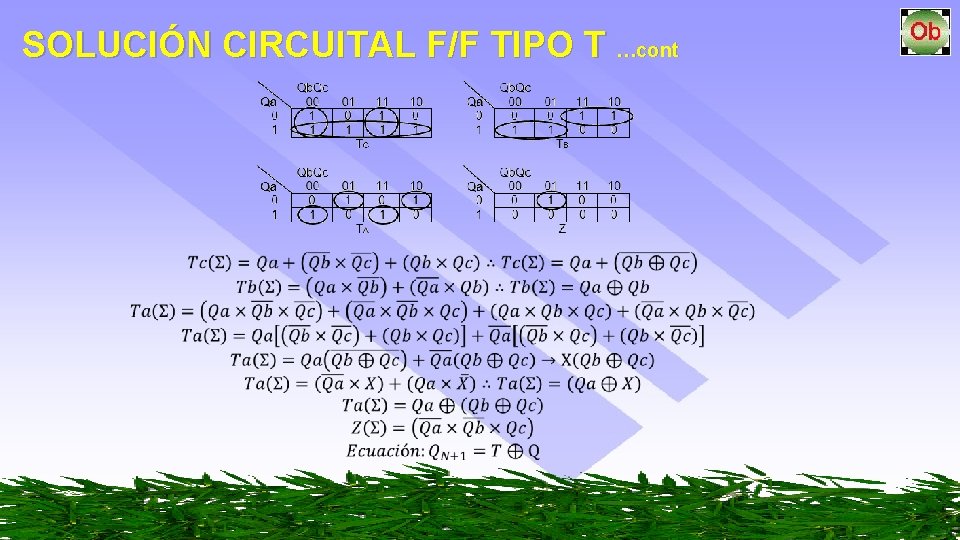

SOLUCIÓN CIRCUITAL F/F TIPO T …cont

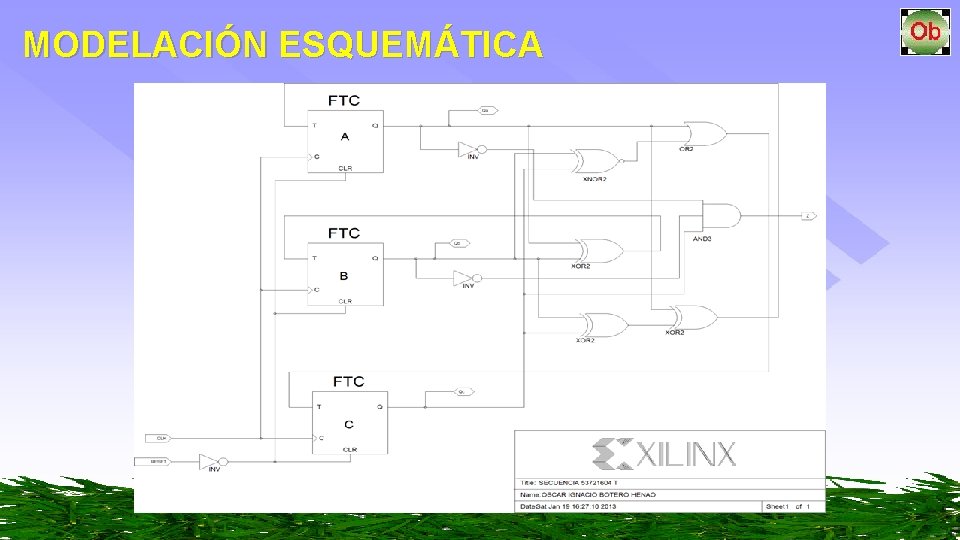

MODELACIÓN ESQUEMÁTICA

SIMULACIÓN EN PROTEUS

MODELACIÓN COMPORTAMENTAL

GRACIAS

- Slides: 23