Organizao e Arquitetura de Computadores II Modos de

- Slides: 34

Organização e Arquitetura de Computadores II Modos de Transferência Interrupção Capítulo 10. 5 do Monteiro Capítulo 7 do Stallings Capítulos 5. 5, 5. 6 do Tanenbaum & Austin Última alteração: 05/04/2018 Prof. Ney Laert Vilar Calazans Baseado em notas de aulas originais do Prof. Dr. César Marcon

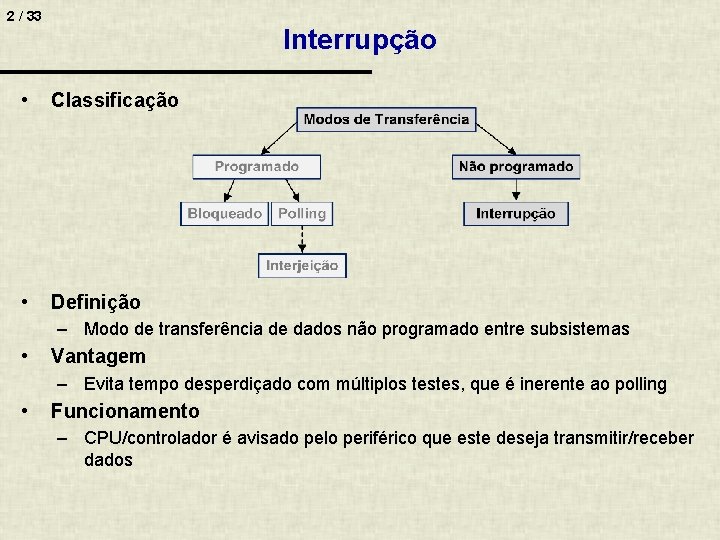

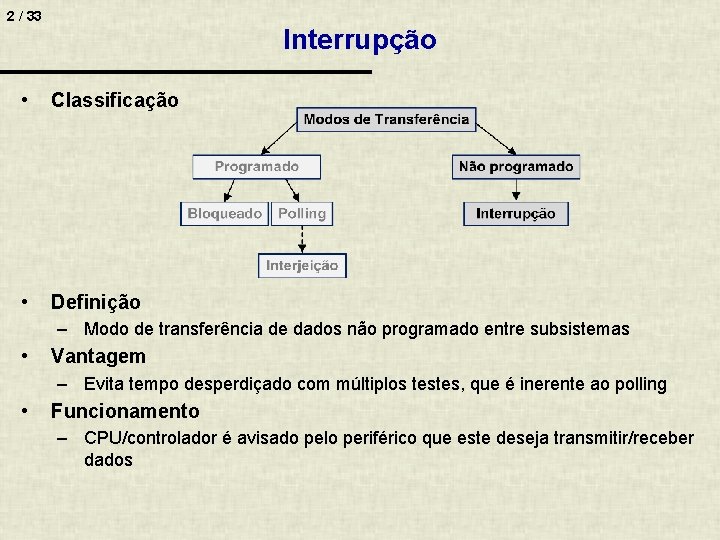

2 / 33 Interrupção • Classificação • Definição – Modo de transferência de dados não programado entre subsistemas • Vantagem – Evita tempo desperdiçado com múltiplos testes, que é inerente ao polling • Funcionamento – CPU/controlador é avisado pelo periférico que este deseja transmitir/receber dados

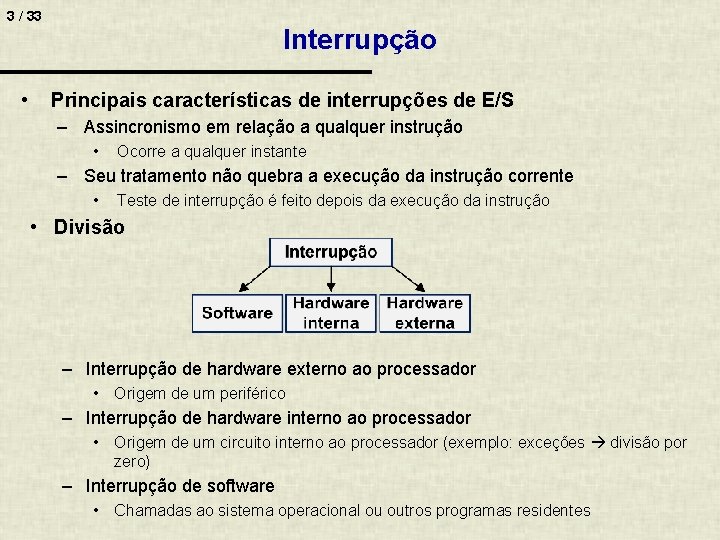

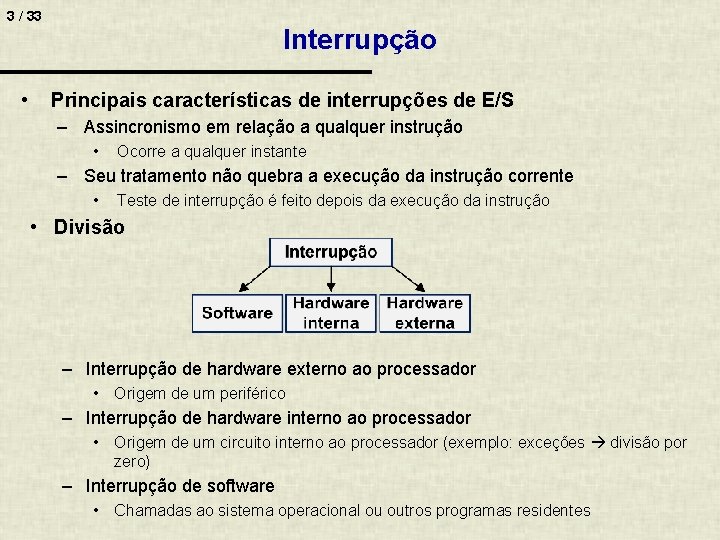

3 / 33 • Interrupção Principais características de interrupções de E/S – Assincronismo em relação a qualquer instrução • Ocorre a qualquer instante – Seu tratamento não quebra a execução da instrução corrente • Teste de interrupção é feito depois da execução da instrução • Divisão – Interrupção de hardware externo ao processador • Origem de um periférico – Interrupção de hardware interno ao processador • Origem de um circuito interno ao processador (exemplo: exceções divisão por zero) – Interrupção de software • Chamadas ao sistema operacional ou outros programas residentes

4 / 33 Interrupção – Procedimento ao Ocorrer Interrupção 1. Priorizar interrupções • Atender de maior prioridade no caso de simultaneidade de interrupções 2. Tratamento de interrupções aninhadas • • Desabilitar interrupções, caso não seja permitido aninhamento de interrupções Prosseguir normalmente, caso contrário 3. Salvar contexto (PC, registradores) • • 4. 5. 6. 7. 8. Salvamento rápido (um ciclo próprio processador) Salvamento lento (diversos ciclos sequência de instruções para por na pilha) Identificar periférico Desviar PC para rotina de tratamento da interrupção Executar programa de interrupção Recuperar contexto Reabilitar interrupções (caso tenham sido desabilitadas)

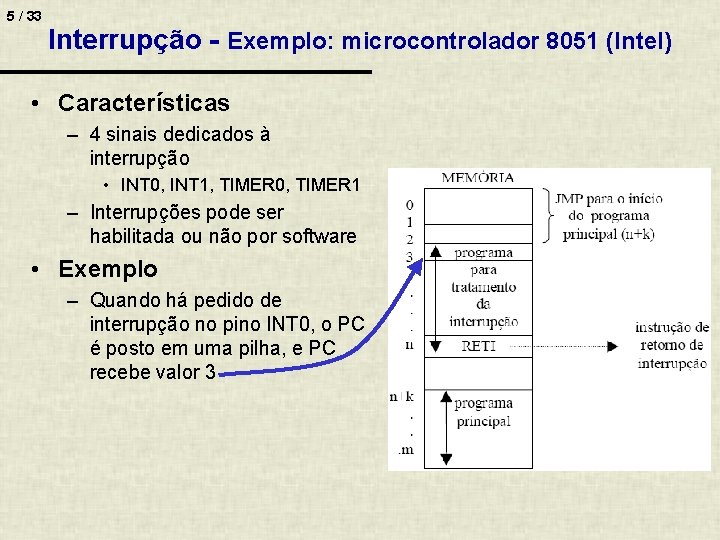

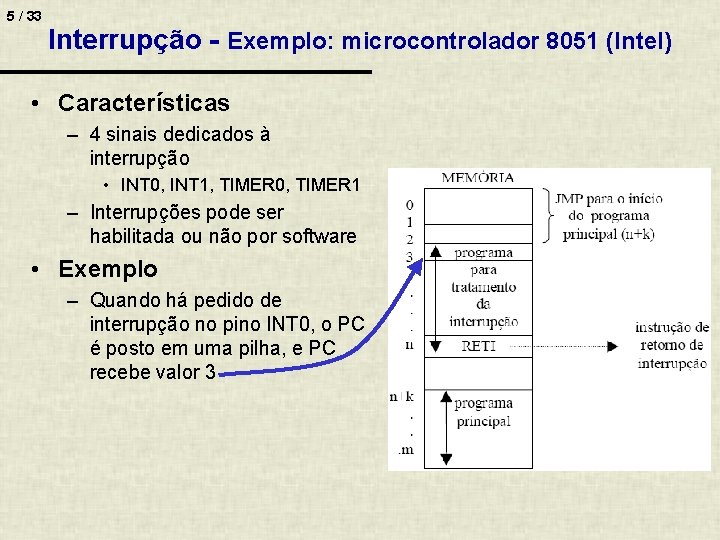

5 / 33 Interrupção - Exemplo: microcontrolador 8051 (Intel) • Características – 4 sinais dedicados à interrupção • INT 0, INT 1, TIMER 0, TIMER 1 – Interrupções pode ser habilitada ou não por software • Exemplo – Quando há pedido de interrupção no pino INT 0, o PC é posto em uma pilha, e PC recebe valor 3

6 / 33 Tratamento de Interrupções Simultâneas Interrupção seguida de polling • Funcionamento – Opera do mesmo modo que na interjeição • Ou lógico de todos os pedidos de interrupção é enviado ao processador/controlador • Vantagem – Menor número de pinos de E/S – Menor custo de hardware • Consequência – Lento • São feitos testes sequenciais para atendimento dos periféricos

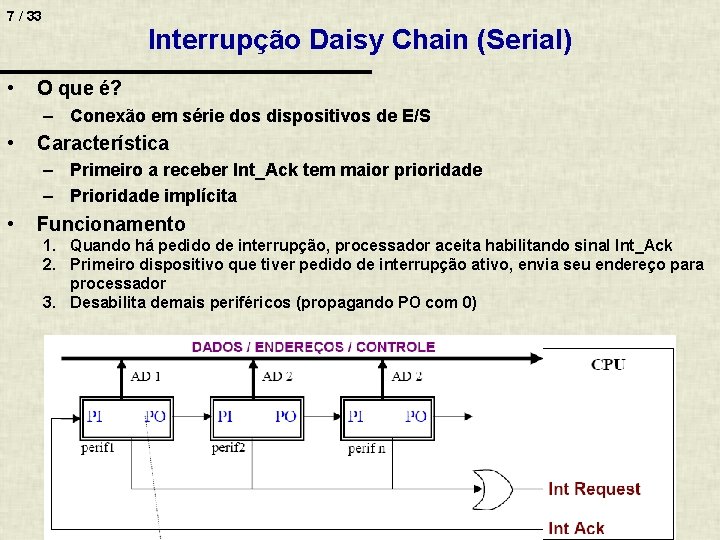

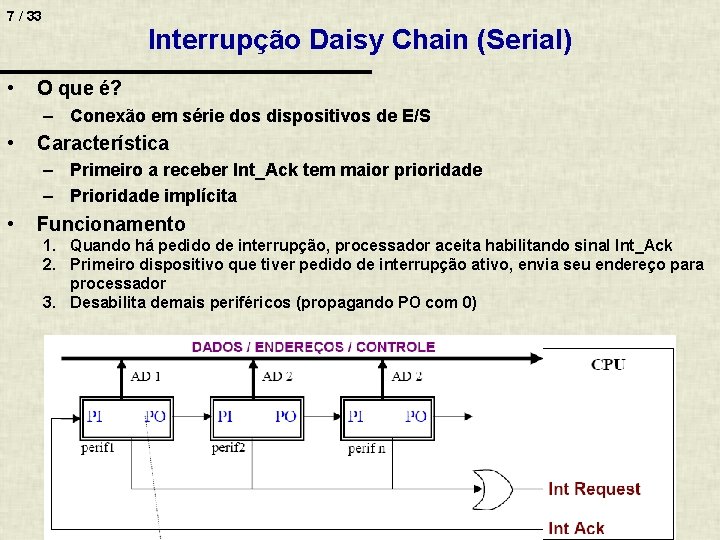

7 / 33 • Interrupção Daisy Chain (Serial) O que é? – Conexão em série dos dispositivos de E/S • Característica – Primeiro a receber Int_Ack tem maior prioridade – Prioridade implícita • Funcionamento 1. Quando há pedido de interrupção, processador aceita habilitando sinal Int_Ack 2. Primeiro dispositivo que tiver pedido de interrupção ativo, envia seu endereço para processador 3. Desabilita demais periféricos (propagando PO com 0)

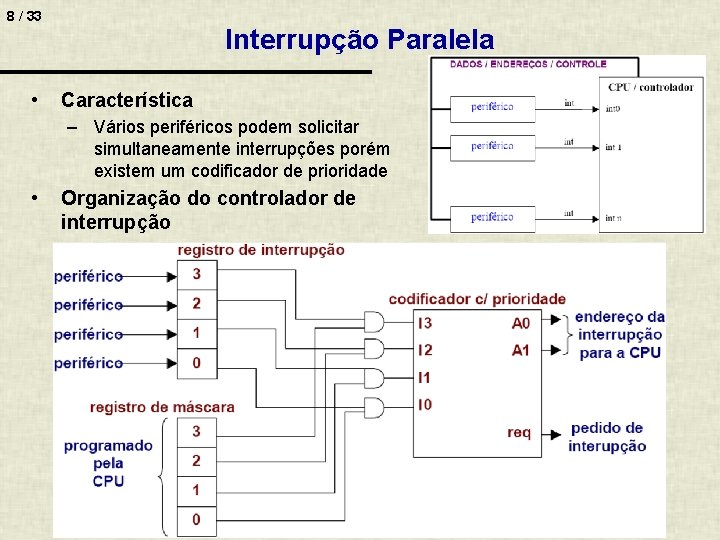

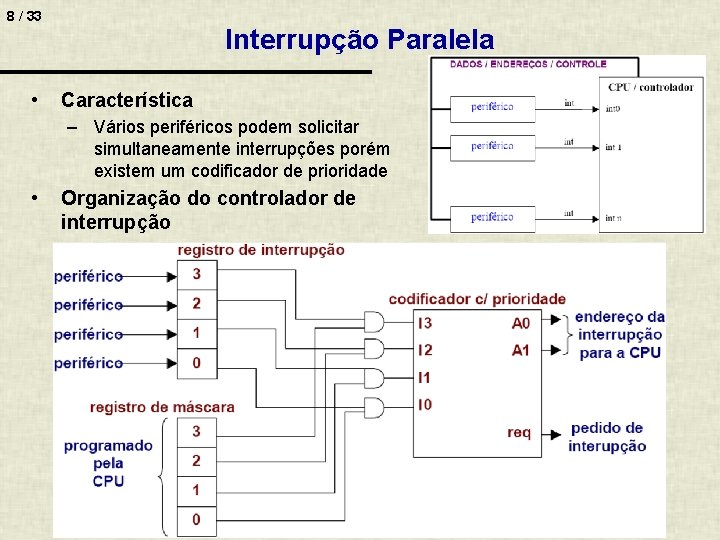

8 / 33 • Interrupção Paralela Característica – Vários periféricos podem solicitar simultaneamente interrupções porém existem um codificador de prioridade • Organização do controlador de interrupção

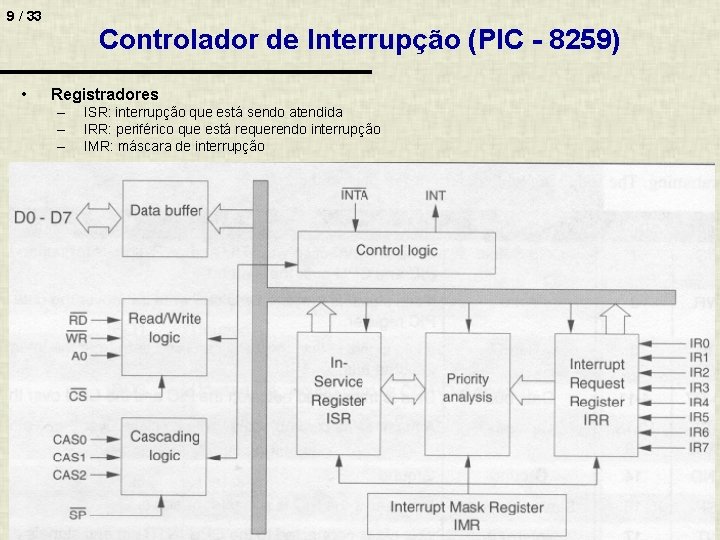

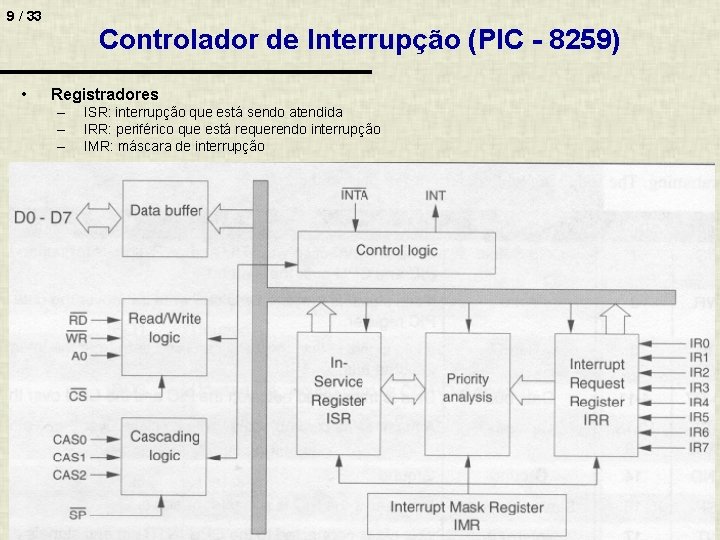

9 / 33 • Controlador de Interrupção (PIC - 8259) Registradores – – – ISR: interrupção que está sendo atendida IRR: periférico que está requerendo interrupção IMR: máscara de interrupção

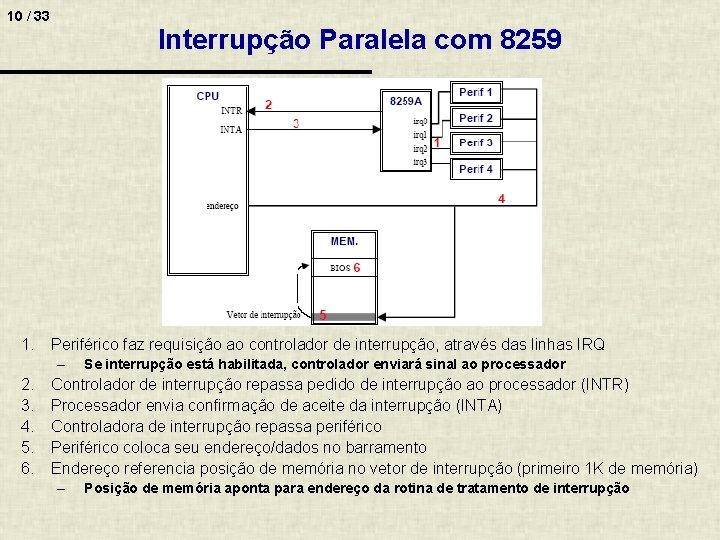

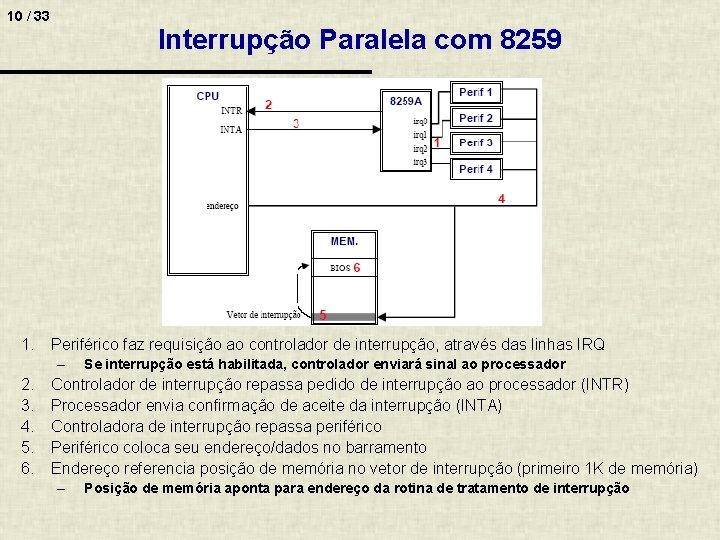

10 / 33 Interrupção Paralela com 8259 1. Periférico faz requisição ao controlador de interrupção, através das linhas IRQ – 2. 3. 4. 5. 6. Se interrupção está habilitada, controlador enviará sinal ao processador Controlador de interrupção repassa pedido de interrupção ao processador (INTR) Processador envia confirmação de aceite da interrupção (INTA) Controladora de interrupção repassa periférico Periférico coloca seu endereço/dados no barramento Endereço referencia posição de memória no vetor de interrupção (primeiro 1 K de memória) – Posição de memória aponta para endereço da rotina de tratamento de interrupção

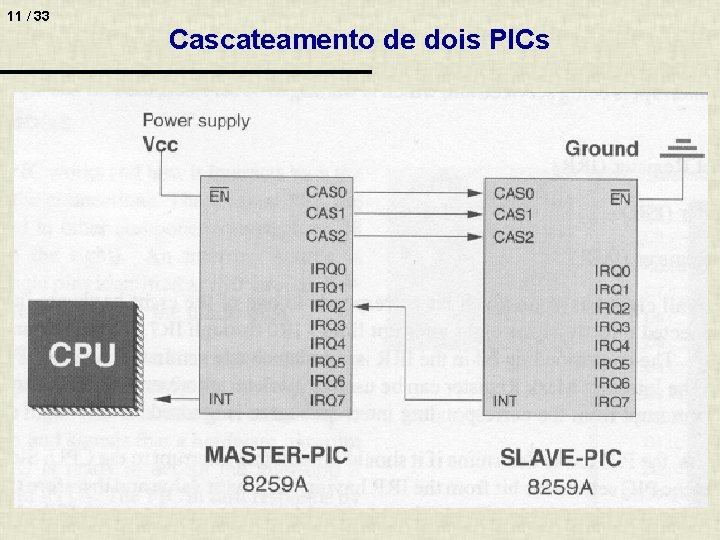

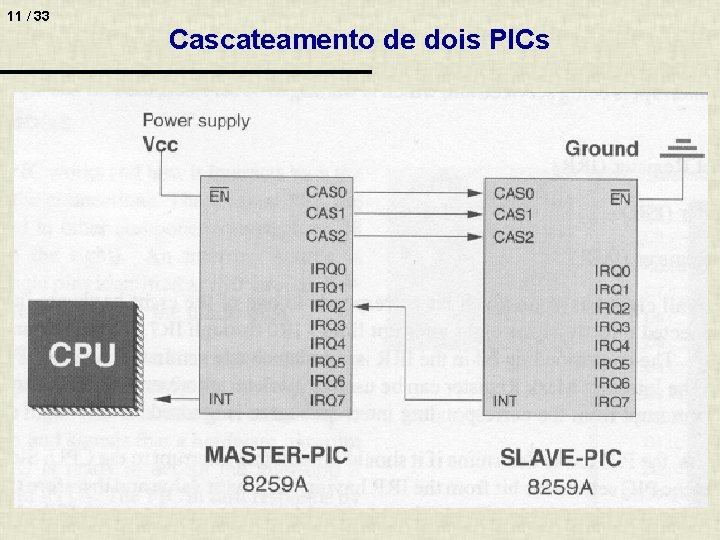

11 / 33 Cascateamento de dois PICs

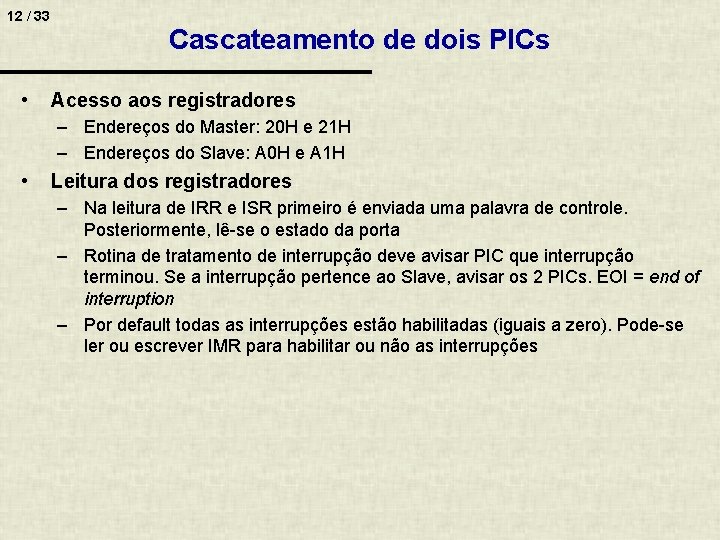

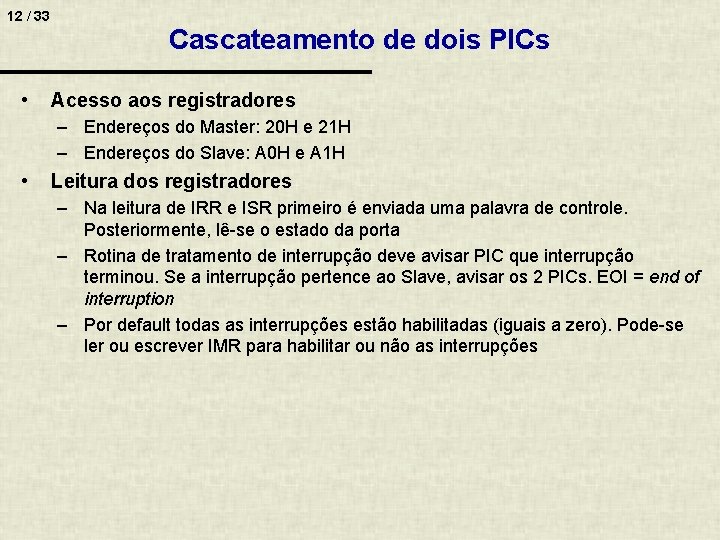

12 / 33 • Cascateamento de dois PICs Acesso aos registradores – Endereços do Master: 20 H e 21 H – Endereços do Slave: A 0 H e A 1 H • Leitura dos registradores – Na leitura de IRR e ISR primeiro é enviada uma palavra de controle. Posteriormente, lê-se o estado da porta – Rotina de tratamento de interrupção deve avisar PIC que interrupção terminou. Se a interrupção pertence ao Slave, avisar os 2 PICs. EOI = end of interruption – Por default todas as interrupções estão habilitadas (iguais a zero). Pode-se ler ou escrever IMR para habilitar ou não as interrupções

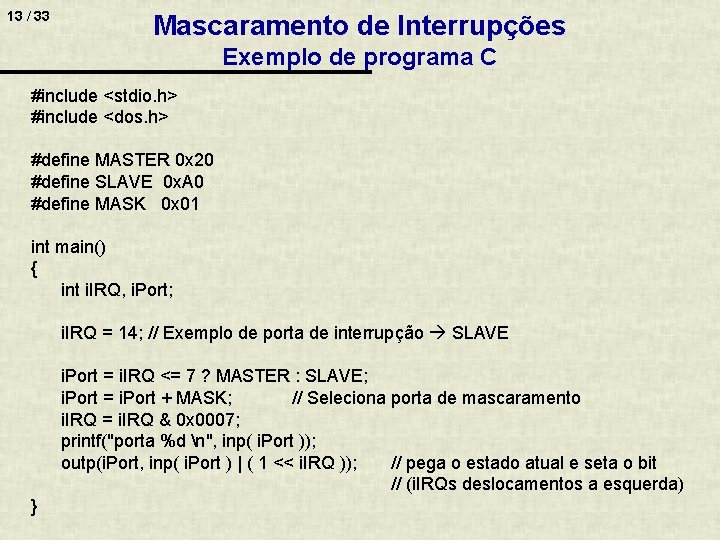

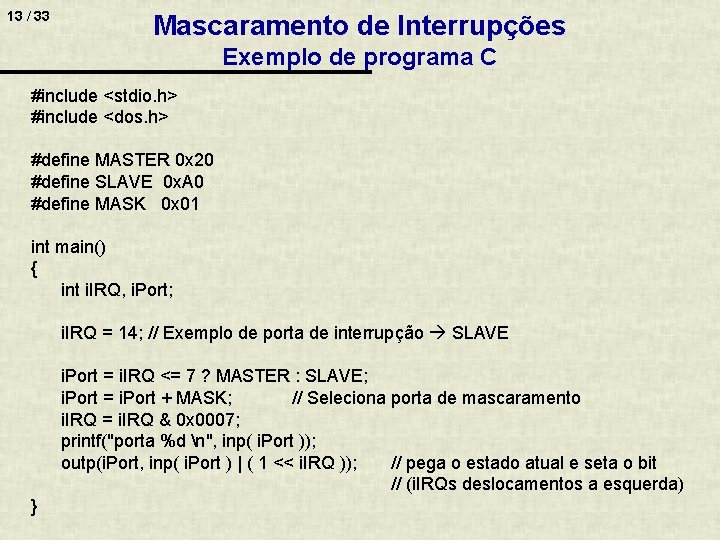

13 / 33 Mascaramento de Interrupções Exemplo de programa C #include <stdio. h> #include <dos. h> #define MASTER 0 x 20 #define SLAVE 0 x. A 0 #define MASK 0 x 01 int main() { int i. IRQ, i. Port; i. IRQ = 14; // Exemplo de porta de interrupção SLAVE i. Port = i. IRQ <= 7 ? MASTER : SLAVE; i. Port = i. Port + MASK; // Seleciona porta de mascaramento i. IRQ = i. IRQ & 0 x 0007; printf("porta %d n", inp( i. Port )); outp(i. Port, inp( i. Port ) | ( 1 << i. IRQ )); // pega o estado atual e seta o bit // (i. IRQs deslocamentos a esquerda) }

14 / 33 Exercícios 1. Explique as principais diferenças entre E/S programada e E/S não programada 2. Mostre o diagrama de um sistema de E/S por interrupção tipo Daisy-Chain. Explique-o 3. Compare polling, interjeição e interrupção em nível de hardware. Fale sobre vantagens e desvantagens 4. Faça a mesma comparação acima agora em nível de software. Mostre como seriam rotinas para tratamento dos métodos. Considere que existem 3 periféricos para serem verificados

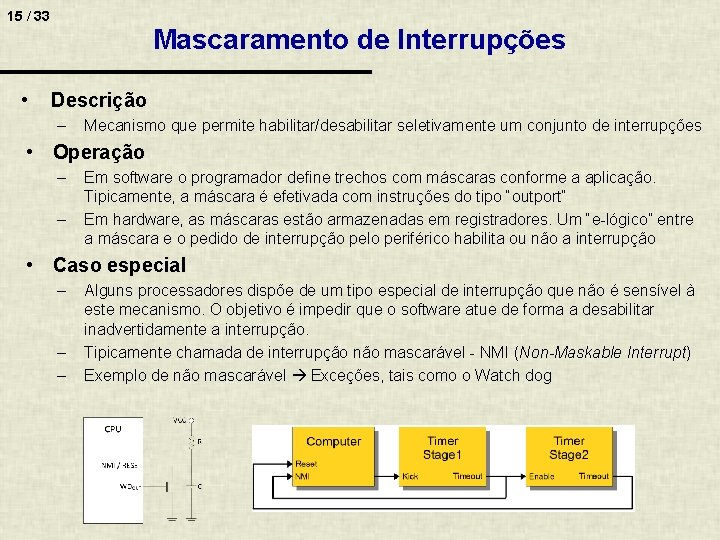

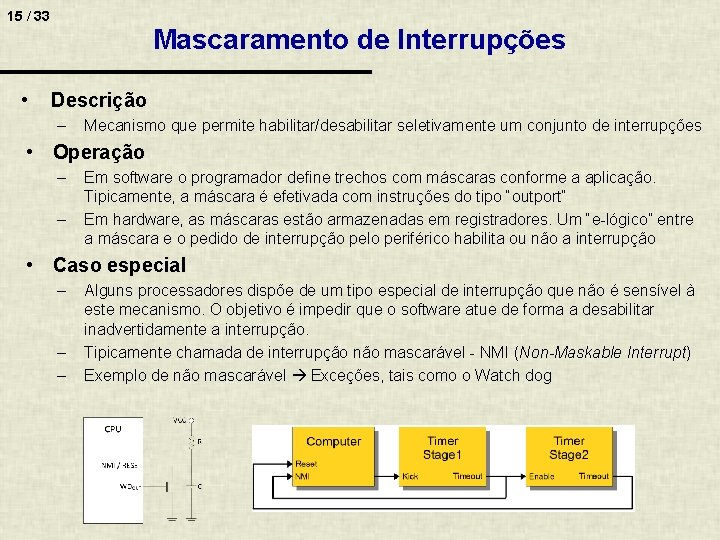

15 / 33 • Mascaramento de Interrupções Descrição – Mecanismo que permite habilitar/desabilitar seletivamente um conjunto de interrupções • Operação – – Em software o programador define trechos com máscaras conforme a aplicação. Tipicamente, a máscara é efetivada com instruções do tipo “outport” Em hardware, as máscaras estão armazenadas em registradores. Um “e-lógico” entre a máscara e o pedido de interrupção pelo periférico habilita ou não a interrupção • Caso especial – – – Alguns processadores dispõe de um tipo especial de interrupção que não é sensível à este mecanismo. O objetivo é impedir que o software atue de forma a desabilitar inadvertidamente a interrupção. Tipicamente chamada de interrupção não mascarável - NMI (Non-Maskable Interrupt) Exemplo de não mascarável Exceções, tais como o Watch dog

16 / 33 Interrupções no x 86 (Intel) 1. Externas – Periféricos • Teclado • Impressora • Placa de rede, … – Ativação • Através de pinos do processador – INTR (interrupt request) – NMI (interrupção não mascarável) 2. Internas ao processador – Também denominadas exceções – Exemplo • Divisão por 0 • Tentativa de executar instrução inválida

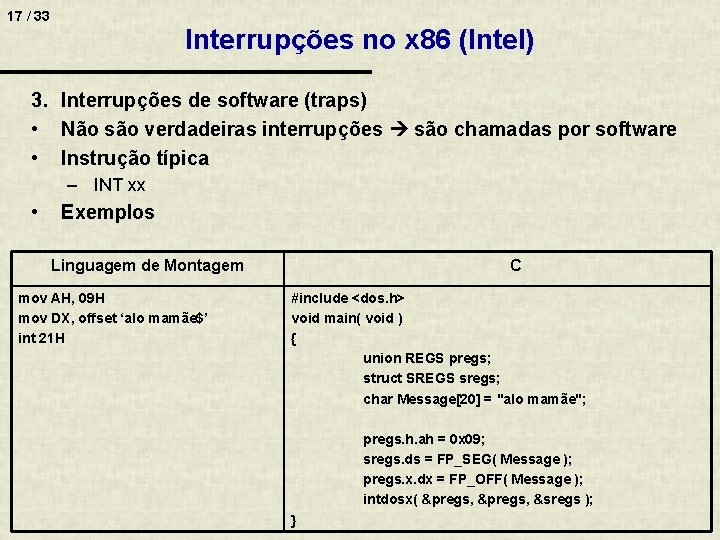

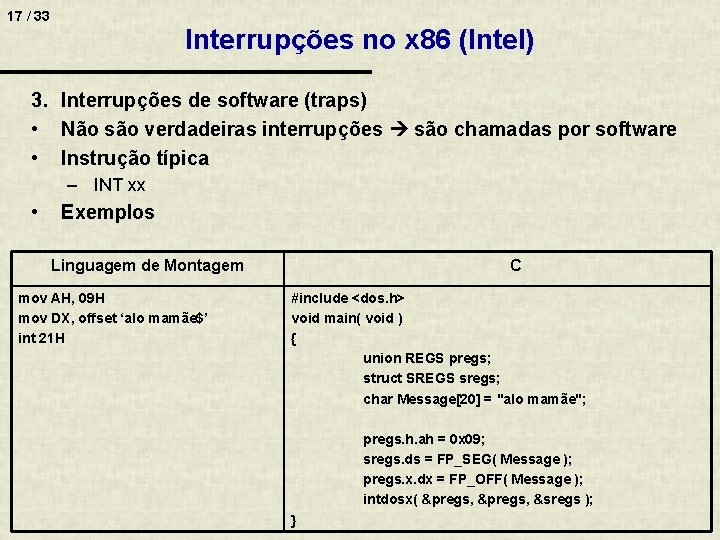

17 / 33 Interrupções no x 86 (Intel) 3. Interrupções de software (traps) • Não são verdadeiras interrupções são chamadas por software • Instrução típica – INT xx • Exemplos Linguagem de Montagem mov AH, 09 H mov DX, offset ‘alo mamãe$’ int 21 H C #include <dos. h> void main( void ) { union REGS pregs; struct SREGS sregs; char Message[20] = "alo mamãe"; pregs. h. ah = 0 x 09; sregs. ds = FP_SEG( Message ); pregs. x. dx = FP_OFF( Message ); intdosx( &pregs, &sregs ); }

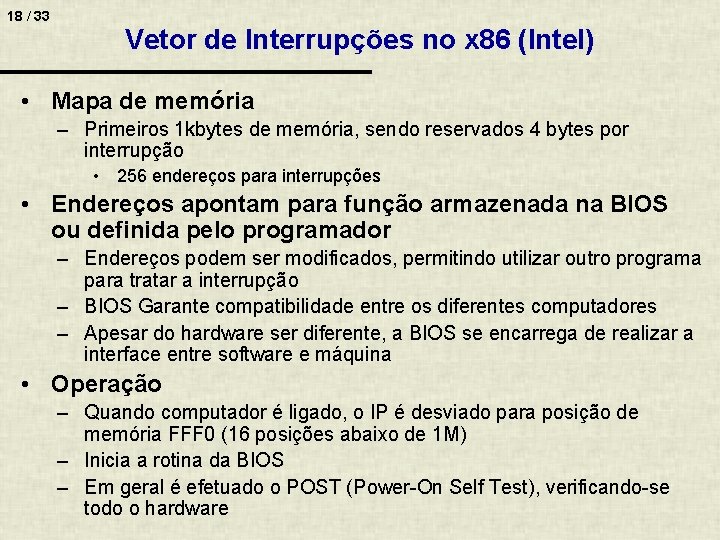

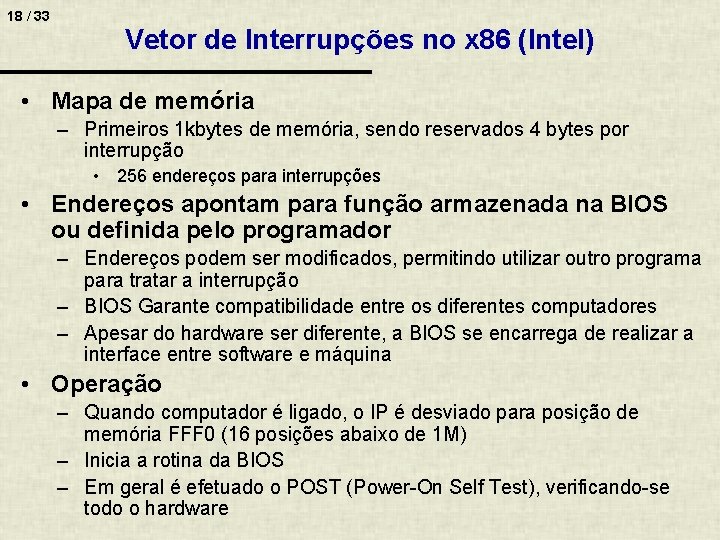

18 / 33 Vetor de Interrupções no x 86 (Intel) • Mapa de memória – Primeiros 1 kbytes de memória, sendo reservados 4 bytes por interrupção • 256 endereços para interrupções • Endereços apontam para função armazenada na BIOS ou definida pelo programador – Endereços podem ser modificados, permitindo utilizar outro programa para tratar a interrupção – BIOS Garante compatibilidade entre os diferentes computadores – Apesar do hardware ser diferente, a BIOS se encarrega de realizar a interface entre software e máquina • Operação – Quando computador é ligado, o IP é desviado para posição de memória FFF 0 (16 posições abaixo de 1 M) – Inicia a rotina da BIOS – Em geral é efetuado o POST (Power-On Self Test), verificando-se todo o hardware

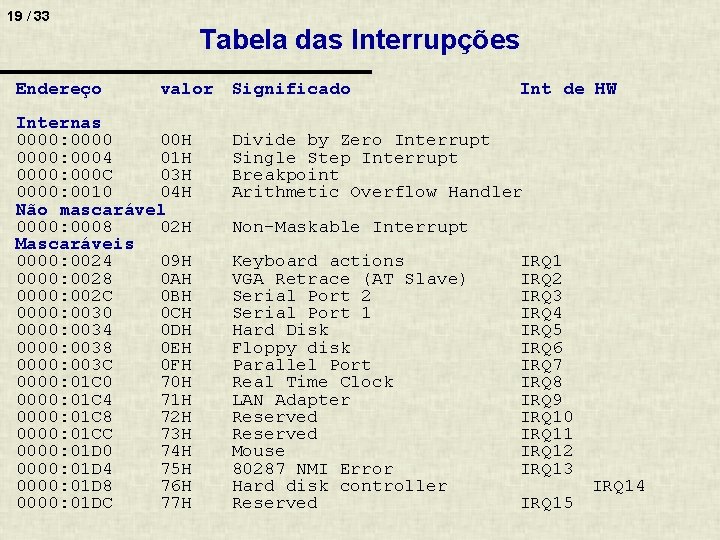

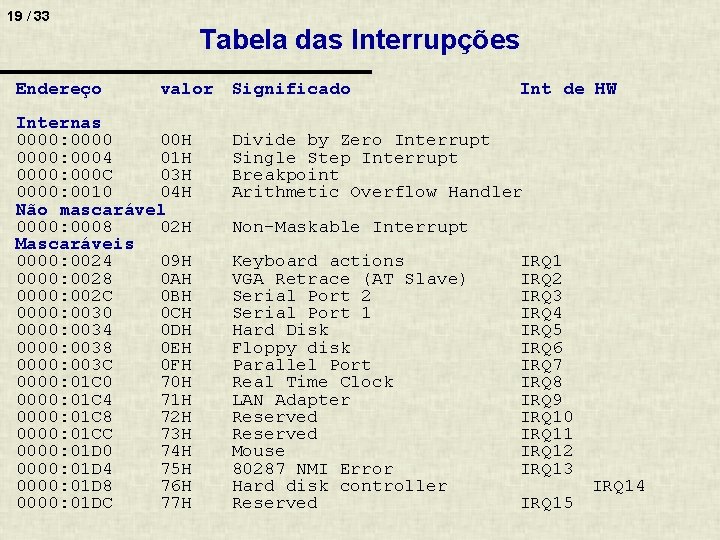

19 / 33 Endereço Tabela das Interrupções valor Significado Internas 0000: 0000 00 H 0000: 0004 01 H 0000: 000 C 03 H 0000: 0010 04 H Não mascarável 0000: 0008 02 H Mascaráveis 0000: 0024 09 H 0000: 0028 0 AH 0000: 002 C 0 BH 0000: 0030 0 CH 0000: 0034 0 DH 0000: 0038 0 EH 0000: 003 C 0 FH 0000: 01 C 0 70 H 0000: 01 C 4 71 H 0000: 01 C 8 72 H 0000: 01 CC 73 H 0000: 01 D 0 74 H 0000: 01 D 4 75 H 0000: 01 D 8 76 H 0000: 01 DC 77 H Int de HW Divide by Zero Interrupt Single Step Interrupt Breakpoint Arithmetic Overflow Handler Non-Maskable Interrupt Keyboard actions VGA Retrace (AT Slave) Serial Port 2 Serial Port 1 Hard Disk Floppy disk Parallel Port Real Time Clock LAN Adapter Reserved Mouse 80287 NMI Error Hard disk controller Reserved IRQ 1 IRQ 2 IRQ 3 IRQ 4 IRQ 5 IRQ 6 IRQ 7 IRQ 8 IRQ 9 IRQ 10 IRQ 11 IRQ 12 IRQ 13 IRQ 15 IRQ 14

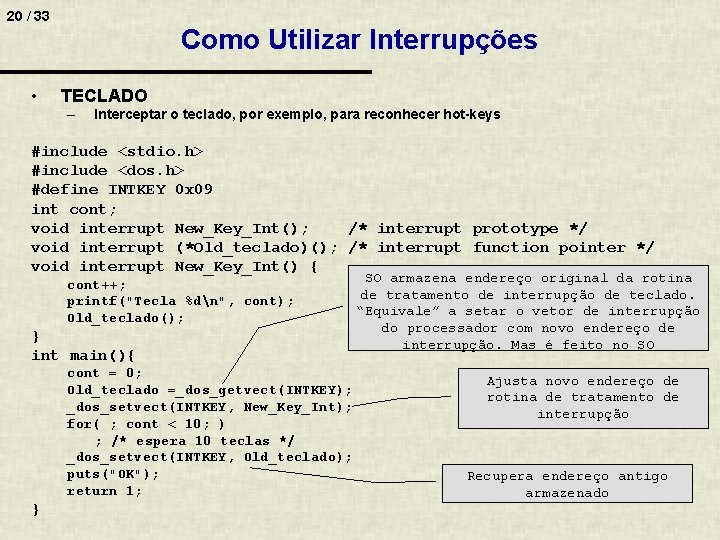

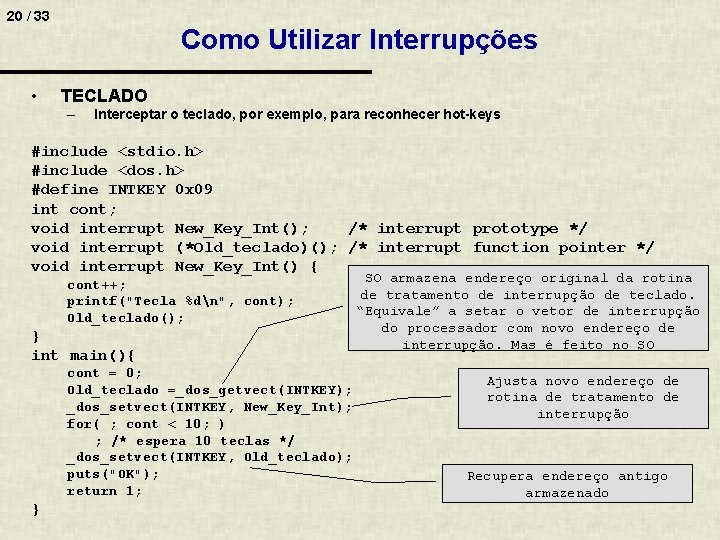

20 / 33 • Como Utilizar Interrupções TECLADO – Interceptar o teclado, por exemplo, para reconhecer hot-keys #include <stdio. h> #include <dos. h> #define INTKEY 0 x 09 int cont; void interrupt New_Key_Int(); /* interrupt prototype */ void interrupt (*Old_teclado)(); /* interrupt function pointer */ void interrupt New_Key_Int() { cont++; printf("Tecla %dn", cont); Old_teclado(); } int main(){ cont = 0; Old_teclado =_dos_getvect(INTKEY); _dos_setvect(INTKEY, New_Key_Int); for( ; cont < 10; ) ; /* espera 10 teclas */ _dos_setvect(INTKEY, Old_teclado); puts("OK"); return 1; } SO armazena endereço original da rotina de tratamento de interrupção de teclado. “Equivale” a setar o vetor de interrupção do processador com novo endereço de interrupção. Mas é feito no SO Ajusta novo endereço de rotina de tratamento de interrupção Recupera endereço antigo armazenado

21 / 33 • Como Utilizar Interrupções TECLADO – Interceptar o control break #include <stdio. h> #include <dos. h> void interrupt get_out(); void interrupt (*oldfunc)(); int looping = 1; void main() { oldfunc = _dos_getvect(5); _dos_setvect(5, get_out); while(looping); _dos_setvect(5, oldfunc); } void interrupt get_out() { looping = 0; }

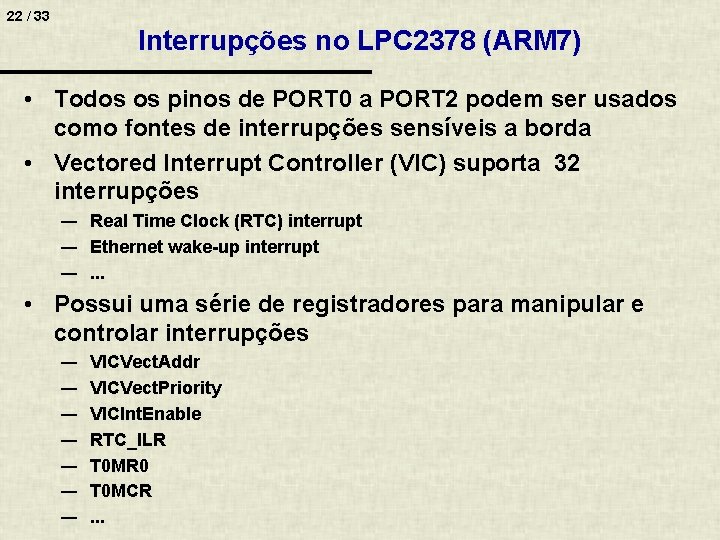

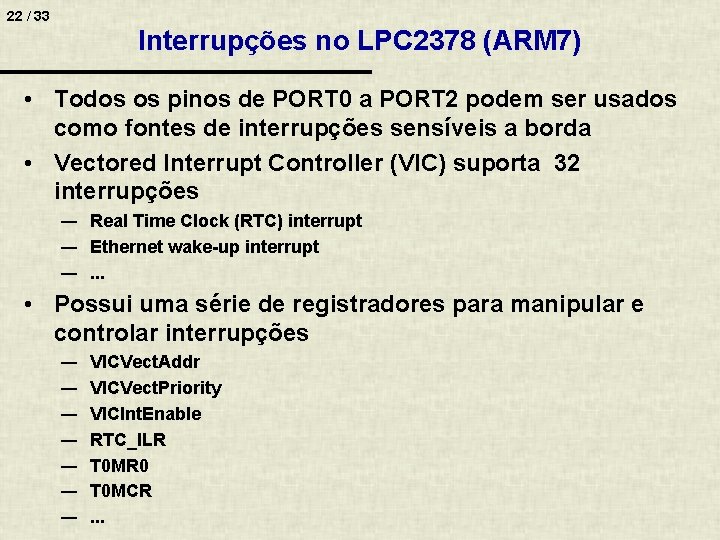

22 / 33 Interrupções no LPC 2378 (ARM 7) • Todos os pinos de PORT 0 a PORT 2 podem ser usados como fontes de interrupções sensíveis a borda • Vectored Interrupt Controller (VIC) suporta 32 interrupções ― Real Time Clock (RTC) interrupt ― Ethernet wake-up interrupt ―. . . • Possui uma série de registradores para manipular e controlar interrupções ― ― ― ― VICVect. Addr VICVect. Priority VICInt. Enable RTC_ILR T 0 MR 0 T 0 MCR. . .

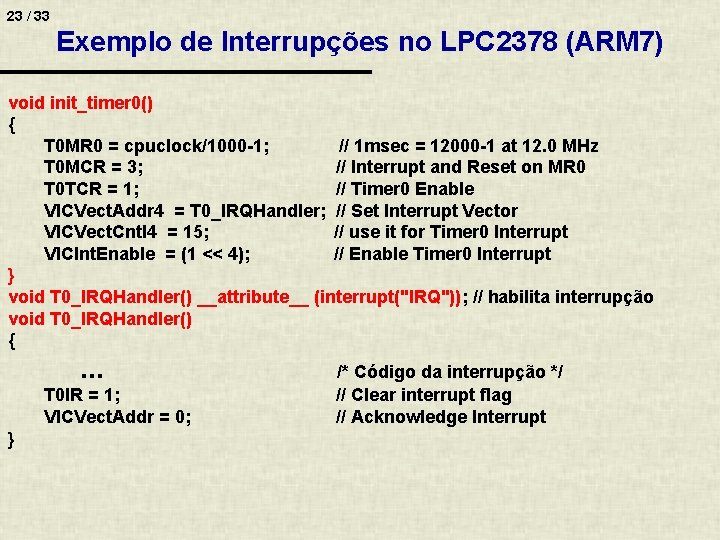

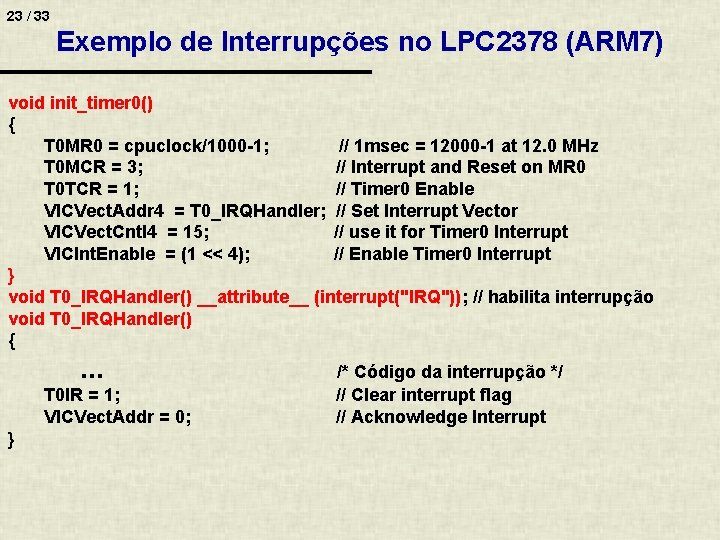

23 / 33 Exemplo de Interrupções no LPC 2378 (ARM 7) void init_timer 0() { T 0 MR 0 = cpuclock/1000 -1; // 1 msec = 12000 -1 at 12. 0 MHz T 0 MCR = 3; // Interrupt and Reset on MR 0 T 0 TCR = 1; // Timer 0 Enable VICVect. Addr 4 = T 0_IRQHandler; // Set Interrupt Vector VICVect. Cntl 4 = 15; // use it for Timer 0 Interrupt VICInt. Enable = (1 << 4); // Enable Timer 0 Interrupt } void T 0_IRQHandler() __attribute__ (interrupt("IRQ")); // habilita interrupção void T 0_IRQHandler() { . . . /* Código da interrupção */ T 0 IR = 1; // Clear interrupt flag VICVect. Addr = 0; // Acknowledge Interrupt }

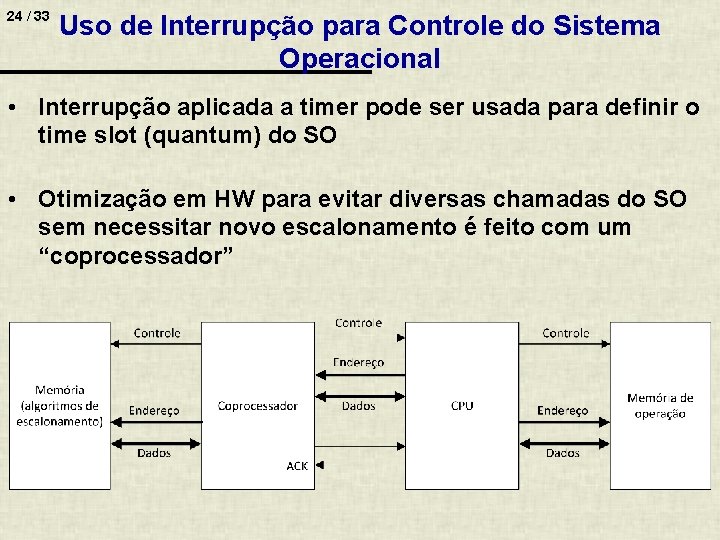

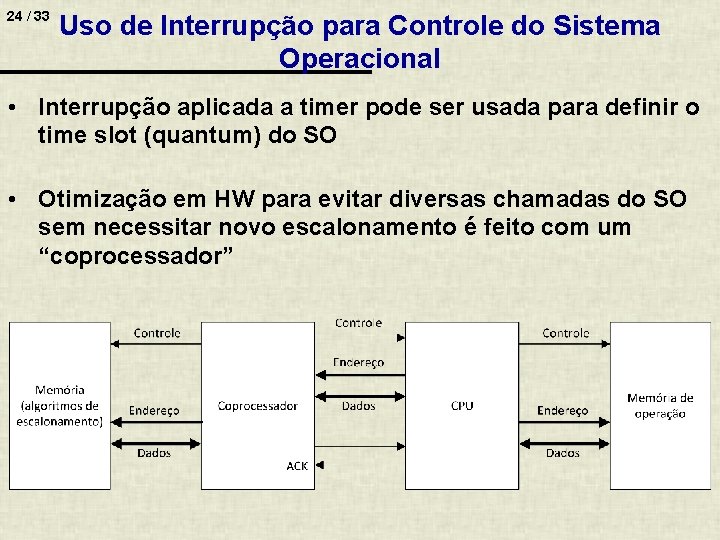

24 / 33 Uso de Interrupção para Controle do Sistema Operacional • Interrupção aplicada a timer pode ser usada para definir o time slot (quantum) do SO • Otimização em HW para evitar diversas chamadas do SO sem necessitar novo escalonamento é feito com um “coprocessador”

25 / 33 Exercícios Extras 1. Como funciona o mecanismo de mascaramento de interrupções? O que significa interrupção não mascarável? Dê um exemplo de aplicação 2. Como é realizado o mecanismo de tratamento de interrupção em um processador? Cite as principais etapas do processo, comparando com o tratamento a atendimento de chamada à sub-rotina 3. Mostre como é feito o tratamento de interrupções de hardware nos computadores baseados em processadores 80 x 86 4. Dado um programa que trata uma comunicação através de interrupção, pede -se: – – O que pode acontecer se o programa foi escrito sem análise de poder ser interrompido em qualquer trecho? Mostre como poderia ser impedida a interrupção de entrar em qualquer ponto do código Qual o mecanismo adotado em hardware para que o procedimento acima seja atendido? Mostre como poderiam ser implementadas rotinas de leitura e escrita serial através de interrupção que não necessite de trechos de código atômicos. A explicação deve salientar os buffers e ponteiros

26 / 33 Exercícios Extras 5. Comparar qual modo de comunicação tem melhor resultado para o problema descrito a seguir. A comparação deve elucidar problemas de complexidade de elaboração do programa, tratamento e verificação de erros e tempo de processamento – – – – – A execução do programa é efetuada em laços que requerem em média 2. 100 ciclos, não considerando trechos de código necessários para teste de polling ou interjeição Existem 4 periféricos que devem ser avaliados Considere que o teste de polling é efetuado duas vezes a cada laço de programa Os testes para verificar se algum dispositivo deseja se comunicar, seja por polling ou interjeição, consome 20 ciclos As rotinas de execução do polling consomem 80 ciclos quando o teste de polling retorna verdadeiro A rotina de interjeição, para verificar qual dispositivo deseja se comunicar, consome 200 ciclos O tratamento da rotina de interrupção consome para qualquer dispositivo 800 ciclos, em média Devido às características do programa são necessários 30 pontos atômicos no código. Ou seja, devem ser inseridas funções que impossibilitem a entrada de interrupção em 30 pontos do programa As rotinas que mantém o código atômico consomem 50 ciclos 6. Altere os dados do programa acima de forma a obter melhores resultados para os dois outros métodos com relação ao tempo de processamento

27 / 33 Exercícios 7. (ENADE 2005) Processadores atuais incluem mecanismos para o tratamento de situações especiais, conhecidas como interrupções. Em uma interrupção, o fluxo normal de instruções é interrompido para que a causa da interrupção seja tratada. Com relação a esse assunto, assinale a opção correta: a. Controladores de entrada e saída geram interrupções de forma síncrona à execução do processador, para que nenhuma instrução fique incompleta devido à ocorrência da interrupção b. Quando uma interrupção ocorre, o próprio processador salva todo o seu contexto atual, tais como registradores de dados e endereço e códigos de condição, para que esse mesmo contexto possa ser restaurado pela rotina de atendimento da interrupção c. O processador pode auto interromper-se para tratar exceções de execução, tais como um erro em uma operação aritmética, uma tentativa de execução de instrução ilegal ou uma falha de página em memória virtual d. Rotinas de tratamento de interrupção devem ser executadas com o mecanismo de interrupção inibido, pois esse tipo de rotina não permite aninhamento e. O uso de interrupção para realizar entrada ou saída de dados somente é eficiente quando o periférico trata grandes quantidades de dados, como é o caso de discos magnéticos e discos ópticos. Para periféricos com pouco volume de dados, como teclados e mouses, o uso de interrupção é ineficiente

28 / 33 Exercícios 7. Comentários sobre a questão (ENADE 2005): a. Controladores de entrada e saída geram interrupções de forma síncrona à execução do processador, para que nenhuma instrução fique incompleta devido à ocorrência da interrupção Resposta errada. Não há sincronismo. Os sistemas (controlador e processador) são essencialmente assíncronos b. Quando uma interrupção ocorre, o próprio processador salva todo o seu contexto atual, tais como registradores de dados e endereço e códigos de condição, para que esse mesmo contexto possa ser restaurado pela rotina de atendimento da interrupção Resposta dúbia. Depende do que se entende pela expressão “o próprio processador”, que pode se referir tão somente às ações de salvamento de contexto definidas na própria arquitetura ou aquelas que o software básico do sistema decidiu serem necessárias ao atender interrupções. O processador pode salvar parte do contexto, e parte deste ser salvo por software do sistemas, dependendo do tipo de mecanismo escolhido. A recuperação do contexto pode ser feita ao término do rotina de atendimento de interrupção, com recuperação de contexto ou após retornar desta, de forma automática pelo próprio processador c. O processador pode auto-interromper-se para tratar exceções de execução, tais como um erro em uma operação aritmética, uma tentativa de execução de instrução ilegal ou uma falha de página em memória virtual Resposta certa. Este mecanismo é implementado na quase totalidade dos processadores comerciais no que às vezes se denomina interrupções de software e/ou chamadas do sistema d. Rotinas de tratamento de interrupção devem ser executadas com o mecanismo de interrupção inibido, pois esse tipo de rotina não permite aninhamento Resposta errada. O erro se deve ao uso da palavra devem. Dependendo da arquitetura do processador não é permitido o aninhamento de interrupções. Este é o caso típico de tratamento de interrupções rápidas que somente tem um banco de registradores espelho. Porém, muitos processadores permitem aninhamento de interrupções e. O uso de interrupção para realizar entrada ou saída de dados somente é eficiente quando o periférico trata grandes quantidades de dados, como é o caso de discos magnéticos e discos ópticos. Para periféricos com pouco volume de dados, como teclados e mouses, o uso de interrupção é ineficiente Resposta errada. O que pode ser considerado errada é dizer que interrupção é somente eficiente se tratar de transferência com grande quantidade de dados. Além do mais, depende do que vem a ser a definição de eficiência. No contexto desta questão, a eficiência parece ter a ver apenas com a velocidade de execução do programa. Aqui não são levadas em consideração questões como código necessário, consumo de energia, etc

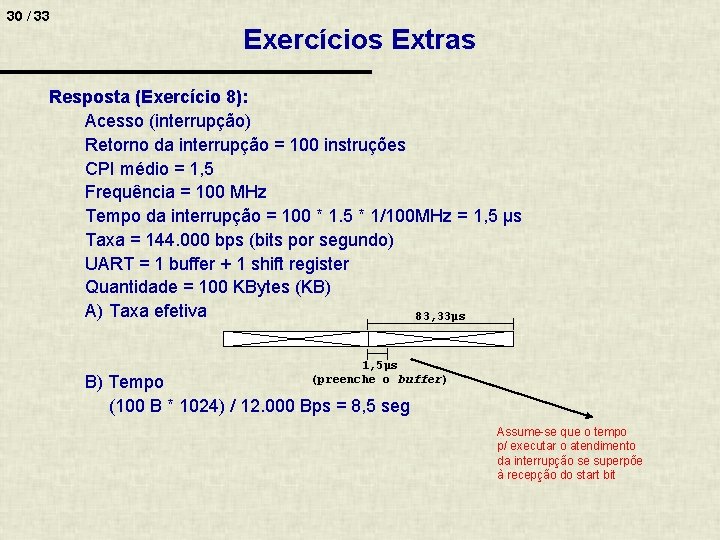

29 / 33 Exercícios Extras 8. Considere um sistema embarcado onde o acesso do processador ao dispositivo de entrada/saída é controlado por interrupção. Assuma que a execução da rotina de tratamento de interrupção consome em média 100 instruções, e que o processador tem CPI médio 1, 5 e emprega um relógio de 100 MHZ. Para uma comunicação assíncrona P 82 (paridade par, 8 bits de dados e dois stop bits além do start bit), com 144. 000 bps e uma UART com um registrador de buffer e um de deslocamento, calcule: – – Qual a taxa máxima de transmissão ideal? Qual a taxa efetiva de transmissão? Qual o tempo necessário para transmitir 100 Kbytes para cada caso acima? Faça um esboço para ilustrar os instantes de tempo onde ocorre transmissão do dado, a comunicação CPU com dispositivo de E/S, e o tempo em que o processador está em atividades interrupção

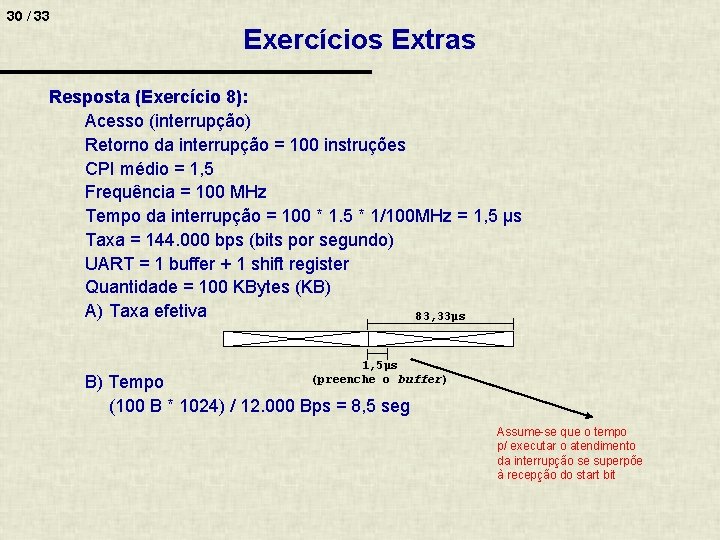

30 / 33 Exercícios Extras Resposta (Exercício 8): Acesso (interrupção) Retorno da interrupção = 100 instruções CPI médio = 1, 5 Frequência = 100 MHz Tempo da interrupção = 100 * 1. 5 * 1/100 MHz = 1, 5 µs Taxa = 144. 000 bps (bits por segundo) UART = 1 buffer + 1 shift register Quantidade = 100 KBytes (KB) A) Taxa efetiva 83, 33µs 1, 5µs (preenche o buffer) B) Tempo (100 B * 1024) / 12. 000 Bps = 8, 5 seg Assume-se que o tempo p/ executar o atendimento da interrupção se superpõe à recepção do start bit

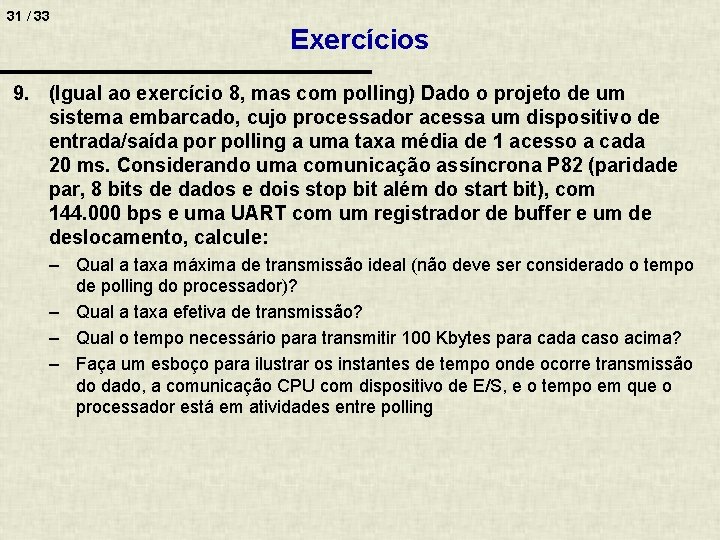

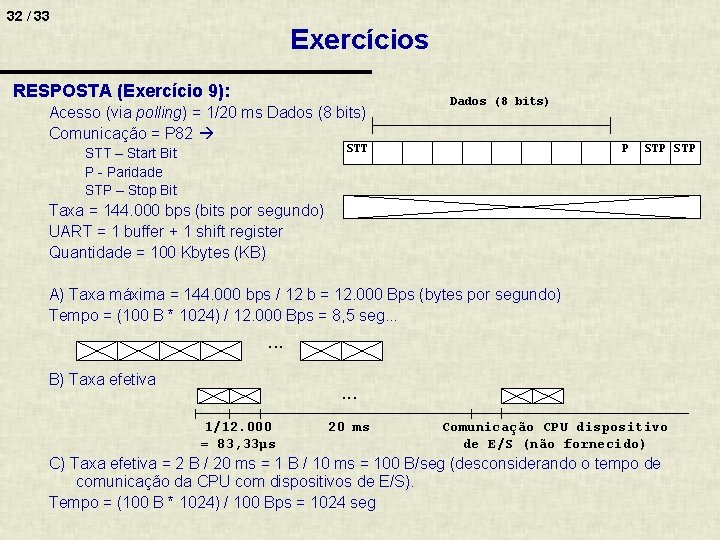

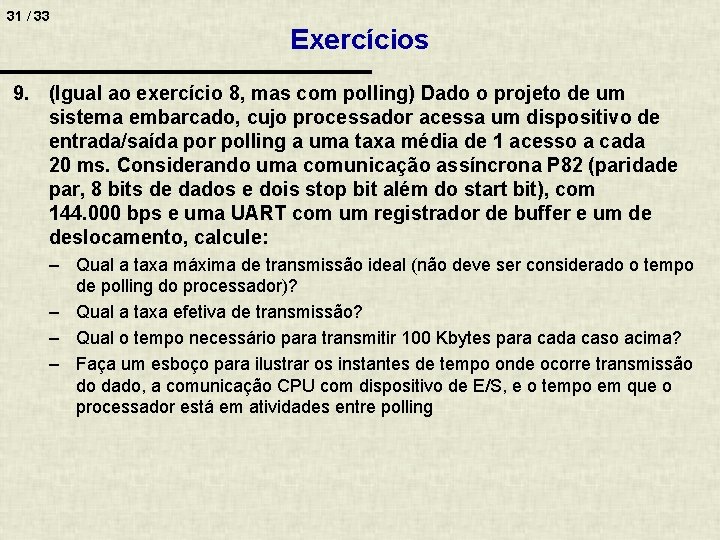

31 / 33 Exercícios 9. (Igual ao exercício 8, mas com polling) Dado o projeto de um sistema embarcado, cujo processador acessa um dispositivo de entrada/saída por polling a uma taxa média de 1 acesso a cada 20 ms. Considerando uma comunicação assíncrona P 82 (paridade par, 8 bits de dados e dois stop bit além do start bit), com 144. 000 bps e uma UART com um registrador de buffer e um de deslocamento, calcule: – Qual a taxa máxima de transmissão ideal (não deve ser considerado o tempo de polling do processador)? – Qual a taxa efetiva de transmissão? – Qual o tempo necessário para transmitir 100 Kbytes para cada caso acima? – Faça um esboço para ilustrar os instantes de tempo onde ocorre transmissão do dado, a comunicação CPU com dispositivo de E/S, e o tempo em que o processador está em atividades entre polling

32 / 33 Exercícios RESPOSTA (Exercício 9): Acesso (via polling) = 1/20 ms Dados (8 bits) Comunicação = P 82 Dados (8 bits) STT – Start Bit P - Paridade STP – Stop Bit P STP Taxa = 144. 000 bps (bits por segundo) UART = 1 buffer + 1 shift register Quantidade = 100 Kbytes (KB) A) Taxa máxima = 144. 000 bps / 12 b = 12. 000 Bps (bytes por segundo) Tempo = (100 B * 1024) / 12. 000 Bps = 8, 5 seg. . . B) Taxa efetiva . . . 1/12. 000 = 83, 33µs 20 ms Comunicação CPU dispositivo de E/S (não fornecido) C) Taxa efetiva = 2 B / 20 ms = 1 B / 10 ms = 100 B/seg (desconsiderando o tempo de comunicação da CPU com dispositivos de E/S). Tempo = (100 B * 1024) / 100 Bps = 1024 seg

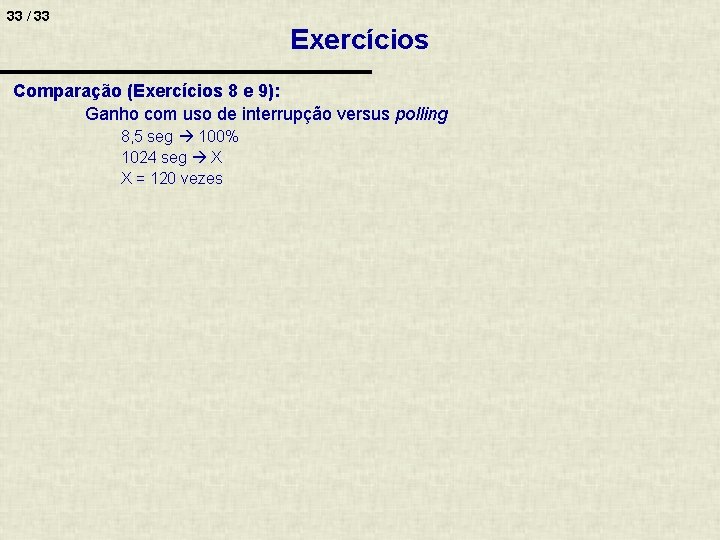

33 / 33 Exercícios Comparação (Exercícios 8 e 9): Ganho com uso de interrupção versus polling 8, 5 seg 100% 1024 seg X X = 120 vezes

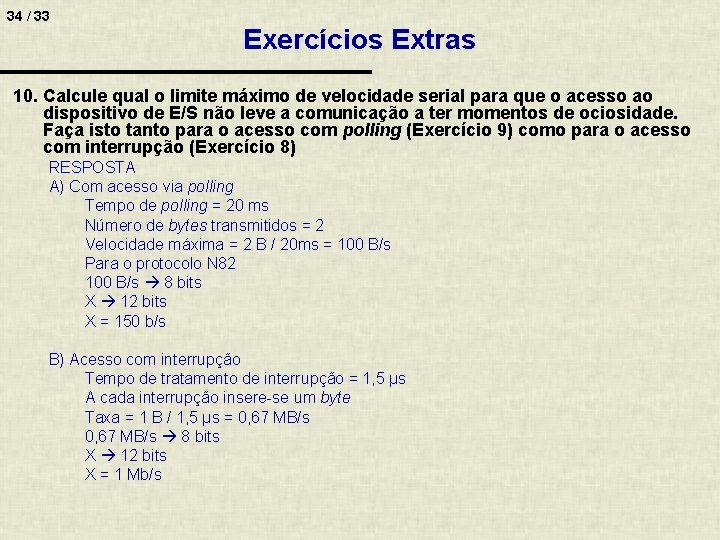

34 / 33 Exercícios Extras 10. Calcule qual o limite máximo de velocidade serial para que o acesso ao dispositivo de E/S não leve a comunicação a ter momentos de ociosidade. Faça isto tanto para o acesso com polling (Exercício 9) como para o acesso com interrupção (Exercício 8) RESPOSTA A) Com acesso via polling Tempo de polling = 20 ms Número de bytes transmitidos = 2 Velocidade máxima = 2 B / 20 ms = 100 B/s Para o protocolo N 82 100 B/s 8 bits X 12 bits X = 150 b/s B) Acesso com interrupção Tempo de tratamento de interrupção = 1, 5 µs A cada interrupção insere-se um byte Taxa = 1 B / 1, 5 µs = 0, 67 MB/s 8 bits X 12 bits X = 1 Mb/s