Organizao e Arquitetura de Computadores II Aula Inaugural

- Slides: 39

Organização e Arquitetura de Computadores II Aula Inaugural Última alteração: 02/08/2017 Prof. Ney Laert Vilar Calazans Baseado em notas de aulas originais do Prof. Dr. César Marcon

2 / 38 Apresentação • Disciplina: Organização e Arquitetura de Computadores II • Horário: 2 CD e 4 CD • Carga horária: > 60 horas • Professor: Ney Laert Vilar Calazans • Email: ney. calazans@pucrs. br • Material: – Homepage: http: //www. inf. pucrs. br/calazans/undergrad/orgarqcomp. II_CC/ – Moodle

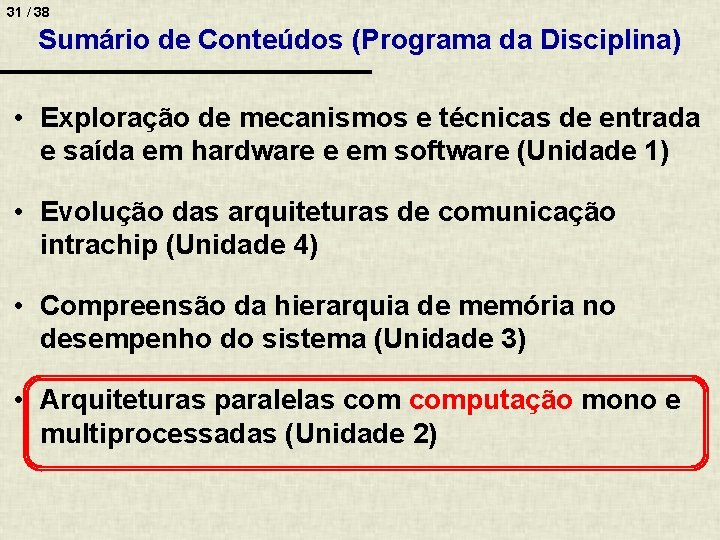

3 / 38 Sumário de Conteúdos (Programa da Disciplina) • Exploração de mecanismos e técnicas de entrada e saída em hardware e em software (Unidade 1) • Evolução das arquiteturas de comunicação intrachip (Unidade 4) • Compreensão da hierarquia de memória no desempenho do sistema (Unidade 3) • Arquiteturas paralelas computação mono e multiprocessadas (Unidade 2)

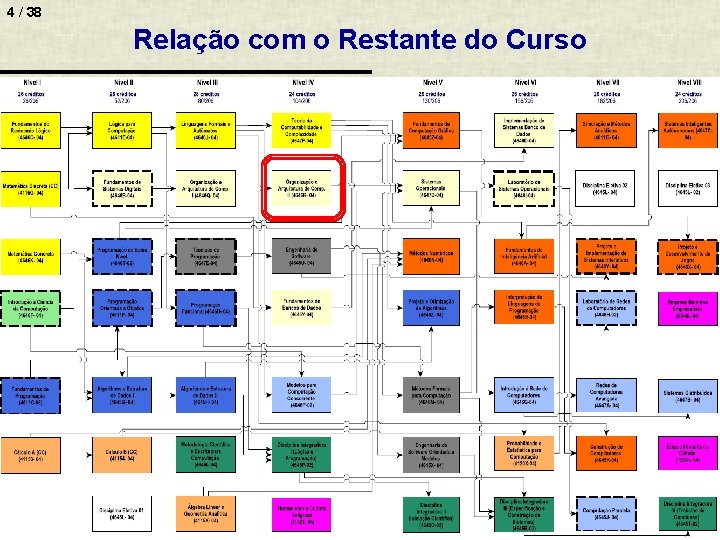

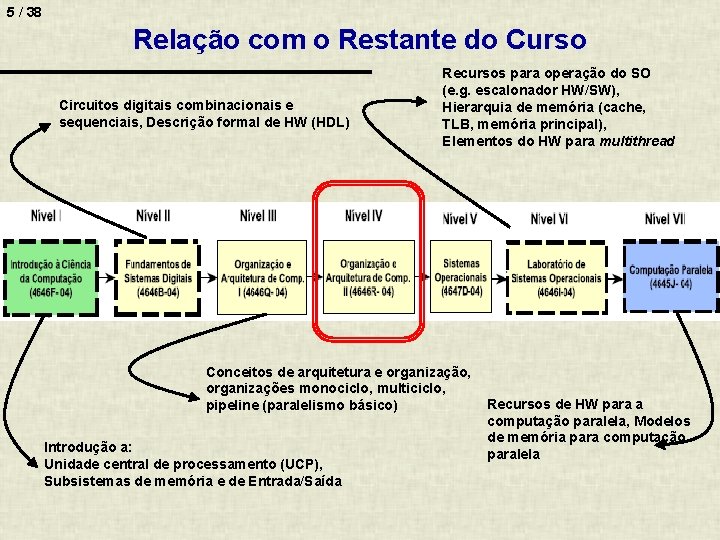

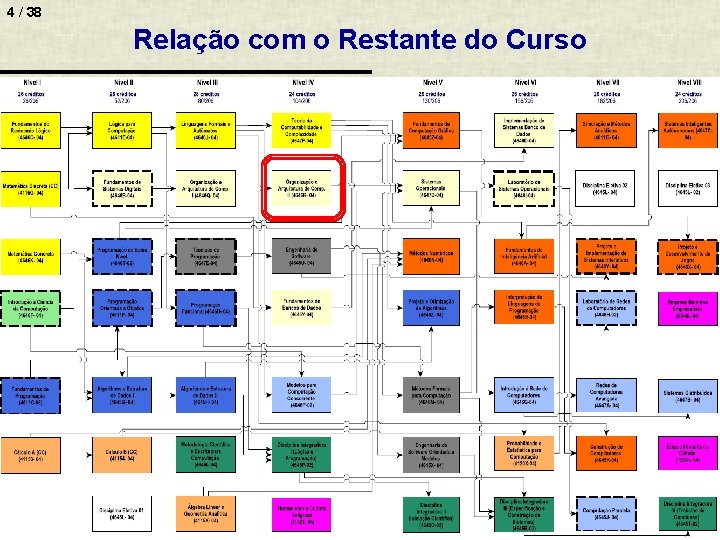

4 / 38 Relação com o Restante do Curso

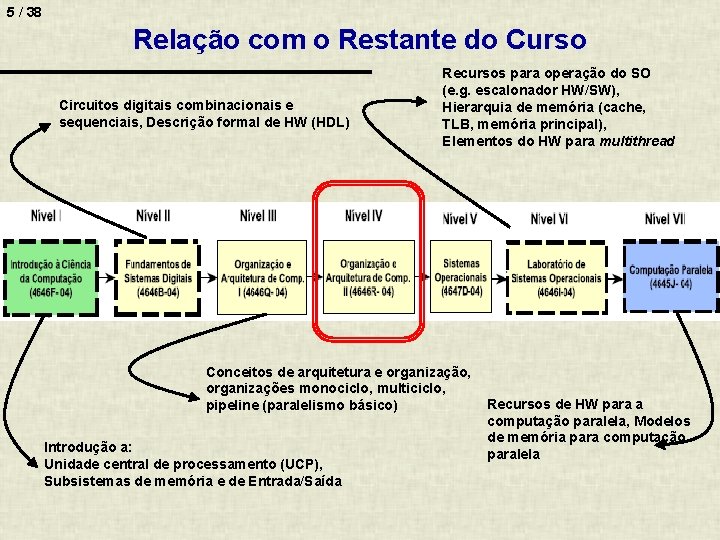

5 / 38 Relação com o Restante do Curso Circuitos digitais combinacionais e sequenciais, Descrição formal de HW (HDL) Recursos para operação do SO (e. g. escalonador HW/SW), Hierarquia de memória (cache, TLB, memória principal), Elementos do HW para multithread Conceitos de arquitetura e organização, organizações monociclo, multiciclo, pipeline (paralelismo básico) Introdução a: Unidade central de processamento (UCP), Subsistemas de memória e de Entrada/Saída Recursos de HW para a computação paralela, Modelos de memória para computação paralela

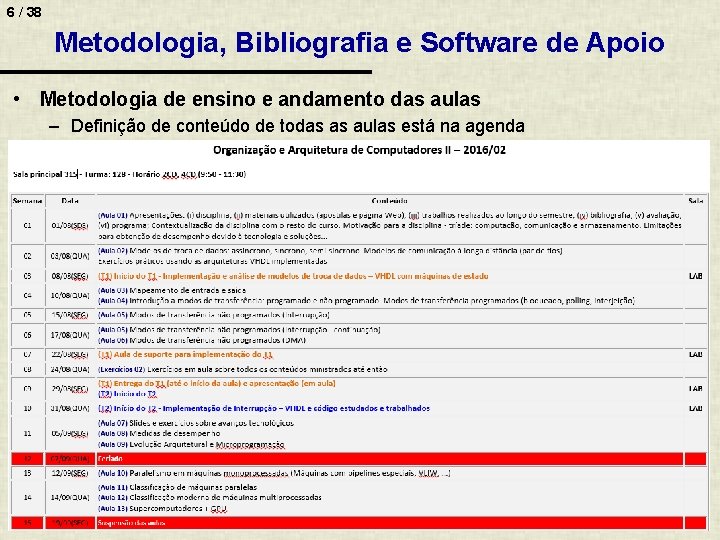

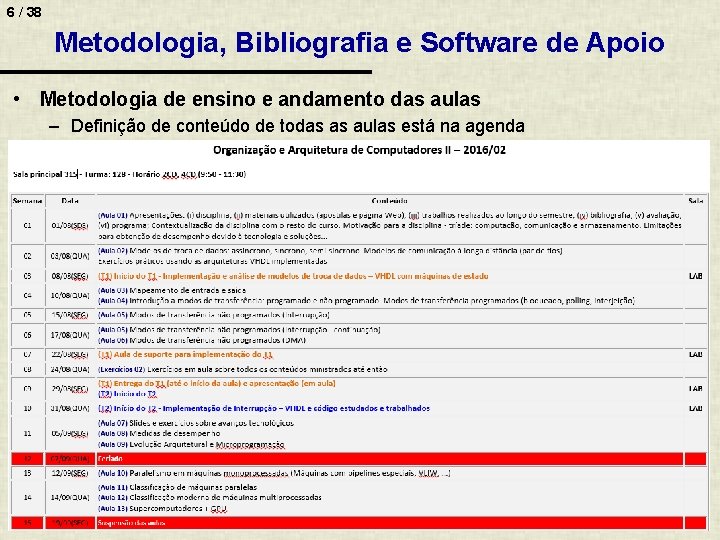

6 / 38 Metodologia, Bibliografia e Software de Apoio • Metodologia de ensino e andamento das aulas – Definição de conteúdo de todas as aulas está na agenda – Conteúdo • Reduzido nos slides da disciplina (referência para a bibliografia) • Estendido nos livros da bibliografia básica e auxiliar – Aulas práticas – Interação professor/aluno, aluno/aluno • Básica – W. Stallings, Arquitetura e organização de computadores, 2010 – J. -L. Baer, Arquitetura de Microprocessadores – do Simples Pipeline ao Multiprocessador em Chip, 2013 – J. Henessy, D. Patterson, Arquitetura de computadores: uma abordagem quantitativa, 2014 • Software de Apoio – ISE (Ferramenta para síntese e simulação funcional para HDL)

7 / 38 Metodologia, Bibliografia e Software de Apoio • Metodologia de ensino e andamento das aulas – Definição de conteúdo de todas as aulas está na agenda – Conteúdo • Reduzido nos slides da disciplina (referência para a bibliografia) • Estendido nos livros da bibliografia básica e auxiliar – Aulas práticas – Interação professor/aluno, aluno/aluno • Básica – W. Stallings, Arquitetura e organização de computadores, 2010 – J. -L. Baer, Arquitetura de Microprocessadores – do Simples Pipeline ao Multiprocessador em Chip, 2013 – J. Hennessy, D. Patterson, Arquitetura de computadores: uma abordagem quantitativa, 2014 • Software de Apoio – ISE (Ferramenta para síntese e simulação funcional para HDL)

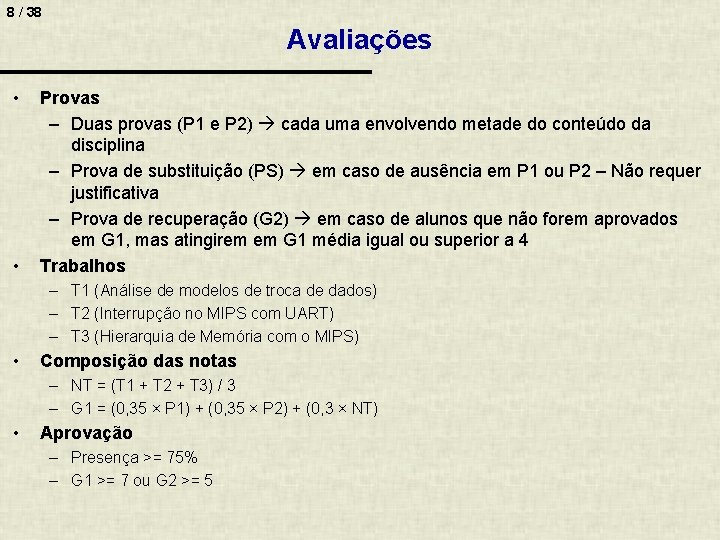

8 / 38 Avaliações • • Provas – Duas provas (P 1 e P 2) cada uma envolvendo metade do conteúdo da disciplina – Prova de substituição (PS) em caso de ausência em P 1 ou P 2 – Não requer justificativa – Prova de recuperação (G 2) em caso de alunos que não forem aprovados em G 1, mas atingirem em G 1 média igual ou superior a 4 Trabalhos – T 1 (Análise de modelos de troca de dados) – T 2 (Interrupção no MIPS com UART) – T 3 (Hierarquia de Memória com o MIPS) • Composição das notas – NT = (T 1 + T 2 + T 3) / 3 – G 1 = (0, 35 × P 1) + (0, 35 × P 2) + (0, 3 × NT) • Aprovação – Presença >= 75% – G 1 >= 7 ou G 2 >= 5

9 / 38 Sumário de Conteúdos (Programa da Disciplina) • Exploração de mecanismos e técnicas de entrada e saída em hardware e em software (Unidade 1) • Evolução das arquiteturas de comunicação intrachip (Unidade 4) • Compreensão da hierarquia de memória no desempenho do sistema (Unidade 3) • Arquiteturas paralelas computação mono e multiprocessadas (Unidade 2)

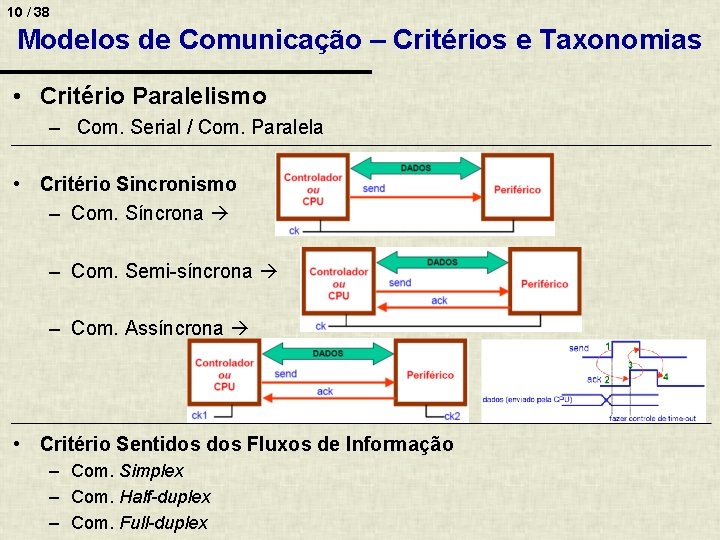

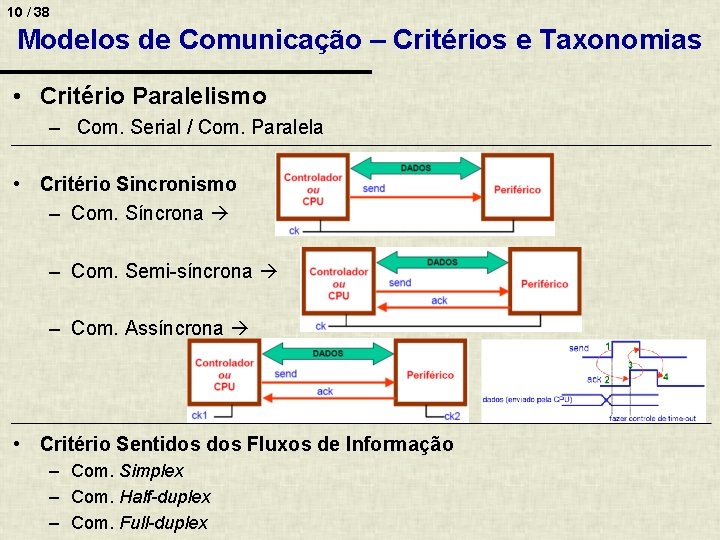

10 / 38 Modelos de Comunicação – Critérios e Taxonomias • Critério Paralelismo – Com. Serial / Com. Paralela • Critério Sincronismo – Com. Síncrona – Com. Semi-síncrona – Com. Assíncrona • Critério Sentidos Fluxos de Informação – Com. Simplex – Com. Half-duplex – Com. Full-duplex

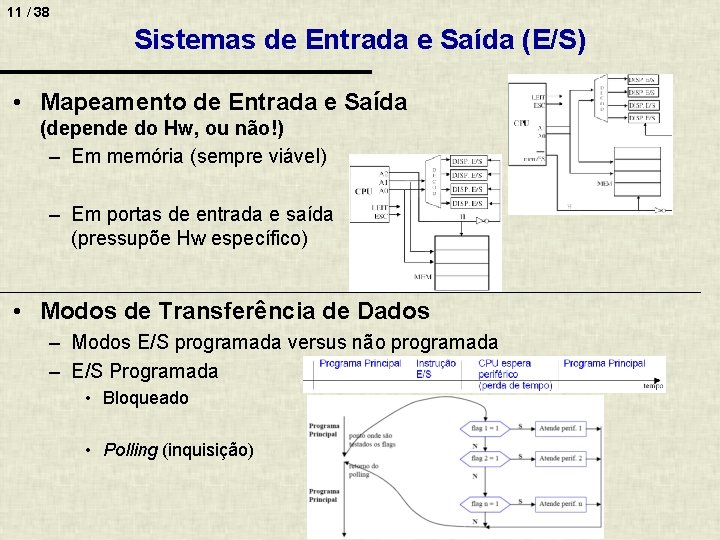

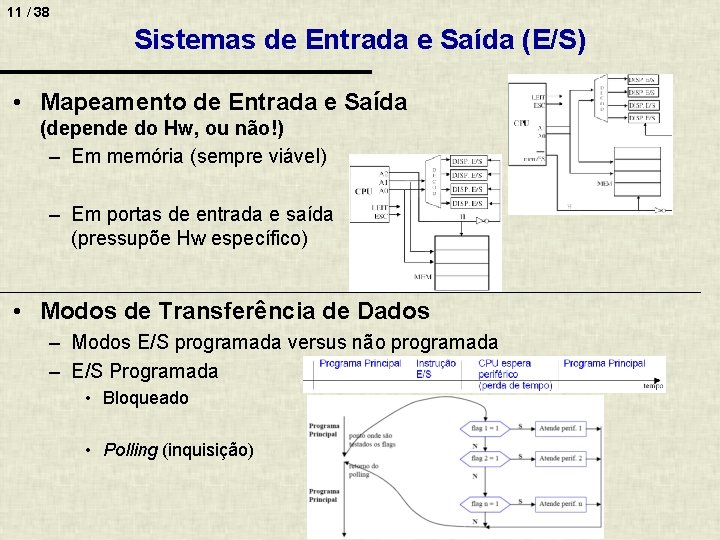

11 / 38 Sistemas de Entrada e Saída (E/S) • Mapeamento de Entrada e Saída (depende do Hw, ou não!) – Em memória (sempre viável) – Em portas de entrada e saída (pressupõe Hw específico) • Modos de Transferência de Dados – Modos E/S programada versus não programada – E/S Programada • Bloqueado • Polling (inquisição)

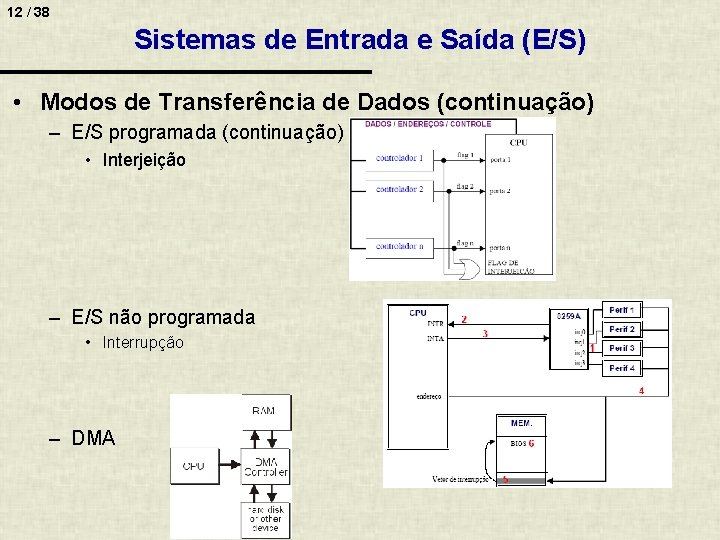

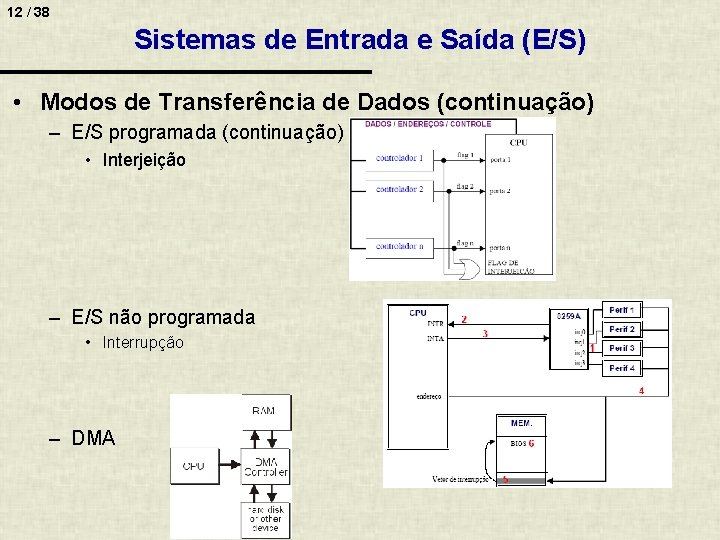

12 / 38 Sistemas de Entrada e Saída (E/S) • Modos de Transferência de Dados (continuação) – E/S programada (continuação) • Interjeição – E/S não programada • Interrupção – DMA

13 / 38 Sumário de Conteúdos (Programa da Disciplina) • Exploração de mecanismos e técnicas de entrada e saída em hardware e em software (Unidade 1) • Evolução das arquiteturas de comunicação intrachip (Unidade 4) • Compreensão da hierarquia de memória no desempenho do sistema (Unidade 3) • Arquiteturas paralelas computação mono e multiprocessadas (Unidade 2)

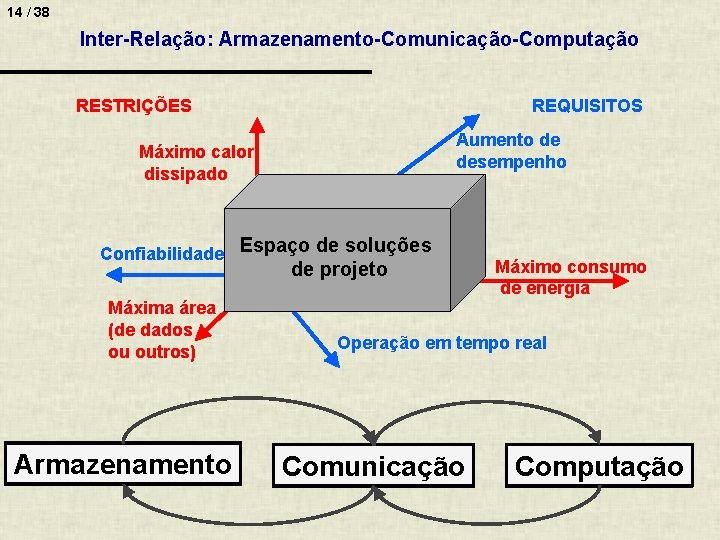

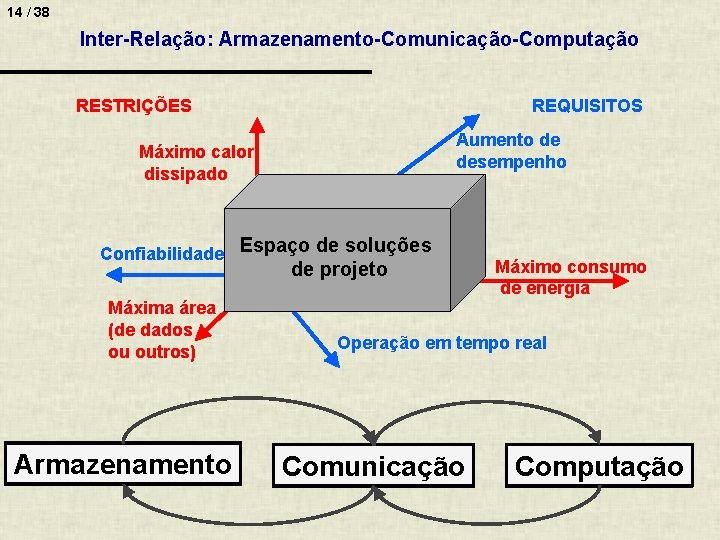

14 / 38 Inter-Relação: Armazenamento-Comunicação-Computação REQUISITOS RESTRIÇÕES Aumento de desempenho Máximo calor dissipado Confiabilidade Espaço de soluções de projeto Máxima área (de dados ou outros) Armazenamento Máximo consumo de energia Operação em tempo real Comunicação Computação

15 / 38 Sumário de Conteúdos (Programa da Disciplina) • Exploração de mecanismos e técnicas de entrada e saída em hardware e em software (Unidade 1) • Evolução das arquiteturas de comunicação intrachip (Unidade 4) • Compreensão da hierarquia de memória no desempenho do sistema (Unidade 3) • Arquiteturas paralelas computação mono e multiprocessadas (Unidade 2)

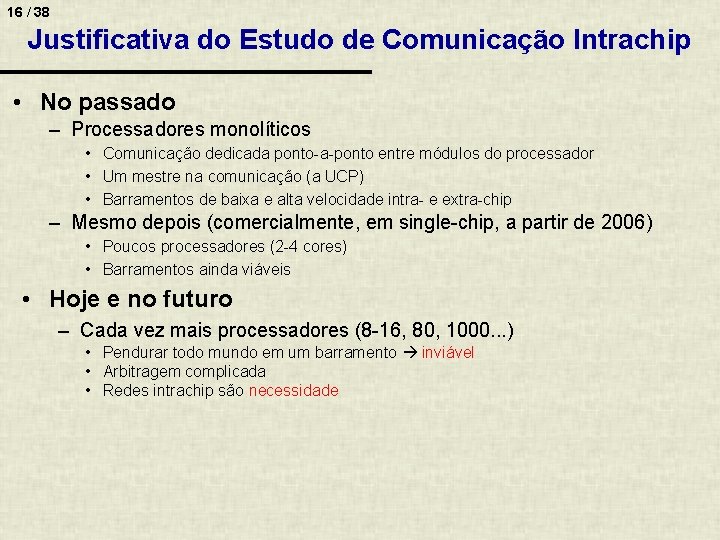

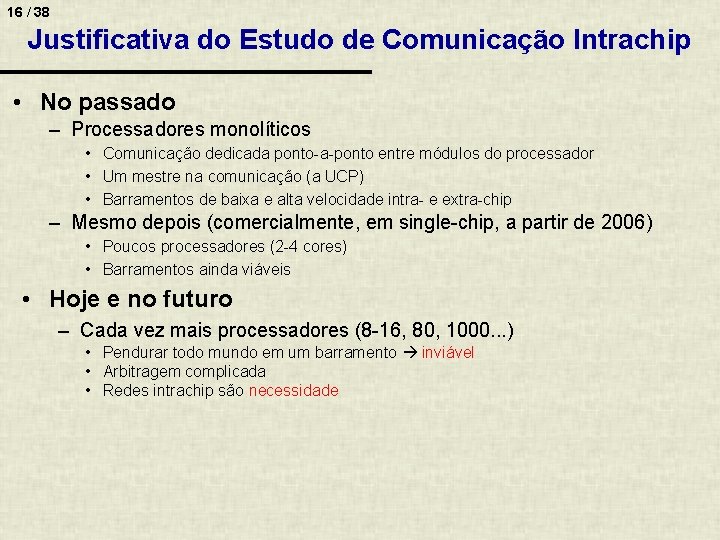

16 / 38 Justificativa do Estudo de Comunicação Intrachip • No passado – Processadores monolíticos • Comunicação dedicada ponto-a-ponto entre módulos do processador • Um mestre na comunicação (a UCP) • Barramentos de baixa e alta velocidade intra- e extra-chip – Mesmo depois (comercialmente, em single-chip, a partir de 2006) • Poucos processadores (2 -4 cores) • Barramentos ainda viáveis • Hoje e no futuro – Cada vez mais processadores (8 -16, 80, 1000. . . ) • Pendurar todo mundo em um barramento inviável • Arbitragem complicada • Redes intrachip são necessidade

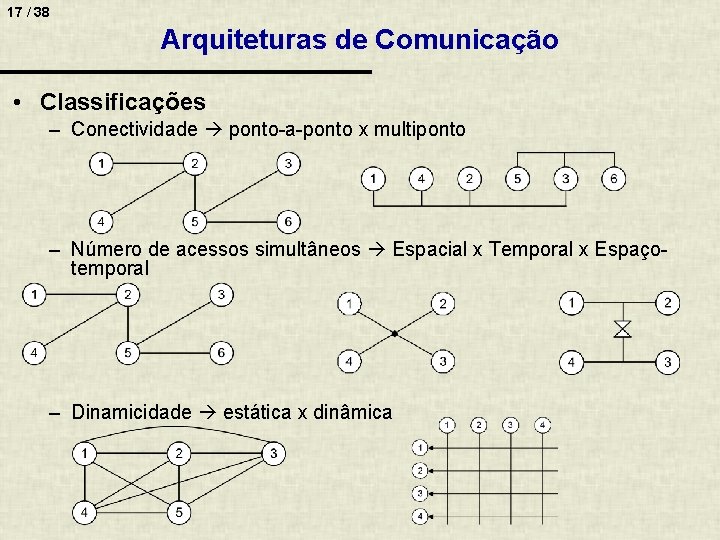

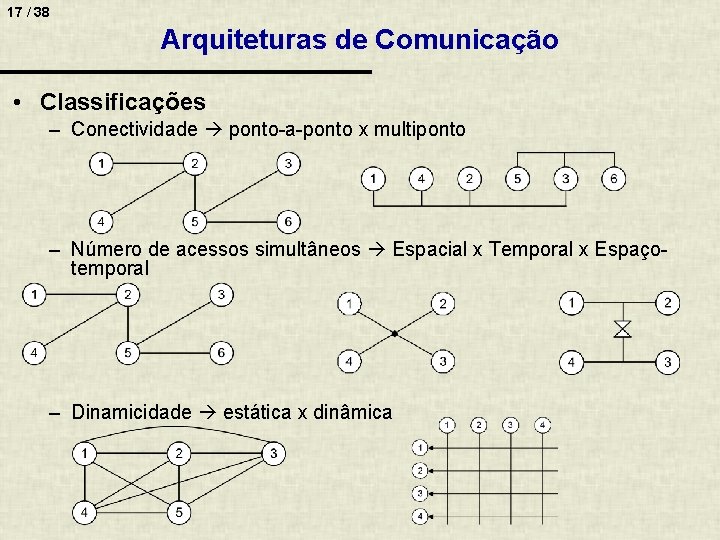

17 / 38 Arquiteturas de Comunicação • Classificações – Conectividade ponto-a-ponto x multiponto – Número de acessos simultâneos Espacial x Temporal x Espaçotemporal – Dinamicidade estática x dinâmica

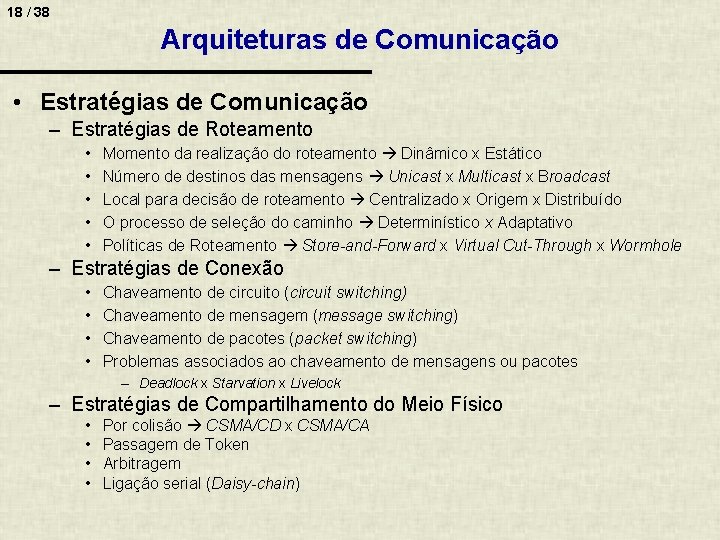

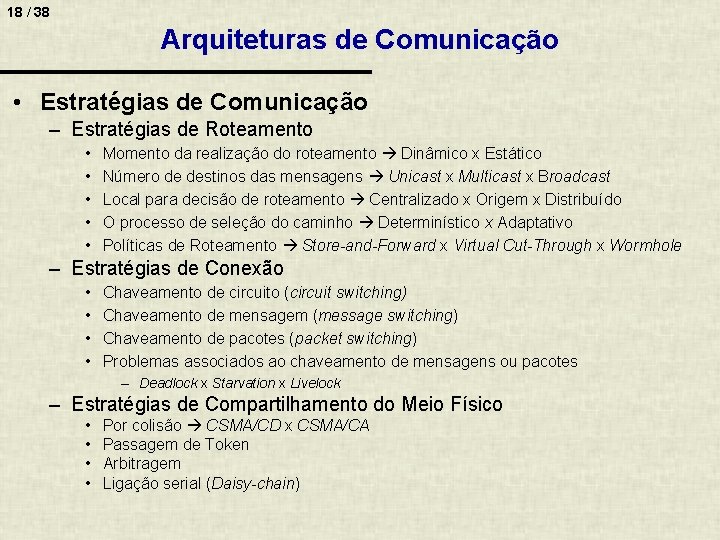

18 / 38 Arquiteturas de Comunicação • Estratégias de Comunicação – Estratégias de Roteamento • • • Momento da realização do roteamento Dinâmico x Estático Número de destinos das mensagens Unicast x Multicast x Broadcast Local para decisão de roteamento Centralizado x Origem x Distribuído O processo de seleção do caminho Determinístico x Adaptativo Políticas de Roteamento Store-and-Forward x Virtual Cut-Through x Wormhole – Estratégias de Conexão • • Chaveamento de circuito (circuit switching) Chaveamento de mensagem (message switching) Chaveamento de pacotes (packet switching) Problemas associados ao chaveamento de mensagens ou pacotes – Deadlock x Starvation x Livelock – Estratégias de Compartilhamento do Meio Físico • • Por colisão CSMA/CD x CSMA/CA Passagem de Token Arbitragem Ligação serial (Daisy-chain)

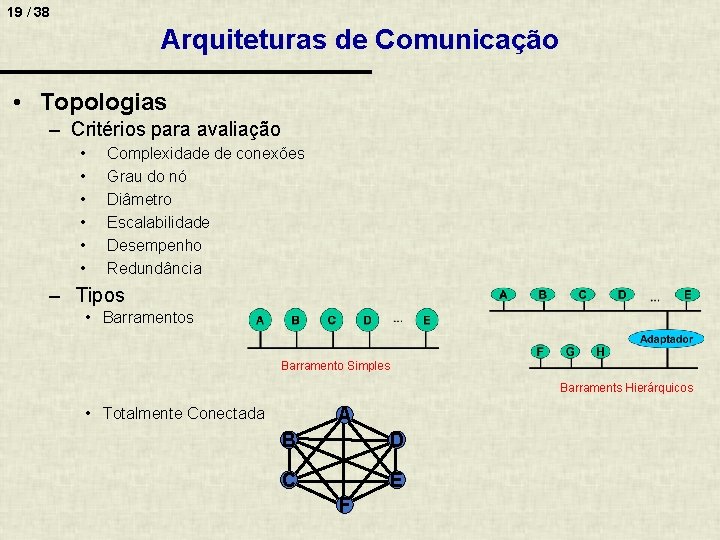

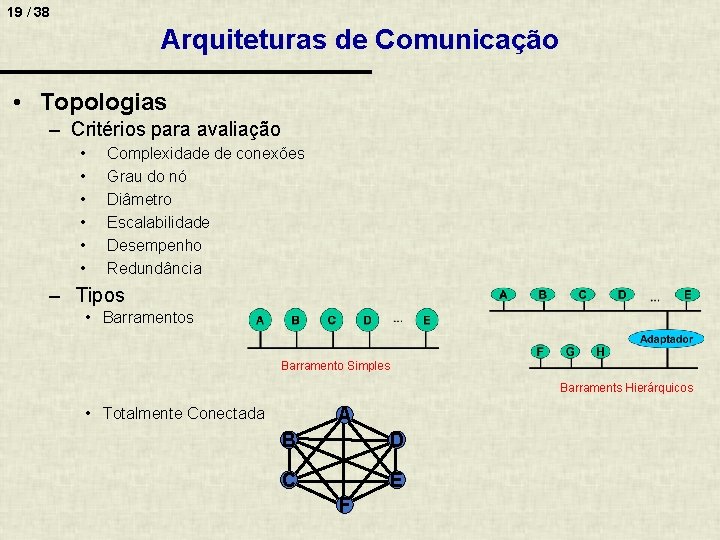

19 / 38 Arquiteturas de Comunicação • Topologias – Critérios para avaliação • • • Complexidade de conexões Grau do nó Diâmetro Escalabilidade Desempenho Redundância – Tipos • Barramentos Barramento Simples Barraments Hierárquicos • Totalmente Conectada A B D C E F

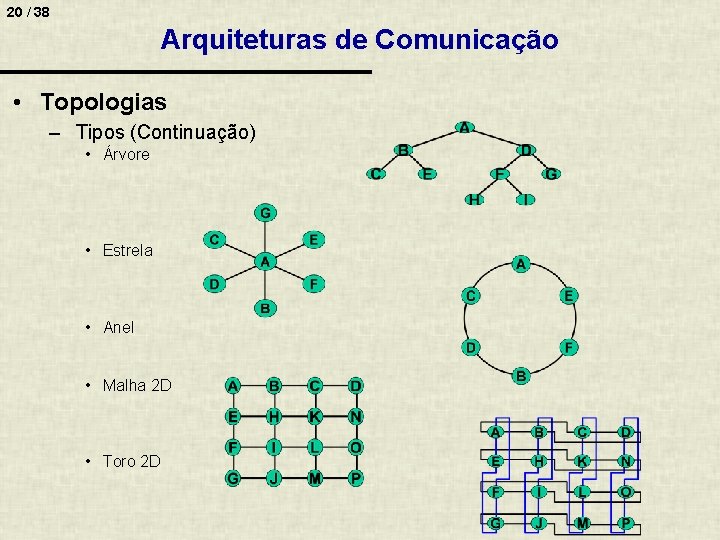

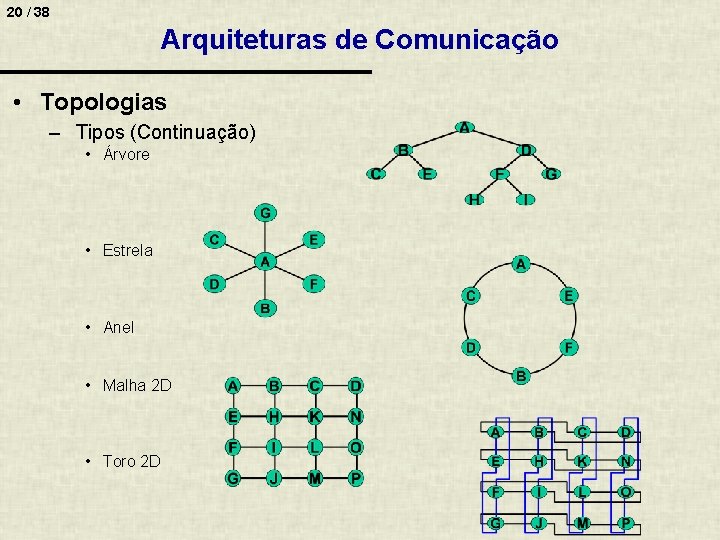

20 / 38 Arquiteturas de Comunicação • Topologias – Tipos (Continuação) • Árvore • Estrela • Anel • Malha 2 D • Toro 2 D

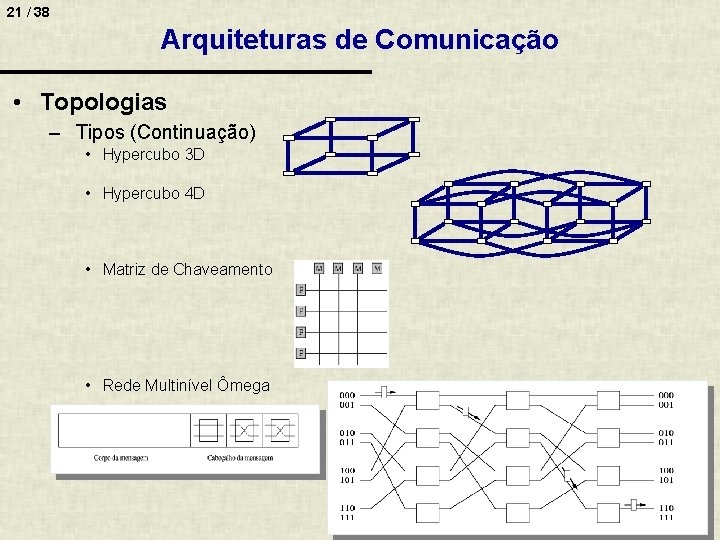

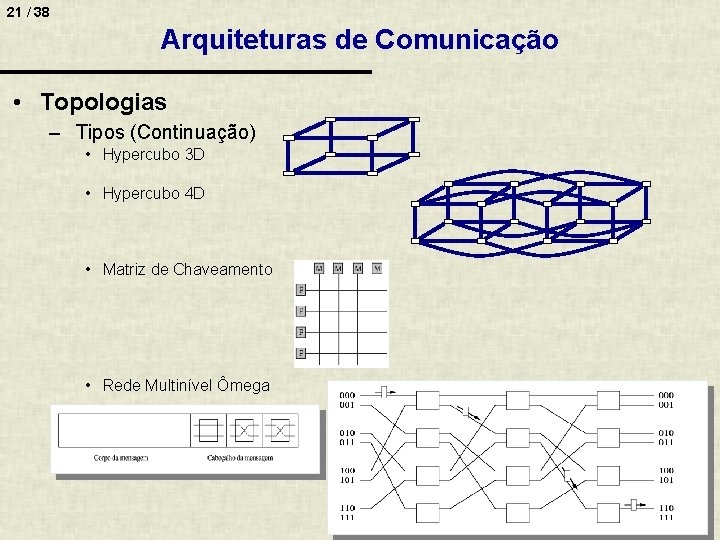

21 / 38 Arquiteturas de Comunicação • Topologias – Tipos (Continuação) • Hypercubo 3 D • Hypercubo 4 D • Matriz de Chaveamento • Rede Multinível Ômega

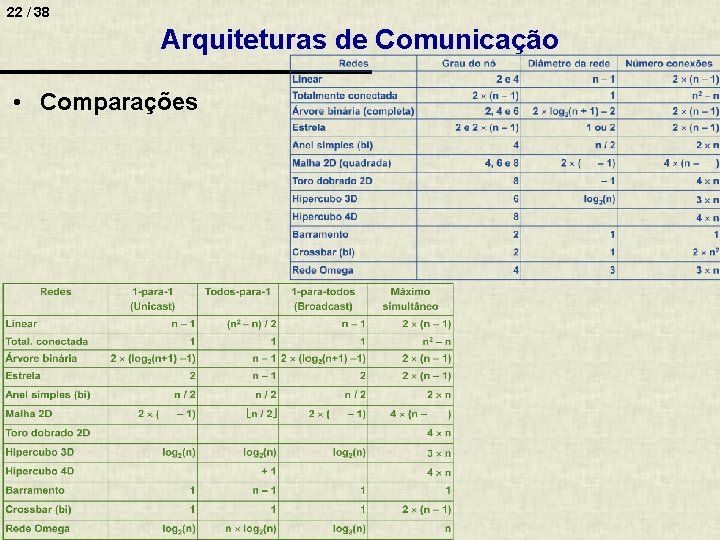

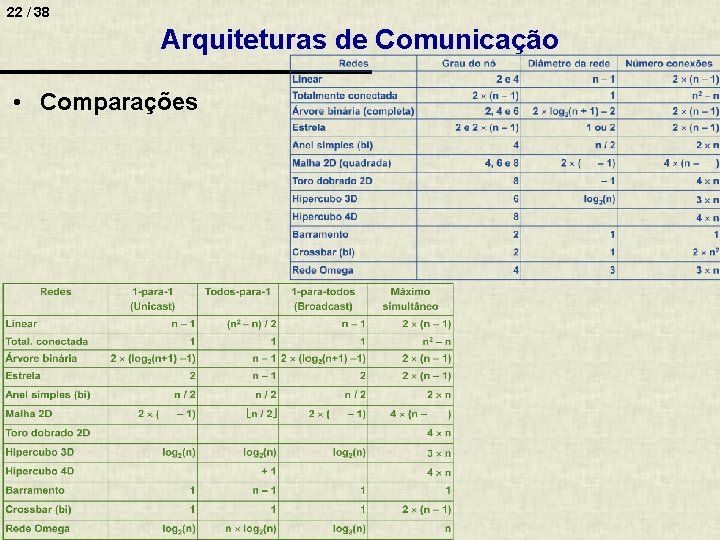

22 / 38 Arquiteturas de Comunicação • Comparações

23 / 38 Sumário de Conteúdos (Programa da Disciplina) • Exploração de mecanismos e técnicas de entrada e saída em hardware e em software (Unidade 1) • Evolução das arquiteturas de comunicação intrachip (Unidade 4) • Compreensão da hierarquia de memória no desempenho do sistema (Unidade 3) • Arquiteturas paralelas computação mono e multiprocessadas (Unidade 2)

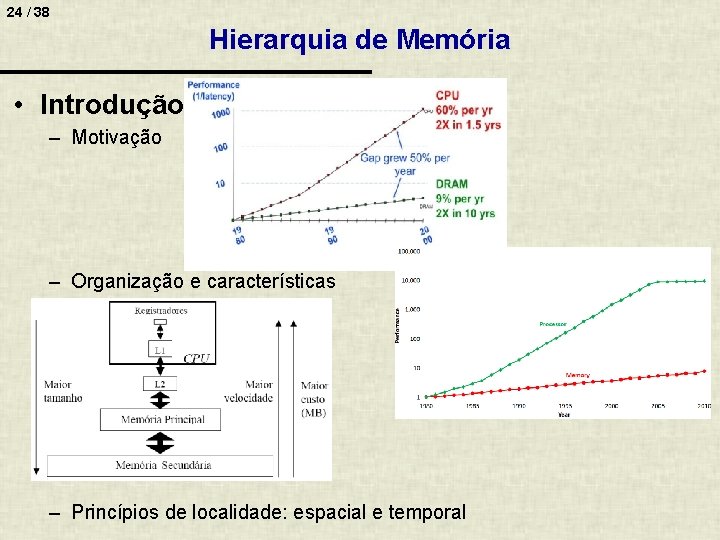

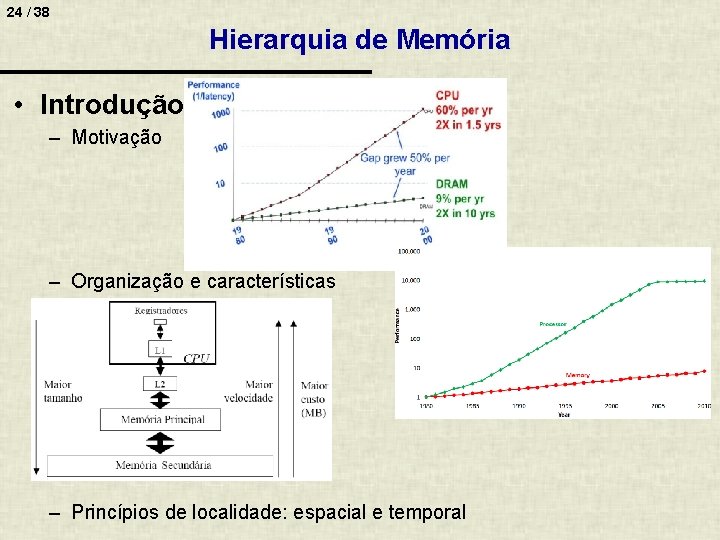

24 / 38 Hierarquia de Memória • Introdução – Motivação – Organização e características – Princípios de localidade: espacial e temporal

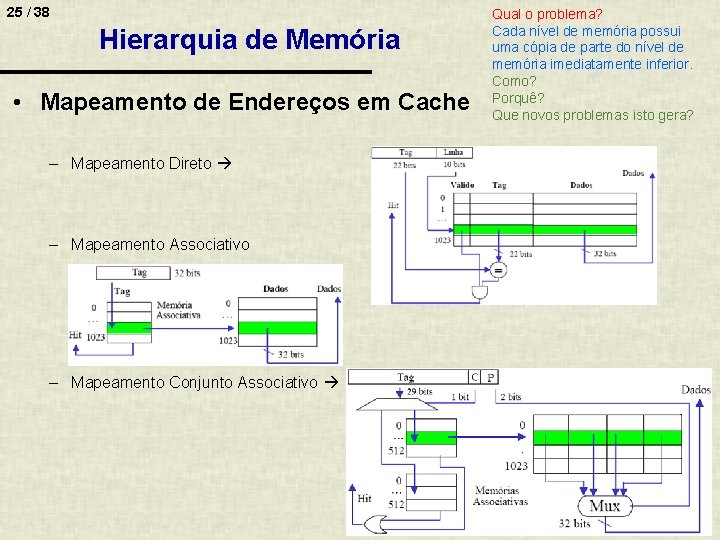

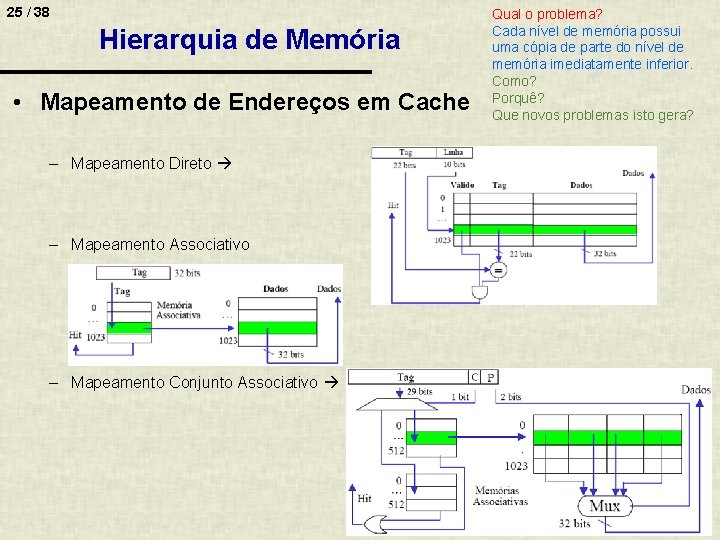

25 / 38 Hierarquia de Memória • Mapeamento de Endereços em Cache – Mapeamento Direto – Mapeamento Associativo – Mapeamento Conjunto Associativo Qual o problema? Cada nível de memória possui uma cópia de parte do nível de memória imediatamente inferior. Como? Porquê? Que novos problemas isto gera?

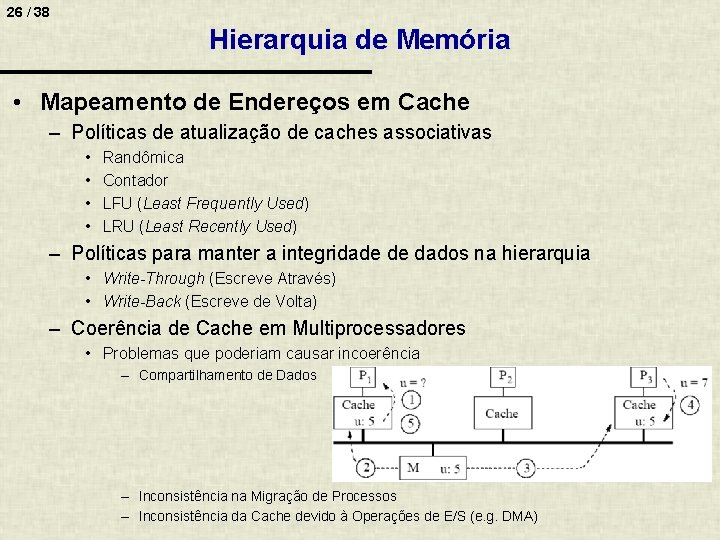

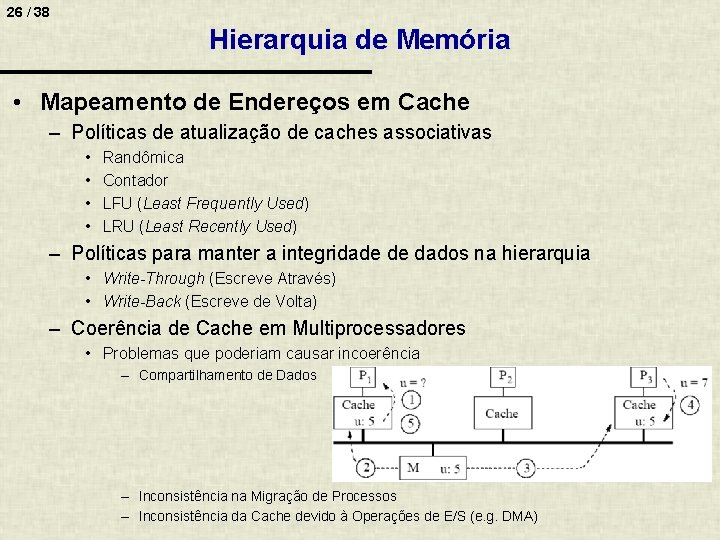

26 / 38 Hierarquia de Memória • Mapeamento de Endereços em Cache – Políticas de atualização de caches associativas • • Randômica Contador LFU (Least Frequently Used) LRU (Least Recently Used) – Políticas para manter a integridade de dados na hierarquia • Write-Through (Escreve Através) • Write-Back (Escreve de Volta) – Coerência de Cache em Multiprocessadores • Problemas que poderiam causar incoerência – Compartilhamento de Dados – Inconsistência na Migração de Processos – Inconsistência da Cache devido à Operações de E/S (e. g. DMA)

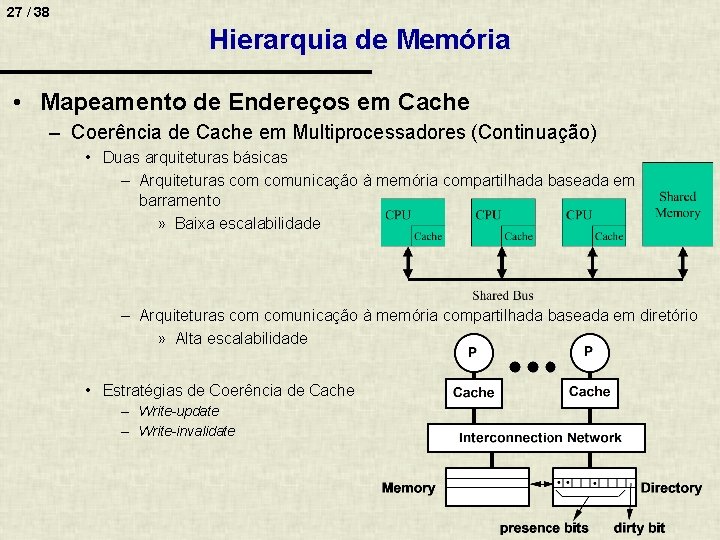

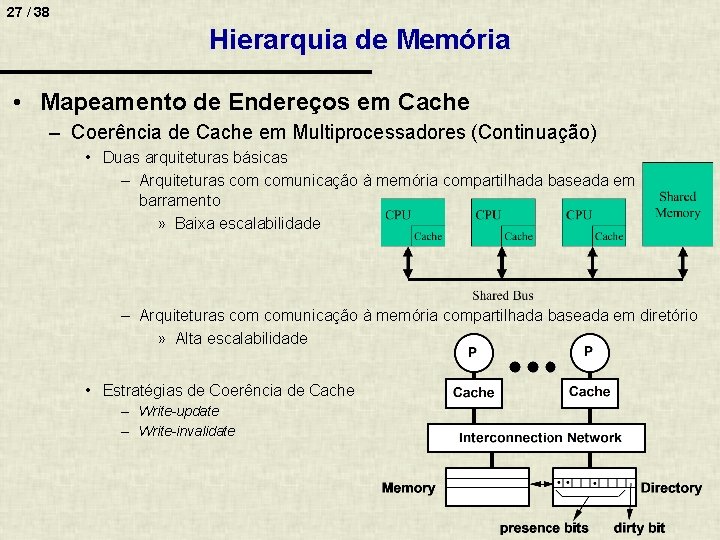

27 / 38 Hierarquia de Memória • Mapeamento de Endereços em Cache – Coerência de Cache em Multiprocessadores (Continuação) • Duas arquiteturas básicas – Arquiteturas comunicação à memória compartilhada baseada em barramento » Baixa escalabilidade – Arquiteturas comunicação à memória compartilhada baseada em diretório » Alta escalabilidade • Estratégias de Coerência de Cache – Write-update – Write-invalidate

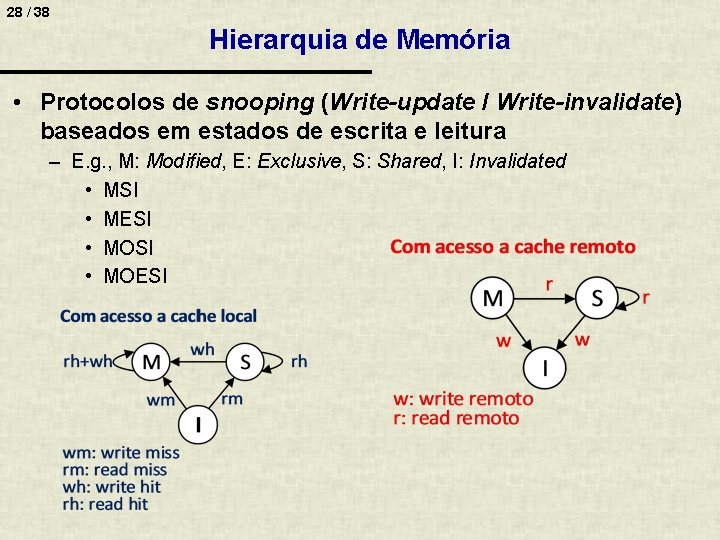

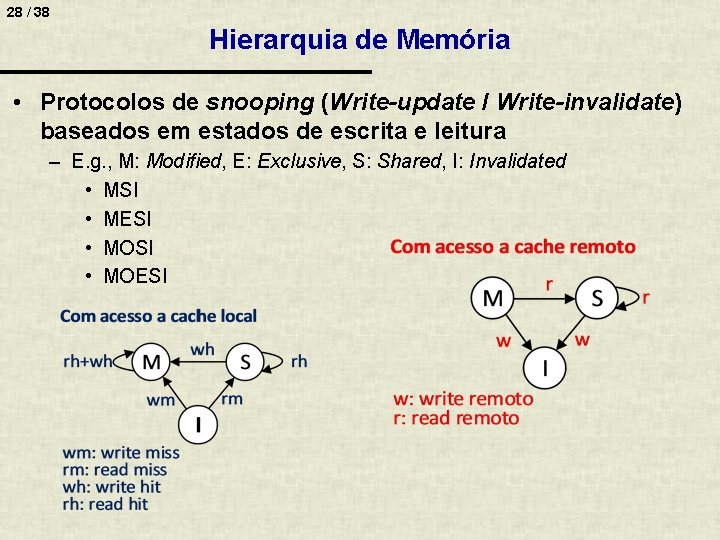

28 / 38 Hierarquia de Memória • Protocolos de snooping (Write-update / Write-invalidate) baseados em estados de escrita e leitura – E. g. , M: Modified, E: Exclusive, S: Shared, I: Invalidated • MSI • MESI • MOESI

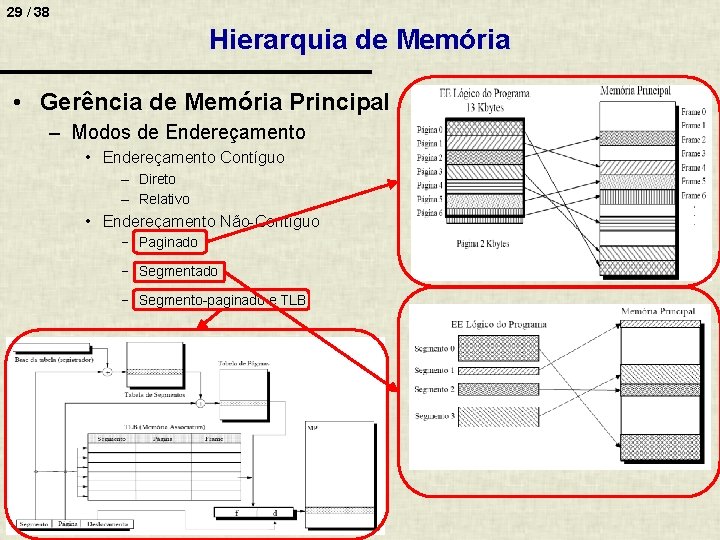

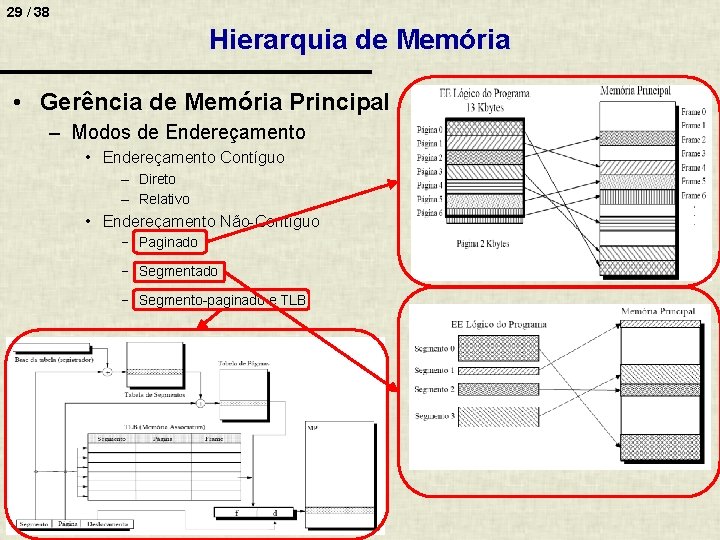

29 / 38 Hierarquia de Memória • Gerência de Memória Principal – Modos de Endereçamento • Endereçamento Contíguo – Direto – Relativo • Endereçamento Não-Contíguo – Paginado – Segmento-paginado e TLB

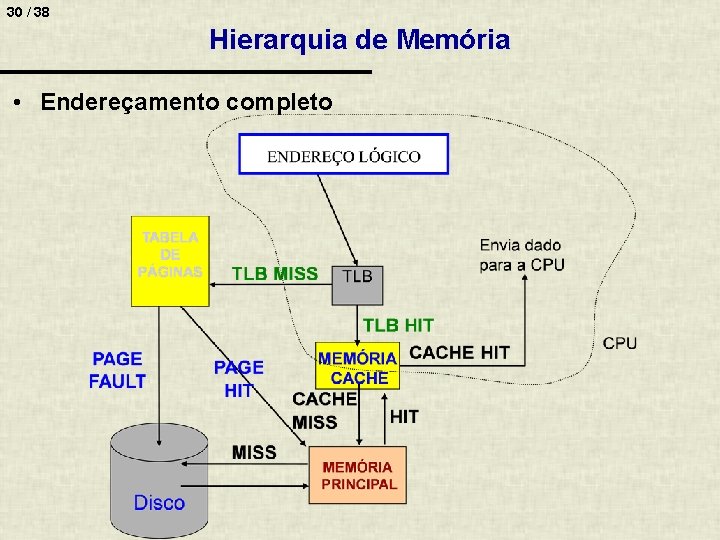

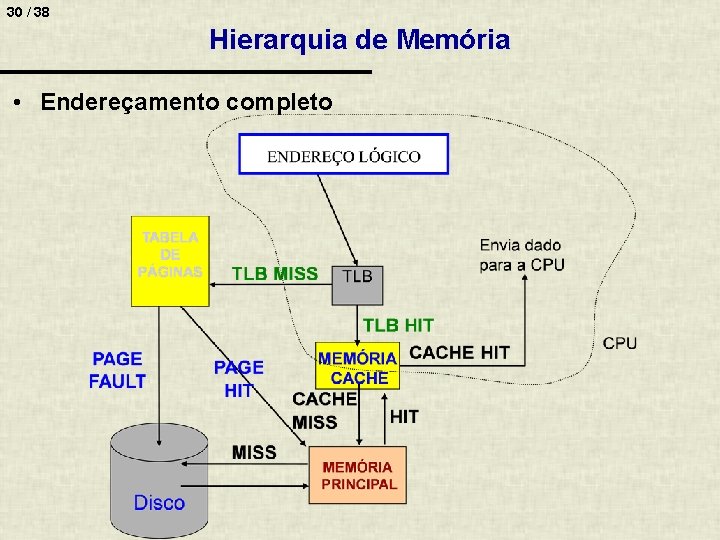

30 / 38 Hierarquia de Memória • Endereçamento completo

31 / 38 Sumário de Conteúdos (Programa da Disciplina) • Exploração de mecanismos e técnicas de entrada e saída em hardware e em software (Unidade 1) • Evolução das arquiteturas de comunicação intrachip (Unidade 4) • Compreensão da hierarquia de memória no desempenho do sistema (Unidade 3) • Arquiteturas paralelas computação mono e multiprocessadas (Unidade 2)

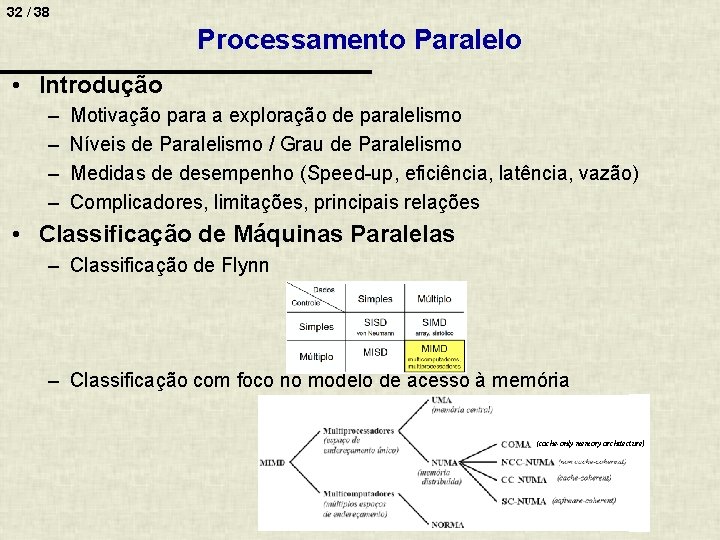

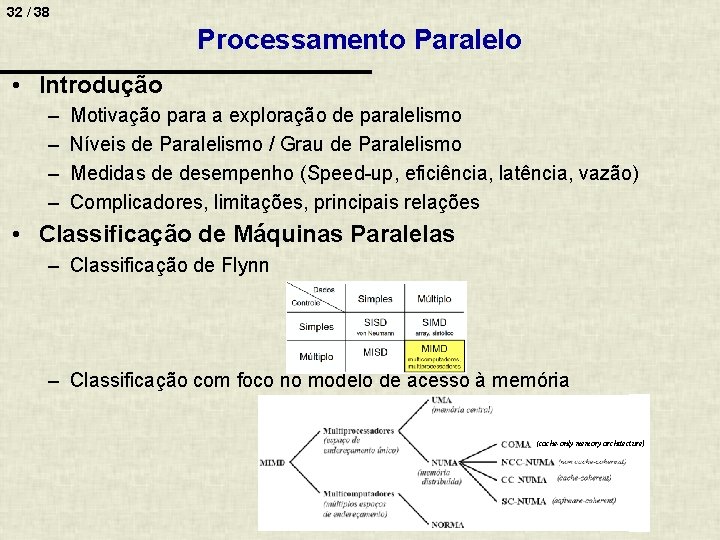

32 / 38 Processamento Paralelo • Introdução – – Motivação para a exploração de paralelismo Níveis de Paralelismo / Grau de Paralelismo Medidas de desempenho (Speed-up, eficiência, latência, vazão) Complicadores, limitações, principais relações • Classificação de Máquinas Paralelas – Classificação de Flynn – Classificação com foco no modelo de acesso à memória (cache-only memory architecture)

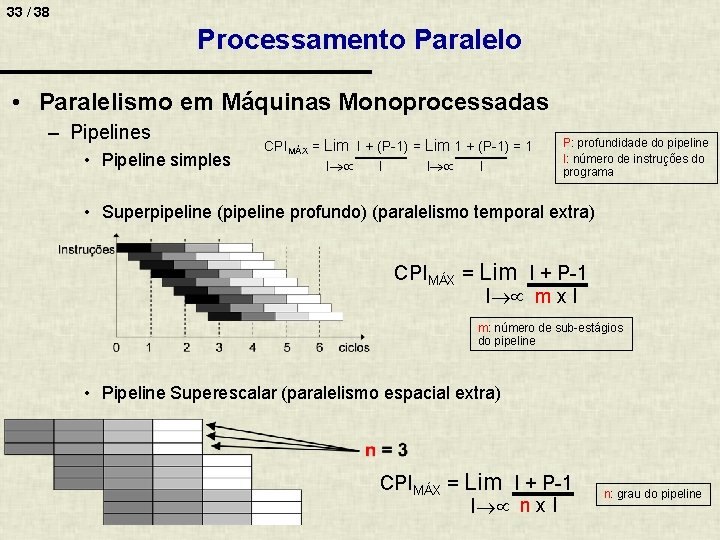

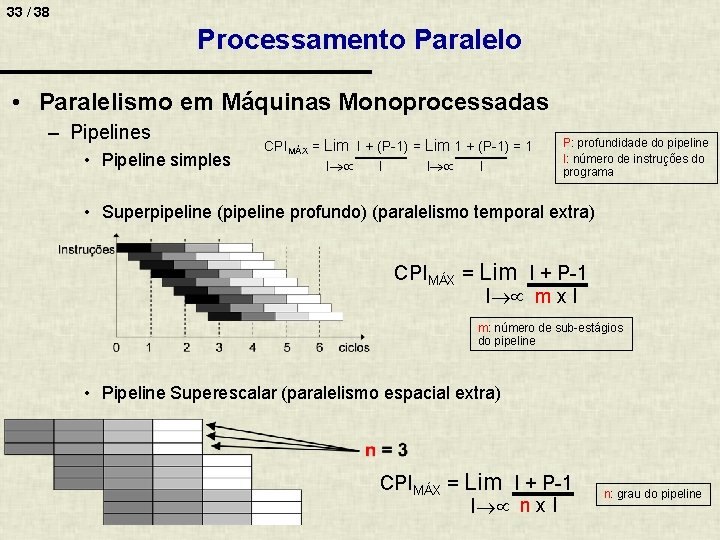

33 / 38 Processamento Paralelo • Paralelismo em Máquinas Monoprocessadas – Pipelines • Pipeline simples CPIMÁX = Lim I + (P-1) = Lim 1 + (P-1) = 1 I I I I P: profundidade do pipeline I: número de instruções do programa • Superpipeline (pipeline profundo) (paralelismo temporal extra) CPIMÁX = Lim I + P-1 I m x I m: número de sub-estágios do pipeline • Pipeline Superescalar (paralelismo espacial extra) CPIMÁX = Lim I + P-1 I n x I n: grau do pipeline

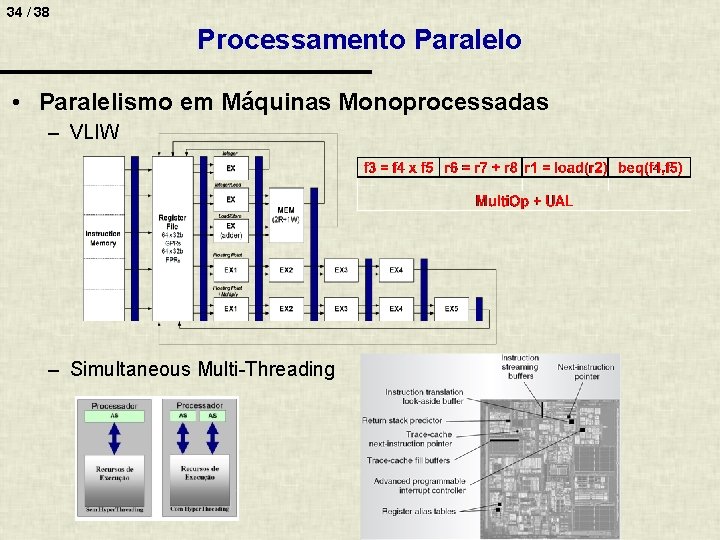

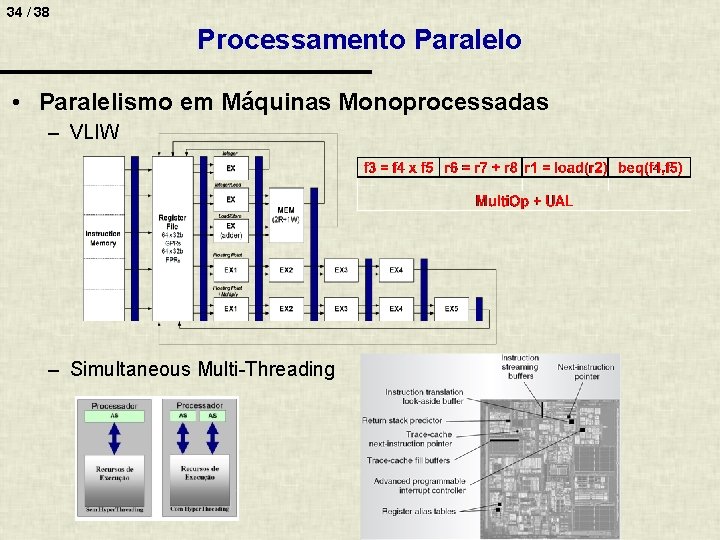

34 / 38 Processamento Paralelo • Paralelismo em Máquinas Monoprocessadas – VLIW – Simultaneous Multi-Threading

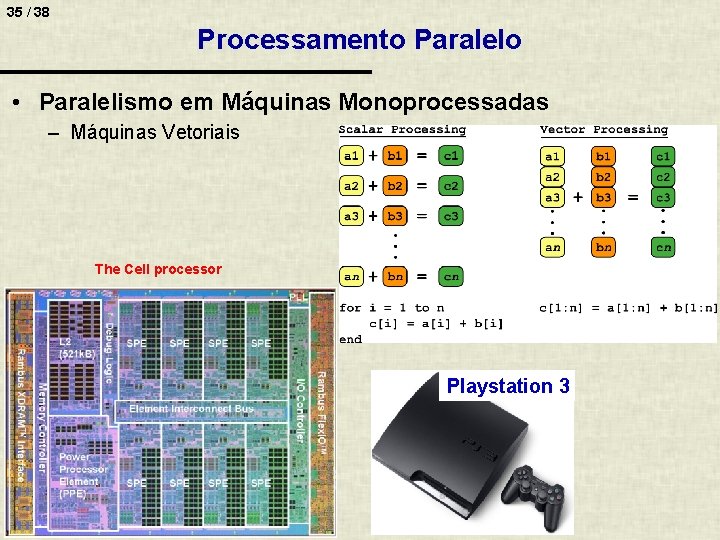

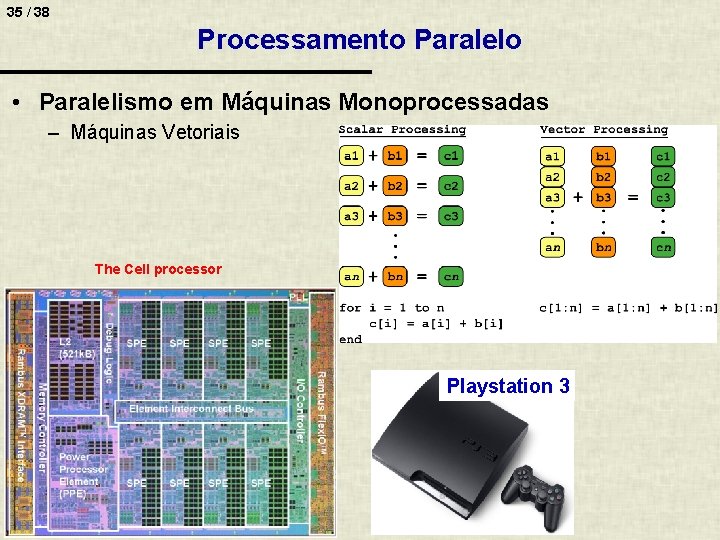

35 / 38 Processamento Paralelo • Paralelismo em Máquinas Monoprocessadas – Máquinas Vetoriais The Cell processor Playstation 3

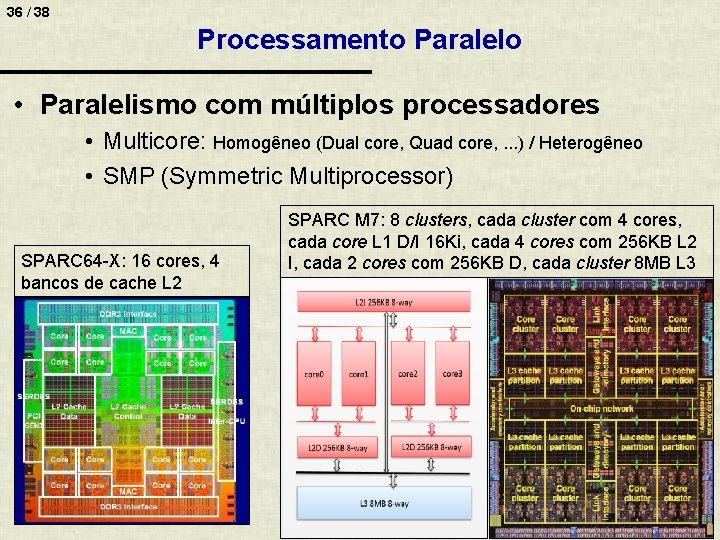

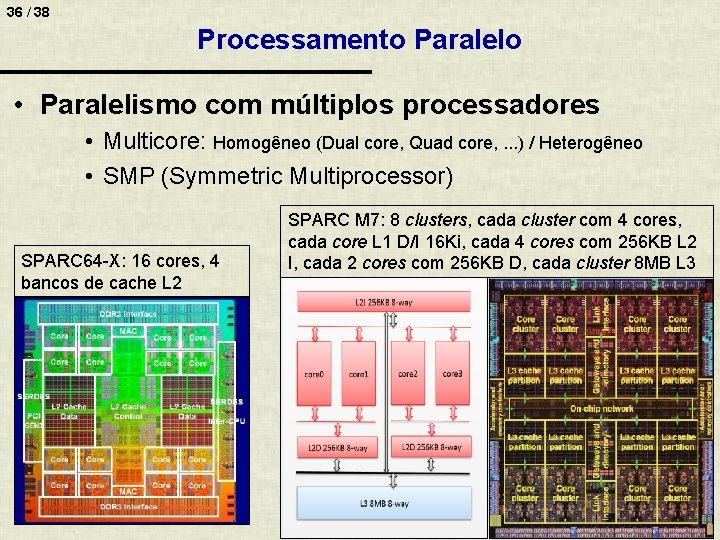

36 / 38 Processamento Paralelo • Paralelismo com múltiplos processadores • Multicore: Homogêneo (Dual core, Quad core, . . . ) / Heterogêneo • SMP (Symmetric Multiprocessor) SPARC 64 -X: 16 cores, 4 bancos de cache L 2 SPARC M 7: 8 clusters, cada cluster com 4 cores, cada core L 1 D/I 16 Ki, cada 4 cores com 256 KB L 2 I, cada 2 cores com 256 KB D, cada cluster 8 MB L 3

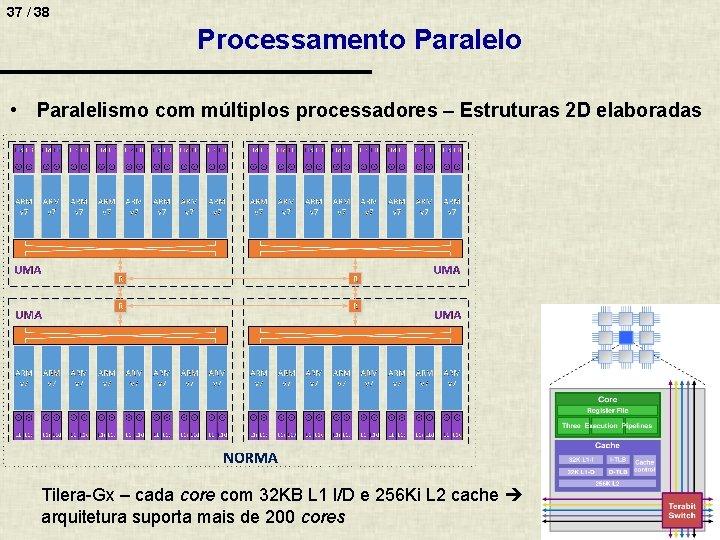

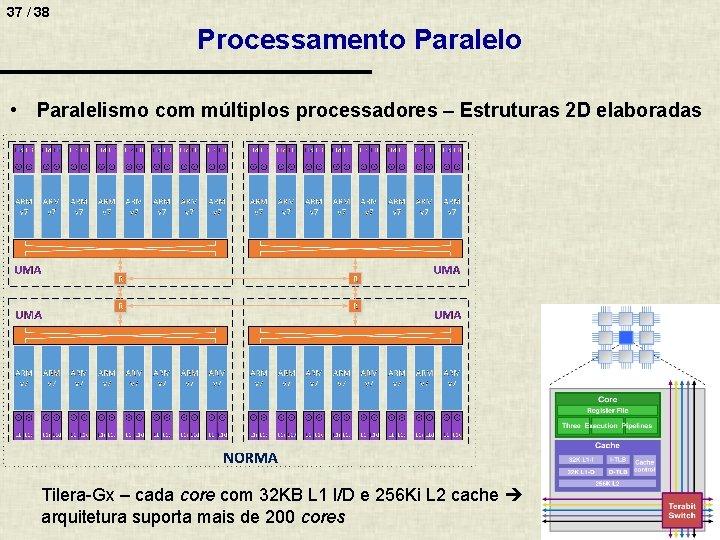

37 / 38 Processamento Paralelo • Paralelismo com múltiplos processadores – Estruturas 2 D elaboradas Tilera-Gx – cada core com 32 KB L 1 I/D e 256 Ki L 2 cache arquitetura suporta mais de 200 cores

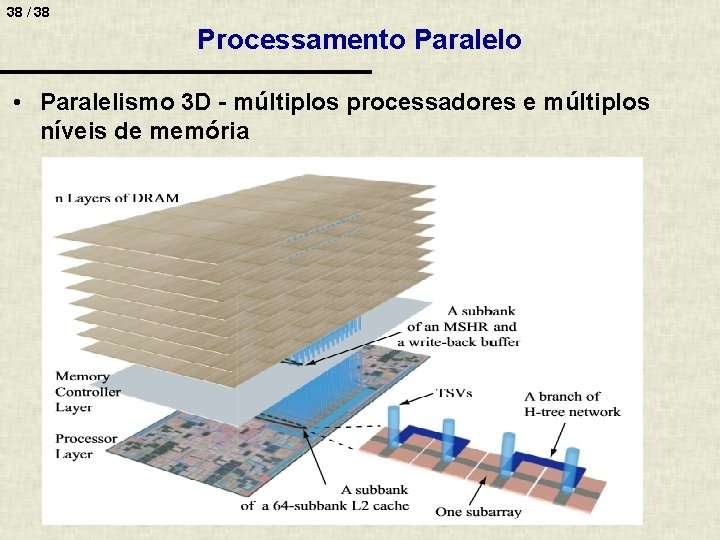

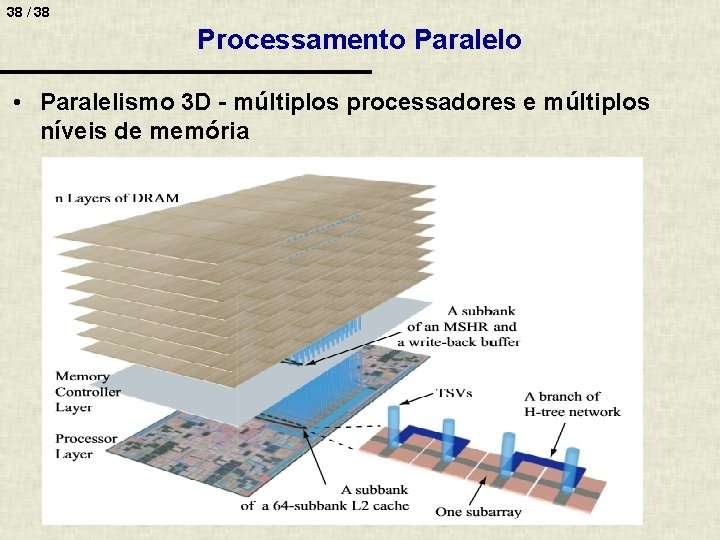

38 / 38 Processamento Paralelo • Paralelismo 3 D - múltiplos processadores e múltiplos níveis de memória

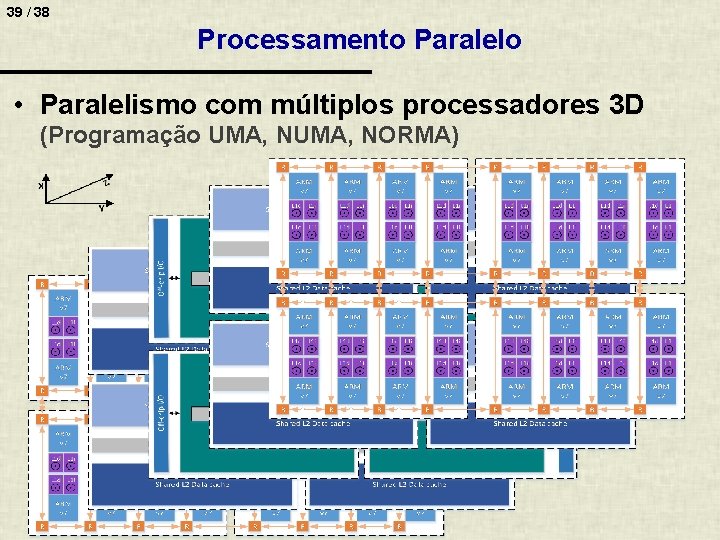

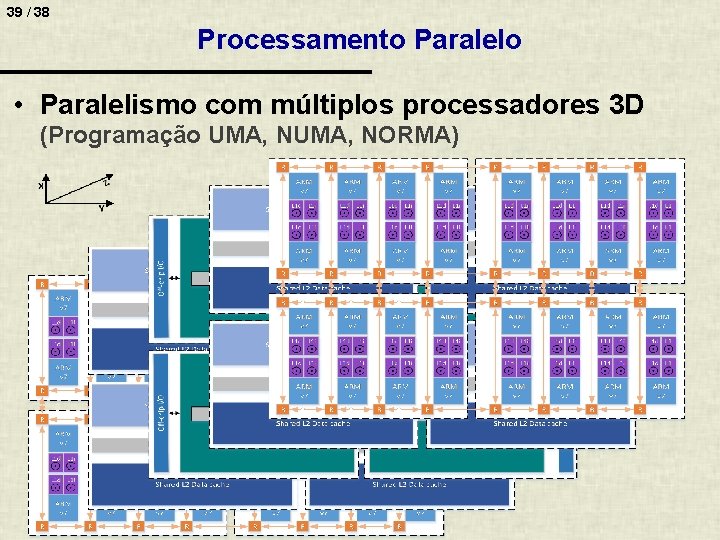

39 / 38 Processamento Paralelo • Paralelismo com múltiplos processadores 3 D (Programação UMA, NORMA)