Organizao de Computadores Organizao do Processador Parte B

Organização de Computadores Organização do Processador Parte B Capítulo 5 – Patterson & Hennessy Prof. Fábio M. Costa Instituto de Informática Universidade Federal de Goiás

Implementação Muticiclo Dividir a execução de uma instrução em passos Cada passo gasta 1 ciclo de relógio Permite que uma mesma unidade funcional seja usada mais de uma vez por uma instrução: – – 2 uma única memória para dados e instruções uma única UAL (sem os somadores especiais) Elementos de estado são escritos na transição do relógio Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

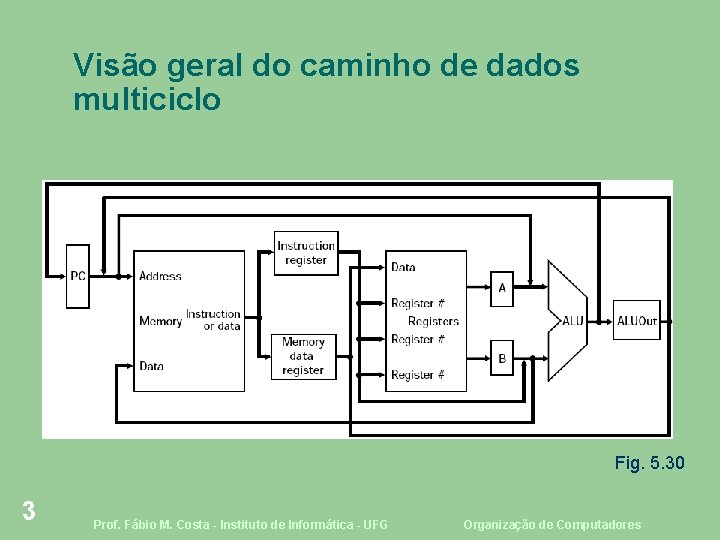

Visão geral do caminho de dados multiciclo Fig. 5. 30 3 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Elementos de estado intermediárioas Armazenam um valor produzido durante um ciclo para uso no próximo ciclo (dentro da mesma instrução) – – 4 IR: instrução buscada da memória MDR: dados lidos da memória A e B: dados a serem alimentados nas entradas respectivas da UALSaída: resultado produzido pela UAL Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

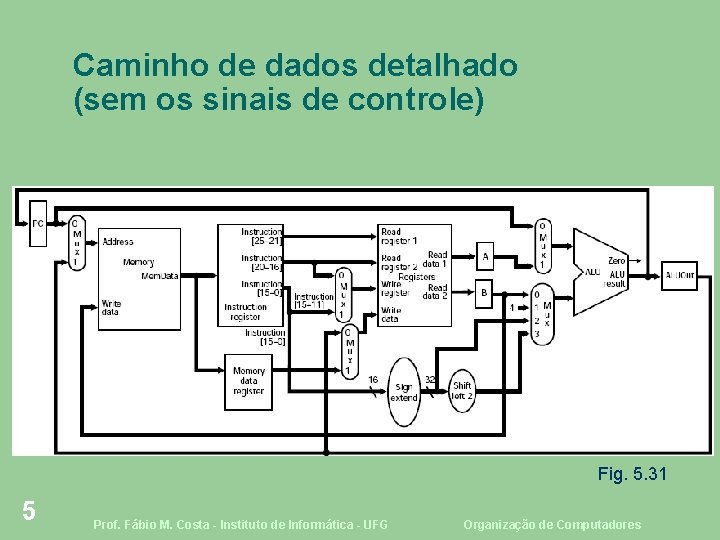

Caminho de dados detalhado (sem os sinais de controle) Fig. 5. 31 5 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

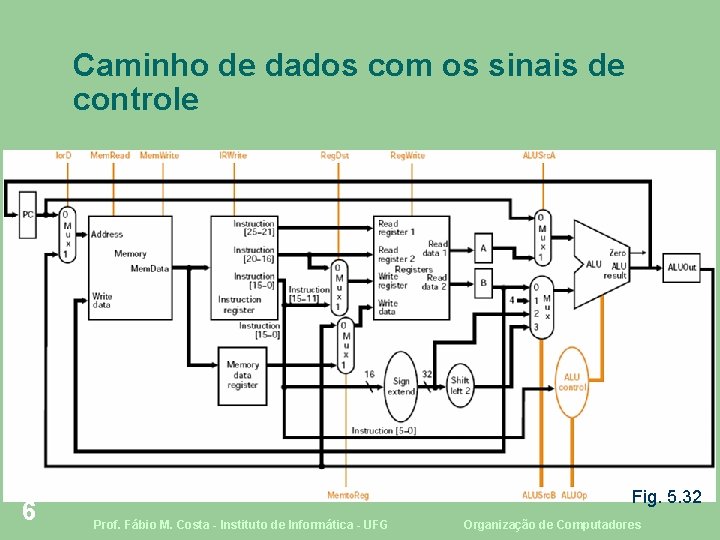

Caminho de dados com os sinais de controle 6 Fig. 5. 32 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

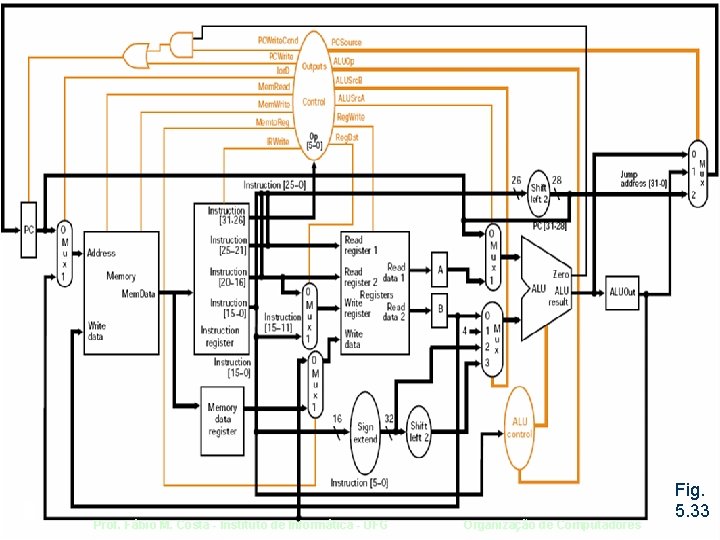

Caminho de dados completo com a UC e lógica de atualização do PC. . . 7 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Caminho de dados 8 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores Fig. 5. 33

Passos na execução de instruções. . . 9 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Passos na execução de instruções 10 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Exercício Analisar a possibilidade de: – – 11 Executar a instrução J em apenas dois ciclos/passos Executar a instrução LW em apenas quatro ciclos/passos Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Implementação da Unidade de Controle Duas alternativas: – – 12 Máquina de estados Microprogramação Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

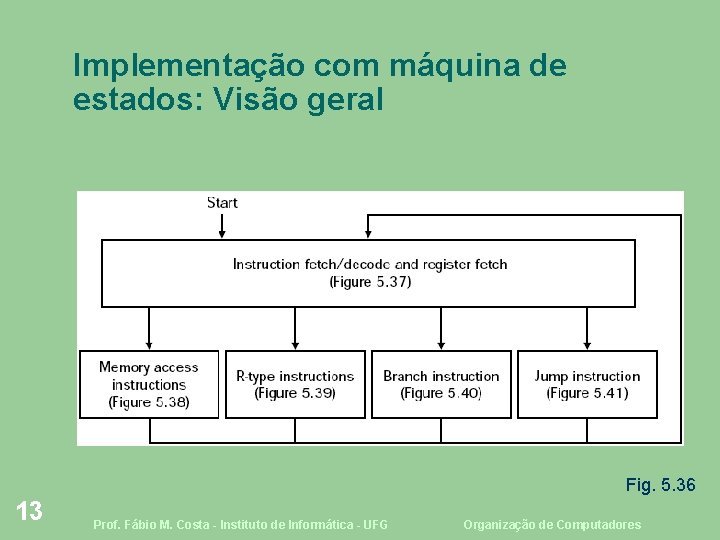

Implementação com máquina de estados: Visão geral Fig. 5. 36 13 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

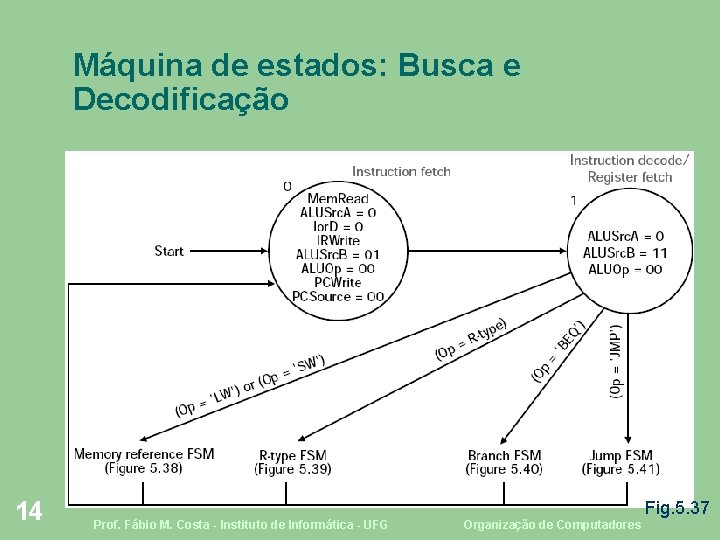

Máquina de estados: Busca e Decodificação 14 Fig. 5. 37 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

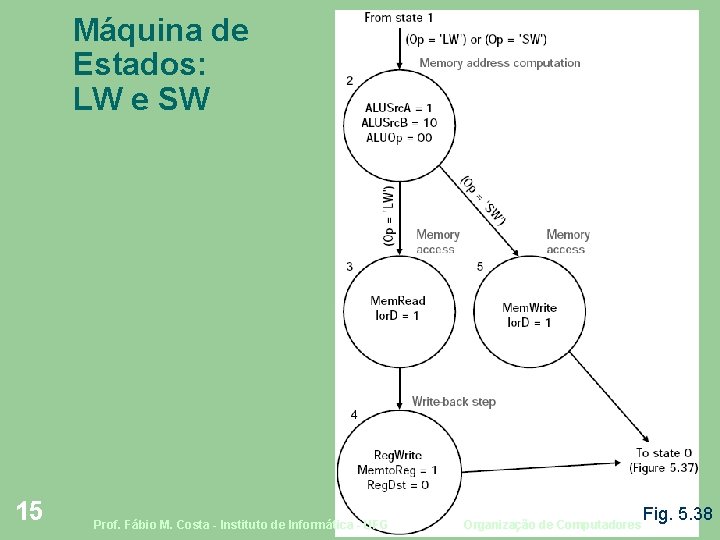

Máquina de Estados: LW e SW 15 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores Fig. 5. 38

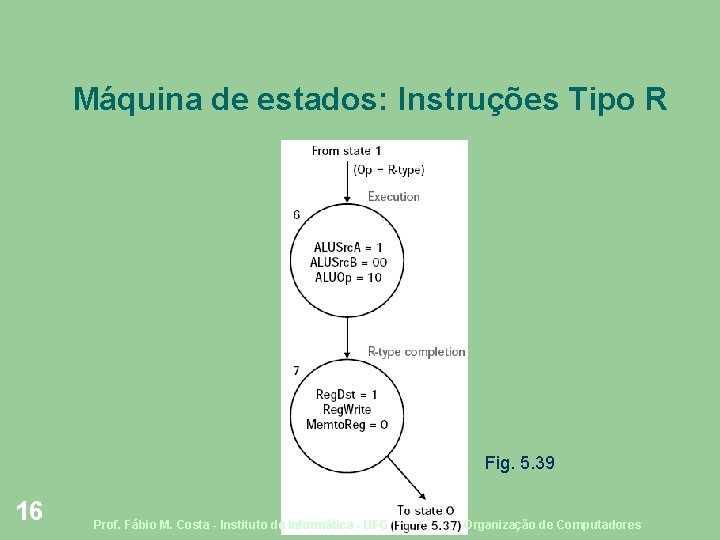

Máquina de estados: Instruções Tipo R Fig. 5. 39 16 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

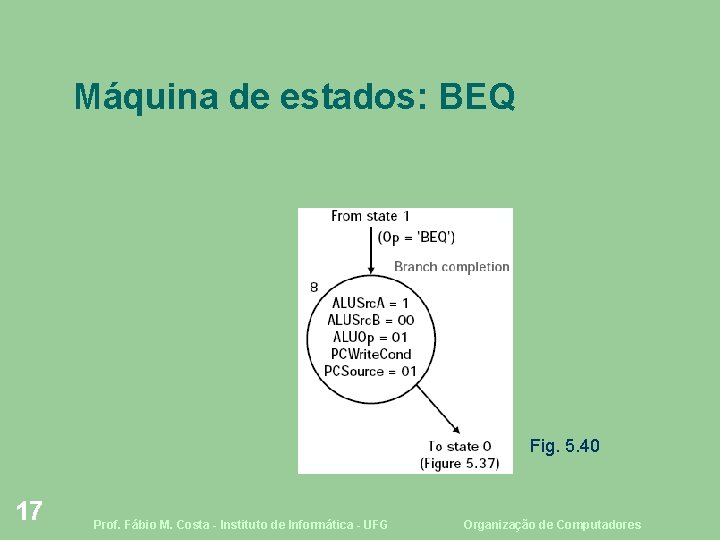

Máquina de estados: BEQ Fig. 5. 40 17 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

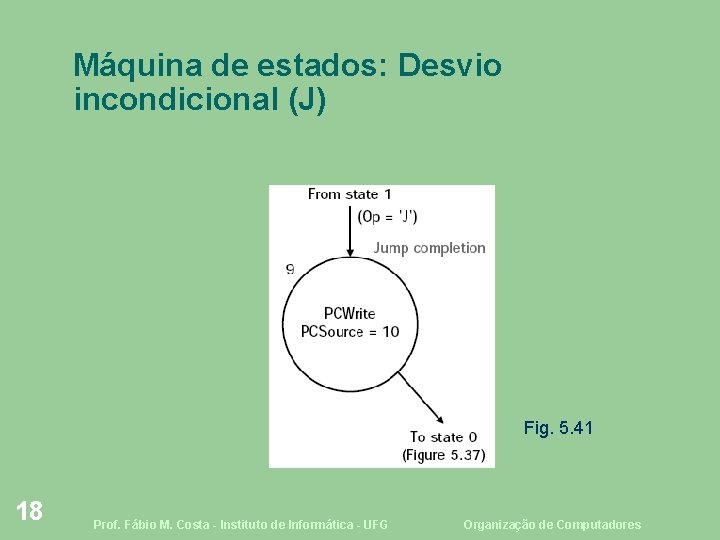

Máquina de estados: Desvio incondicional (J) Fig. 5. 41 18 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Máquina de Estados Completa. . . 19 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

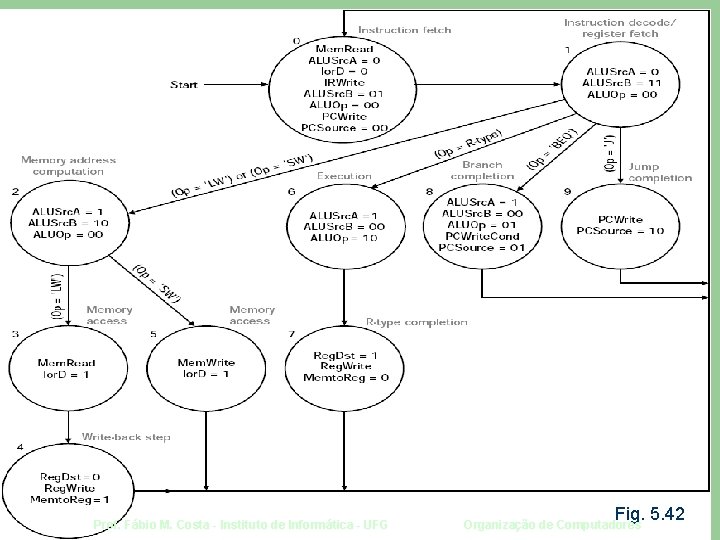

20 Prof. Fábio M. Costa - Instituto de Informática - UFG Fig. 5. 42 Organização de Computadores

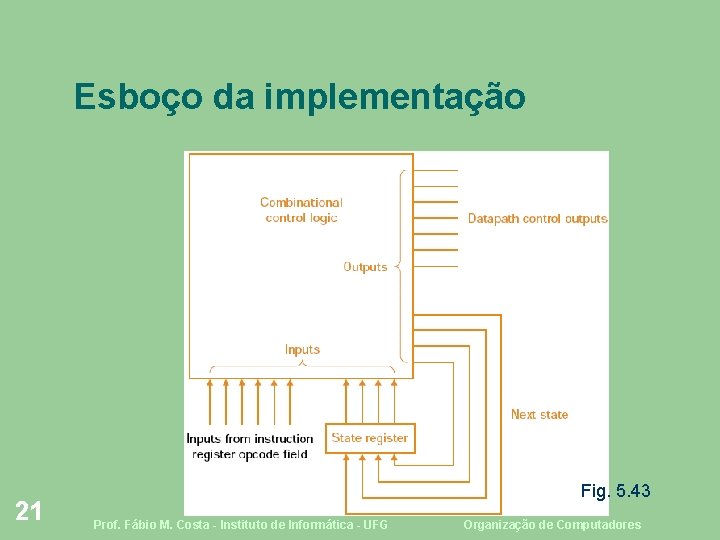

Esboço da implementação 21 Fig. 5. 43 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

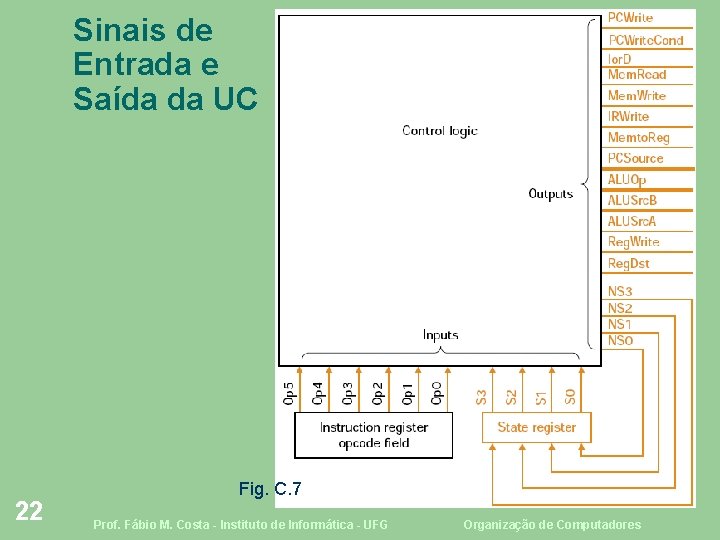

Sinais de Entrada e Saída da UC 22 Fig. C. 7 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Equações lógicas da UC: Quais sinais são ativados em cada estado 23 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Sinais de controle em função do estado corrente (Exercício: completar a tabela) 24 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Equações lógicas da UC: Determinação do próximo estado (1) 25 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Equações lógicas da UC: Determinação do próximo estado (2) 26 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Equações lógicas da UC: Determinação do próximo estado (3) 27 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Equações lógicas da UC: Determinação do próximo estado (4) 28 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Equações lógicas da UC: Determinação do próximo estado (5) 29 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Implementação da lógica de controle através de uma ROM Endereços: serão as entradas da lógica de controle – – Palavras – – – 16 bits de sinais de controle do caminho de dados (bits 19 -4) 4 bits indicadores do próximo estado (bits 3 -0) Total: 20 bits Tamanho da ROM: 1024 x 20 = 20 Kbits – 30 6 bits de Op. Code (bits 9 -4) + 4 bits do estado corrente (bits 3 -0) i. e. : 10 bits: 210 = 1024 palavras (i. e. 1 K palavras) Obs. : muitas palavras serão desperdiçadas, por não corresponderem a entradas significativas Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Conteúdo da ROM (1): Sinais de controle em função do estado corrente 31 Tabela C. 12 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Conteúdo da ROM (2): Próximo estado em função do estado corrente e do opcode 32 Prof. Fábio M. Costa - Instituto de Informática - UFG Fig. Organização de Computadores C-13

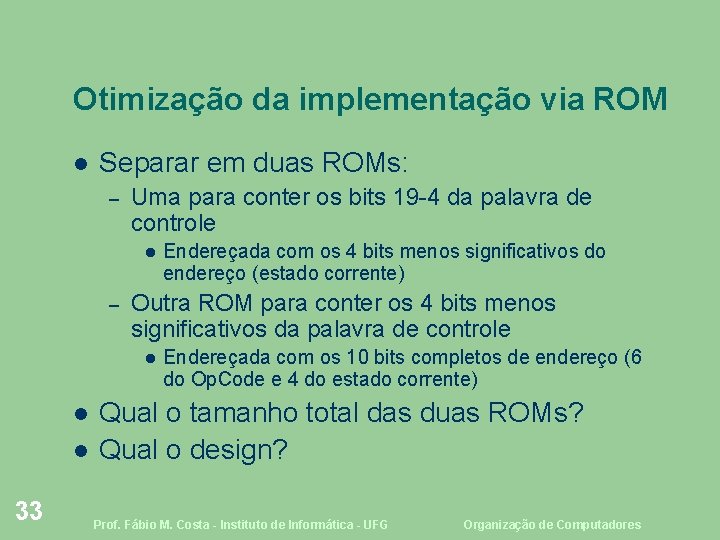

Otimização da implementação via ROM Separar em duas ROMs: – Uma para conter os bits 19 -4 da palavra de controle – Outra ROM para conter os 4 bits menos significativos da palavra de controle 33 Endereçada com os 4 bits menos significativos do endereço (estado corrente) Endereçada com os 10 bits completos de endereço (6 do Op. Code e 4 do estado corrente) Qual o tamanho total das duas ROMs? Qual o design? Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

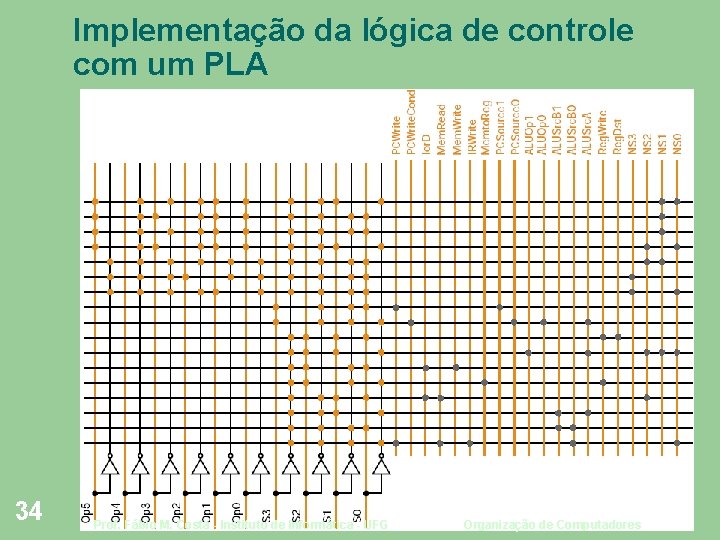

Implementação da lógica de controle com um PLA 34 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

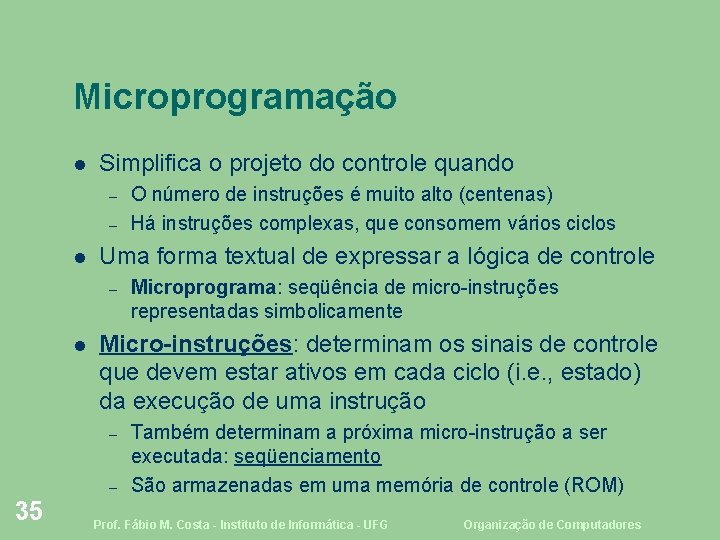

Microprogramação Simplifica o projeto do controle quando – – Uma forma textual de expressar a lógica de controle – Microprograma: seqüência de micro-instruções representadas simbolicamente Micro-instruções: determinam os sinais de controle que devem estar ativos em cada ciclo (i. e. , estado) da execução de uma instrução – – 35 O número de instruções é muito alto (centenas) Há instruções complexas, que consomem vários ciclos Também determinam a próxima micro-instrução a ser executada: seqüenciamento São armazenadas em uma memória de controle (ROM) Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Formato das micro-instruções 36 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Valores dos campos de uma microinstrução (1) 37 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Valores dos campos de uma microinstrução (2) 38 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

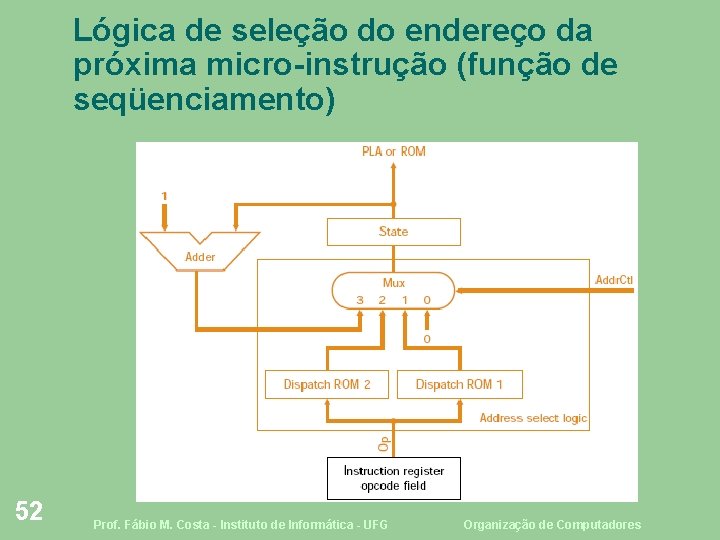

Seqüenciamento de micro-instruções Seqüencial: a próxima micro-instrução a ser executada está no endereço seguinte na ROM de controle – Busca: a próxima micro-instrução é a que executa a busca da próxima instrução ISA a ser executada – Apenas incrementa-se o endereço Ao término da seqüência de micro-instruções que executou uma dada instrução ISA Despacho: a próxima instrução é escolhida com base no Opcode da instrução ISA sendo executada – Usado para indexar uma “tabela de despacho”, que contém o endereço efetivo da próxima micro-instrução – 39 Tabelas de despacho: uma para cada estado com mais de uma transição Ex. : transições que partem do estado 1 na máq. de estados Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Microprograma: Busca de instruções 40 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Microprograma: Instruções de acesso à memória 41 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Microprograma: Instruções Tipo R 42 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Microprograma: Instrução de desvio condicional 43 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Microprograma: Instrução de desvio incondicional 44 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Microprograma completo 45 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Tabelas de Despacho 46 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

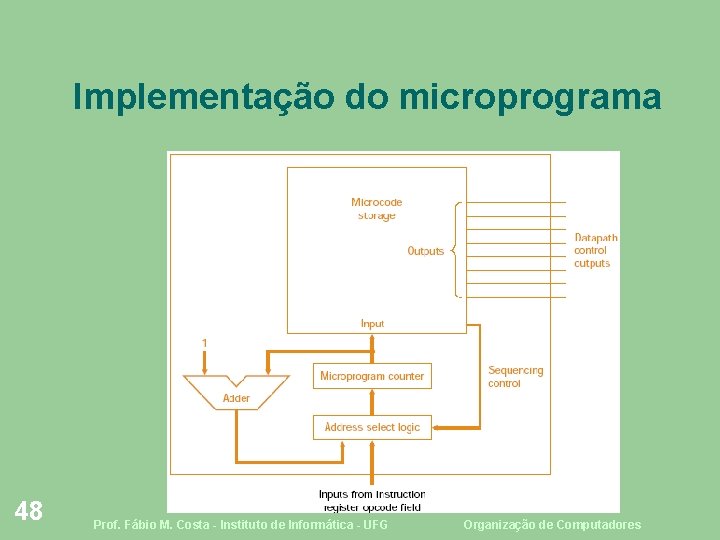

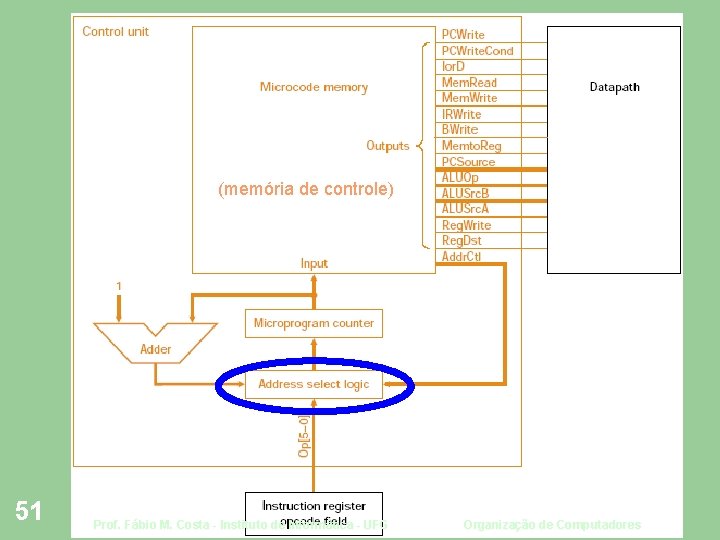

Implementação do microprograma Duas partes: – Método para armazenar a função de controle principal ROM, cujas palavras determinam: o valor das linhas de controle do caminho de dados – como selecionar a próxima micro-instrução – – Função de seqüenciamento 47 incrementador (semelhante ao PC) Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Implementação do microprograma 48 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

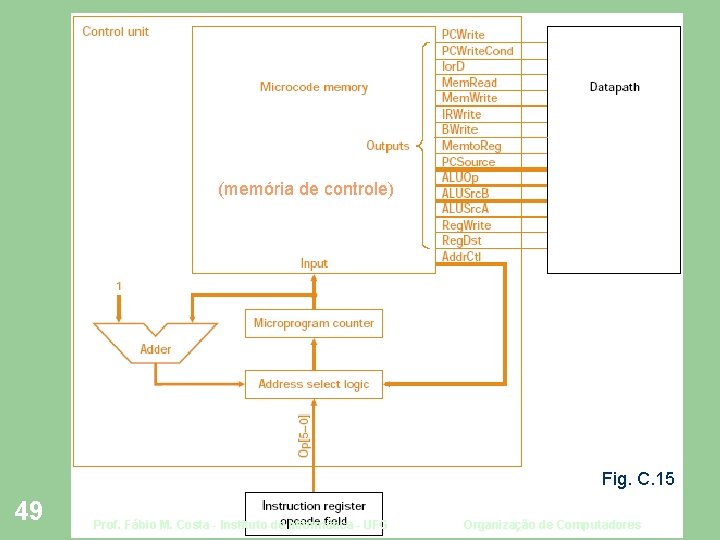

Detalhamento. . . (memória de controle) Fig. C. 15 49 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

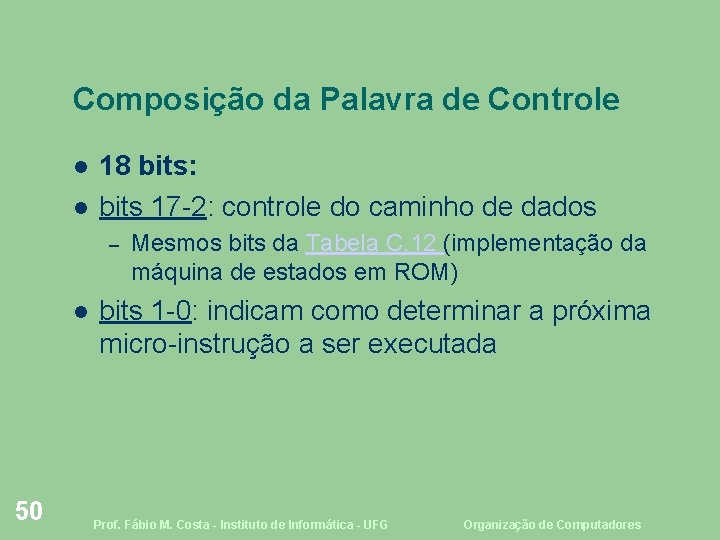

Composição da Palavra de Controle 18 bits: bits 17 -2: controle do caminho de dados – 50 Mesmos bits da Tabela C. 12 (implementação da máquina de estados em ROM) bits 1 -0: indicam como determinar a próxima micro-instrução a ser executada Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Detalhamento. . . (memória de controle) 51 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Lógica de seleção do endereço da próxima micro-instrução (função de seqüenciamento) 52 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Significado dos bits Addr. Ctl (End. Ctl) (bits 0 e 1 da palavra de controle) 53 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Valores dos bits Addr. Ctl (End. Ctl) para cada micro-instrução (bits 0 e 1 da palavra de controle) 54 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Conteúdo da memória de controle 55 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Micromontador Permite a codificação simbólica do microprograma – – Gera o código binário que constituirá as palavras de controle armazenadas na memória de controle Pode otimizar o uso de endereços seqüenciais para µ-instruções que executam em seqüência – – 56 nomes simbólicos para as micro-instruções rótulos em lugar de endereços Otimiza o uso do contador de micro-programa (µ-PC) i. e. , mais µ-instruções vão ser seqüenciadas com base apenas no incremento do contador Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Outras otimizações Codificação do micro-programa – Combinando linhas de controle mutuamente exclusivas com o uso de decodificadores – 57 Ex. : 8 bits de controle que nunca são ativados simultaneamente podem ser substituídas por 3 bits e um decodificador 3: 8 Permite reduzir o tamanho da palavra de controle (i. e. , das micro-instruções) Uso de vários formatos de micro-instruções Tarefa que pode ser realizada pelo microassembler Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

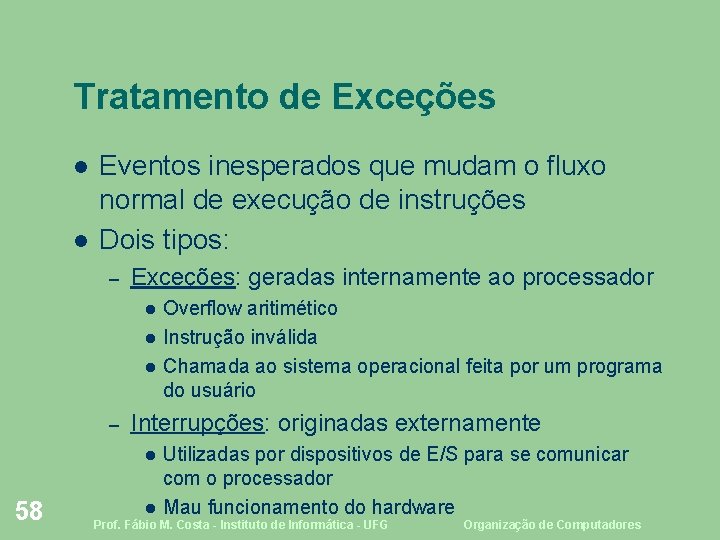

Tratamento de Exceções Eventos inesperados que mudam o fluxo normal de execução de instruções Dois tipos: – Exceções: geradas internamente ao processador – Interrupções: originadas externamente 58 Overflow aritimético Instrução inválida Chamada ao sistema operacional feita por um programa do usuário Utilizadas por dispositivos de E/S para se comunicar com o processador Mau funcionamento do hardware Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

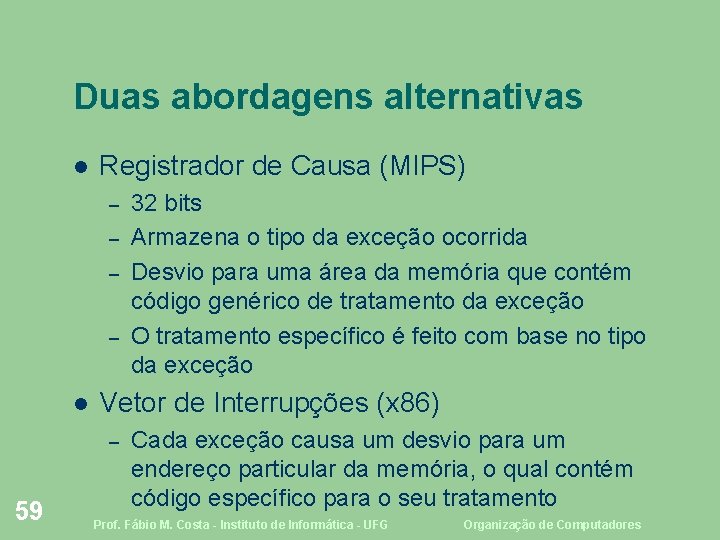

Duas abordagens alternativas Registrador de Causa (MIPS) – – Vetor de Interrupções (x 86) – 59 32 bits Armazena o tipo da exceção ocorrida Desvio para uma área da memória que contém código genérico de tratamento da exceção O tratamento específico é feito com base no tipo da exceção Cada exceção causa um desvio para um endereço particular da memória, o qual contém código específico para o seu tratamento Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

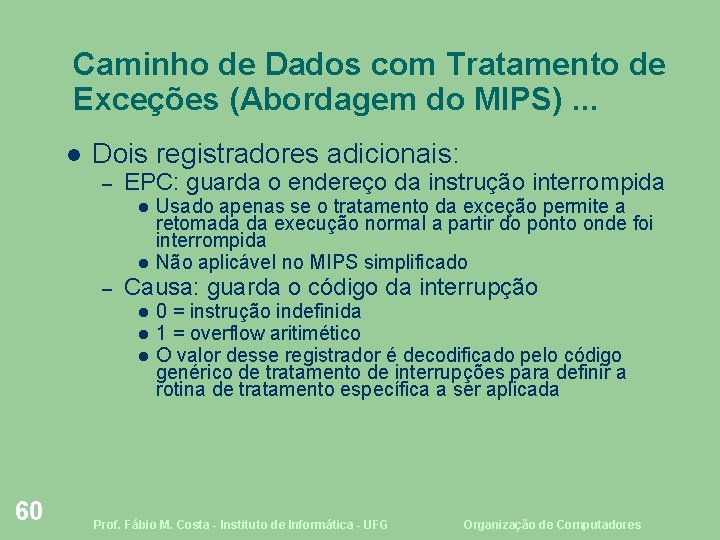

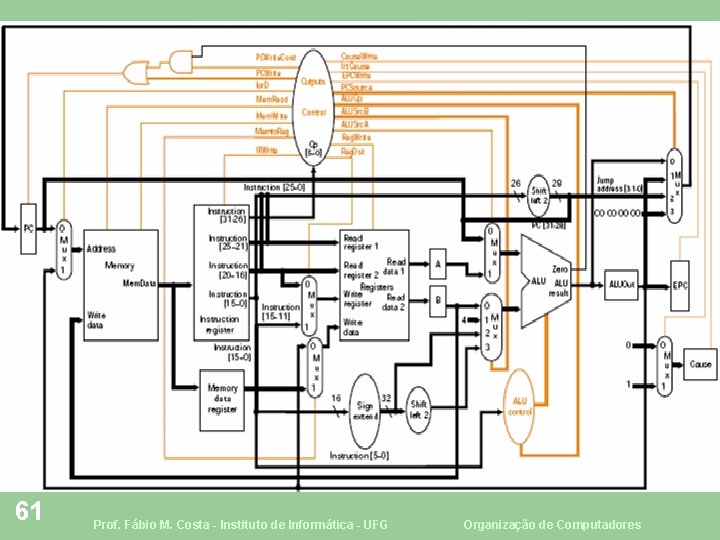

Caminho de Dados com Tratamento de Exceções (Abordagem do MIPS). . . Dois registradores adicionais: – EPC: guarda o endereço da instrução interrompida – Causa: guarda o código da interrupção 60 Usado apenas se o tratamento da exceção permite a retomada da execução normal a partir do ponto onde foi interrompida Não aplicável no MIPS simplificado 0 = instrução indefinida 1 = overflow aritimético O valor desse registrador é decodificado pelo código genérico de tratamento de interrupções para definir a rotina de tratamento específica a ser aplicada Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

61 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

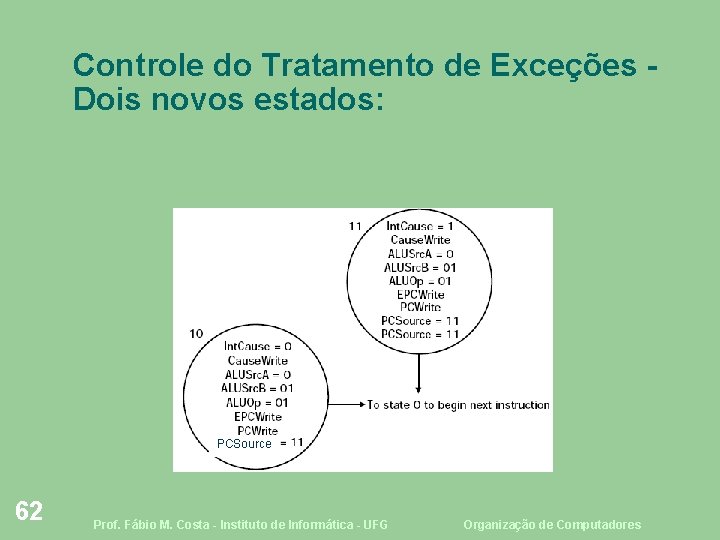

Controle do Tratamento de Exceções Dois novos estados: PCSource 62 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

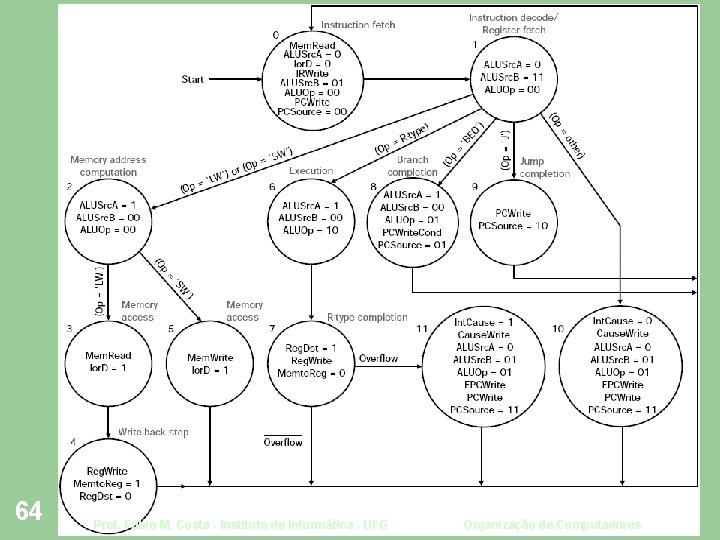

Máquina de Estados com Tratamento de Exceções. . . 63 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

64 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

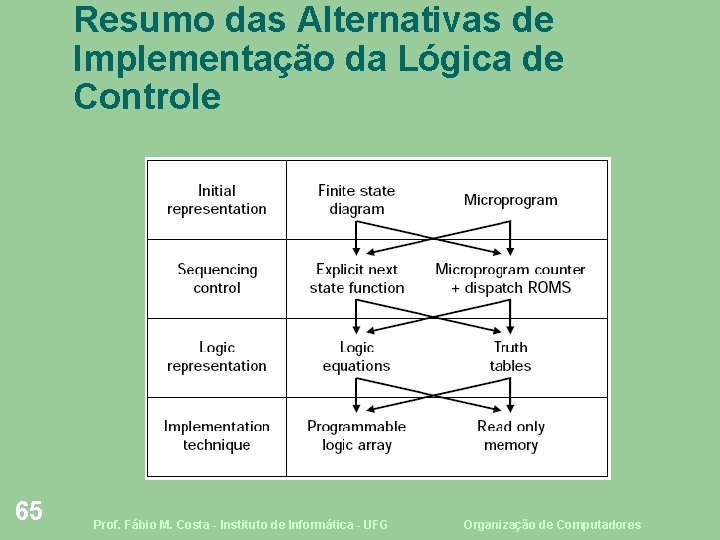

Resumo das Alternativas de Implementação da Lógica de Controle 65 Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

Trabalho - Preparativos Estudar os dois simuladores de circuitos digitais disponíveis – – Ambos disponíveis em: – 66 Digital Works Circuit Maker www. inf. ufg. br/~fmc/orgcomp/simuladores O trabalho consistirá em implementar o projeto do Capítulo 5 (Patterson&Hennessy) utilizando um destes simuladores Prof. Fábio M. Costa - Instituto de Informática - UFG Organização de Computadores

- Slides: 66