Organizao de Computadores Introduo Captulo 2 Tanenbaum Prof

Organização de Computadores Introdução Capítulo 2 - Tanenbaum Prof. Fábio M. Costa Instituto de Informática Universidade Federal de Goiás

Roteiro Processadores Memória primária Memória secundária Entrada e Saída (I/O) Conectados através de um (ou mais ) barramento(s) Um computador pode ser visto como um sistema interconectado consistindo de elementos das categorias acima 2 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

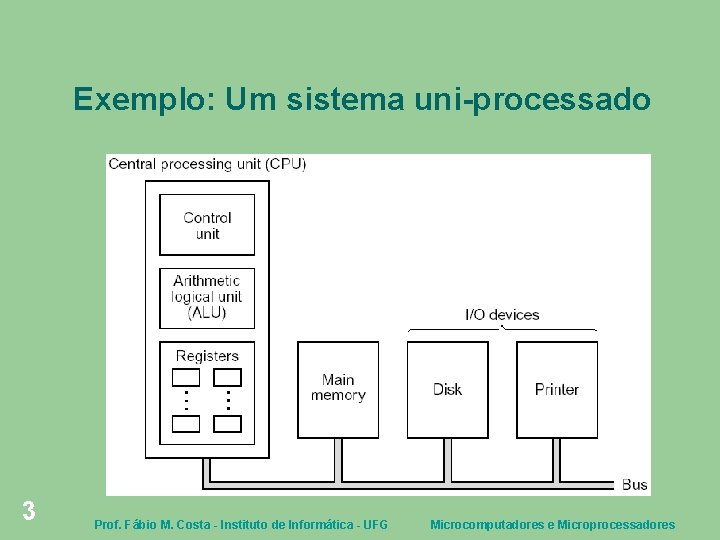

Exemplo: Um sistema uni-processado 3 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador – Unidade Central de Processamento (CPU) Executam programas armazenados na memória, instrução por instrução – Conectado através de barramentos aos demais componentes do sistema Barramento: – 4 busca, decodificação e execução uma coleção de “fios” paralelos, usados para transmitir dados, endereços e sinais de controle entre os componentes do sistema Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Componentes do processador Unidade de controle – – Unidade lógico-aritimética (ALU) – busca de instruções na memória decodificação das instruções (tipo, endereços, etc. ) realiza operações tais como adição, subtração, AND, OR, etc. Conjunto de registradores – memória de altíssima velocidade, usada para armazenamento temporário dos resultados de operações. Exemplos: 5 Program Counter (PC): endereço da próxima instrução Instruction Register (IR): contém a instrução sendo executada Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

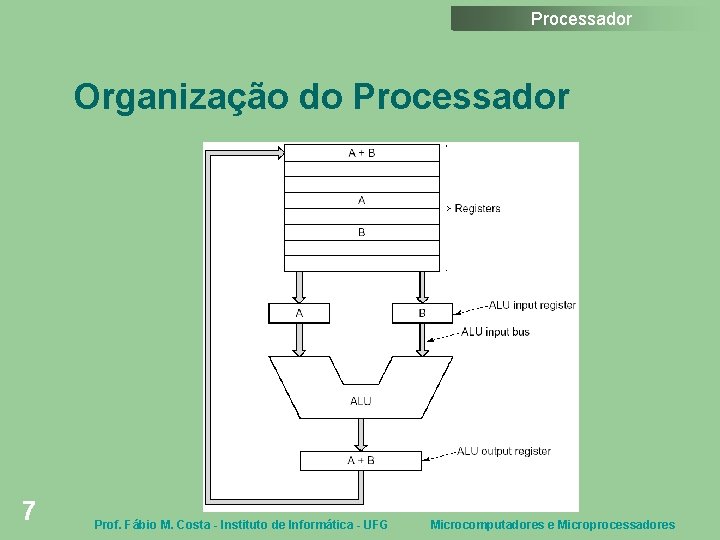

Processador Organização do Processador Data path (caminho de dados) – – Tipos de instruções – – registrador-memória: load, store registrador-registrador: add a, b Ciclo do caminho de dados (data path cycle) – 6 Registradores ALU Barramentos internos Execução controlada por instruções de máquina carga dos operandos na ALU, processamento, e armazenamento do resultado Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Organização do Processador 7 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

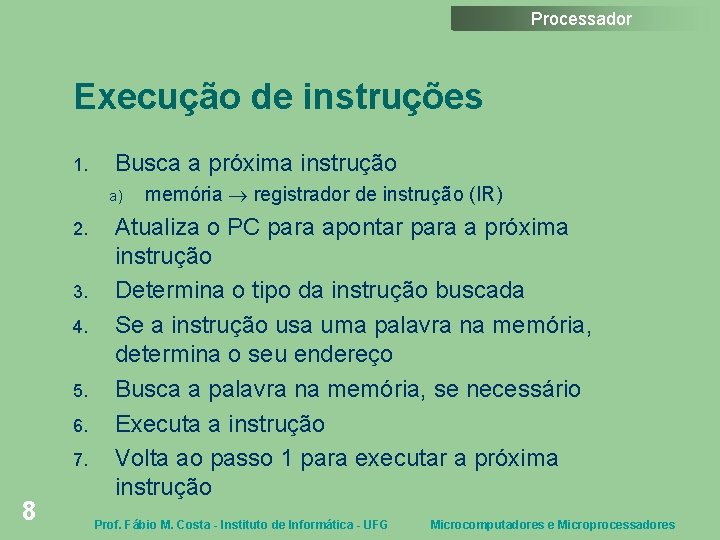

Processador Execução de instruções 1. Busca a próxima instrução a) 2. 3. 4. 5. 6. 7. 8 memória registrador de instrução (IR) Atualiza o PC para apontar para a próxima instrução Determina o tipo da instrução buscada Se a instrução usa uma palavra na memória, determina o seu endereço Busca a palavra na memória, se necessário Executa a instrução Volta ao passo 1 para executar a próxima instrução Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

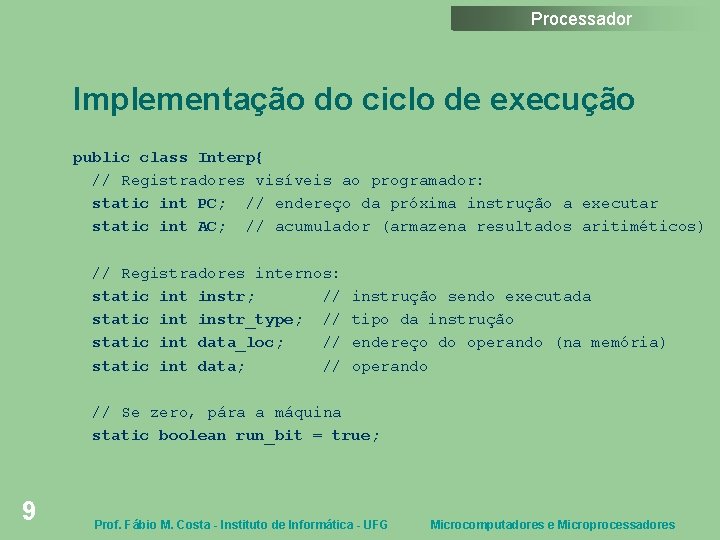

Processador Implementação do ciclo de execução public class Interp{ // Registradores visíveis ao programador: static int PC; // endereço da próxima instrução a executar static int AC; // acumulador (armazena resultados aritiméticos) // Registradores internos: static int instr; // static int instr_type; // static int data_loc; // static int data; // instrução sendo executada tipo da instrução endereço do operando (na memória) operando // Se zero, pára a máquina static boolean run_bit = true; 9 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

![Processador Implementação do ciclo de execução 10 public static void interpret(int memory[], int starting Processador Implementação do ciclo de execução 10 public static void interpret(int memory[], int starting](http://slidetodoc.com/presentation_image_h2/1615a56937edcfb3e6e45c1a4f73598a/image-10.jpg)

Processador Implementação do ciclo de execução 10 public static void interpret(int memory[], int starting address){ PC = starting_address; while (run_bit) { instr = memory[PC]; PC = PC + 1; instr_type = get_instr_type(instr); data_loc = find_data(instr, instr_type); if (data_loc >= 0) data = memory[data_loc]; execute(instr_type, data); } } private static int get_instr_type(int addr) {. . . } private static int find_data(int instr, int type) {. . . } private static void execute(int type, int data) {. . . } } Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

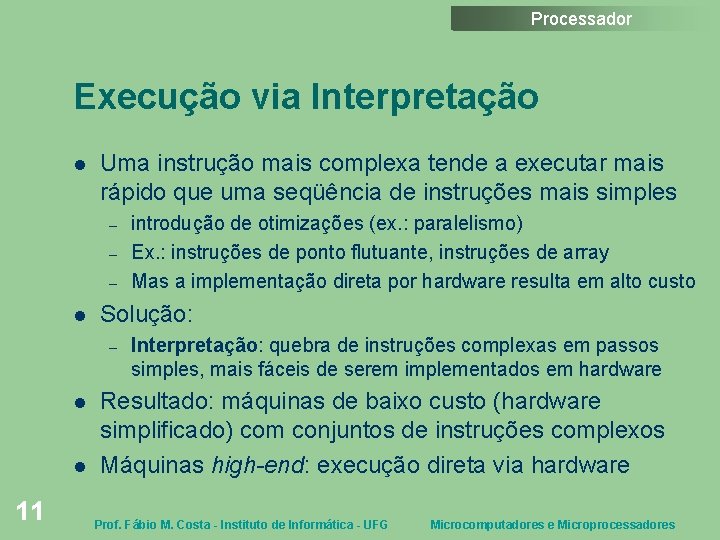

Processador Execução via Interpretação Uma instrução mais complexa tende a executar mais rápido que uma seqüência de instruções mais simples – – – Solução: – 11 introdução de otimizações (ex. : paralelismo) Ex. : instruções de ponto flutuante, instruções de array Mas a implementação direta por hardware resulta em alto custo Interpretação: quebra de instruções complexas em passos simples, mais fáceis de serem implementados em hardware Resultado: máquinas de baixo custo (hardware simplificado) com conjuntos de instruções complexos Máquinas high-end: execução direta via hardware Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Execução via Interpretação (2) Interpretador Hardware 12 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Execução via Interpretação: Benefícios Facilidade para corrigir instruções implementadas incorretamente Possibilidade de corrigir (ou contornar) deficiências no hardware básico Facilidade de adicionar novas instruções Permite aplicar técnicas de projeto estruturado: – 13 maior eficiência: desenvolvimento, testes e documentação Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Execução via Interpretação: Terminologia Interpretador: micro-programa (micro-código) Memória onde o micro-programa fica armazenado: memória de controle – Passos mais simples para decomposição das instruções: micro-instruções – – 14 ROM de alta velocidade, geralmente localizada dentro do processador instruções no nível da micro-arquitetura usadas para decompor instruções de máquina Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador RISC versus CISC RISC = computadores com conjunto de instruções reduzido – CISC = computadores com conjunto de instruções complexo – execução por interpretação (software) Tendência para RISC – 15 execução direta por hardware Máquinas CISC (e seus micro-programas) se tornaram muito complexas, ao ponto de penalizar a eficiência de execução Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador RISC Instruções simples – Principal argumento (exemplo): – – – 4 instruções RISC para fazer o trabalho de 1 instrução CISC é 10 vezes mais rápida resultado final: RISC é mais rápido Fatores dominantes na prática: – – – 16 executáveis em um único ciclo do data path simplicidade de cada instrução individual (não o tamanho do conjunto de instruções em si) velocidade da memória de controle em relação à memória principal emprego de técnicas de otimização inovadoras Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Princípios modernos de projeto Amplamente influenciados pela “escola” RISC Baseados em suposições sobre a base tecnológica atual – Atualmente adotados também no projeto de máquinas CISC – 17 Ex. : desempenho do processador em relação à memória principal Implementações híbridas Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Princípios modernos de projeto 18 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

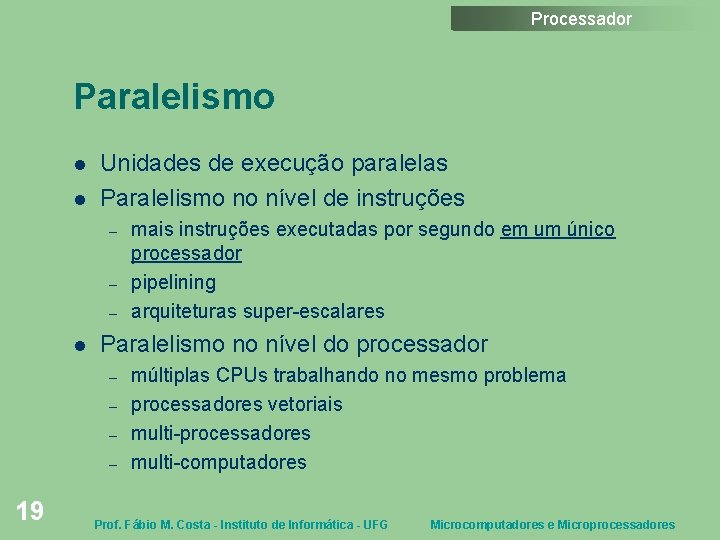

Processador Paralelismo Unidades de execução paralelas Paralelismo no nível de instruções – – – Paralelismo no nível do processador – – 19 mais instruções executadas por segundo em um único processador pipelining arquiteturas super-escalares múltiplas CPUs trabalhando no mesmo problema processadores vetoriais multi-processadores multi-computadores Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

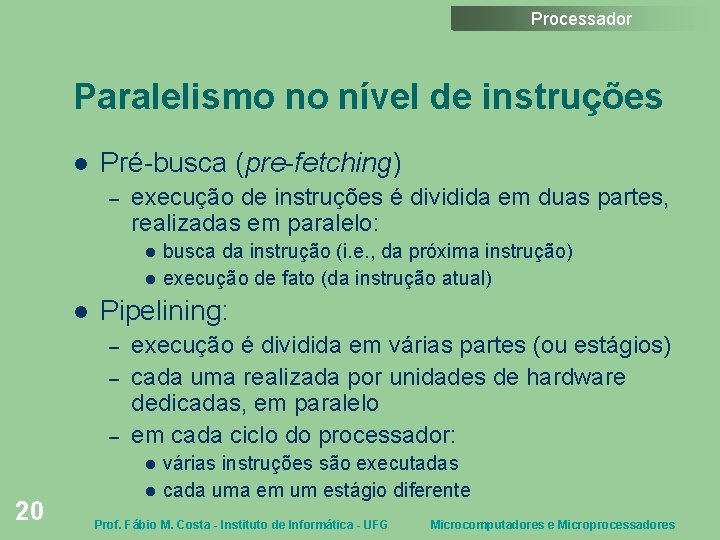

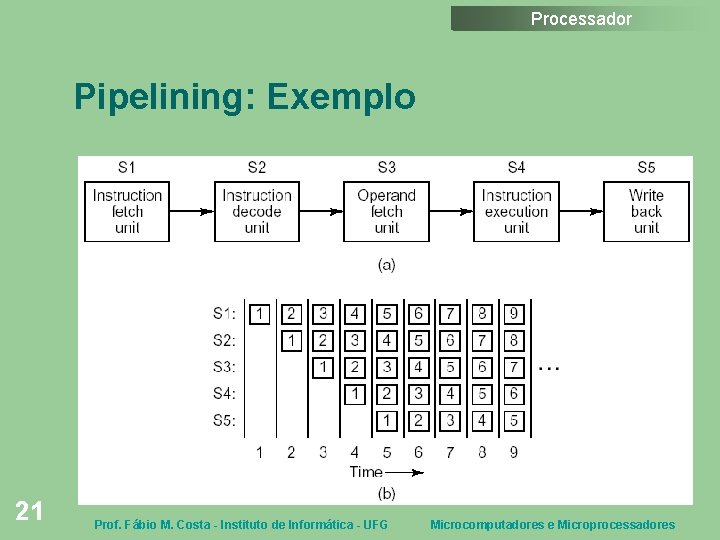

Processador Paralelismo no nível de instruções Pré-busca (pre-fetching) – execução de instruções é dividida em duas partes, realizadas em paralelo: Pipelining: – – – execução é dividida em várias partes (ou estágios) cada uma realizada por unidades de hardware dedicadas, em paralelo em cada ciclo do processador: 20 busca da instrução (i. e. , da próxima instrução) execução de fato (da instrução atual) várias instruções são executadas cada uma em um estágio diferente Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Pipelining: Exemplo 21 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Pipelining: Exemplo 1 22 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Pipelining: Análise de eficiência Exemplo – – ciclo de máquina: 2 ns execução de cada instrução com cinco estágios de pipeline: 10 ns – mas uma vez que o pipeline está “cheio” (i. e. , todos os estágios estão executando em paralelo): uma instrução é completada a cada 2 ns resultado: 500 MIPS Latência (atraso inicial) X Largura de Banda da CPU – 23 aparentemente: 100 MIPS: milhões de instruções por segundo – n estágios, com tempo de ciclo = T latência = n. T Largura de banda (ou throughput) = 1000/T MIPS Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

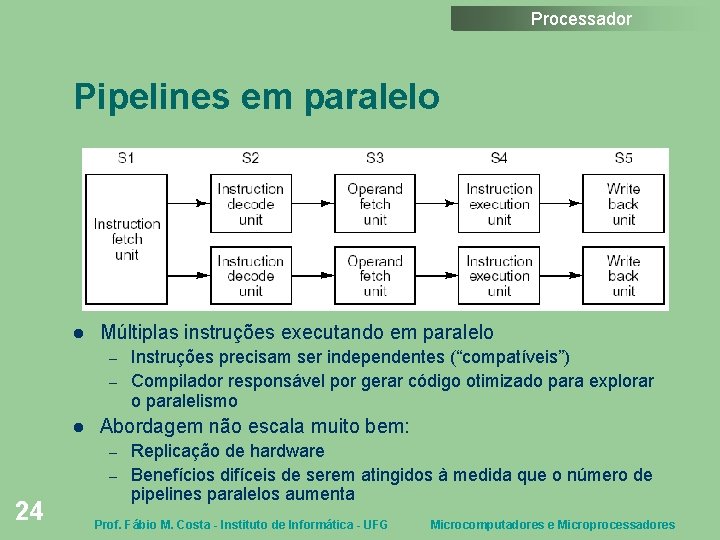

Processador Pipelines em paralelo Múltiplas instruções executando em paralelo – – Abordagem não escala muito bem: – – 24 Instruções precisam ser independentes (“compatíveis”) Compilador responsável por gerar código otimizado para explorar o paralelismo Replicação de hardware Benefícios difíceis de serem atingidos à medida que o número de pipelines paralelos aumenta Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

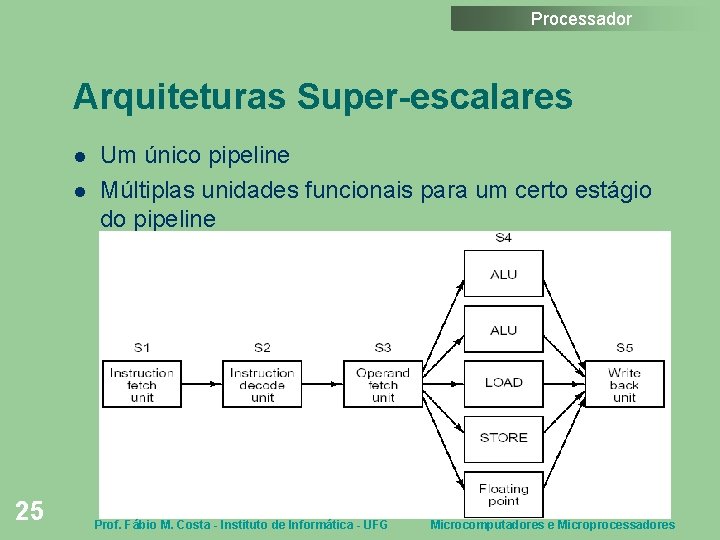

Processador Arquiteturas Super-escalares 25 Um único pipeline Múltiplas unidades funcionais para um certo estágio do pipeline Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Paralelismo no nível do processador Limitações físicas: – – Parelelismo no nível de instruções: – Ganhos de desempenho: 5 a 10 vezes Para obter ganhos maiores: – 26 Velocidade da luz Super-aquecimento do processador Computadores com múltiplas CPUs rodando em paralelo Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

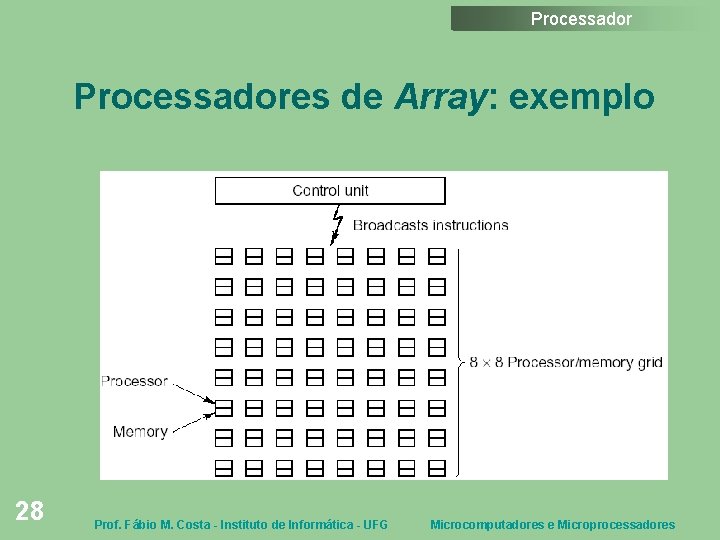

Processadores de Array Múltiplos processadores idênticos – Cada um operando em um subconjunto dos dados do problema – – Resultados são combinados ao final Uma unidade de controle central Aplicável a problemas do tipo “matricial” – ou que possam ser interpretados como tal 27 A mesma instrução é executada por toods os processadores isto é: cujo conjunto de dados possa ser particionado em subconjuntos independentes para serem processados em paralelo SIMD – Single Instruction, Multiple Data Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processadores de Array: exemplo 28 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

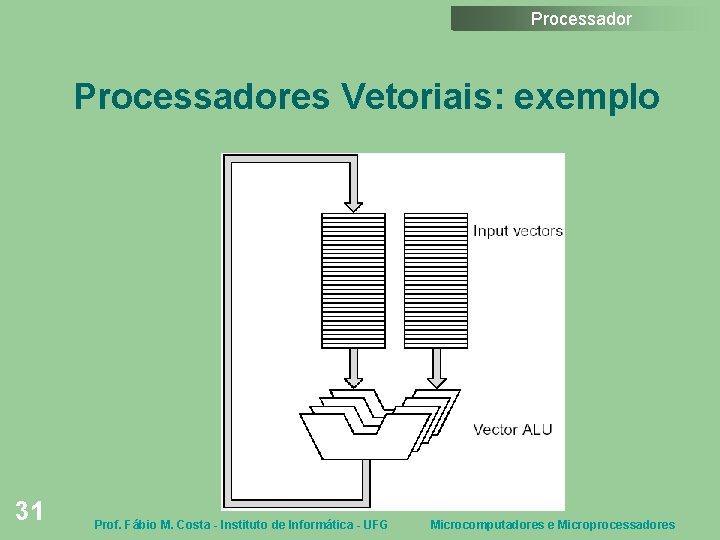

Processadores Vetoriais Também voltado para o processamento de problemas matriciais Paralelismo dentro da ALU – Registradores vetoriais – ALU vetorial: implementada através de pipelining Capazes de armazenar os múltiplos elementos de um vetor Instruções vetoriais – Aritiméticas 29 – Vetor-vetor, vetor-escalar Carga e armazenamento de vetores na memória Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processadores de Array e Vetoriais: Comparação Array: – – – Vetorial: – – – 30 1 processador para cada elemento da matriz Altamente especializados: inapropriados para problemas não matriciais Requer técnicas sofisticadas de programação/compilação para explorar o paralelismo Um único processador com paralelismo no nível de instruções (pipelining) operando em registradores vetoriais Mais flexíveis: bom desempenho em problemas híbridos (escalar X vetorial), sem muito desperdício de hardware Mais simples de se programar Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processadores Vetoriais: exemplo 31 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

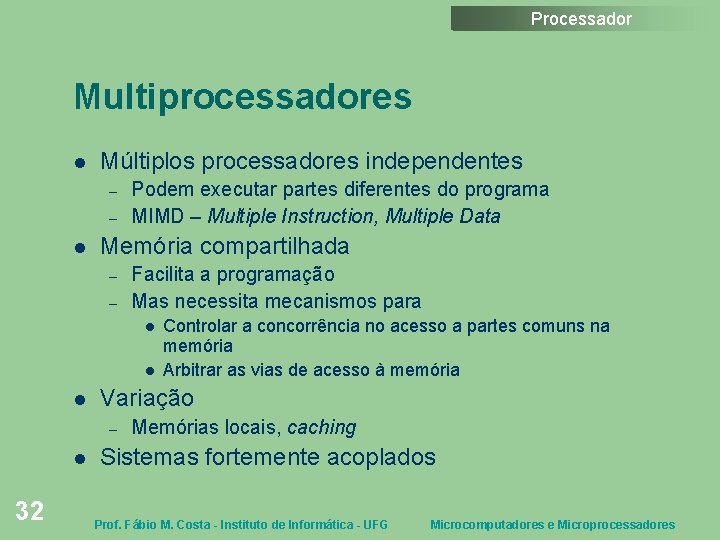

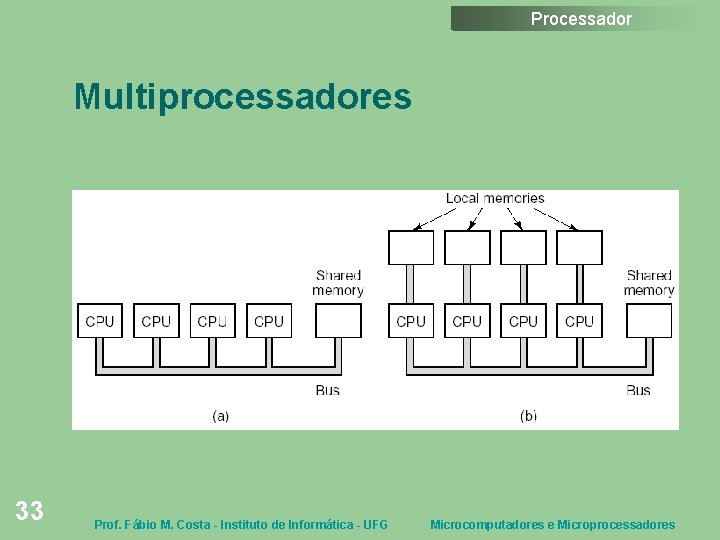

Processador Multiprocessadores Múltiplos processadores independentes – – Podem executar partes diferentes do programa MIMD – Multiple Instruction, Multiple Data Memória compartilhada – – Facilita a programação Mas necessita mecanismos para Variação – 32 Controlar a concorrência no acesso a partes comuns na memória Arbitrar as vias de acesso à memória Memórias locais, caching Sistemas fortemente acoplados Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Multiprocessadores 33 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Processador Multi-computadores Computadores independentes (CPU + memória) interconectados – – Conexões de alta velocidade Sem memória compartilhada – – Comunicação por passagem de mensagens Sistemas fracamente acoplados Maior escalabilidade – 34 Embora possa ser simulada para facilitar a programação Não necessita arbitrar o acesso à memória compartilhada Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Armazenamento de dados e programas – Unidade de armazenamento: Bit – – Valores: 0 ou 1 Representado através da distinção de dois níveis diferentes de valores de alguma quantidade física; Ex. : voltagem Vantagens do sistema binário – – 35 diretamente acessível ao processador Facilidade de representação em sistemas eletrônicos Confiabilidade Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

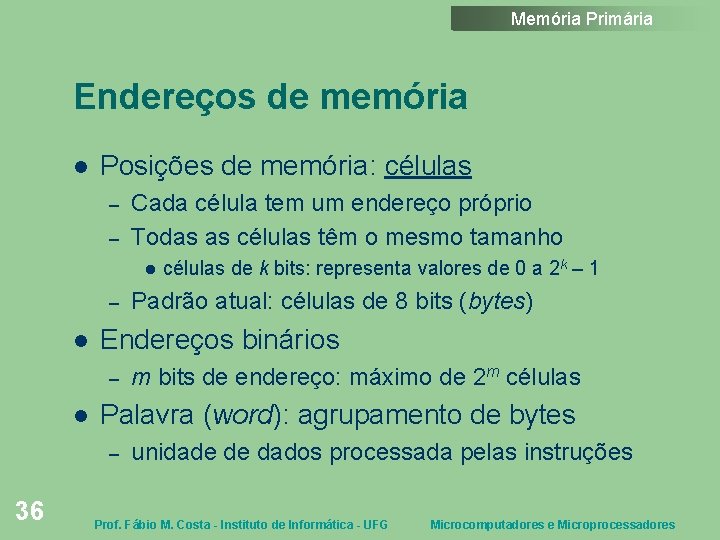

Memória Primária Endereços de memória Posições de memória: células – – Cada célula tem um endereço próprio Todas as células têm o mesmo tamanho – m bits de endereço: máximo de 2 m células Palavra (word): agrupamento de bytes – 36 Padrão atual: células de 8 bits (bytes) Endereços binários – células de k bits: representa valores de 0 a 2 k – 1 unidade de dados processada pelas instruções Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Endereços de memória (2) Figura 2. 9 37 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

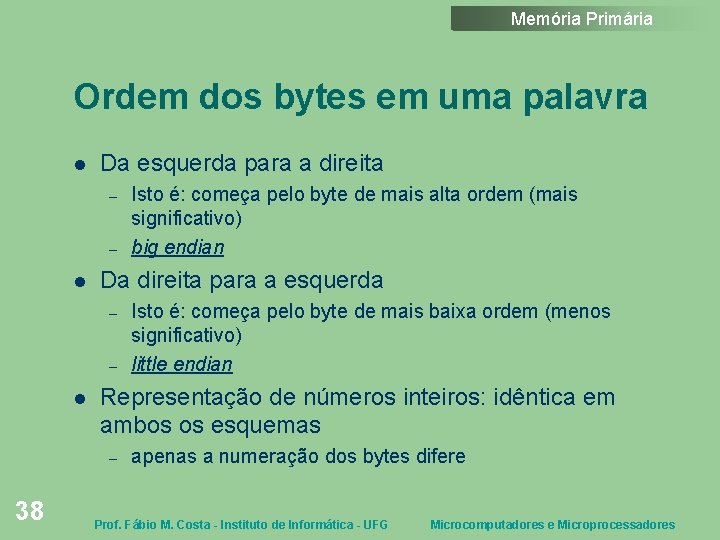

Memória Primária Ordem dos bytes em uma palavra Da esquerda para a direita – – Da direita para a esquerda – – Isto é: começa pelo byte de mais baixa ordem (menos significativo) little endian Representação de números inteiros: idêntica em ambos os esquemas – 38 Isto é: começa pelo byte de mais alta ordem (mais significativo) big endian apenas a numeração dos bytes difere Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

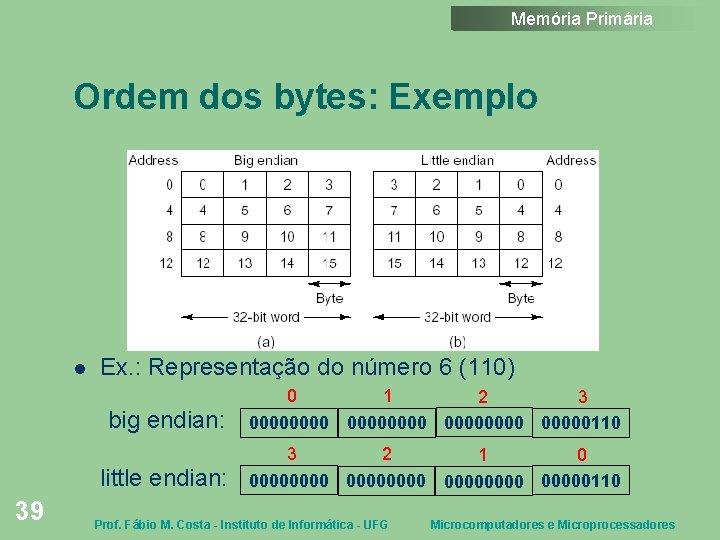

Memória Primária Ordem dos bytes: Exemplo Figura 2. 11 39 Ex. : Representação do número 6 (110) big endian: 1 0 2 3 00000000 00000110 little endian: 2 3 1 0 00000000 00000110 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Ordem dos bytes: Problema Quando se representa vários tipos de dados diferentes – – – 40 Ex. : inteiros e cadeias de caracteres Apenas inverter a ordem dos bytes não é suficiente O que fazer então? Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

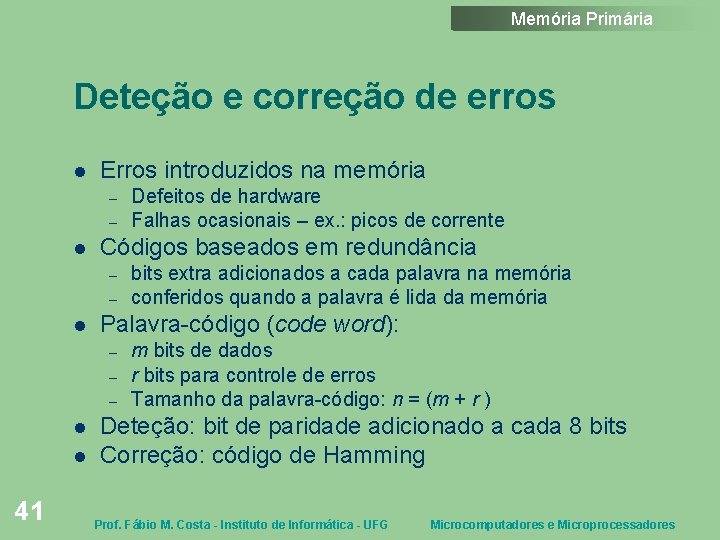

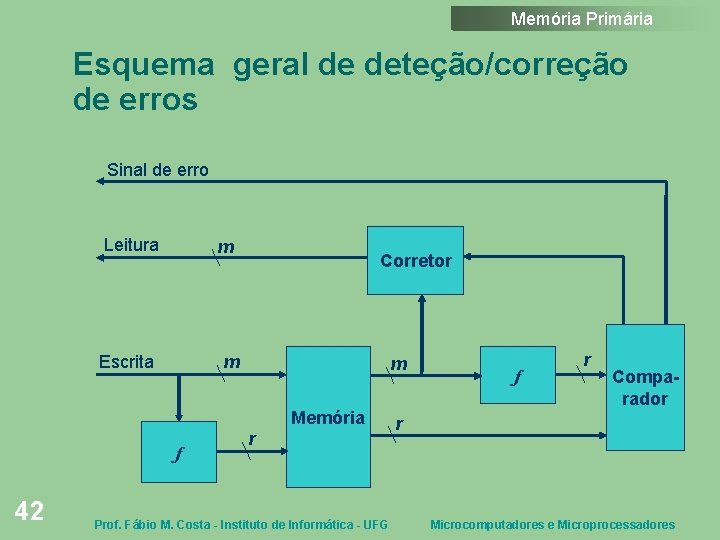

Memória Primária Deteção e correção de erros Erros introduzidos na memória – – Códigos baseados em redundância – – 41 bits extra adicionados a cada palavra na memória conferidos quando a palavra é lida da memória Palavra-código (code word): – Defeitos de hardware Falhas ocasionais – ex. : picos de corrente m bits de dados r bits para controle de erros Tamanho da palavra-código: n = (m + r ) Deteção: bit de paridade adicionado a cada 8 bits Correção: código de Hamming Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Esquema geral de deteção/correção de erros Sinal de erro Leitura m Escrita Corretor m m Memória f 42 r Prof. Fábio M. Costa - Instituto de Informática - UFG f r Comparador r Microcomputadores e Microprocessadores

Memória Primária Cache: Problema a ser resolvido Requisitos para a memória principal: – – Resultado: memórias lentas (em relação à CPU) Exemplo: – – Tempo de acesso à memória: 10 ciclos de clock Processador ficará parado até concluir o acesso Solução simples: – – 43 Baixo custo Alta capacidade Processador continua executando até chegar a uma instrução que necessite fazer acesso à memória Não é suficiente Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Cache: Princípio básico Combinar – – Resultado: – – – 44 uma pequena quantidade de memória rápida, mas de alto custo (cache) uma grande quantidade de memória lenta e de baixo custo Grande capacidade de memória Rapidez de acesso Custo moderado Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Cache 45 Pequena quantidade de memória rápida Fica entre a memória principal e a CPU Geralmente localizada dentro do chip da CPU Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Cache: Operação CPU requisita o conteúdo de uma posição de memória Se os dados já estão na cache (“acerto”) – obtém os dados a partir da cache (acesso rápido) Senão (“perda”) – lê um bloco inteiro de dados da memória principal – 46 Bloco definido pela vizinhança da posição de memória solicitada Bloco = linha da cache Retorna os dados da cache para a CPU Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Cache: Princípio da Localidade Programas não acessam endereços de memória (para dados ou código) de forma aleatória – Aumenta a taxa de acerto – 47 Há grande probabilidade de que a próxima palavra requisitada pela CPU esteja na “vizinhança” da palavra lida anteriormente Uma vez que o conteúdo da memória nos endereços vizinhos já se encontra na cache Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Cache: Aspectos de projeto Tamanho da cache Tamanho das linhas da cache Mapeamento da cache para os endereços na memória principal Consistência entre cache e memória principal Cache unificada x caches especializadas – – 48 Cache de instruções Cache de dados Número de caches em um sistema Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Tipos memória (Packaging) Chips de memória montados em uma pequena placa de circuito impresso – Ex. : SIMM de 128 MB 49 8 chips de 128 megabits cada Sem suporte para deteção e correção de erros – SIMM (Single Inline Memory Module) DIMM (Dual Inline Memory Module) SO-DIMM (Small Outline DIMM) i. e. , sem paridade Tipicamente: 4 slots para módulos de memória Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Tipos de memórias: SIMMs SIMM de 30 pinos • 8 bits por acesso SIMM de 72 pinos • 32 bits por acesso 50 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Primária Tipos de memórias: DIMMs 51 84 conectores em cada lado: 168 conectores Capaz de transferir 64 bits de cada vez Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária Hierarquias de memória Discos magnéticos – – Discos óticos – – – 52 Discos flexíveis (floppy disks) Discos IDE Discos SCSI RAID CD-ROM CD-R e CD-RW DVD, DVD-R, DVD+R, DVD-RW, DVD+RW, DVD -RAM Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

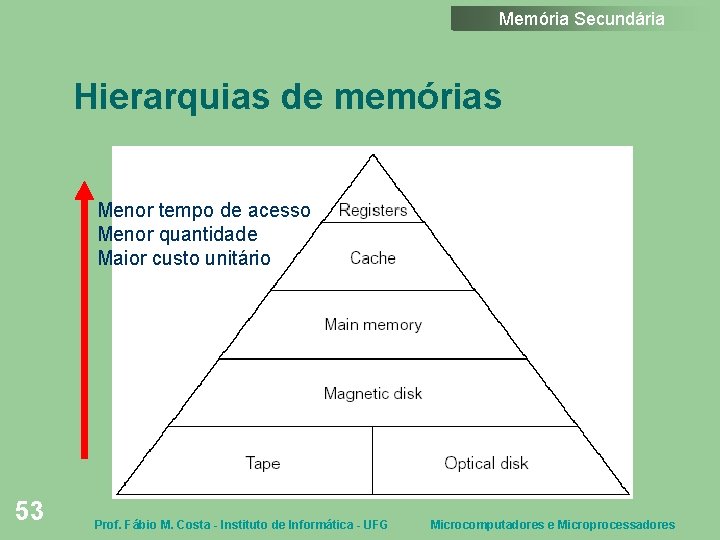

Memória Secundária Hierarquias de memórias Menor tempo de acesso Menor quantidade Maior custo unitário 53 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

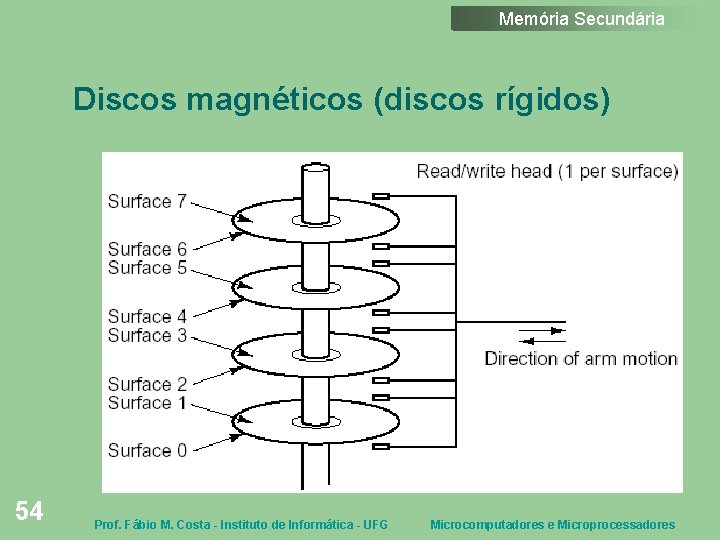

Memória Secundária Discos magnéticos (discos rígidos) 54 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

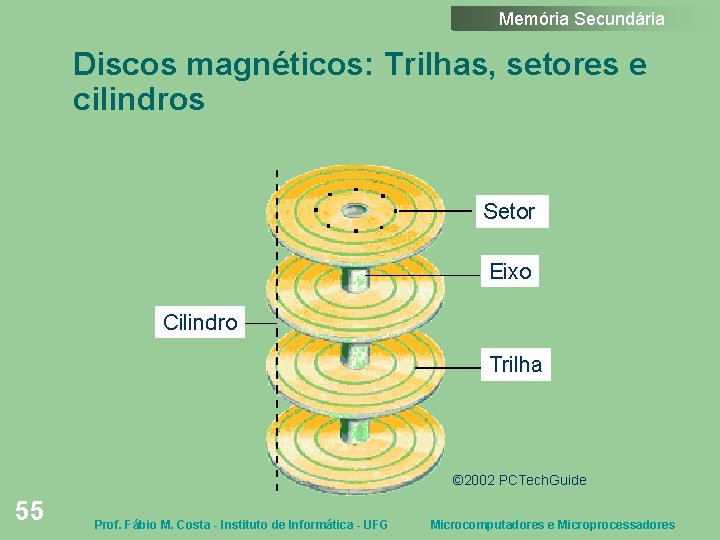

Memória Secundária Discos magnéticos: Trilhas, setores e cilindros Setor Eixo Cilindro Trilha © 2002 PCTech. Guide 55 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária Discos magnéticos: Geometria típica de trilhas e setores Preâmbulo: sincronização da cabeça Lacunas – – 56 entre setores: amenizam a necessidade de alta precisão da cabeça entre trilhas: reduzem interferência magnética Código de correção de erros (ECC): Reed-Solomon Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

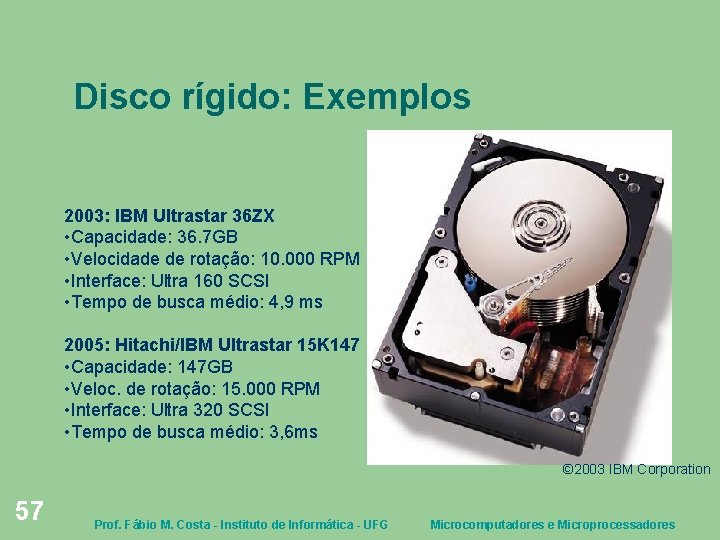

Disco rígido: Exemplos 2003: IBM Ultrastar 36 ZX • Capacidade: 36. 7 GB • Velocidade de rotação: 10. 000 RPM • Interface: Ultra 160 SCSI • Tempo de busca médio: 4, 9 ms 2005: Hitachi/IBM Ultrastar 15 K 147 • Capacidade: 147 GB • Veloc. de rotação: 15. 000 RPM • Interface: Ultra 320 SCSI • Tempo de busca médio: 3, 6 ms © 2003 IBM Corporation 57 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária Discos magnéticos: Tempos de acesso Tempo de busca – Latência rotacional – 58 Tempo para o setor desejado passar sob a cabeça de leitura/escrita Tempo de transferência – Posicionamento da cabeça na trilha correta Função da densidade linear e da velocidade de rotação Demanda otimização da ocupação do disco Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária Controladora de disco Aceita comandos de software – READ, WRITE, FORMAT Traduz estes comandos em ações – – – Controle dos movimentos das cabeças Deteção e correção de erros Bufferização de múltiplos setores Caching de setores para acesso rápido Remapeamento de setores 59 Quando o setor original se torna defeituoso Substituído por um setor sobressalente no cilindro Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária Discos flexíveis Geometria semelhante a discos rígidos – 60 Apenas dois cilindros Cabeça de leitura/escrita em contato com a superfície do disco Rotação é interrompida quando não em uso Maior atraso inicial Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

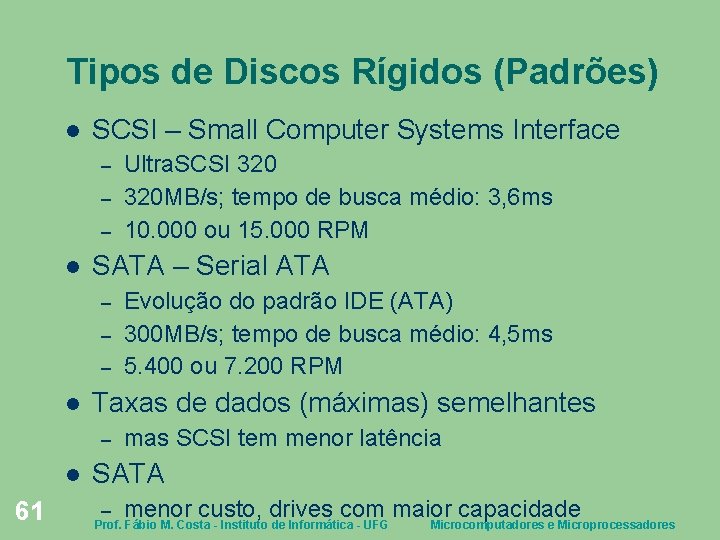

Tipos de Discos Rígidos (Padrões) SCSI – Small Computer Systems Interface – – – SATA – Serial ATA – – – 61 Evolução do padrão IDE (ATA) 300 MB/s; tempo de busca médio: 4, 5 ms 5. 400 ou 7. 200 RPM Taxas de dados (máximas) semelhantes – Ultra. SCSI 320 MB/s; tempo de busca médio: 3, 6 ms 10. 000 ou 15. 000 RPM mas SCSI tem menor latência SATA – menor custo, drives com maior capacidade Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

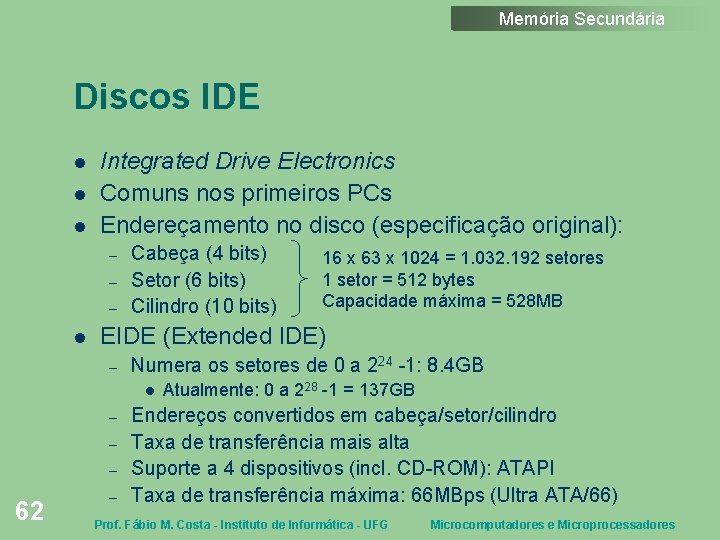

Memória Secundária Discos IDE Integrated Drive Electronics Comuns nos primeiros PCs Endereçamento no disco (especificação original): – – – Cabeça (4 bits) Setor (6 bits) Cilindro (10 bits) EIDE (Extended IDE) – Numera os setores de 0 a 224 -1: 8. 4 GB – – – 62 16 x 63 x 1024 = 1. 032. 192 setores 1 setor = 512 bytes Capacidade máxima = 528 MB – Atualmente: 0 a 228 -1 = 137 GB Endereços convertidos em cabeça/setor/cilindro Taxa de transferência mais alta Suporte a 4 dispositivos (incl. CD-ROM): ATAPI Taxa de transferência máxima: 66 MBps (Ultra ATA/66) Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

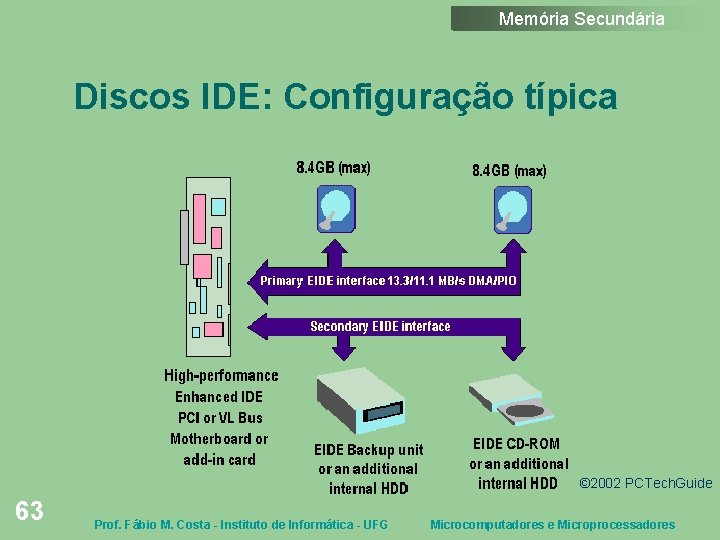

Memória Secundária Discos IDE: Configuração típica © 2002 PCTech. Guide 63 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

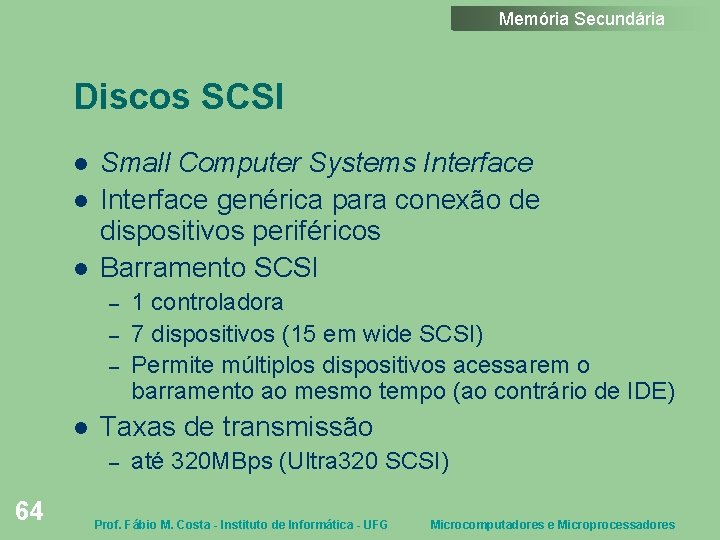

Memória Secundária Discos SCSI Small Computer Systems Interface genérica para conexão de dispositivos periféricos Barramento SCSI – – – Taxas de transmissão – 64 1 controladora 7 dispositivos (15 em wide SCSI) Permite múltiplos dispositivos acessarem o barramento ao mesmo tempo (ao contrário de IDE) até 320 MBps (Ultra 320 SCSI) Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

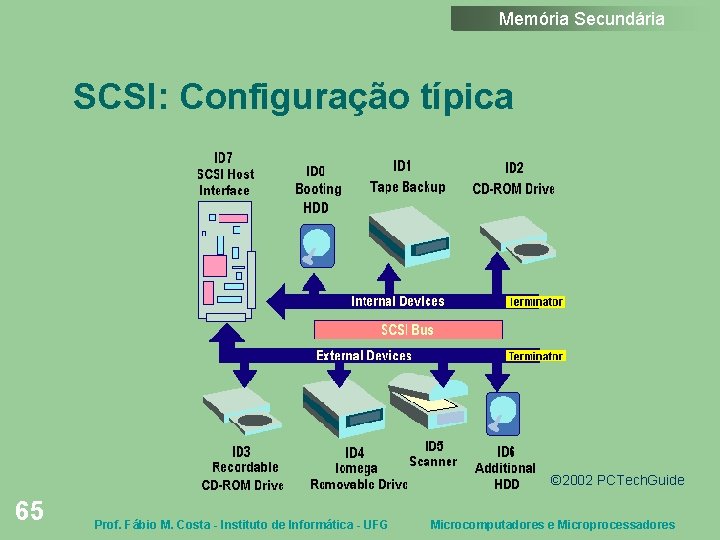

Memória Secundária SCSI: Configuração típica © 2002 PCTech. Guide 65 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária RAID 66 Redundant Array of Inexpensive Disks Uso de vários discos (tipicamente SCSI) em paralelo Controladora RAID dá a ilusão de um único disco virtual Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária RAID nível 0 Divide os setores do disco virtual em faixas de k setores cada Faixas são escritas nos discos físicos em round robin Leitura de grandes blocos de dados – 67 I/O paralela: cada disco contribui com uma ou mais faixas Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária RAID nível 1 Duplica a configuração do RAID nível 0 – 68 Drives de backup Melhor tolerância a falhas Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária RAID nível 2 Cada bit de uma palavra é escrito em um disco físico separado Juntamente com bits de paridade para compor o código de Hamming da palavra – Correção de erros 69 Ex. : se um disco quebrar Throughput elevado Todos os discos devem estar sincronizados Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária RAID nível 3 Versão simplificada de RAID nível 2 Um bit de paridade é adicionado a cada palavra – Apenas um disco extra é necessário Correção de erros – Em caso de quebra de um disco, a posição do bit em “erro” é conhecida 70 Então: bit de paridade é suficiente para a correção Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária RAID nível 4 Semelhante ao RAID nível 0 Um disco extra é usado para guardar a paridade das faixas dos outros discos Permite corrigir erros causados pela quebra de um disco Desempenho baixo para escrita de pequenas quantidades de dados – 71 Cálculo da paridade envolvendo todos os discos Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária RAID nível 5 Semelhante ao RAID nível 5 Distribui as faixas de paridade entre os discos – 72 Em ordem round robin Difícil reconstituir o conteúdo de um disco em caso de falha Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Memória Secundária Leitura 73 CD-ROMs – 2. 3. 7 CD-Recordable (CD-R) – 2. 3. 8 CD-Rewritable (CD-RW) – 2. 3. 9 DVD – 2. 3. 10 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Entrada e Saída (I/O) Barramentos Terminais – – – 74 Teclados Monitores CRT Monitores LCD Terminais de caracteres Terminais de bit-map Terminais RS-232 -C Mouse Impressoras Modems Códigos de caracteres Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

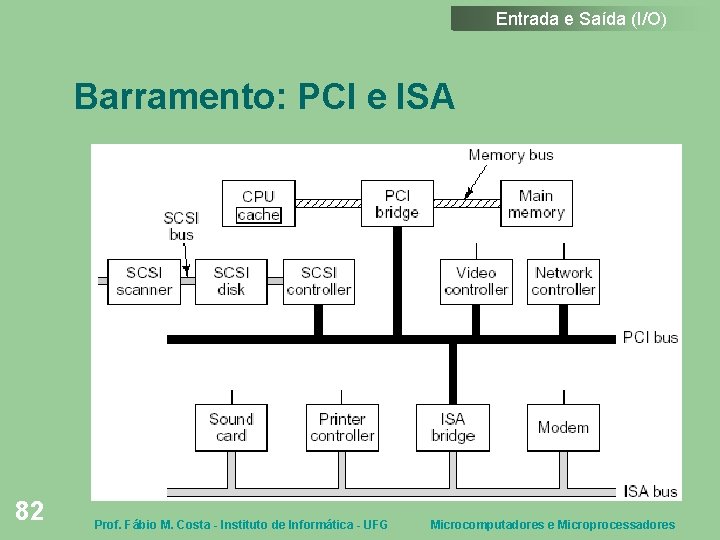

Barramento Conjunto de “fios” em paralelo Localizado na placa-mãe Conecta os dispositivos de I/O à CPU Slots com soquetes para conexão dos dispositivos – Tipos comuns de barramentos – – 75 Pontos de acesso ao barramento ISA PCI Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

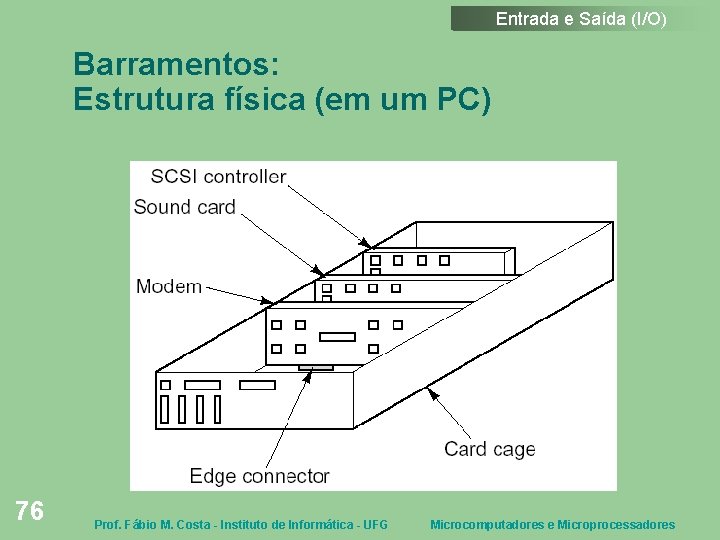

Entrada e Saída (I/O) Barramentos: Estrutura física (em um PC) 76 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

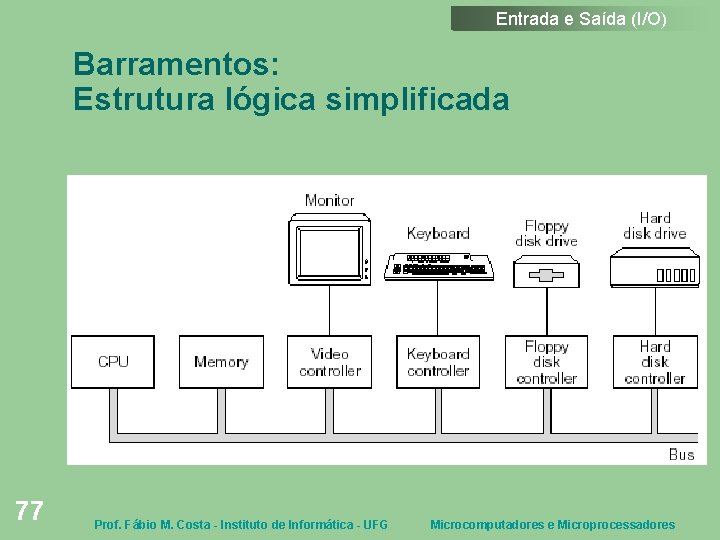

Entrada e Saída (I/O) Barramentos: Estrutura lógica simplificada 77 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

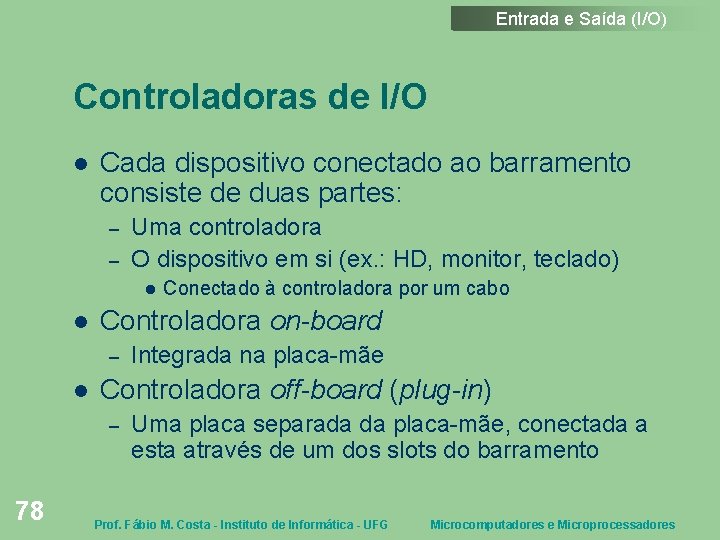

Entrada e Saída (I/O) Controladoras de I/O Cada dispositivo conectado ao barramento consiste de duas partes: – – Uma controladora O dispositivo em si (ex. : HD, monitor, teclado) Controladora on-board – Integrada na placa-mãe Controladora off-board (plug-in) – 78 Conectado à controladora por um cabo Uma placa separada da placa-mãe, conectada a esta através de um dos slots do barramento Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

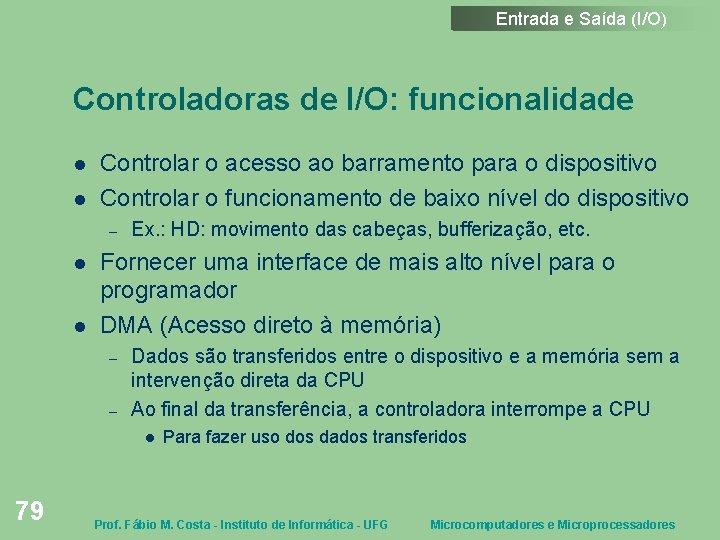

Entrada e Saída (I/O) Controladoras de I/O: funcionalidade Controlar o acesso ao barramento para o dispositivo Controlar o funcionamento de baixo nível do dispositivo – Ex. : HD: movimento das cabeças, bufferização, etc. Fornecer uma interface de mais alto nível para o programador DMA (Acesso direto à memória) – – Dados são transferidos entre o dispositivo e a memória sem a intervenção direta da CPU Ao final da transferência, a controladora interrompe a CPU 79 Para fazer uso dos dados transferidos Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

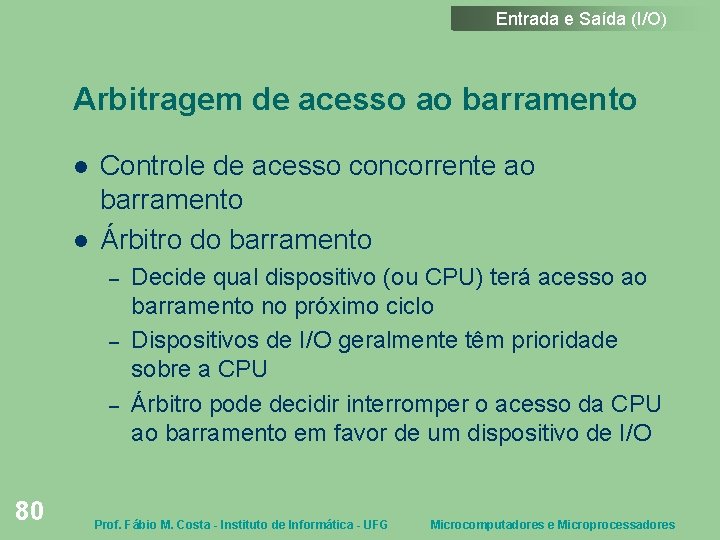

Entrada e Saída (I/O) Arbitragem de acesso ao barramento Controle de acesso concorrente ao barramento Árbitro do barramento – – – 80 Decide qual dispositivo (ou CPU) terá acesso ao barramento no próximo ciclo Dispositivos de I/O geralmente têm prioridade sobre a CPU Árbitro pode decidir interromper o acesso da CPU ao barramento em favor de um dispositivo de I/O Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

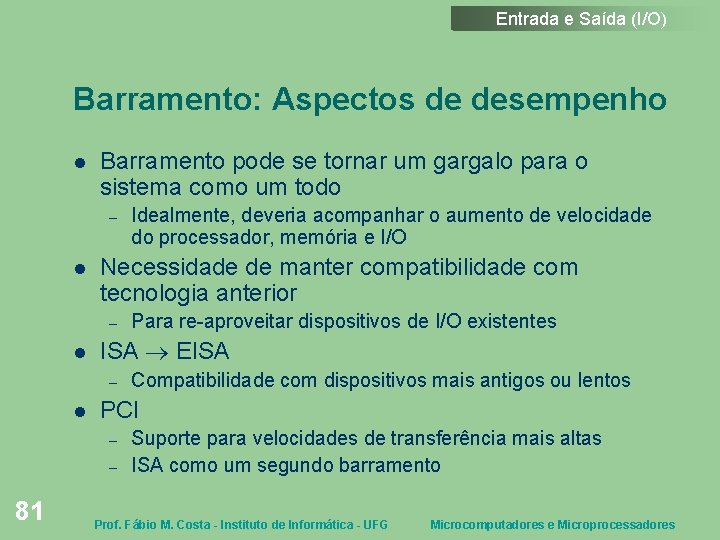

Entrada e Saída (I/O) Barramento: Aspectos de desempenho Barramento pode se tornar um gargalo para o sistema como um todo – Necessidade de manter compatibilidade com tecnologia anterior – Compatibilidade com dispositivos mais antigos ou lentos PCI – – 81 Para re-aproveitar dispositivos de I/O existentes ISA EISA – Idealmente, deveria acompanhar o aumento de velocidade do processador, memória e I/O Suporte para velocidades de transferência mais altas ISA como um segundo barramento Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Entrada e Saída (I/O) Barramento: PCI e ISA 82 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

Entrada e Saída (I/O) Leitura dirigida 83 Terminais – 2. 4. 2 Mouse – 2. 4. 3 Impressoras – 2. 4. 4 Modems – 2. 4. 5 Códigos de caracteres – 2. 4. 6 Prof. Fábio M. Costa - Instituto de Informática - UFG Microcomputadores e Microprocessadores

- Slides: 83