Optimization of Spanning Tree Adders Overview Compare designs

- Slides: 39

Optimization of Spanning Tree Adders 報告者 曾俊雄 賴韋志 巫祈賢

Overview Compare designs of spanning tree adders in terms of l l l delay complexity power consumption l Spanning tree adders is an existing category of adders, this paper does not focus on inventing new spanning tree adders but performing experiments on several possible configuration of spanning tree adders.

Introduction to several adders Why spanning tree adders are needed? Experimental result Conclusion & future work

Agenda Introduction to Adders & Problem Statement Spanning Tree Adders Result & Conclusion

Introduction to Adders & Problem Statement Spanning Tree Adders Result & Conclusion

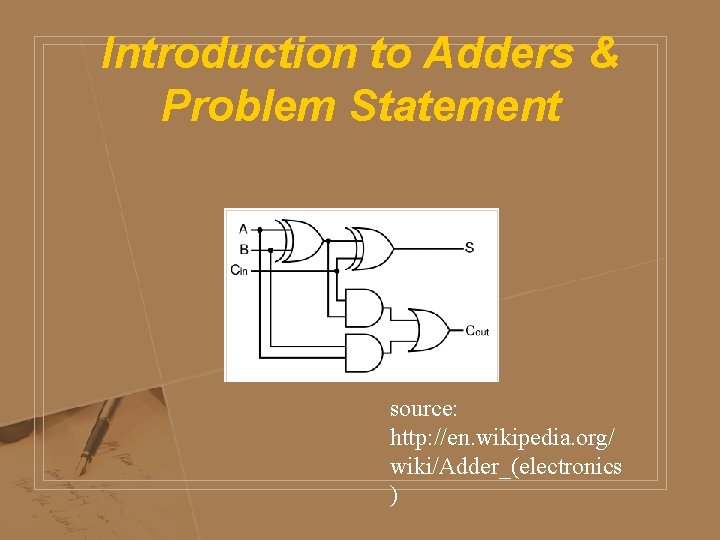

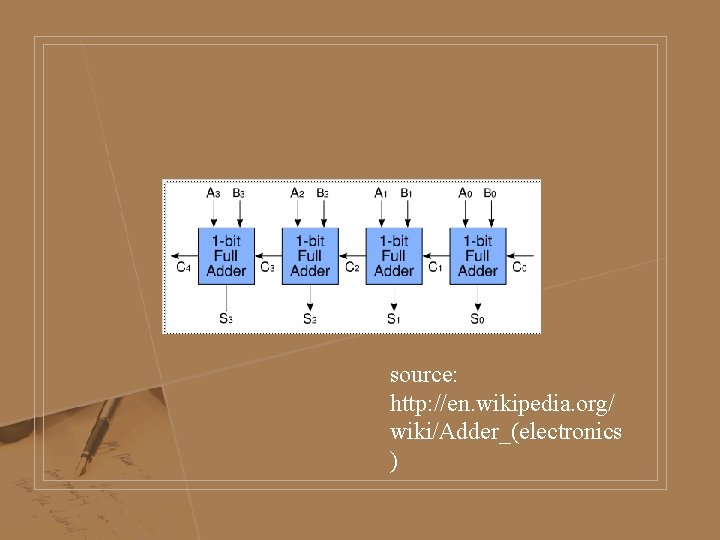

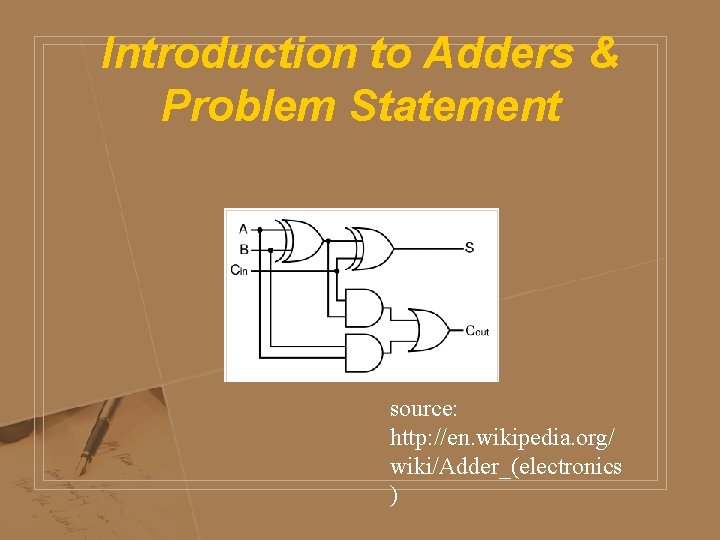

Introduction to Adders & Problem Statement source: http: //en. wikipedia. org/ wiki/Adder_(electronics )

Very brief introduction on several existing adders: l l ripple carry adders carry skip adders carry look ahead adders tree structured adders l l l Brent-Kung Spanning Tree Ling Han-Carlson Kogge-Stone

Very brief introduction on several existing adders: l l ripple carry adders carry skip adders carry look ahead adders tree structured adders l l l Brent-Kung Spanning Tree Ling Han-Carlson Kogge-Stone

Propagation Delay Basically, the performance of adders are evaluated with propagation delay (in this paper)

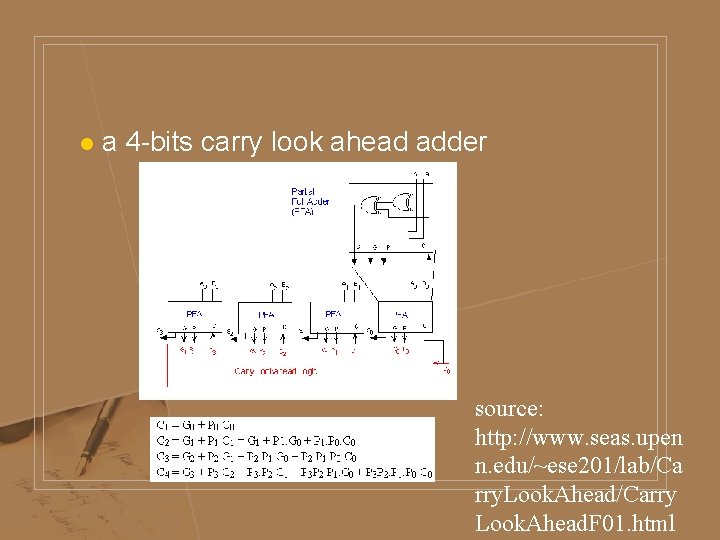

Propagation Delay: also called gate delay, the time difference between the change of input and output signals. source: http: //www. seas. upenn. edu/~ese 201/lab/Carry. L ook. Ahead/Carry. Look. A head. F 01. html

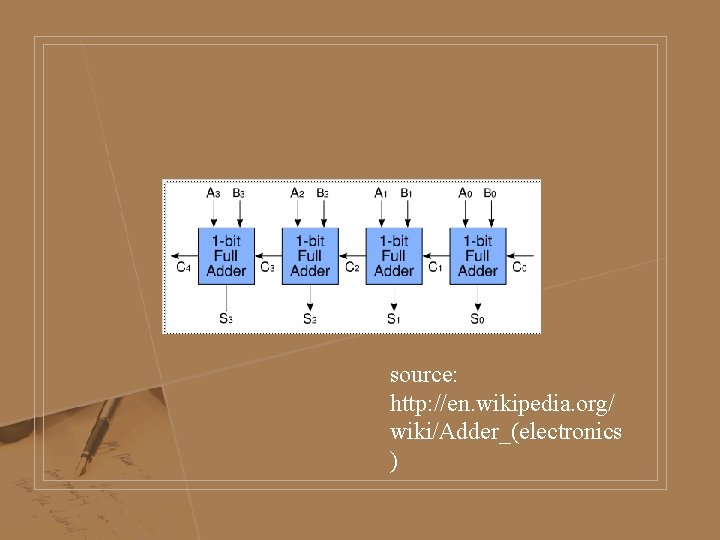

Ripple Carry Adders Goal: the adder should be able to compute the sum of more than 1 bits l Idea: just chain several adders together l

source: http: //en. wikipedia. org/ wiki/Adder_(electronics )

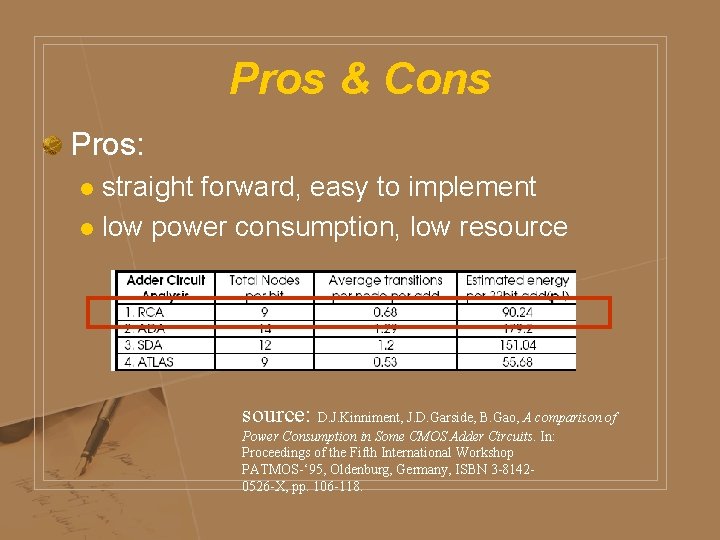

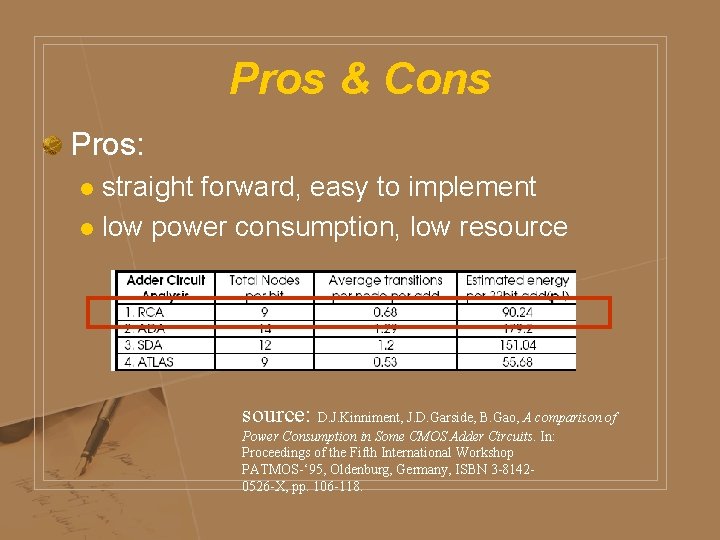

Pros & Cons Pros: straight forward, easy to implement l low power consumption, low resource l source: D. J. Kinniment, J. D. Garside, B. Gao, A comparison of Power Consumption in Some CMOS Adder Circuits. In: Proceedings of the Fifth International Workshop PATMOS-‘ 95, Oldenburg, Germany, ISBN 3 -81420526 -X, pp. 106 -118.

Cons: l slow (high propagation delay) l a 32 -bits adder requires 31 carry computations source: http: //en. wikipedia. org/ wiki/Adder_(electronics )

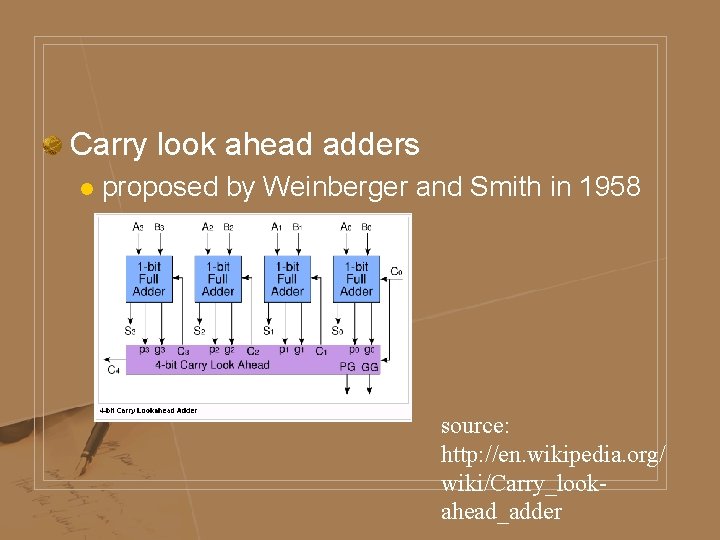

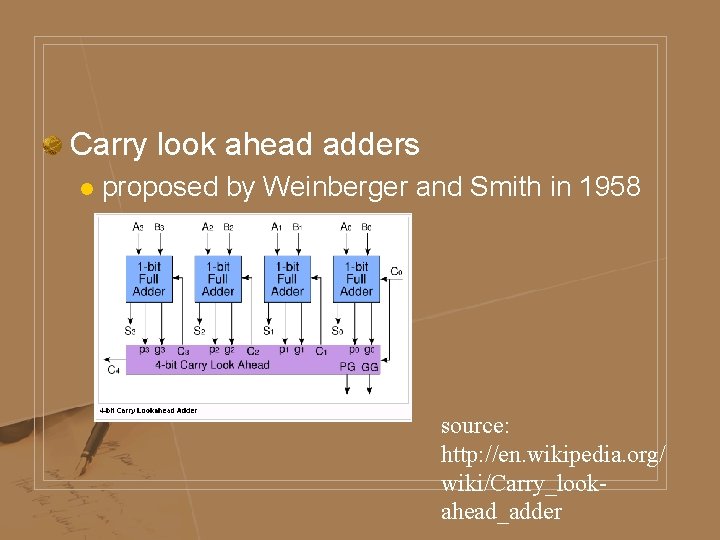

Carry look ahead adders l proposed by Weinberger and Smith in 1958 source: http: //en. wikipedia. org/ wiki/Carry_lookahead_adder

l carry look ahead adders work by creating “Propagate” and “Generate” signals for each bit Propagate: controls whether a carry is propagated from lower bits to higher bits l Generate: controls whether a carry is generated l

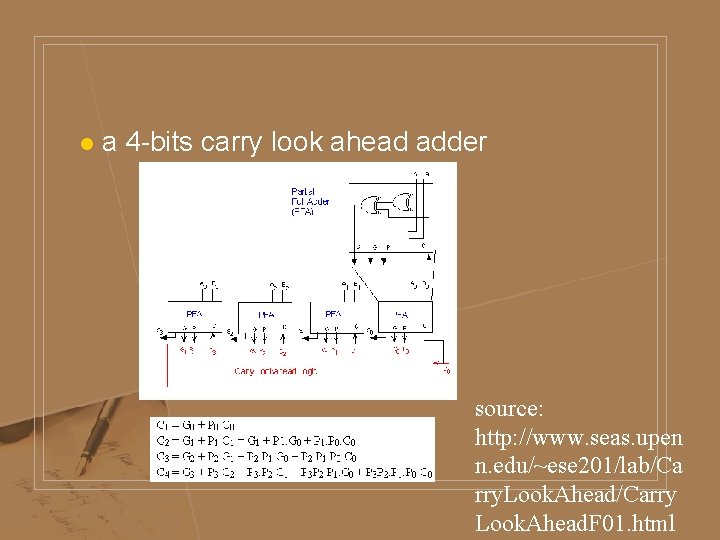

l a 4 -bits carry look ahead adder source: http: //www. seas. upen n. edu/~ese 201/lab/Ca rry. Look. Ahead/Carry Look. Ahead. F 01. html

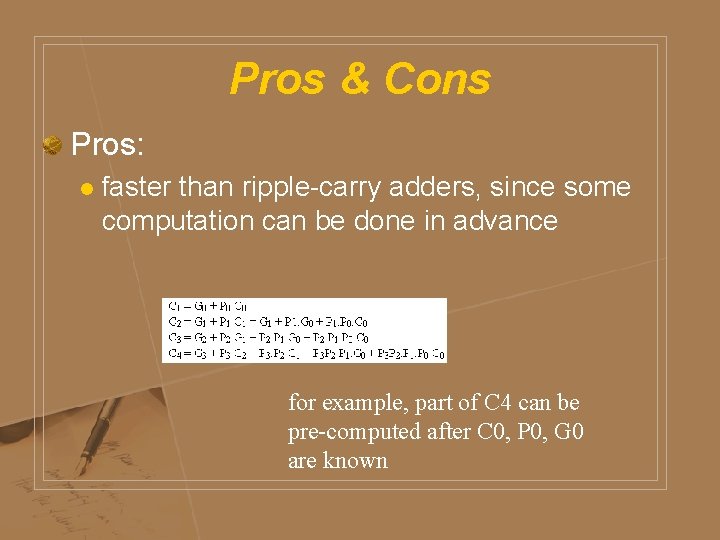

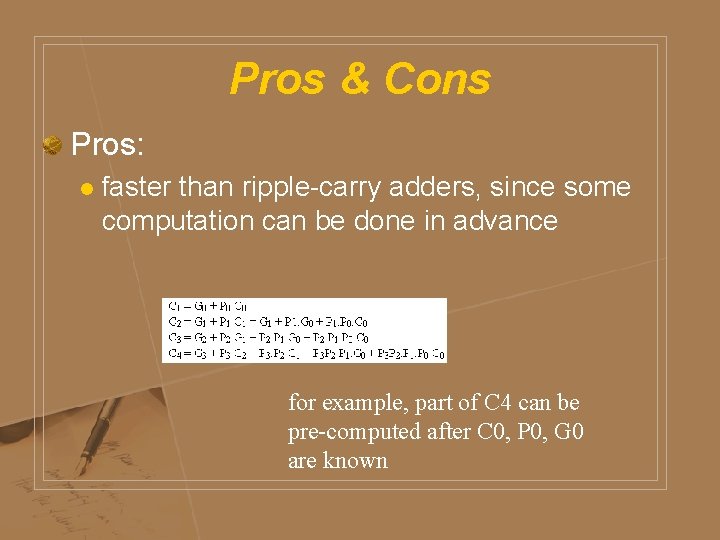

Pros & Cons Pros: l faster than ripple-carry adders, since some computation can be done in advance for example, part of C 4 can be pre-computed after C 0, P 0, G 0 are known

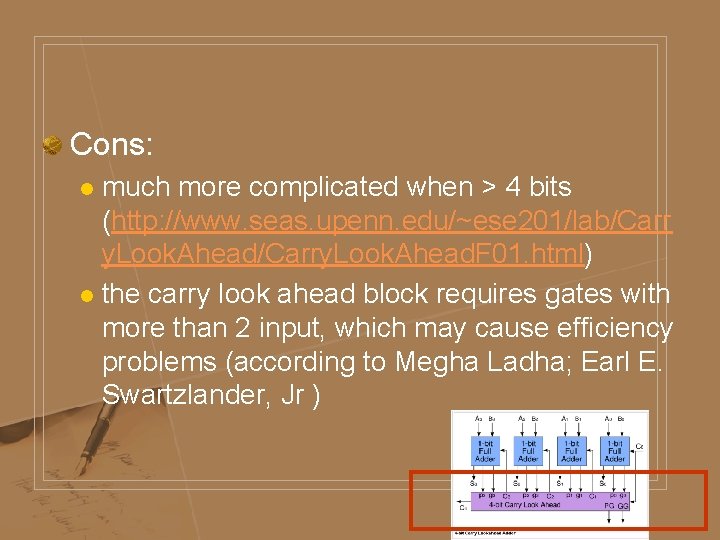

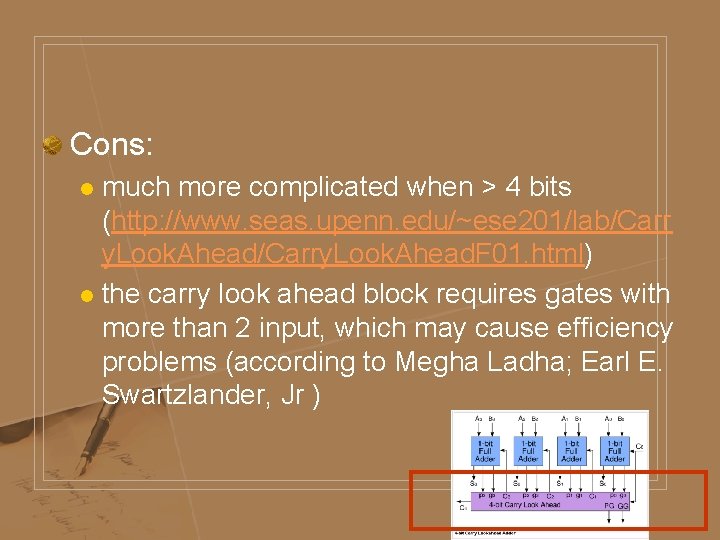

Cons: much more complicated when > 4 bits (http: //www. seas. upenn. edu/~ese 201/lab/Carr y. Look. Ahead/Carry. Look. Ahead. F 01. html) l the carry look ahead block requires gates with more than 2 input, which may cause efficiency problems (according to Megha Ladha; Earl E. Swartzlander, Jr ) l

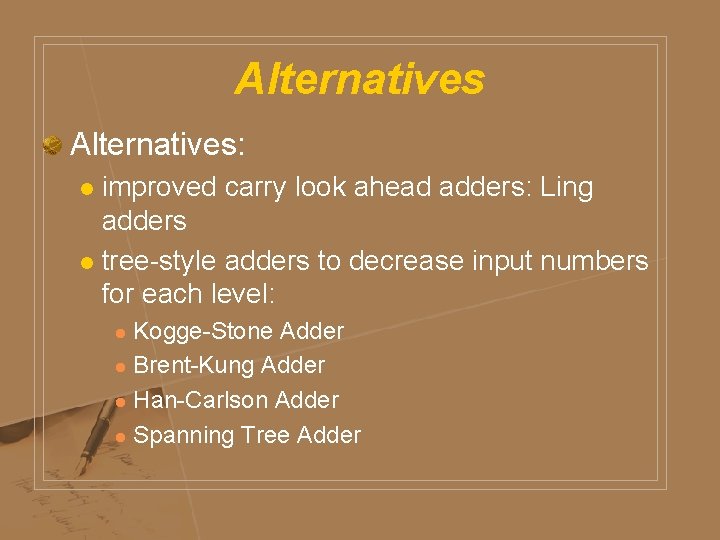

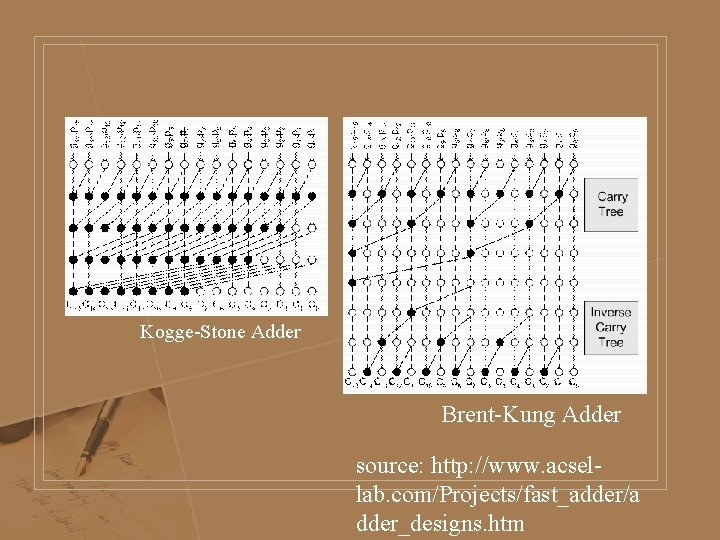

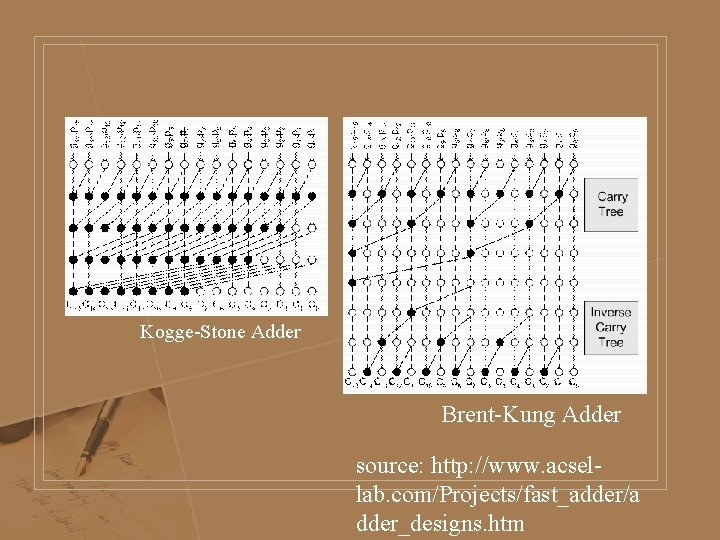

Alternatives: improved carry look ahead adders: Ling adders l tree-style adders to decrease input numbers for each level: l Kogge-Stone Adder l Brent-Kung Adder l Han-Carlson Adder l Spanning Tree Adder l

Kogge-Stone Adder Brent-Kung Adder source: http: //www. acsellab. com/Projects/fast_adder/a dder_designs. htm

Introduction to Adders & Problem Statement Spanning Tree Adders Result & Conclusion

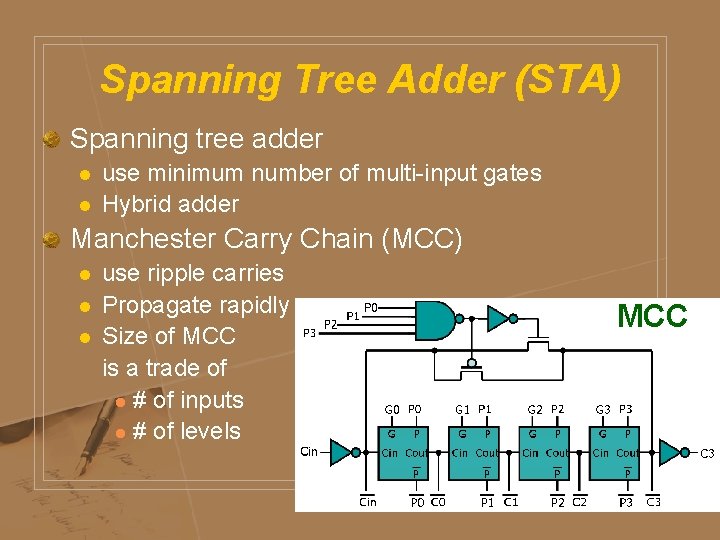

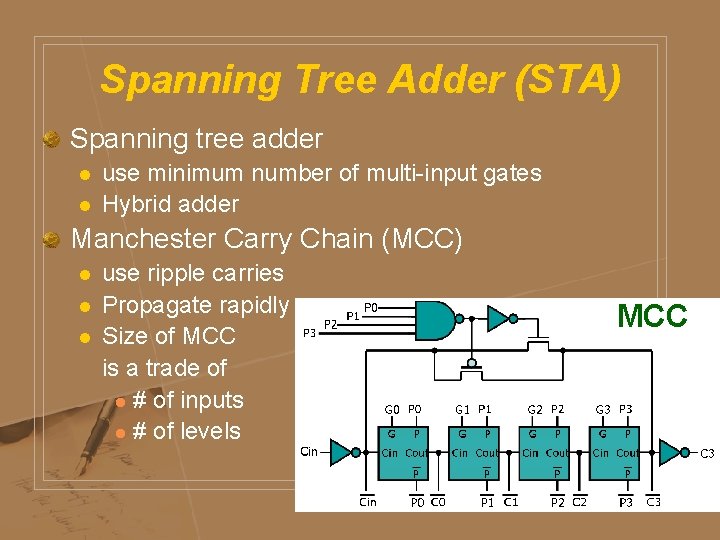

Spanning Tree Adder (STA) Spanning tree adder l l use minimum number of multi-input gates Hybrid adder Manchester Carry Chain (MCC) l l l use ripple carries Propagate rapidly Size of MCC is a trade of l # of inputs l # of levels MCC

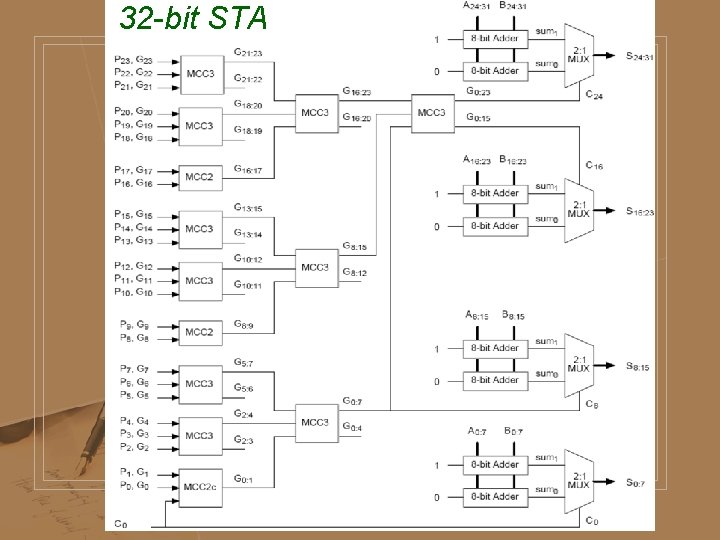

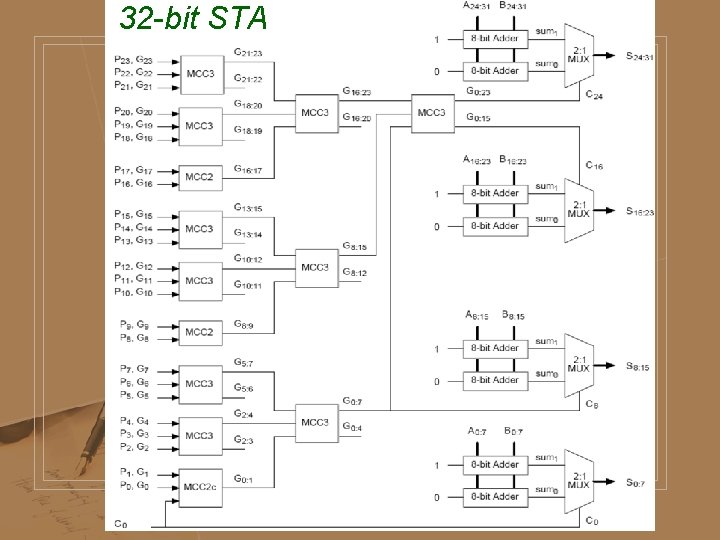

32 -bit STA

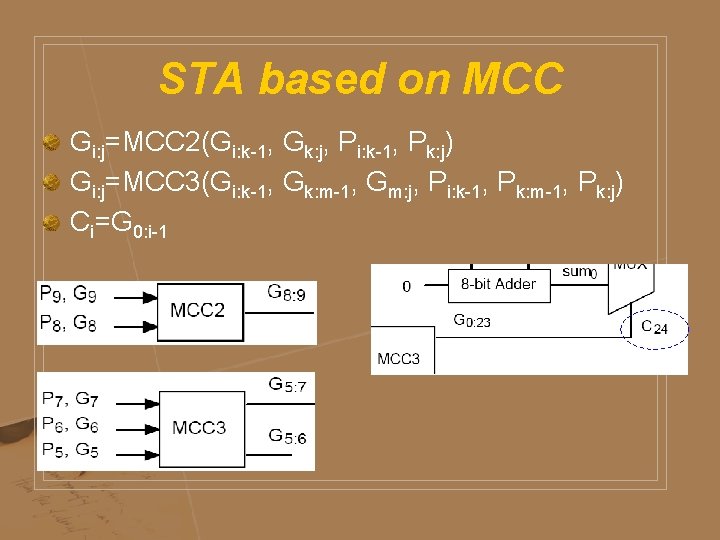

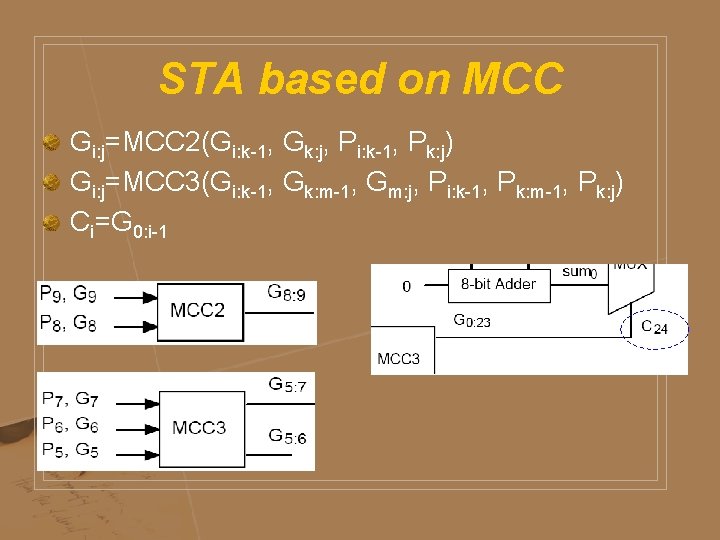

STA based on MCC Gi: j=MCC 2(Gi: k-1, Gk: j, Pi: k-1, Pk: j) Gi: j=MCC 3(Gi: k-1, Gk: m-1, Gm: j, Pi: k-1, Pk: m-1, Pk: j) Ci=G 0: i-1

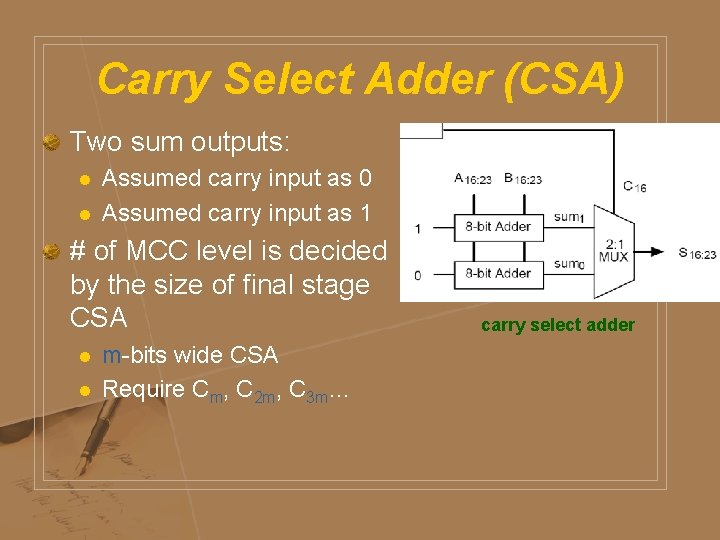

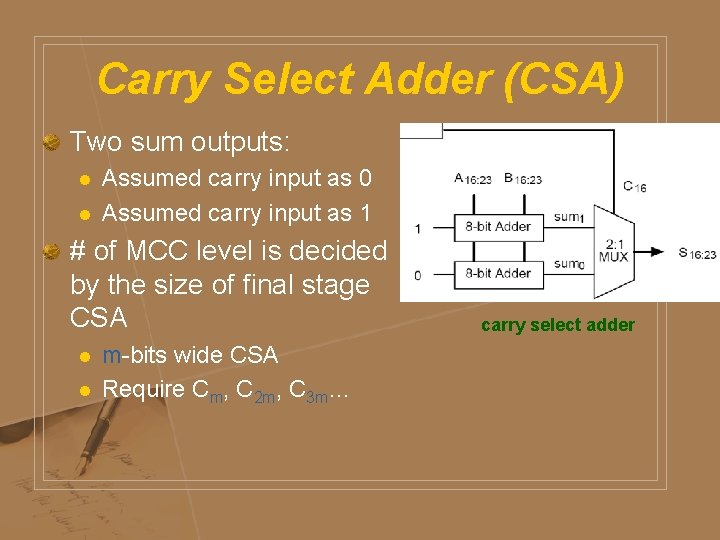

Carry Select Adder (CSA) Two sum outputs: l l Assumed carry input as 0 Assumed carry input as 1 # of MCC level is decided by the size of final stage CSA l l m-bits wide CSA Require Cm, C 2 m, C 3 m… carry select adder

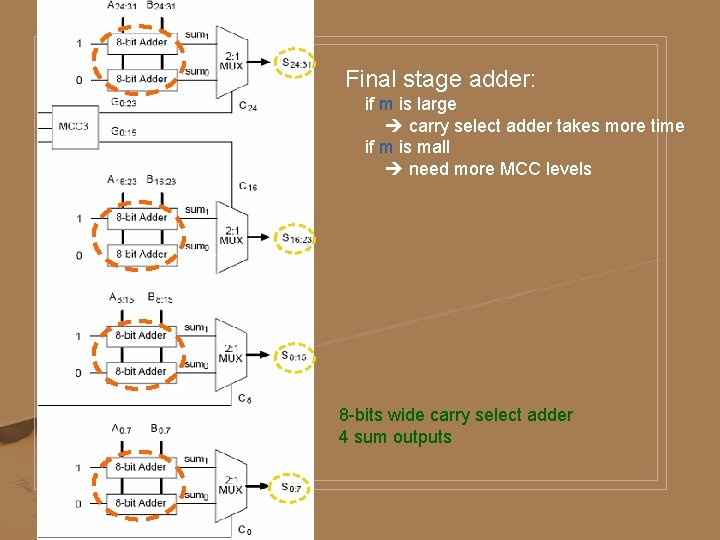

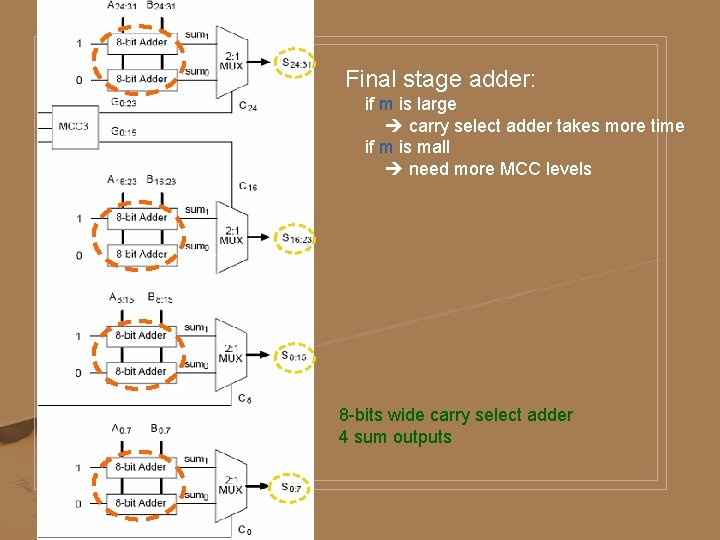

Final stage adder: if m is large carry select adder takes more time if m is mall need more MCC levels 8 -bits wide carry select adder 4 sum outputs

Introduction to Adders & Problem Statement Spanning Tree Adders Result & Conclusion

Main Comparion 16 -bit vs. 32 -bit adders CLA vs. Spanning tree adders 4 -bit, 8 -bit, 16 -bit RCA vs. CSA Measure: Delay, complexity, power consumption l Delay and power consumption are performed with Synopsys and Cadence

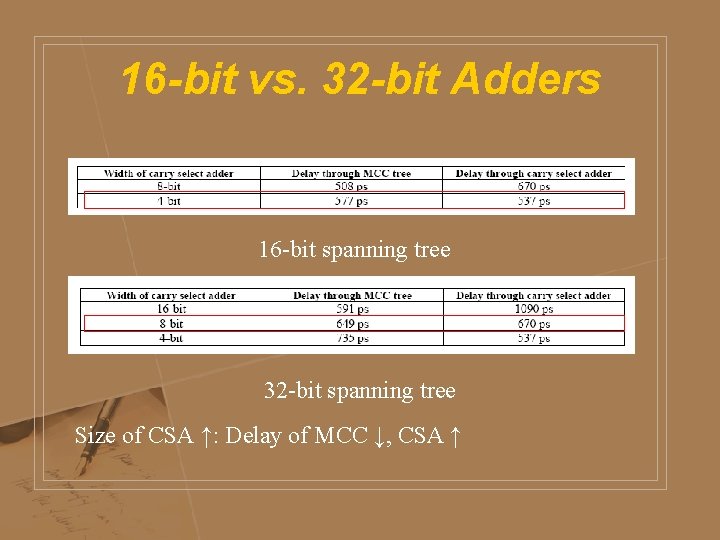

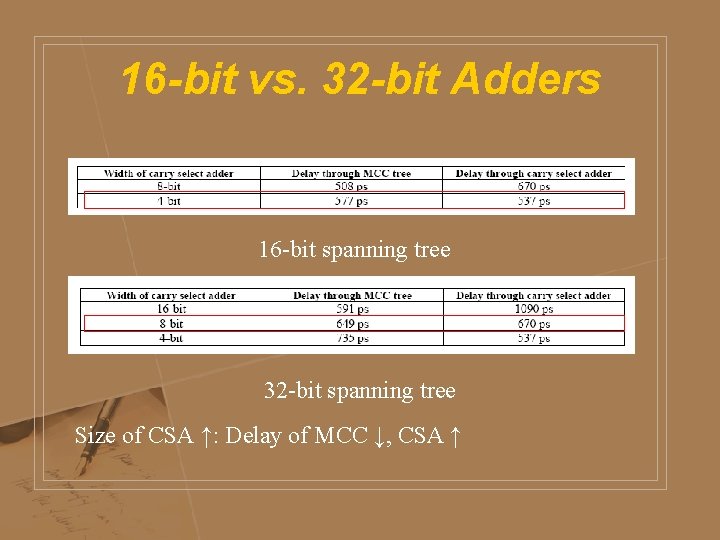

16 -bit vs. 32 -bit Adders 16 -bit spanning tree 32 -bit spanning tree Size of CSA ↑: Delay of MCC ↓, CSA ↑

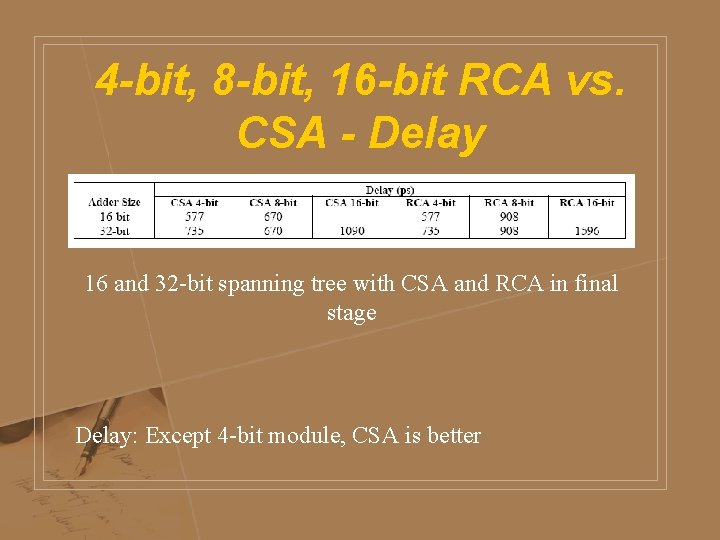

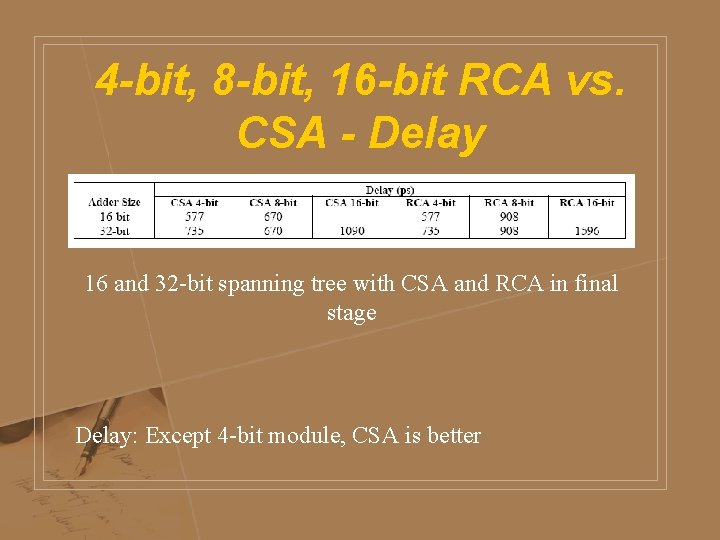

4 -bit, 8 -bit, 16 -bit RCA vs. CSA - Delay 16 and 32 -bit spanning tree with CSA and RCA in final stage Delay: Except 4 -bit module, CSA is better

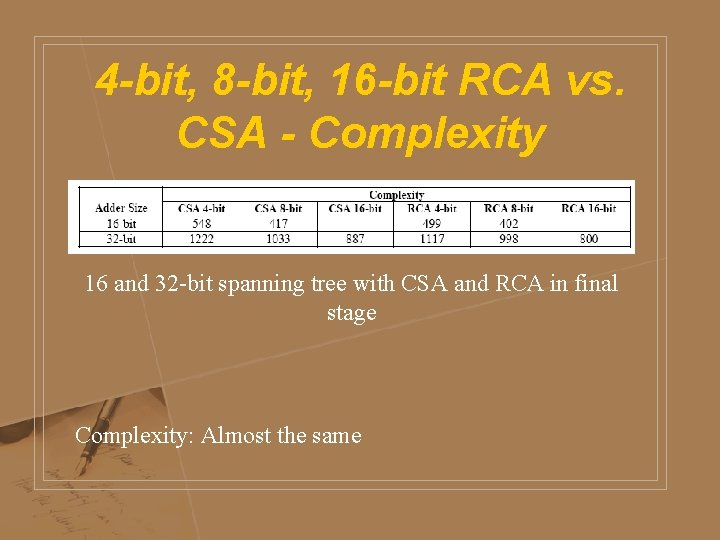

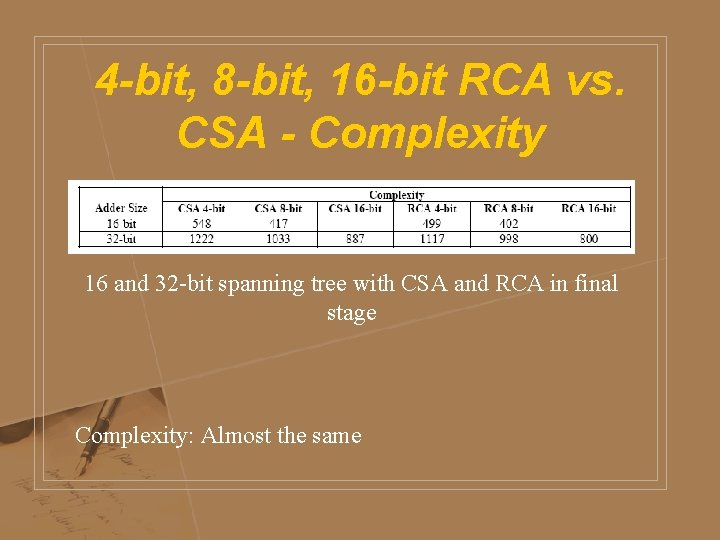

4 -bit, 8 -bit, 16 -bit RCA vs. CSA - Complexity 16 and 32 -bit spanning tree with CSA and RCA in final stage Complexity: Almost the same

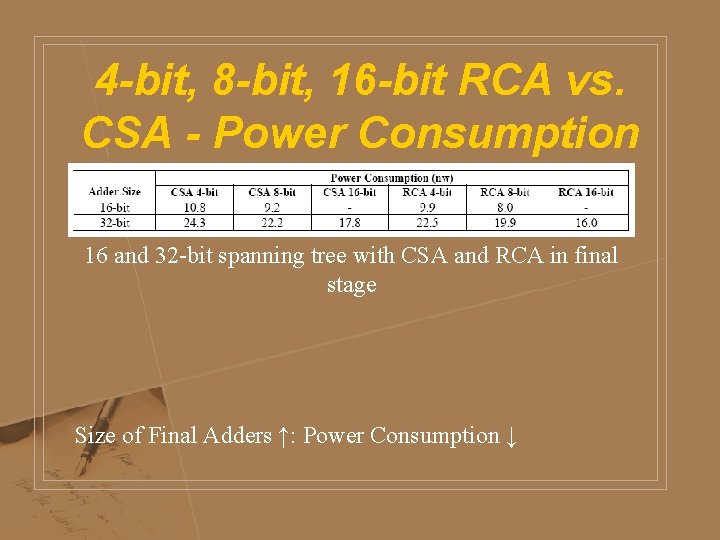

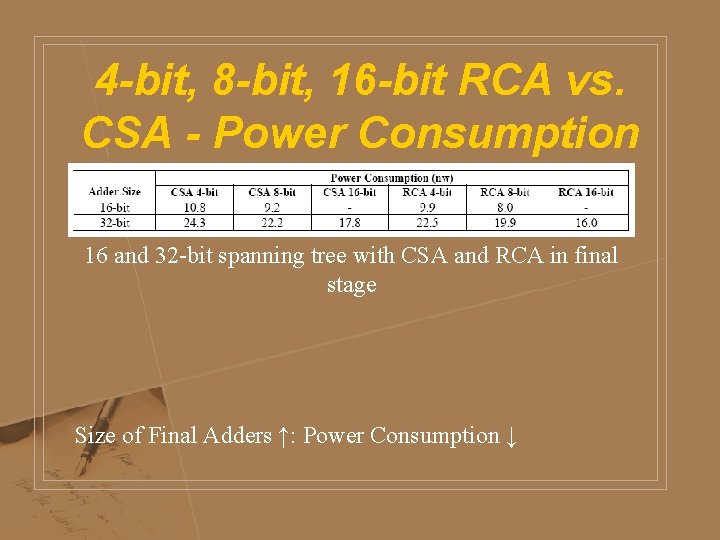

4 -bit, 8 -bit, 16 -bit RCA vs. CSA - Power Consumption 16 and 32 -bit spanning tree with CSA and RCA in final stage Size of Final Adders ↑: Power Consumption ↓

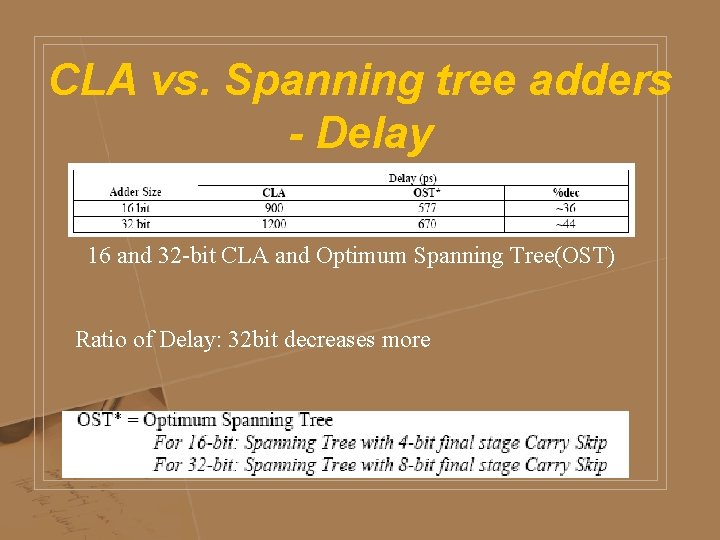

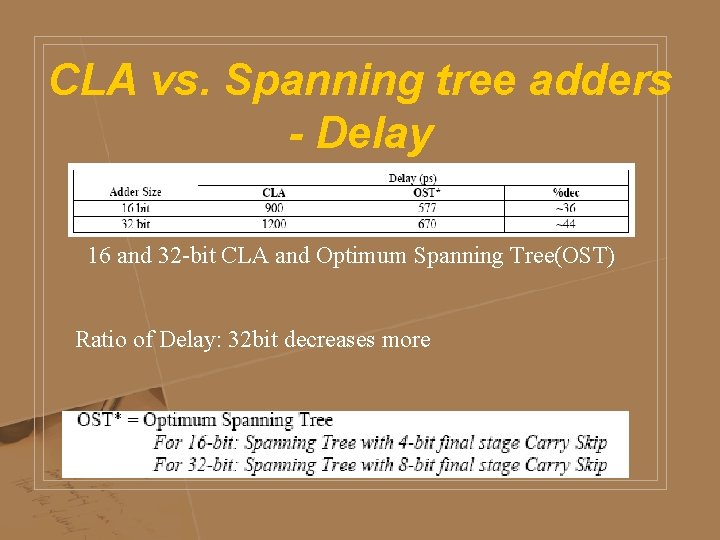

CLA vs. Spanning tree adders - Delay 16 and 32 -bit CLA and Optimum Spanning Tree(OST) Ratio of Delay: 32 bit decreases more

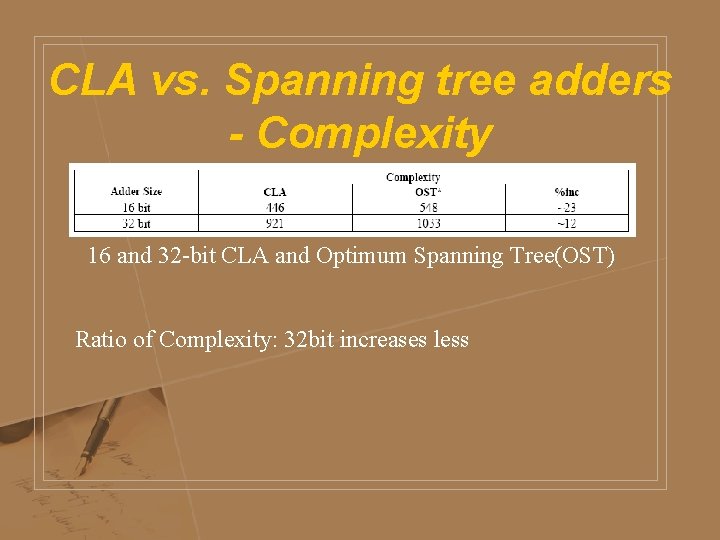

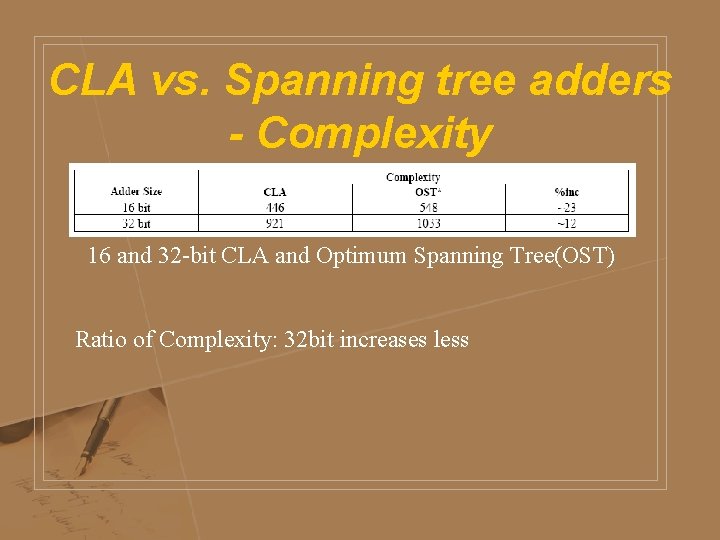

CLA vs. Spanning tree adders - Complexity 16 and 32 -bit CLA and Optimum Spanning Tree(OST) Ratio of Complexity: 32 bit increases less

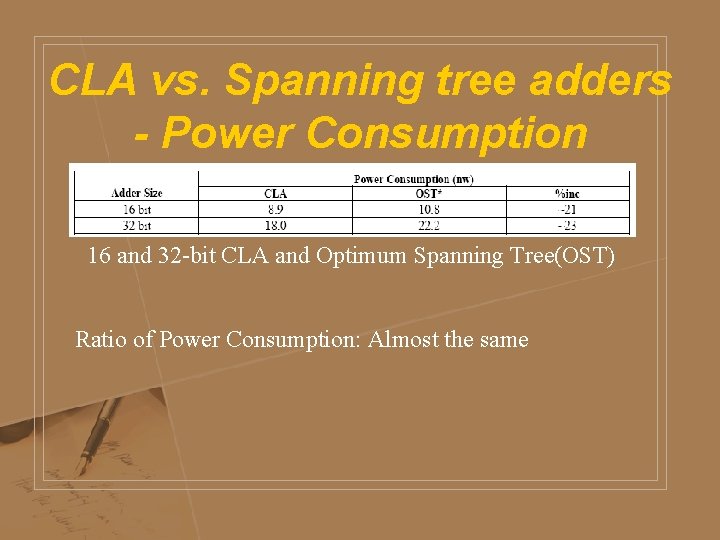

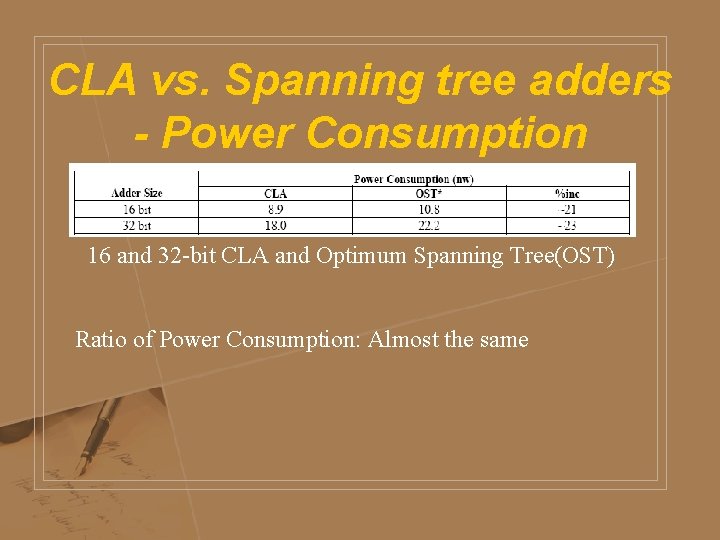

CLA vs. Spanning tree adders - Power Consumption 16 and 32 -bit CLA and Optimum Spanning Tree(OST) Ratio of Power Consumption: Almost the same

Conclusion Performance: In 16 -bit Spanning tree adder, 4 -bit, RCA and CSA are the same l In 32 -bit Spanning tree adder, 8 -bit above, RCA is better l Spanning tree is more ideal for larger size. l

Future Work Use transistor to design final adders and MCC blocks Sized for optimum performance Use transistor multiplexer instead of gate level multiplexer

Some Others – IC Design Language level: Like C language Gate level: Assembly language Transistor level: Machine code