OPERATORS and CONCURRENT STATEMENTS OPERATORS 1 The Operators

- Slides: 30

OPERATORS and CONCURRENT STATEMENTS

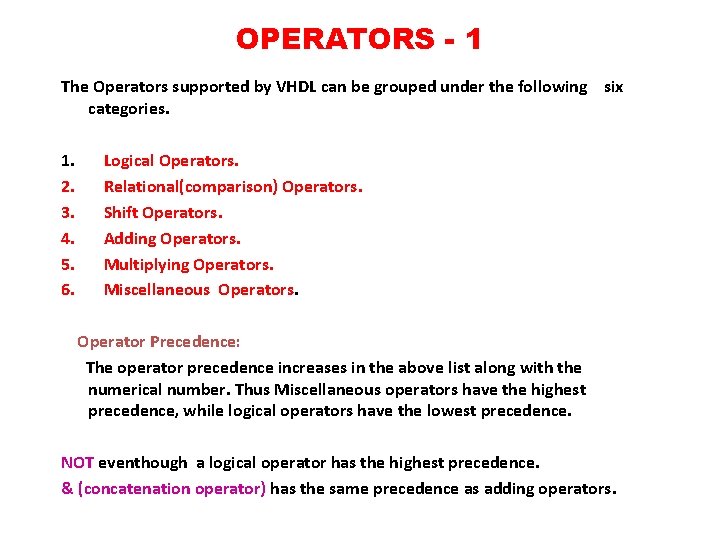

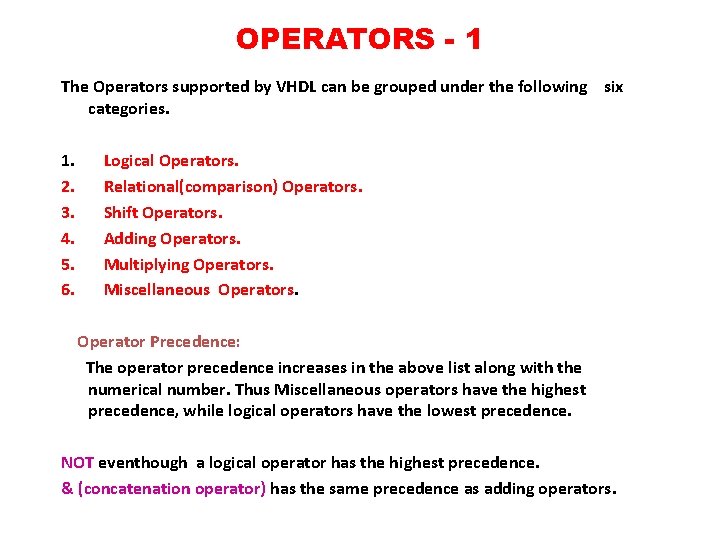

OPERATORS - 1 The Operators supported by VHDL can be grouped under the following six categories. 1. 2. 3. 4. 5. 6. Logical Operators. Relational(comparison) Operators. Shift Operators. Adding Operators. Multiplying Operators. Miscellaneous Operators. Operator Precedence: The operator precedence increases in the above list along with the numerical number. Thus Miscellaneous operators have the highest precedence, while logical operators have the lowest precedence. NOT eventhough a logical operator has the highest precedence. & (concatenation operator) has the same precedence as adding operators.

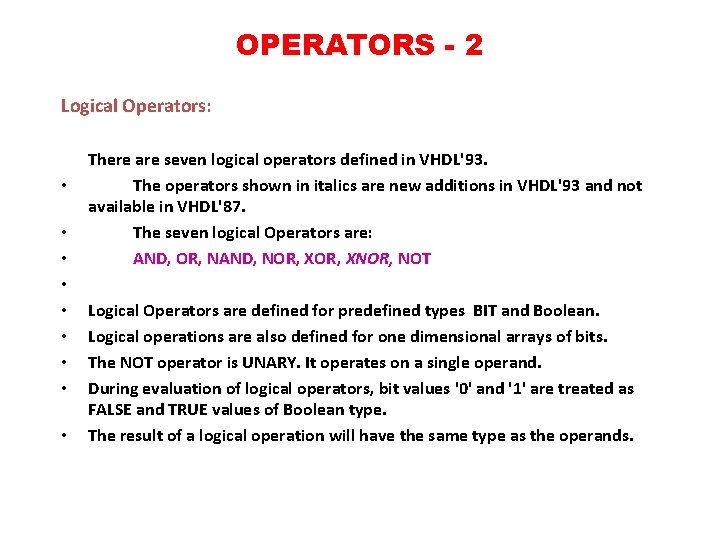

OPERATORS - 2 Logical Operators: • • • There are seven logical operators defined in VHDL'93. The operators shown in italics are new additions in VHDL'93 and not available in VHDL'87. The seven logical Operators are: AND, OR, NAND, NOR, XNOR, NOT Logical Operators are defined for predefined types BIT and Boolean. Logical operations are also defined for one dimensional arrays of bits. The NOT operator is UNARY. It operates on a single operand. During evaluation of logical operators, bit values '0' and '1' are treated as FALSE and TRUE values of Boolean type. The result of a logical operation will have the same type as the operands.

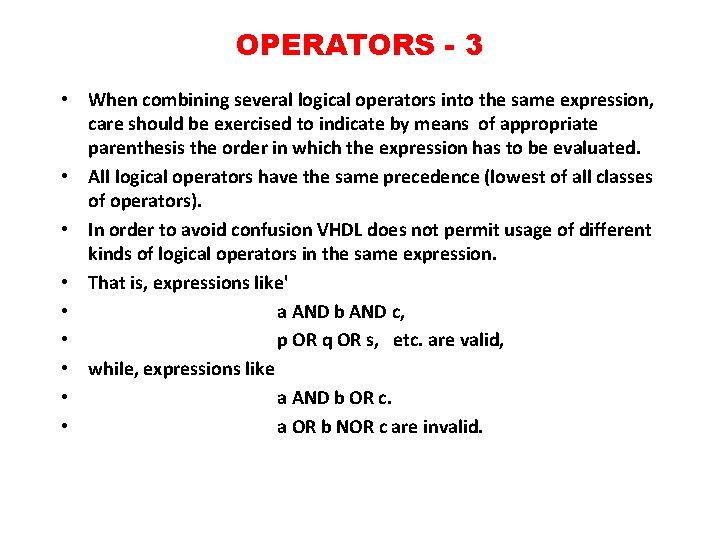

OPERATORS - 3 • When combining several logical operators into the same expression, care should be exercised to indicate by means of appropriate parenthesis the order in which the expression has to be evaluated. • All logical operators have the same precedence (lowest of all classes of operators). • In order to avoid confusion VHDL does not permit usage of different kinds of logical operators in the same expression. • That is, expressions like' • a AND b AND c, • p OR q OR s, etc. are valid, • while, expressions like • a AND b OR c. • a OR b NOR c are invalid.

OPERATORS - 4 • When different operators have to be mixed in the same expression , use parenthesis to indicate order of evaluation explicitly. • Expressions like, • a OR (b AND c) , • (a OR b) AND c , etc. are valid expressions. Needless to say that both evaluated differently. • Further, multiple NAND and NOR operators are not allowed in the same expression without parenthesis to indicate order of evaluation. • This is because unlike OR, AND , and XOR operators, NAND and NOR operators are not associative.

OPERATORS - 5 • While a AND (b AND c) is same as (a AND b) AND c is same as a AND b AND c, and • a OR (b OR c) is same as (a OR b) OR c is same as a OR b OR c, • and • a XOR (b XOR c) is same as (a XOR b) XOR c is same as a XOR b XOR c, • a NAND (b NAND c) is not same as (a NAND b) NAND c is same as • a NAND b AND c, • and • a NOR (b NOR c) is same as (a NOR b) NOR c is same as a NOR b NOR c. • While logical operators have lowest precedence among all operators, NOT is an exception. NOT along with miscellaneous operators has the highest precedence.

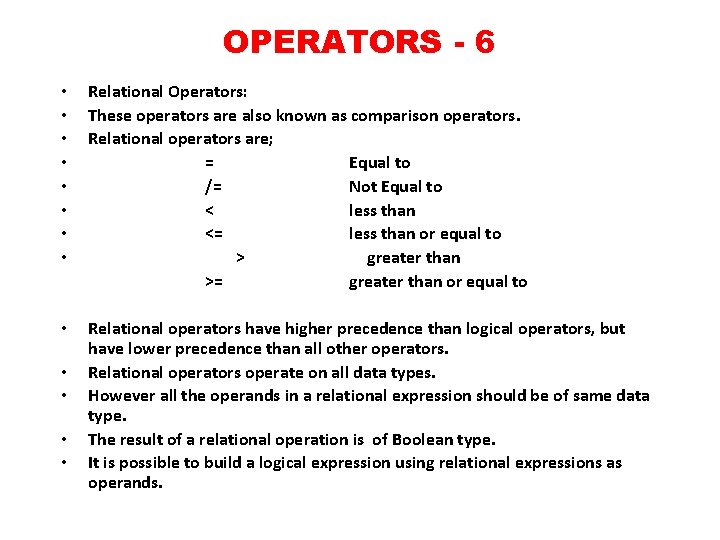

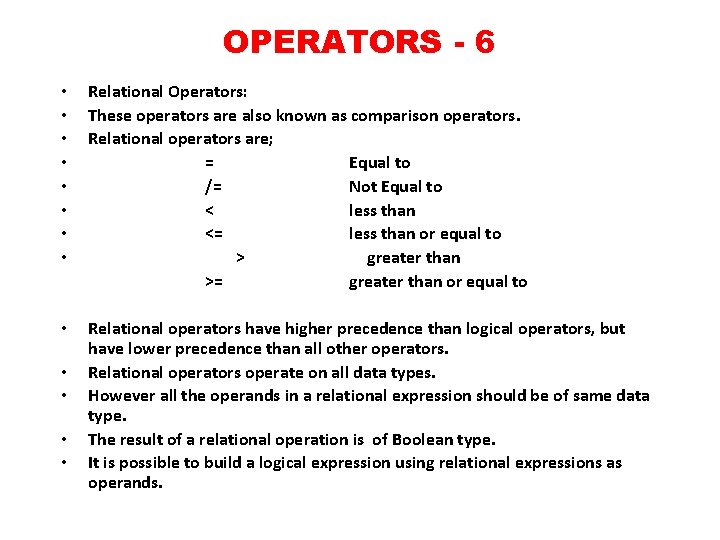

OPERATORS - 6 • • Relational Operators: These operators are also known as comparison operators. Relational operators are; = Equal to /= Not Equal to < less than <= less than or equal to > greater than >= greater than or equal to • Relational operators have higher precedence than logical operators, but have lower precedence than all other operators. Relational operators operate on all data types. However all the operands in a relational expression should be of same data type. The result of a relational operation is of Boolean type. It is possible to build a logical expression using relational expressions as operands. • •

OPERATORS - 7 EXAMPLE: IF a='0' AND b=c THEN IF a='0' OR b='1' OR c= d Are valid. However using parenthesis will remove ambiguities and makes the code more understandable. Example: IF ((a='0') OR (b ='1') OR (c=d)) THEN ---is a better and unambiguous way.

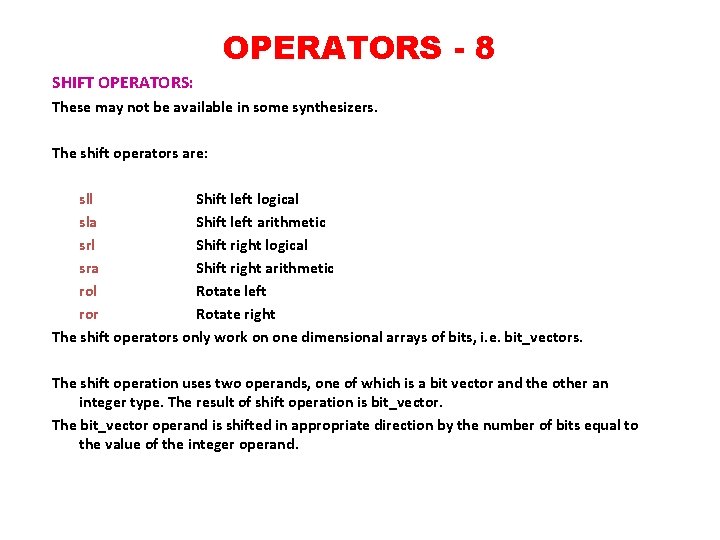

OPERATORS - 8 SHIFT OPERATORS: These may not be available in some synthesizers. The shift operators are: sll Shift left logical sla Shift left arithmetic srl Shift right logical sra Shift right arithmetic rol Rotate left ror Rotate right The shift operators only work on one dimensional arrays of bits, i. e. bit_vectors. The shift operation uses two operands, one of which is a bit vector and the other an integer type. The result of shift operation is bit_vector. The bit_vector operand is shifted in appropriate direction by the number of bits equal to the value of the integer operand.

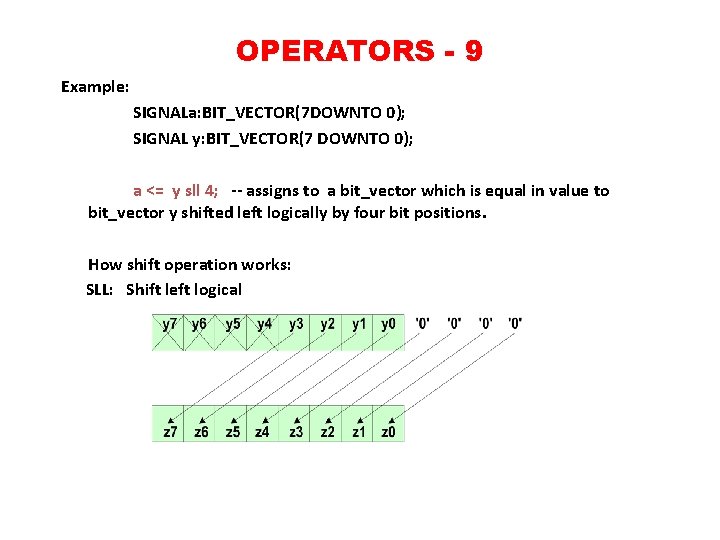

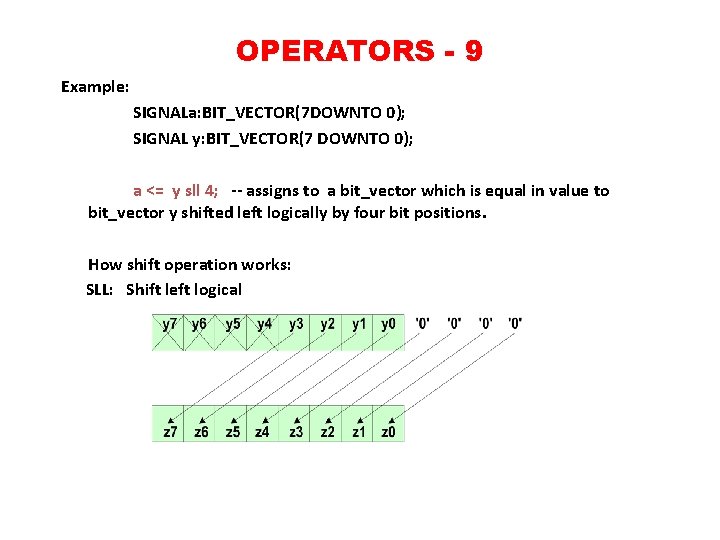

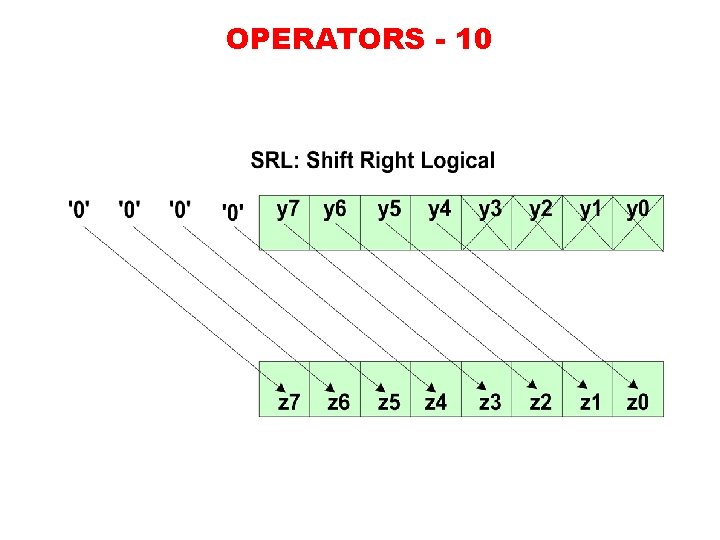

OPERATORS - 9 Example: SIGNALa: BIT_VECTOR(7 DOWNTO 0); SIGNAL y: BIT_VECTOR(7 DOWNTO 0); a <= y sll 4; -- assigns to a bit_vector which is equal in value to bit_vector y shifted left logically by four bit positions. How shift operation works: SLL: Shift left logical

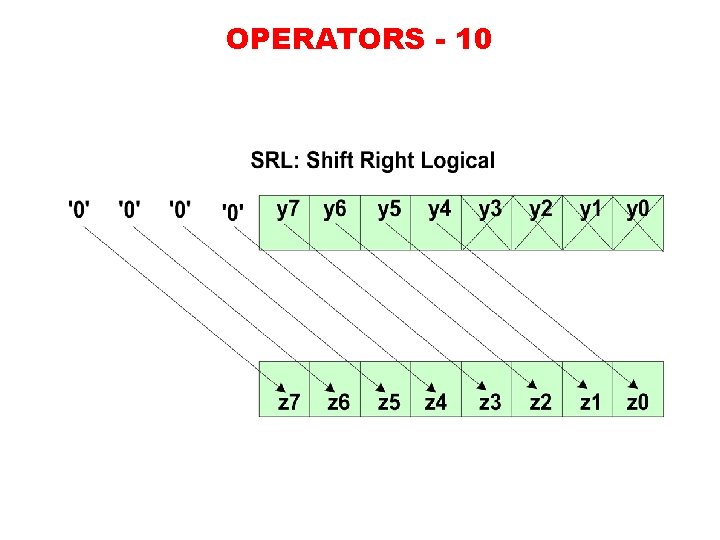

OPERATORS - 10

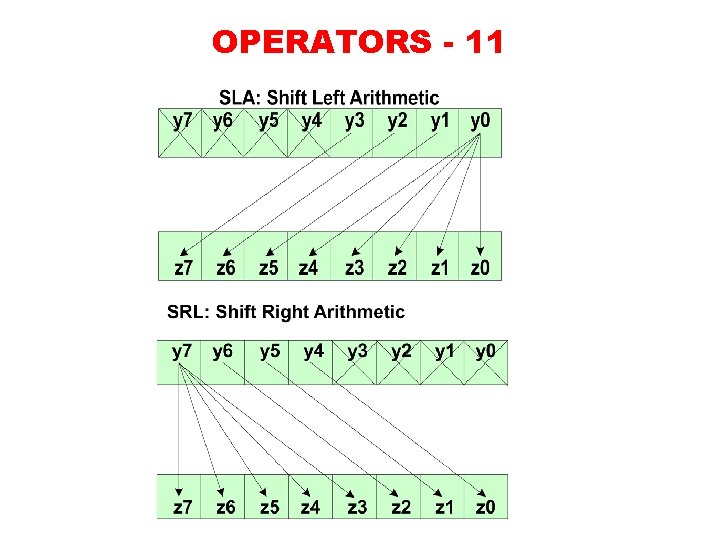

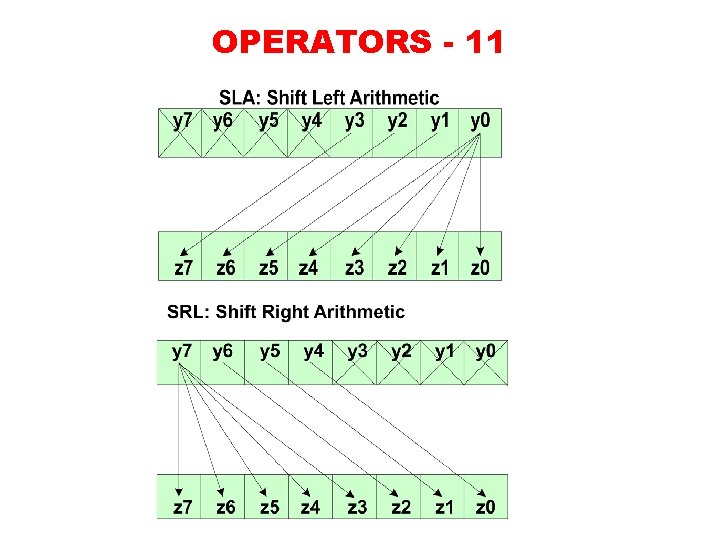

OPERATORS - 11

OPERATORS - 12 • • • The following points regarding shift operations should be noted. 1. There is no circuit synthesized for shift operations. Instead, depending on the value by which shift operation has to be carried out, and the type of shift operation, signal wires (connections) between source and destination are appropriately manipulated. 2. As a consequence the operand value which specifies the amount of shift has to be a constant and not a signal or variable. This makes the shift operation of limited use. However note that this shift operation has no time delay(except wire delay) associated with it. 3. As can be seen from figures above, while the logical shift operations behave as expected, the arithmetic shift operations do not work in a straight forward manner, rendering them to be of little use. It is better not to use shift operators, unless one is clear about how they behave. It is better to implement general purpose parallel shifters with multiplexers or ordinary shift registers with clocked logic and concatenation operators.

OPERATORS - 13 • Arithmetic Operators: • Group A operators along with logical operator NOT have the highest precedence, while group D operators have the lowest precedence. • • The concatenation operator & is not really an arithmetic operator, but it is grouped along with addition operators as it has the same precedence. • • A. Miscellaneous operators: **, ABS • B. Multiplying operators: *, / , mod, rem • C. Sign: +, • D. Addition operators: +, -, &

OPERATORS - 14 Synthesis interpretation of arithmetic operators: different synthesizers implement arithmetic may be different. Many synthesizers may provide a choice of implementation depending in the speed/area constraints. The plus operator has no effect on the operand. It is simply feed through of the operand has no circuit implementation. Eg. z <= +y; The minus sign is implemented as two's complement negation. Negation is done by subtracting the operand from 0, using a ripple borrow chain of half subtractors. •

OPERATORS - 15 • • Multiplication is implemented using a matrix of full adders. Division, remainder, modulus and exponentiation are not normally supported or only supported to a limited extent (when one of the operands is a power of two). • Arithmetic operations are supported only on integer types , float types and physical types. Synthesizers support is limited. But library functions or special packages may be available from individual vendors. • • Note that all operators cannot be used with all data types. Appropriate type conversions will be needed if operations not allowed on a particular data type are required. The most frequently required conversion is from integer types to bit_vectors and vice versa.

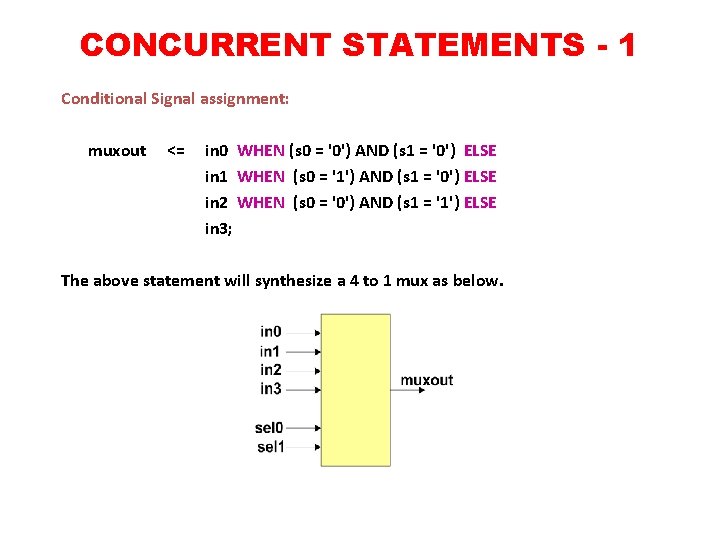

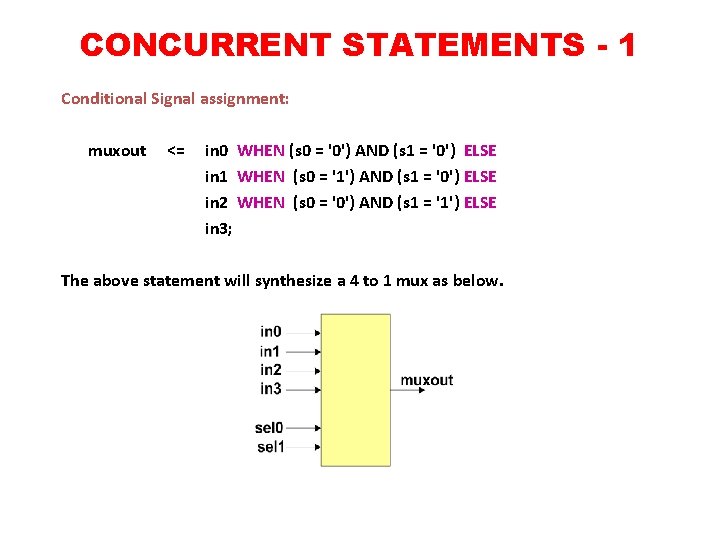

CONCURRENT STATEMENTS - 1 Conditional Signal assignment: muxout <= in 0 WHEN (s 0 = '0') AND (s 1 = '0') ELSE in 1 WHEN (s 0 = '1') AND (s 1 = '0') ELSE in 2 WHEN (s 0 = '0') AND (s 1 = '1') ELSE in 3; The above statement will synthesize a 4 to 1 mux as below.

CONCURRENT STATEMENTS - 2 The general form of a conditional signal assignment is Target_signal <= source 1 WHEN (condition 1) ELSE source 2 WHEN (condition 2) ELSE source 3 WHEN (condition 3) ELSE. . . sourcen WHEN (condition n); Any number of sources and corresponding conditions can be there. Even though different conditions are shown on different lines, the whole thing is a single statement as indicated by the semicolon at the end of the statement. The value corresponding to the first condition that becomes true is assigned to the target signal.

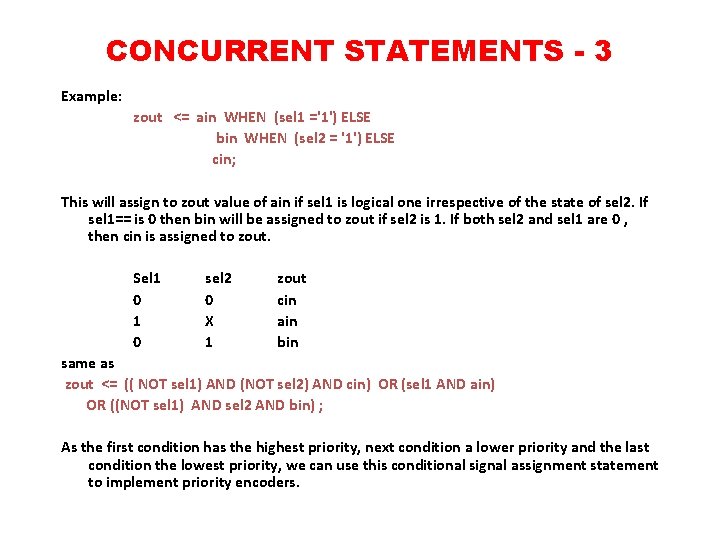

CONCURRENT STATEMENTS - 3 Example: zout <= ain WHEN (sel 1 ='1') ELSE bin WHEN (sel 2 = '1') ELSE cin; This will assign to zout value of ain if sel 1 is logical one irrespective of the state of sel 2. If sel 1== is 0 then bin will be assigned to zout if sel 2 is 1. If both sel 2 and sel 1 are 0 , then cin is assigned to zout. Sel 1 0 sel 2 0 X 1 zout cin ain bin same as zout <= (( NOT sel 1) AND (NOT sel 2) AND cin) OR (sel 1 AND ain) OR ((NOT sel 1) AND sel 2 AND bin) ; As the first condition has the highest priority, next condition a lower priority and the last condition the lowest priority, we can use this conditional signal assignment statement to implement priority encoders.

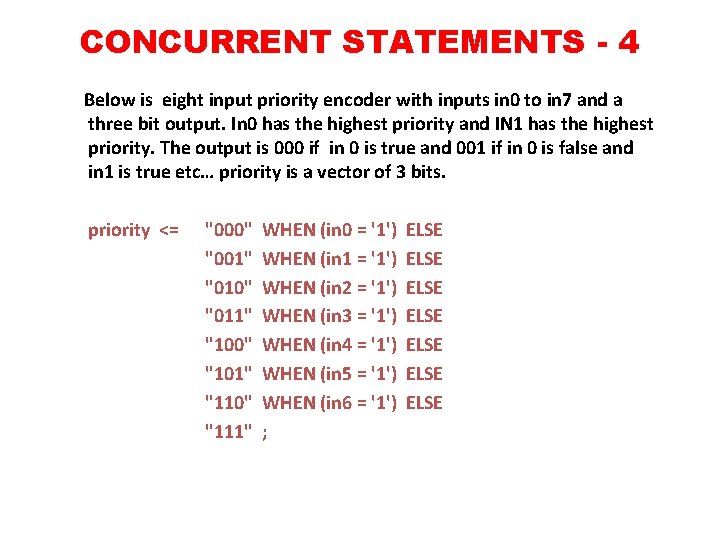

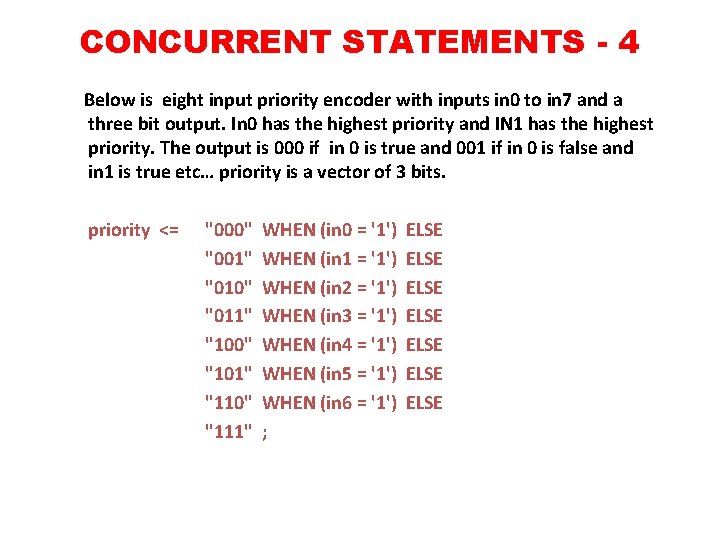

CONCURRENT STATEMENTS - 4 Below is eight input priority encoder with inputs in 0 to in 7 and a three bit output. In 0 has the highest priority and IN 1 has the highest priority. The output is 000 if in 0 is true and 001 if in 0 is false and in 1 is true etc… priority is a vector of 3 bits. priority <= "000" "001" "010" "011" "100" "101" "110" "111" WHEN (in 0 = '1') WHEN (in 1 = '1') WHEN (in 2 = '1') WHEN (in 3 = '1') WHEN (in 4 = '1') WHEN (in 5 = '1') WHEN (in 6 = '1') ; ELSE ELSE

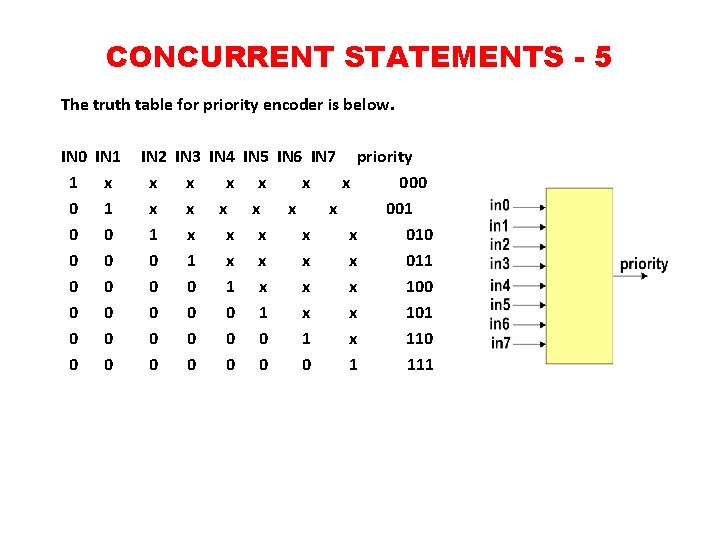

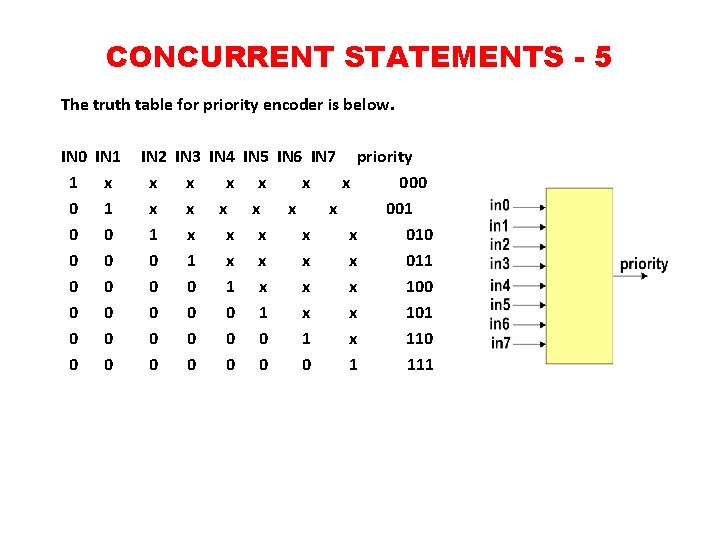

CONCURRENT STATEMENTS - 5 The truth table for priority encoder is below. IN 0 1 0 0 0 0 IN 1 x 1 0 0 0 IN 2 IN 3 IN 4 IN 5 IN 6 IN 7 priority x x x 000 x x x 001 1 x x x 010 0 1 x x 011 0 0 1 x x x 100 0 1 x x 101 0 0 1 x 110 0 0 1 111

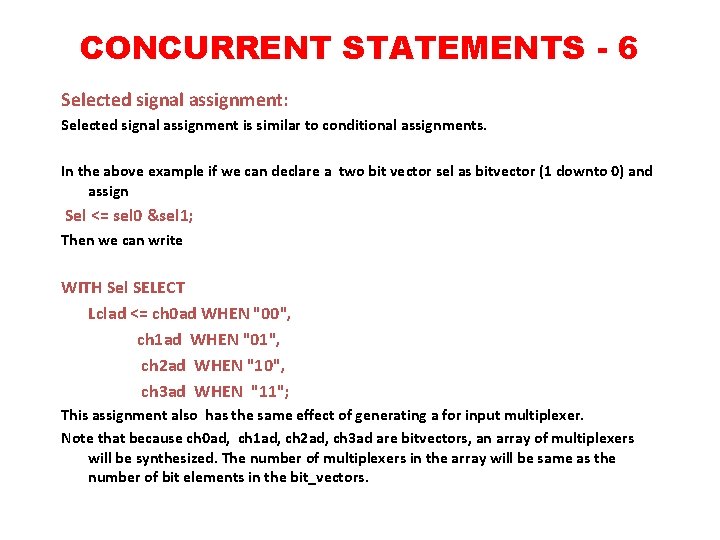

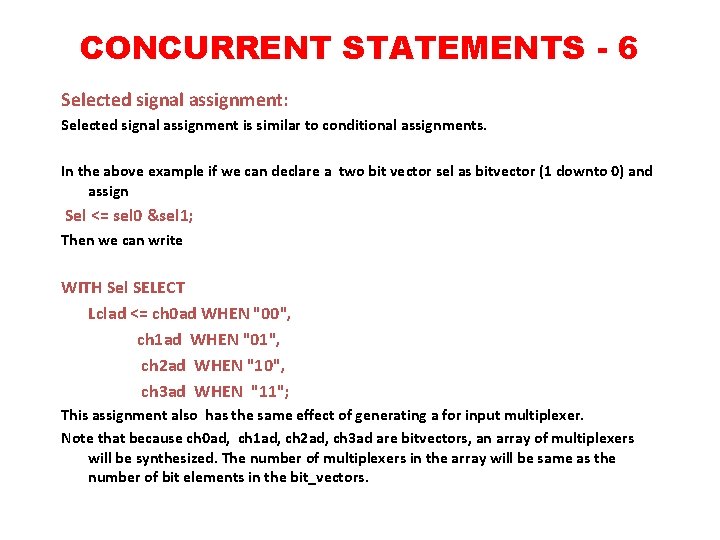

CONCURRENT STATEMENTS - 6 Selected signal assignment: Selected signal assignment is similar to conditional assignments. In the above example if we can declare a two bit vector sel as bitvector (1 downto 0) and assign Sel <= sel 0 &sel 1; Then we can write WITH Sel SELECT Lclad <= ch 0 ad WHEN "00", ch 1 ad WHEN "01", ch 2 ad WHEN "10", ch 3 ad WHEN "11"; This assignment also has the same effect of generating a for input multiplexer. Note that because ch 0 ad, ch 1 ad, ch 2 ad, ch 3 ad are bitvectors, an array of multiplexers will be synthesized. The number of multiplexers in the array will be same as the number of bit elements in the bit_vectors.

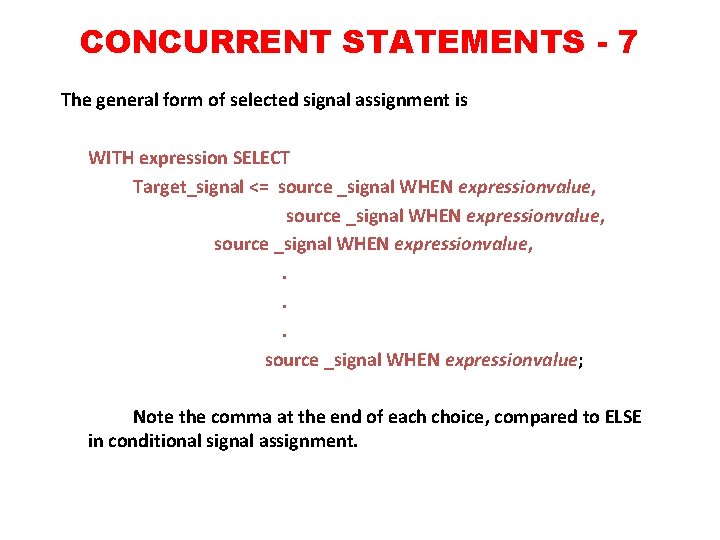

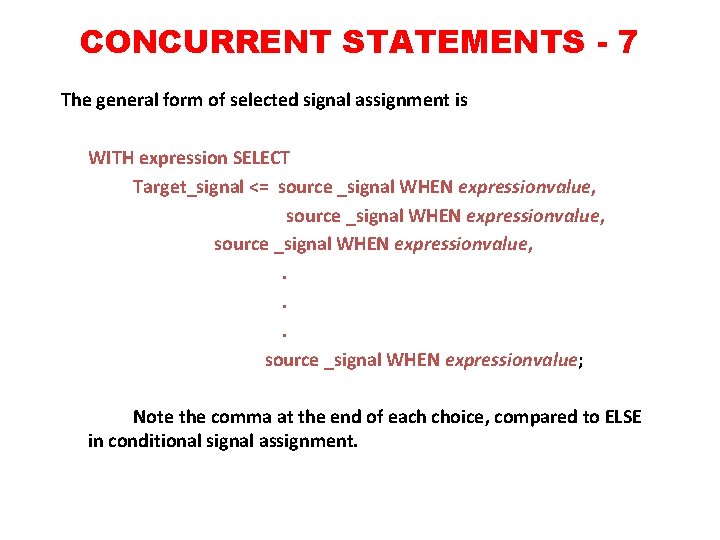

CONCURRENT STATEMENTS - 7 The general form of selected signal assignment is WITH expression SELECT Target_signal <= source _signal WHEN expressionvalue, . . . source _signal WHEN expressionvalue; Note the comma at the end of each choice, compared to ELSE in conditional signal assignment.

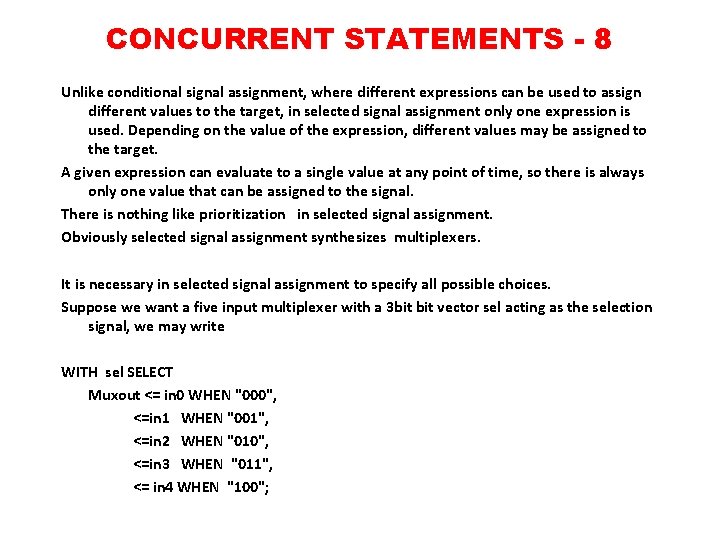

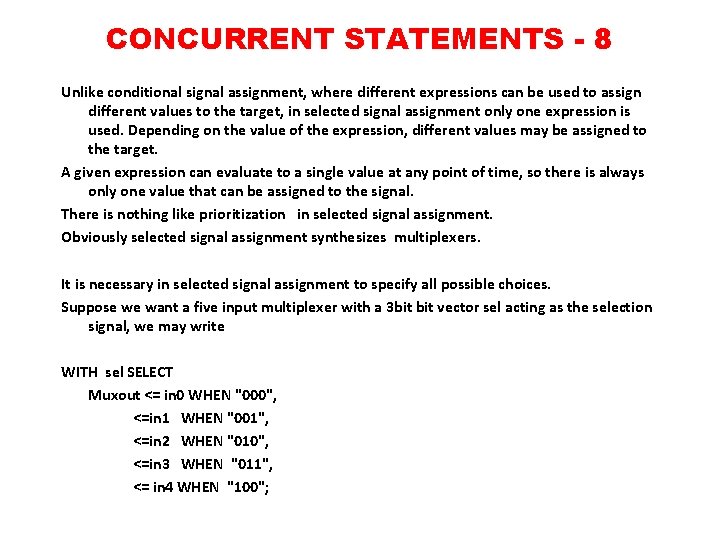

CONCURRENT STATEMENTS - 8 Unlike conditional signal assignment, where different expressions can be used to assign different values to the target, in selected signal assignment only one expression is used. Depending on the value of the expression, different values may be assigned to the target. A given expression can evaluate to a single value at any point of time, so there is always only one value that can be assigned to the signal. There is nothing like prioritization in selected signal assignment. Obviously selected signal assignment synthesizes multiplexers. It is necessary in selected signal assignment to specify all possible choices. Suppose we want a five input multiplexer with a 3 bit vector sel acting as the selection signal, we may write WITH sel SELECT Muxout <= in 0 WHEN "000", <=in 1 WHEN "001", <=in 2 WHEN "010", <=in 3 WHEN "011", <= in 4 WHEN "100";

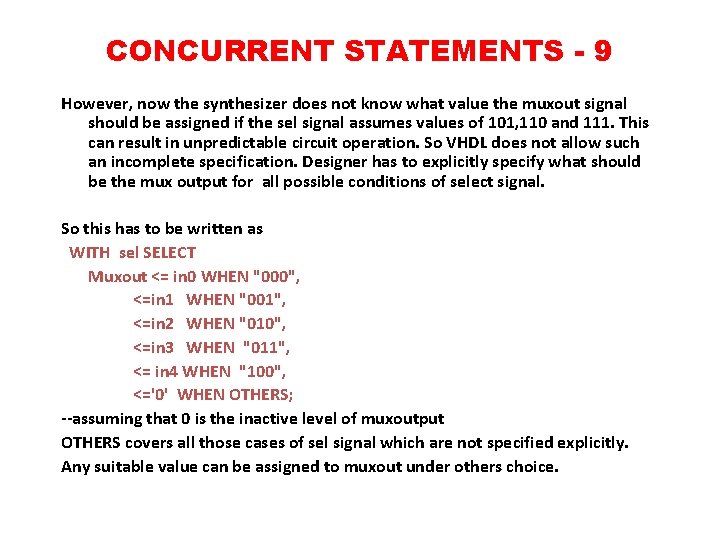

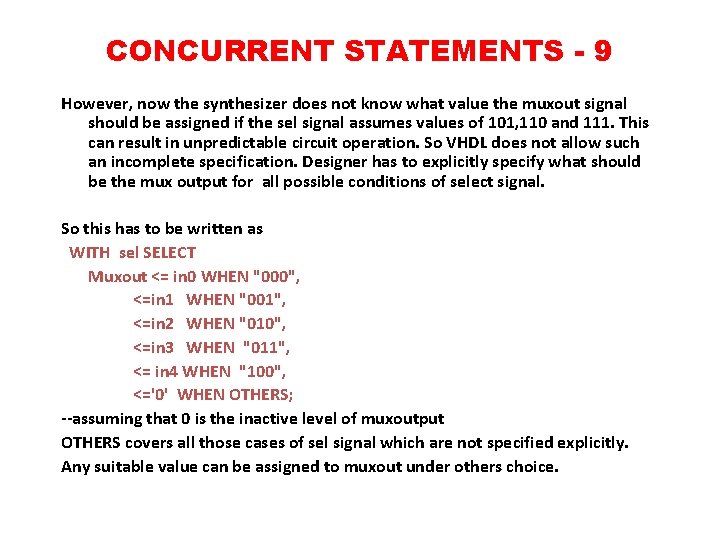

CONCURRENT STATEMENTS - 9 However, now the synthesizer does not know what value the muxout signal should be assigned if the sel signal assumes values of 101, 110 and 111. This can result in unpredictable circuit operation. So VHDL does not allow such an incomplete specification. Designer has to explicitly specify what should be the mux output for all possible conditions of select signal. So this has to be written as WITH sel SELECT Muxout <= in 0 WHEN "000", <=in 1 WHEN "001", <=in 2 WHEN "010", <=in 3 WHEN "011", <= in 4 WHEN "100", <='0' WHEN OTHERS; --assuming that 0 is the inactive level of muxoutput OTHERS covers all those cases of sel signal which are not specified explicitly. Any suitable value can be assigned to muxout under others choice.

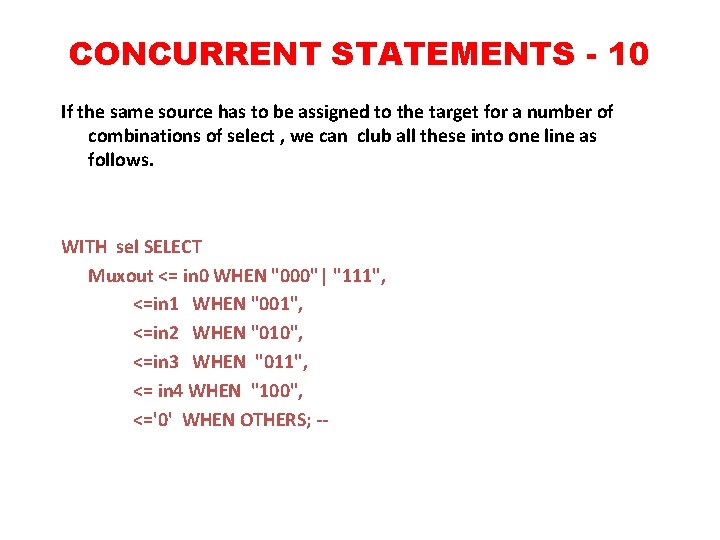

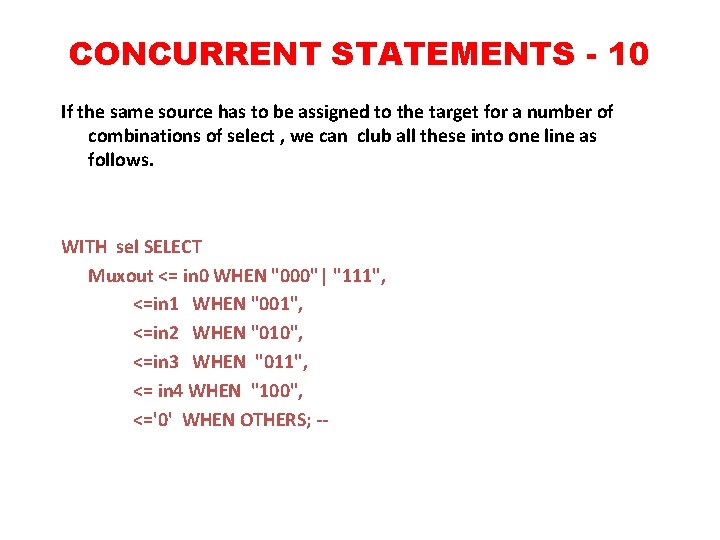

CONCURRENT STATEMENTS - 10 If the same source has to be assigned to the target for a number of combinations of select , we can club all these into one line as follows. WITH sel SELECT Muxout <= in 0 WHEN "000"| "111", <=in 1 WHEN "001", <=in 2 WHEN "010", <=in 3 WHEN "011", <= in 4 WHEN "100", <='0' WHEN OTHERS; --

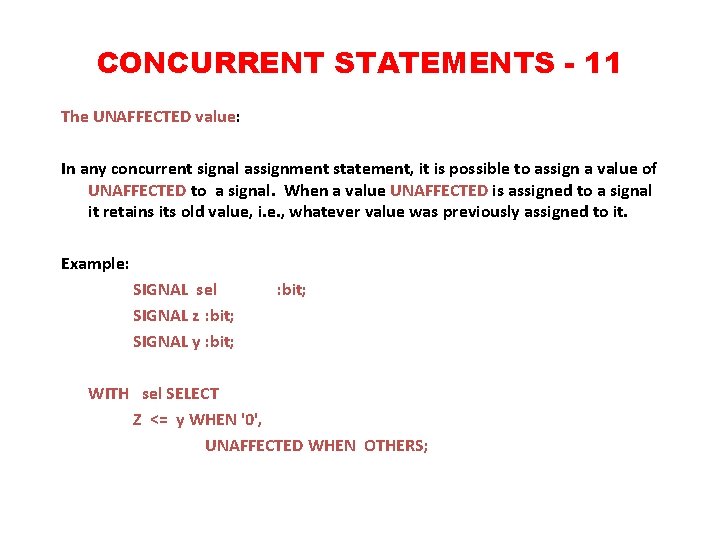

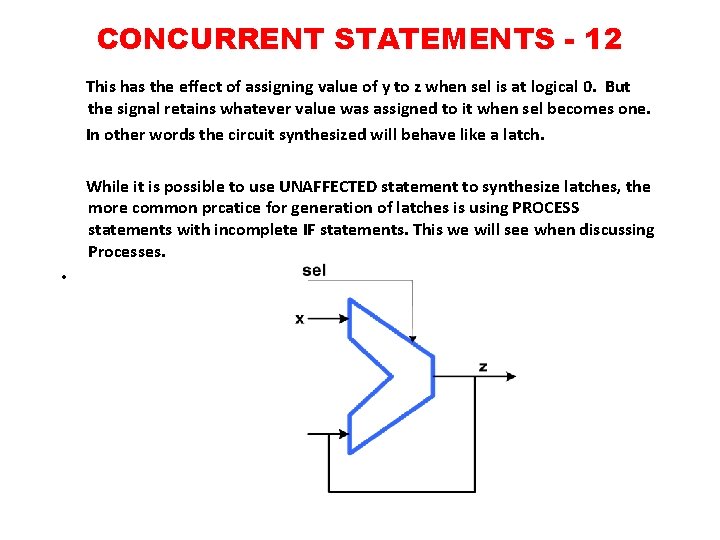

CONCURRENT STATEMENTS - 11 The UNAFFECTED value: In any concurrent signal assignment statement, it is possible to assign a value of UNAFFECTED to a signal. When a value UNAFFECTED is assigned to a signal it retains its old value, i. e. , whatever value was previously assigned to it. Example: SIGNAL sel SIGNAL z : bit; SIGNAL y : bit; WITH sel SELECT Z <= y WHEN '0', UNAFFECTED WHEN OTHERS;

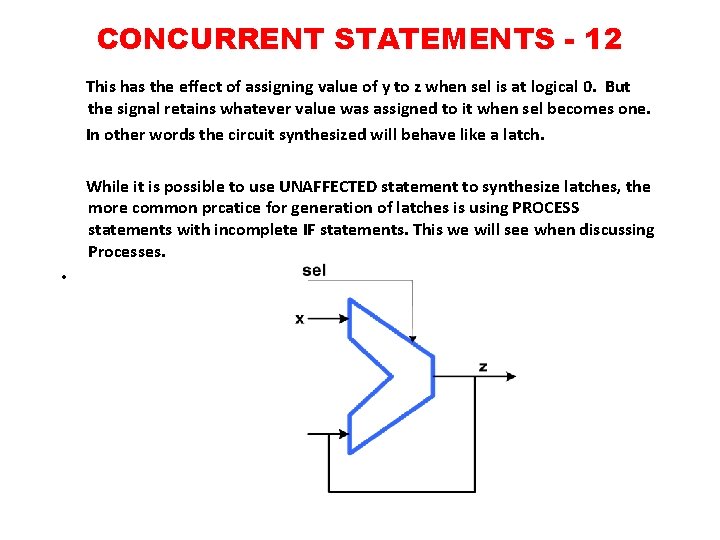

CONCURRENT STATEMENTS - 12 This has the effect of assigning value of y to z when sel is at logical 0. But the signal retains whatever value was assigned to it when sel becomes one. In other words the circuit synthesized will behave like a latch. While it is possible to use UNAFFECTED statement to synthesize latches, the more common prcatice for generation of latches is using PROCESS statements with incomplete IF statements. This we will see when discussing Processes. •

CONCURRENT STATEMENTS - 13 • Block Statement: • At this point of time we will only mention that Block statement is a very useful concurrent statement which provides the following facilities. • 1. By using guarded block statements multiple drivers can be used for the same signal. Synthesizers will translate these into tristate buffers. • 2. By using block statements, we can partition our design. • 3. The scope of signal declarations gets limited to the block. So if different blocks use the same signal names, there will not be any conflict.

CONCURRENT STATEMENTS - 14 • There are other concurrent statements, listed below, which we will discuss at an appropriate point. • These are, Concurrent assertion Concurrent procedure call Component instantiation Generate statement Process statement Out of these the Process statement is a strange statement because it is not a single statement. • While a process itself is viewed as a single concurrent statement, it can contain a number of sequential statements. • When we write VHDL description for any digital system, bulk of the description will be in the form of process statements.