Operations on data path ALU ports can get

- Slides: 6

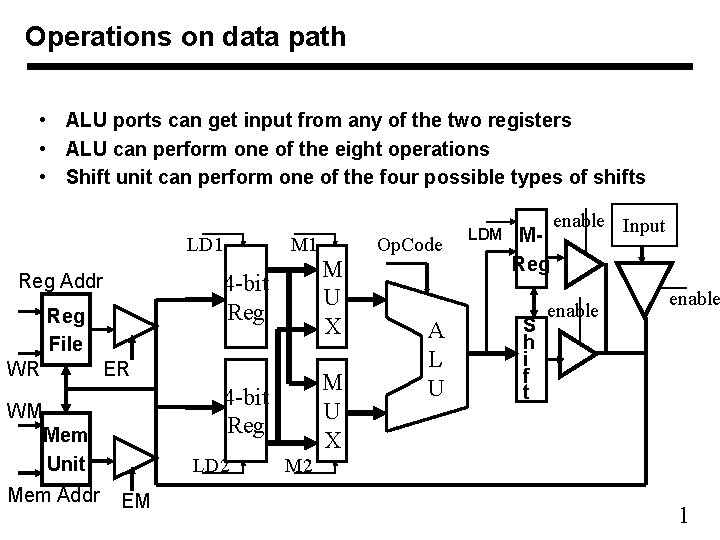

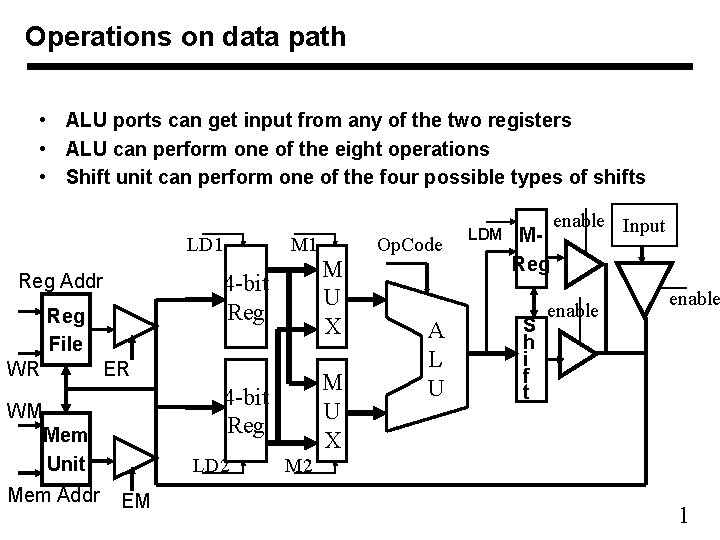

Operations on data path • ALU ports can get input from any of the two registers • ALU can perform one of the eight operations • Shift unit can perform one of the four possible types of shifts LD 1 Reg Addr Reg File WR M 1 4 -bit Reg M U X ER WM Mem Unit Mem Addr LD 2 EM Op. Code A L U LDM enable Input MReg S h i f t enable M 2 1

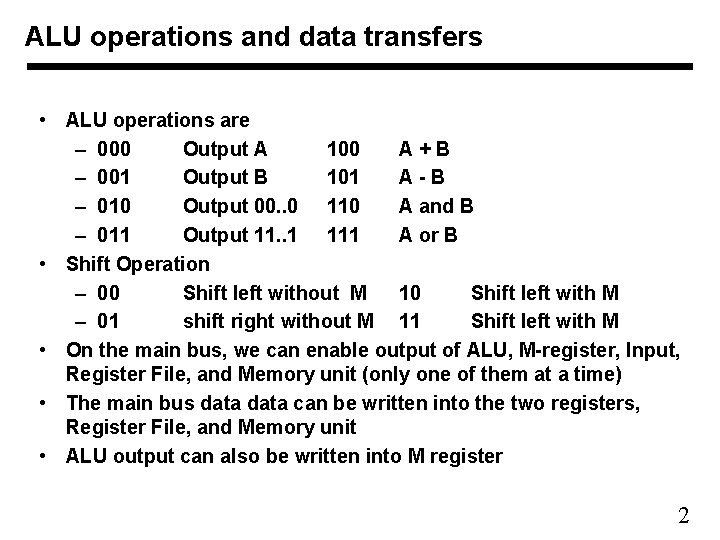

ALU operations and data transfers • ALU operations are – 000 Output A 100 A+B – 001 Output B 101 A-B – 010 Output 00. . 0 110 A and B – 011 Output 11. . 1 111 A or B • Shift Operation – 00 Shift left without M 10 Shift left with M – 01 shift right without M 11 Shift left with M • On the main bus, we can enable output of ALU, M-register, Input, Register File, and Memory unit (only one of them at a time) • The main bus data can be written into the two registers, Register File, and Memory unit • ALU output can also be written into M register 2

Some actual transfers • To transfer Input to any register – Enable input to main bus – Write in register by enabling LD 1 or LD 2 – Other control signals should be asserted in such a way so that they do not cause any change in state • To transfer a register data to M register – Select register through one of the multiplexers – Select ALU operation to transfer selected port to output – Write in M register by asserting LDM signal • To transfer Register file or memory unit output to a register – Select appropriate register in Register file or memory location in memory and enable appropriate unit output to bus – Write in a register using LD 1 or LD 2 3

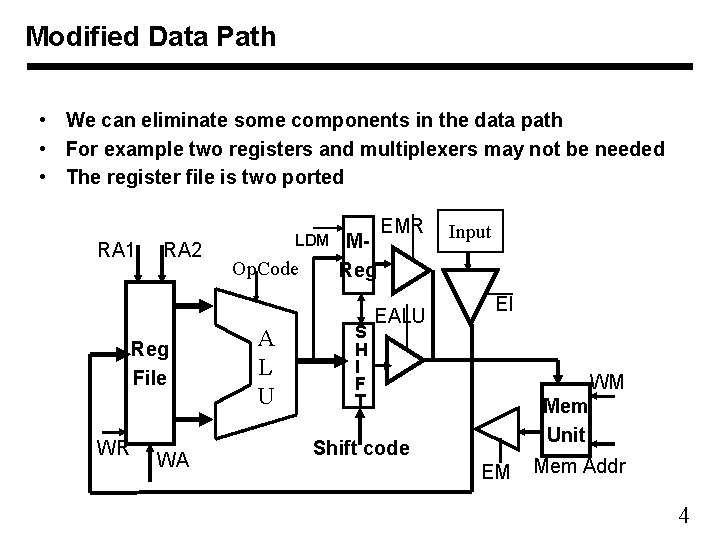

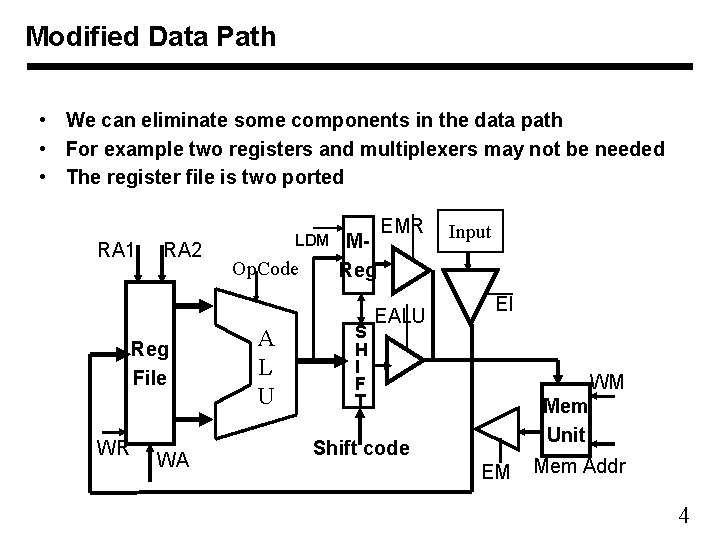

Modified Data Path • We can eliminate some components in the data path • For example two registers and multiplexers may not be needed • The register file is two ported RA 1 RA 2 Reg File WR WA LDM Op. Code A L U MReg S H I F T EMR EALU Input EI WM Mem Unit Shift code EM Mem Addr 4

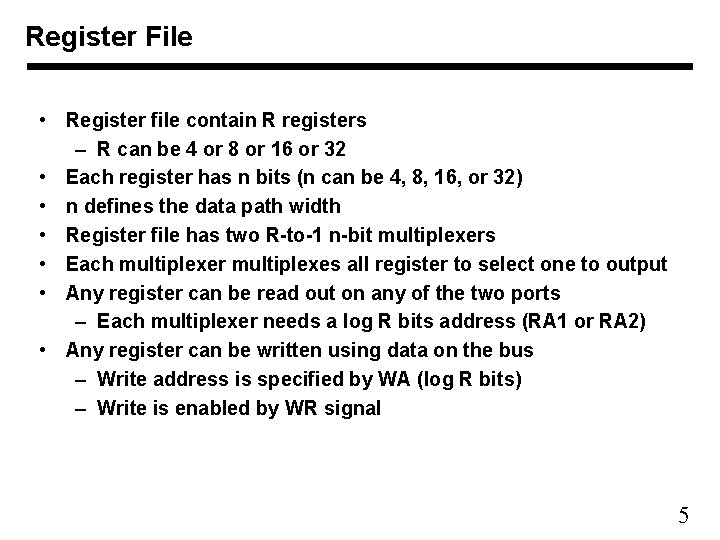

Register File • Register file contain R registers – R can be 4 or 8 or 16 or 32 • Each register has n bits (n can be 4, 8, 16, or 32) • n defines the data path width • Register file has two R-to-1 n-bit multiplexers • Each multiplexer multiplexes all register to select one to output • Any register can be read out on any of the two ports – Each multiplexer needs a log R bits address (RA 1 or RA 2) • Any register can be written using data on the bus – Write address is specified by WA (log R bits) – Write is enabled by WR signal 5

Operations • An instruction specifies is a set of bit specifying an operation • It includes – an operation code to specify an ALU function – RA 1 and RA 2 bits to specify two registers – WA to specify which register to write back – shift code to specify shift operation • Includes operation like no shift, shift left or right with M register – Memory address and control to read or write memory • Not every instruction specifies all instructions • A nano instruction is set of control bits for all units 6