OPERATING SYSTEMS Shared Pages Segmentation CPU Example Sharing

- Slides: 25

OPERATING SYSTEMS

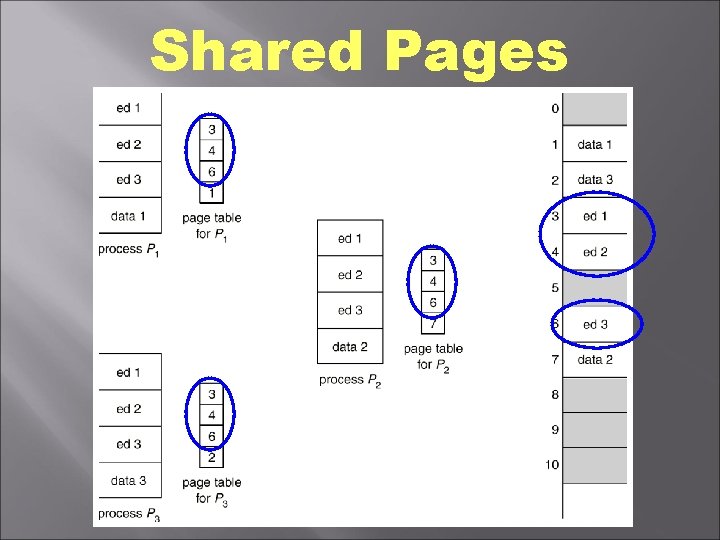

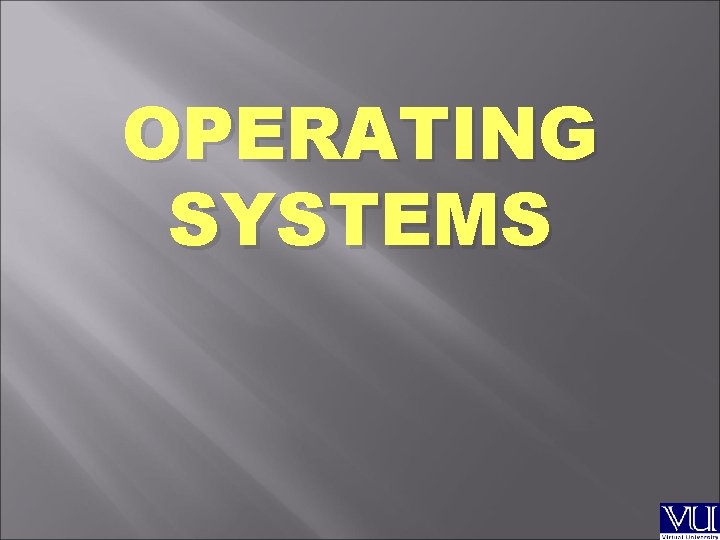

Shared Pages

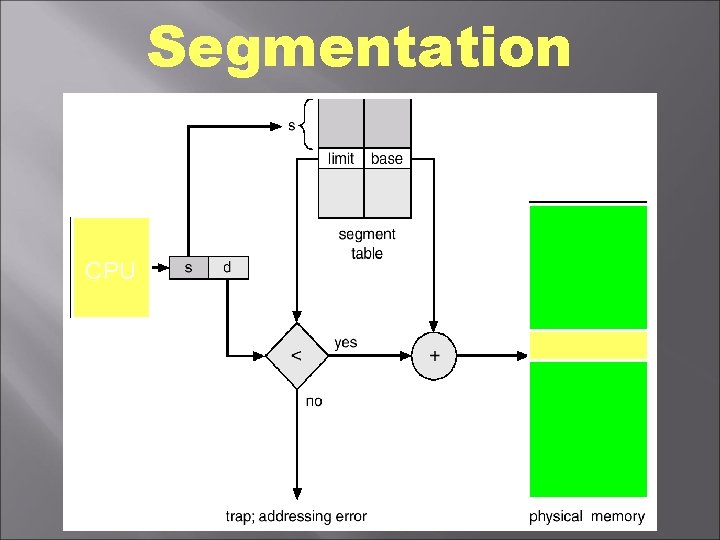

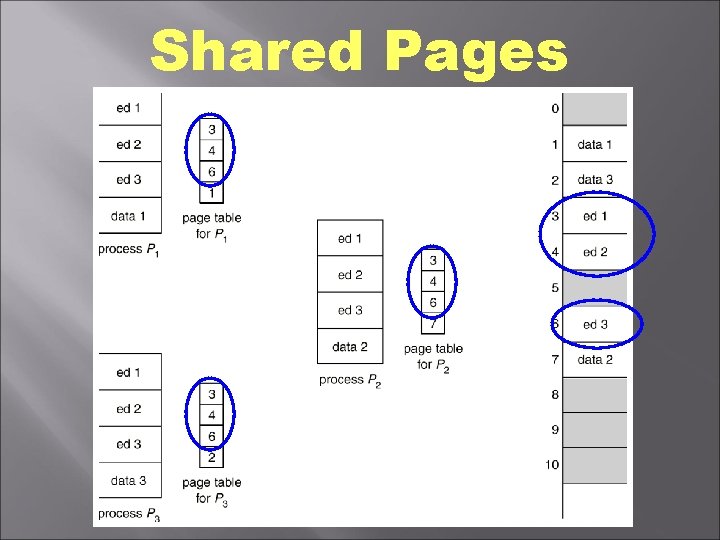

Segmentation CPU

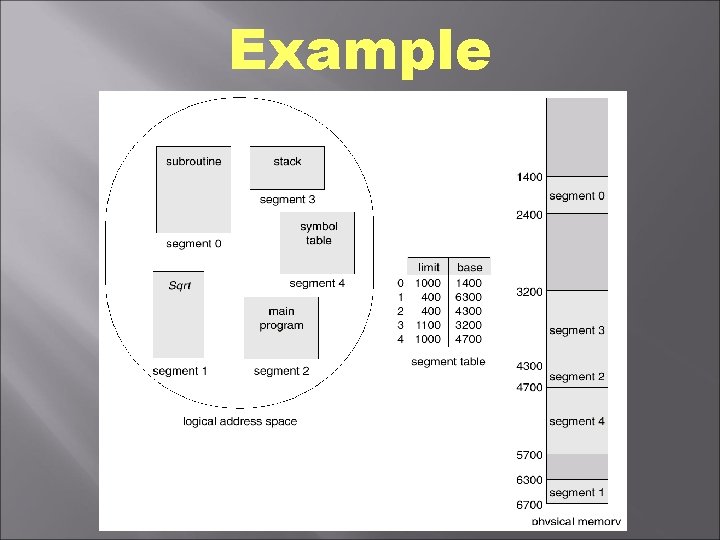

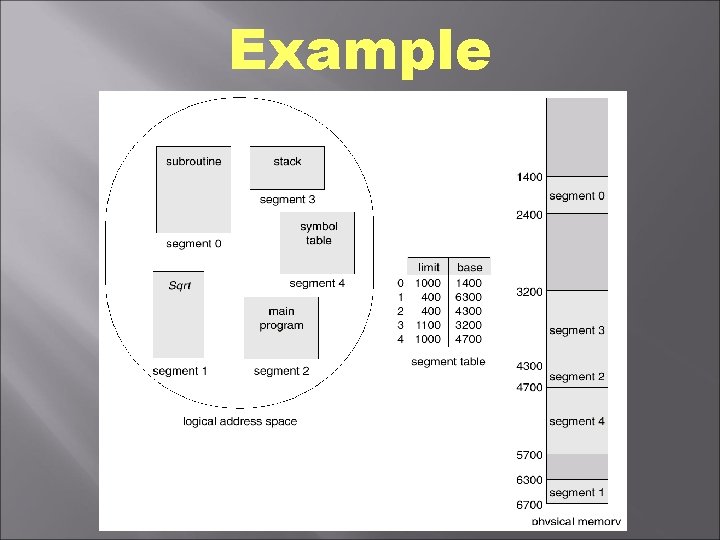

Example

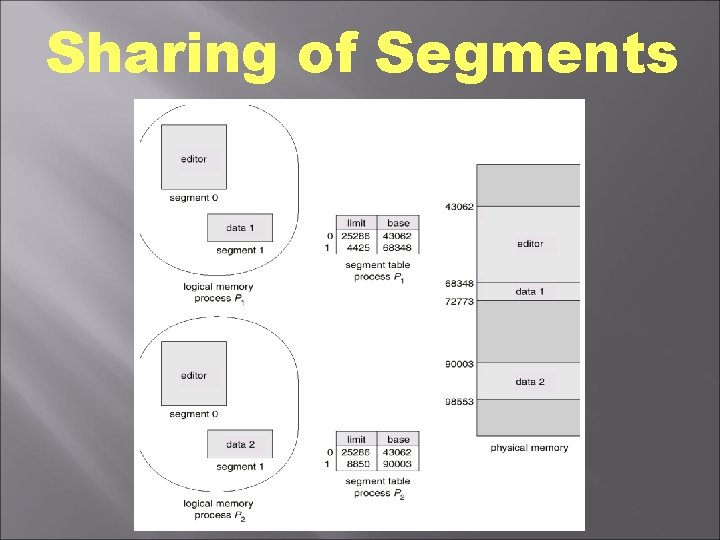

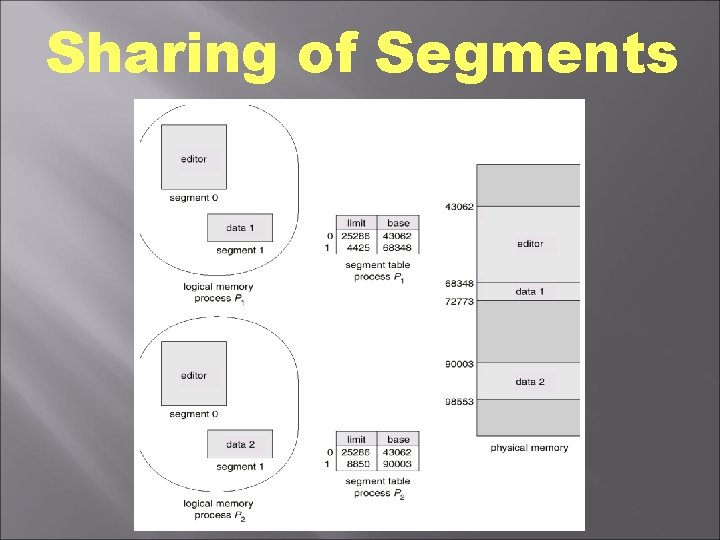

Sharing of Segments

Protection n Associate valid/invalid bit with each segment table entry to indicate if the referenced segment is part of the process address space or not n Read, write, and execute bits to define legal operations on a segment

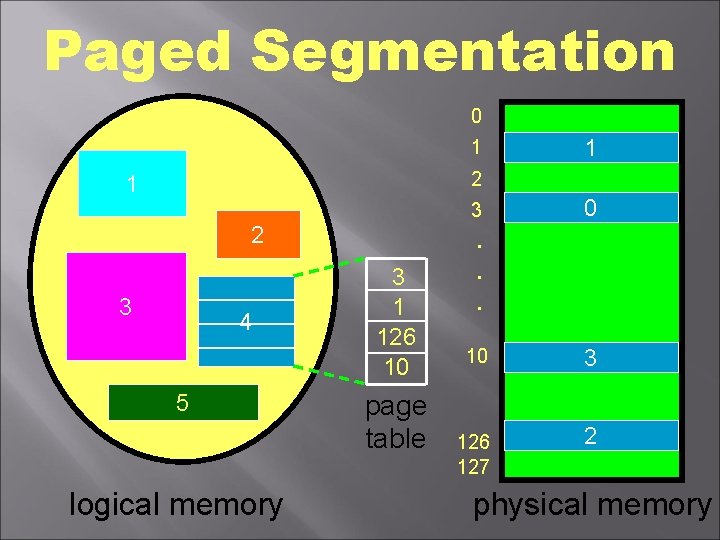

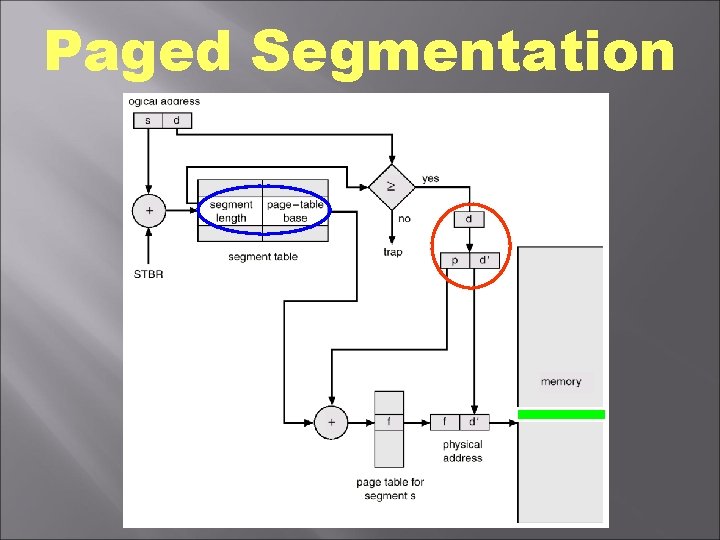

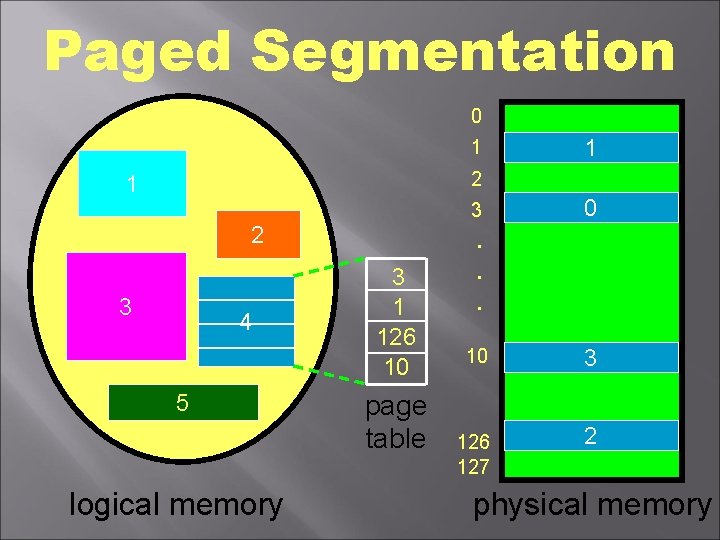

Paged Segmentation n Divide every segment in a process into fixed size pages n Need for a page table per segment n CPU’s memory management unit must support both segmentation and paging

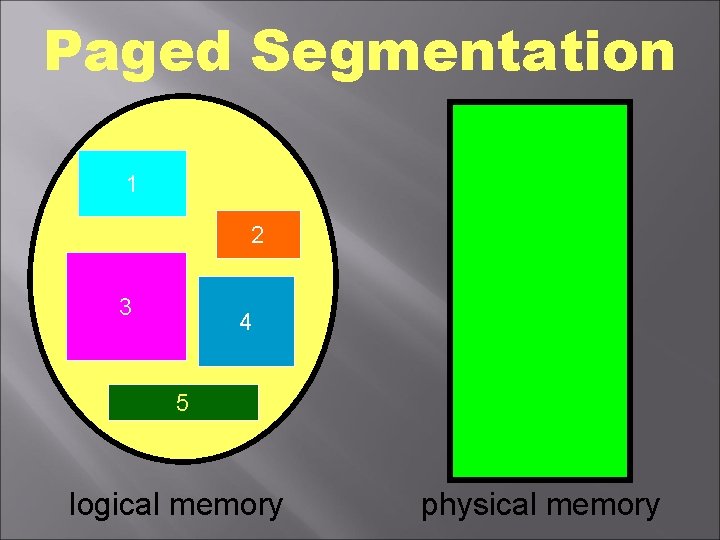

Paged Segmentation 1 2 3 4 5 logical memory physical memory

Paged Segmentation 0 1 1 2 1 3 2 3 4 5 logical memory 0 . 3 1 126 10 page table . . 10 3 126 127 2 physical memory

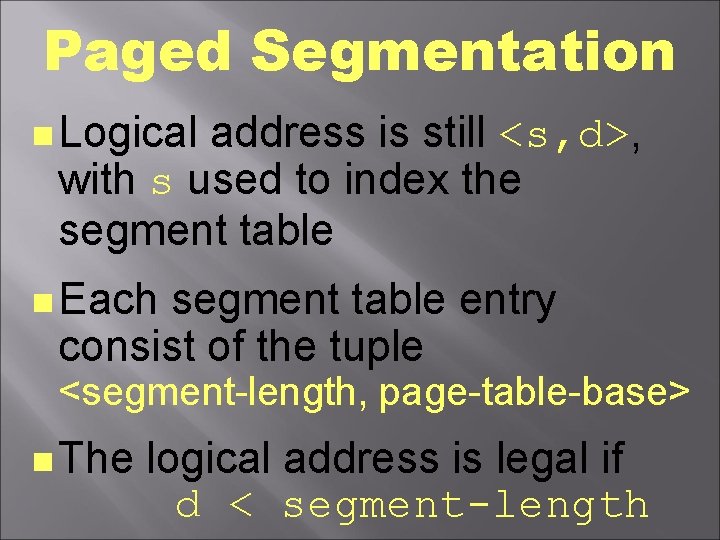

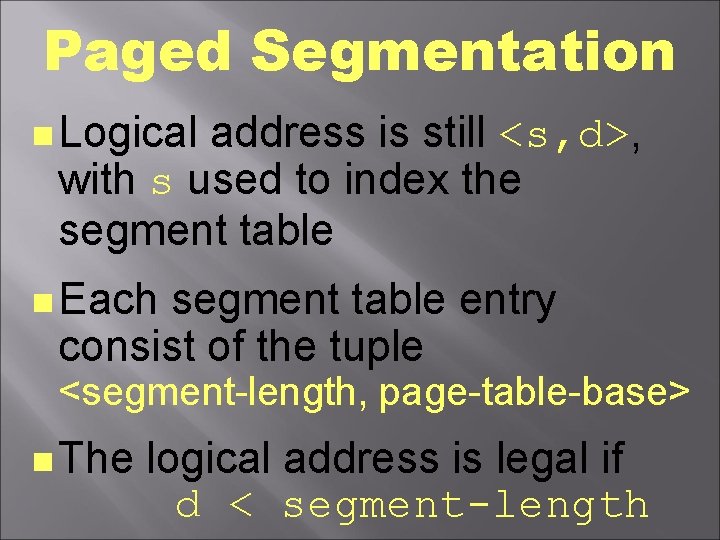

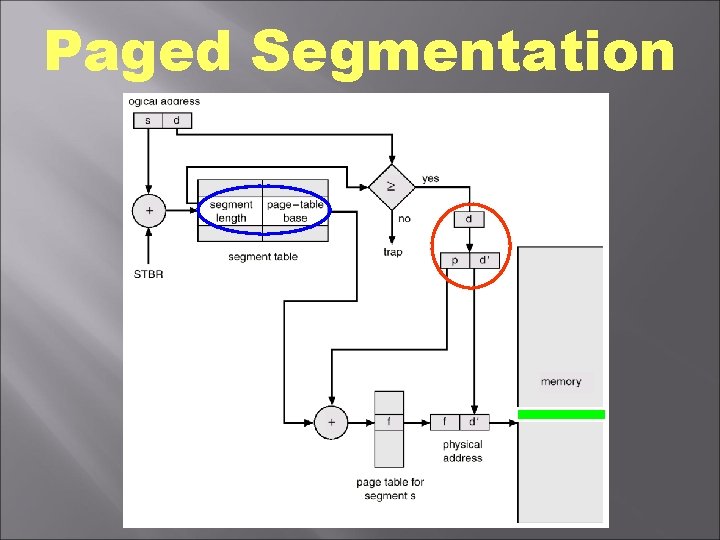

Paged Segmentation n Logical address is still <s, d>, with s used to index the segment table n Each segment table entry consist of the tuple <segment-length, page-table-base> n The logical address is legal if d < segment-length

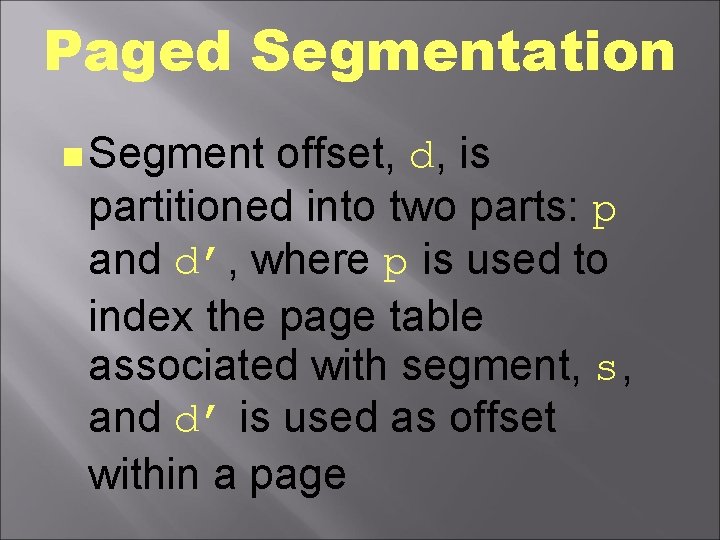

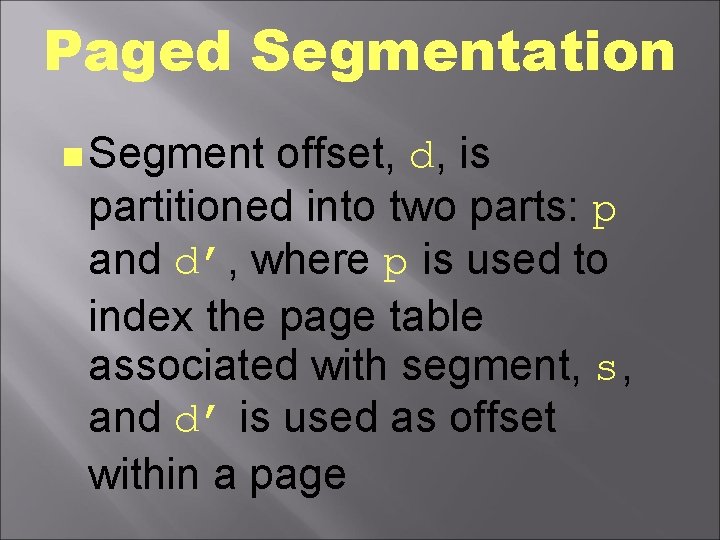

Paged Segmentation n Segment offset, d, is partitioned into two parts: p and d’, where p is used to index the page table associated with segment, s, and d’ is used as offset within a page

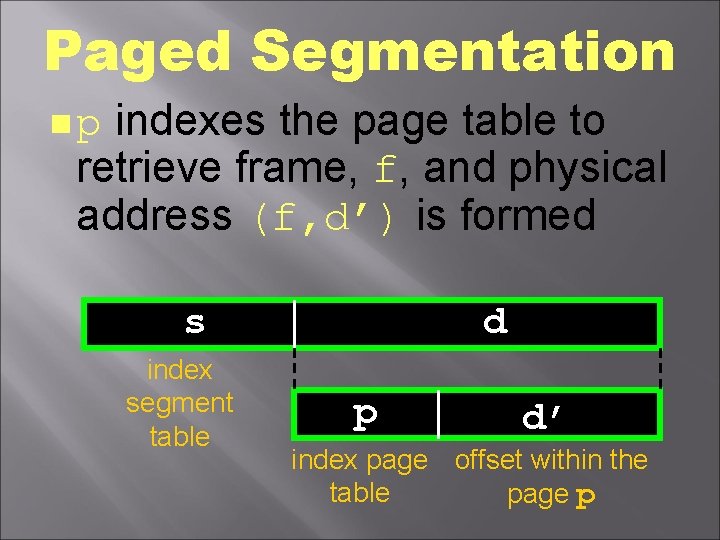

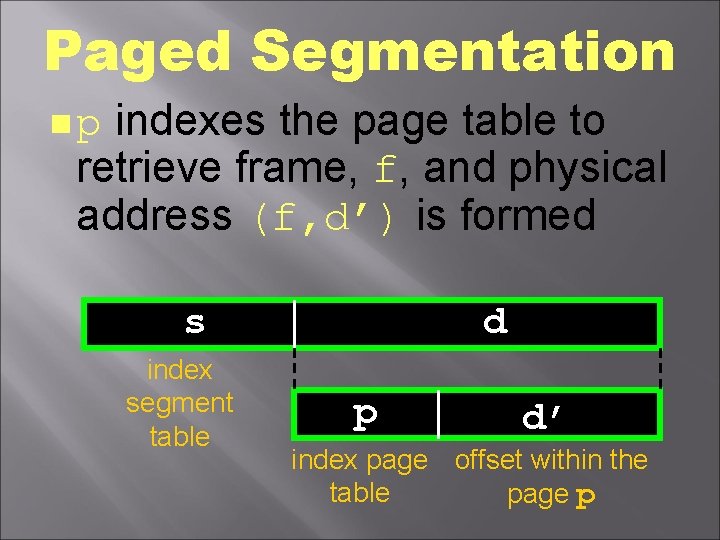

Paged Segmentation indexes the page table to retrieve frame, f, and physical address (f, d’) is formed np s index segment table d p d’ index page offset within the table page p

Paged Segmentation

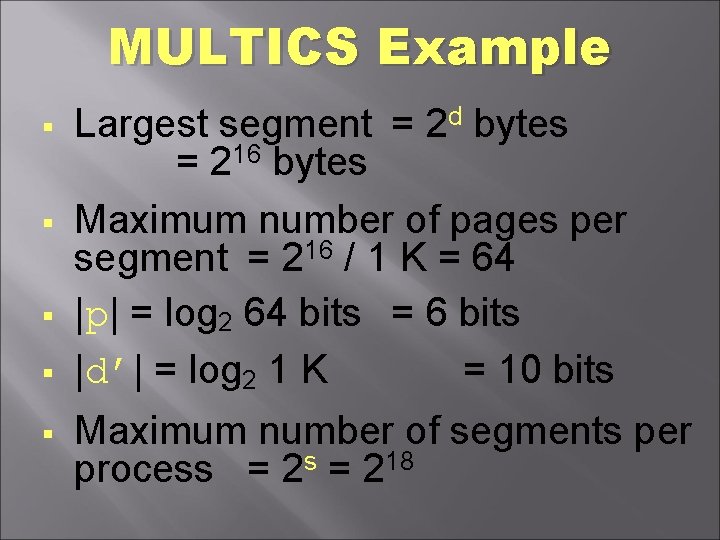

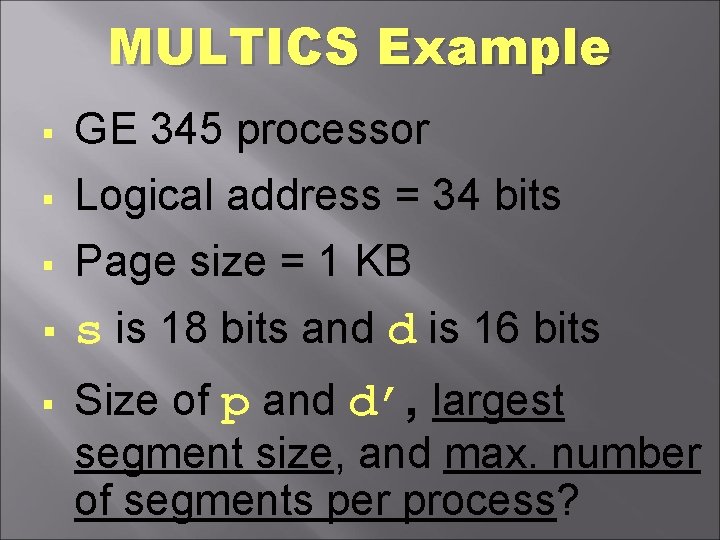

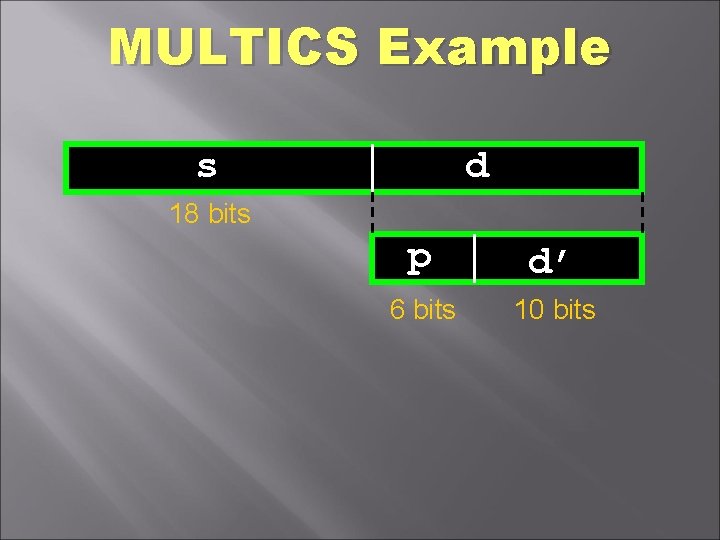

MULTICS Example § § § GE 345 processor Logical address = 34 bits Page size = 1 KB s is 18 bits and d is 16 bits Size of p and d’, largest segment size, and max. number of segments per process?

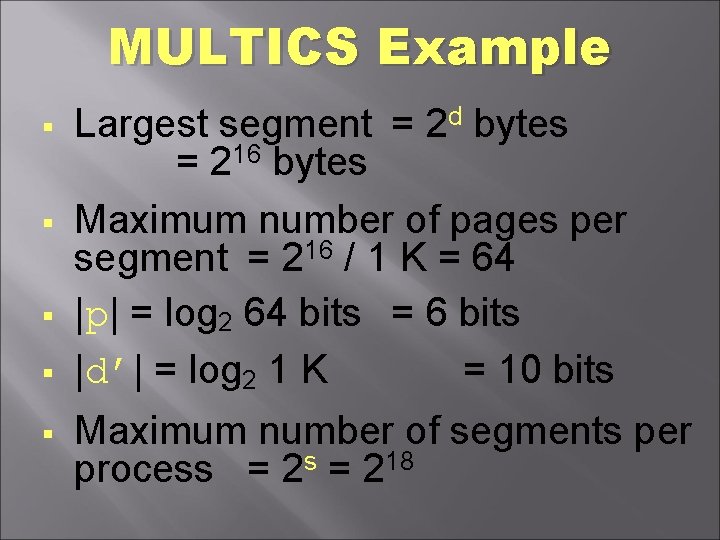

MULTICS Example § § § Largest segment = 2 d bytes = 216 bytes Maximum number of pages per segment = 216 / 1 K = 64 |p| = log 2 64 bits = 6 bits |d’| = log 2 1 K = 10 bits Maximum number of segments per process = 218

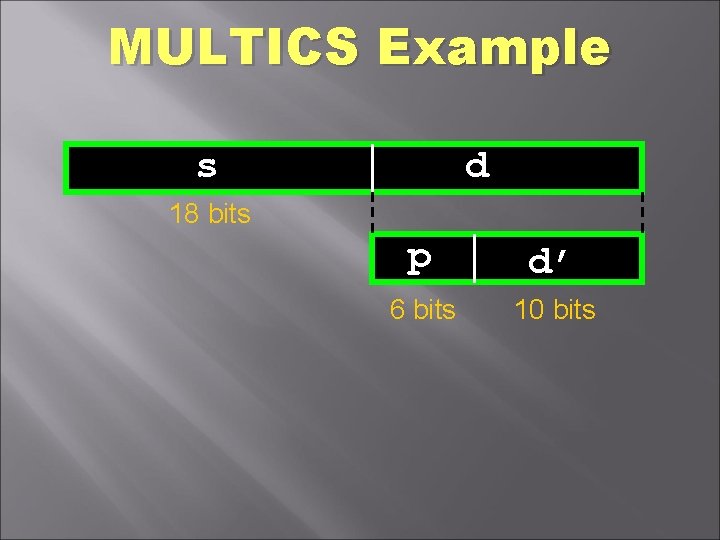

MULTICS Example s d 18 bits p d’ 6 bits 10 bits

MULTICS Example § § Consider a process with its segment 15 having 5096 bytes. The process generates a logical address (15, 3921). Is it a legal address? How many pages does the segment have? What page does the logical address refer to?

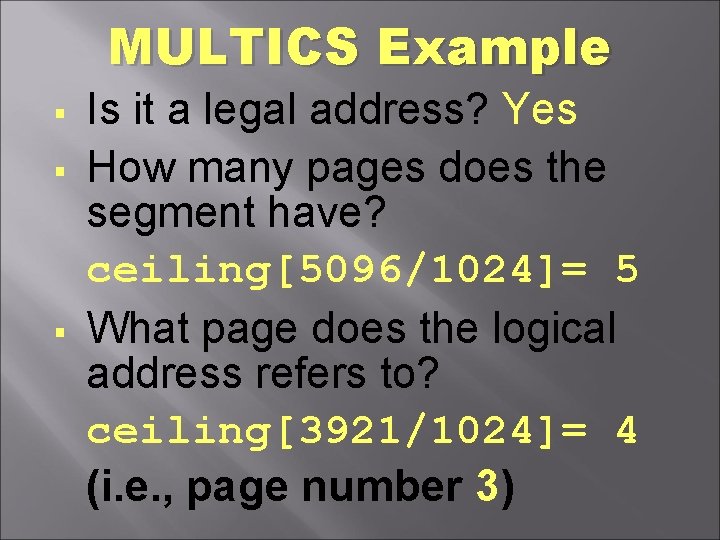

MULTICS Example § § § Is it a legal address? Yes How many pages does the segment have? ceiling[5096/1024]= 5 What page does the logical address refers to? ceiling[3921/1024]= 4 (i. e. , page number 3)

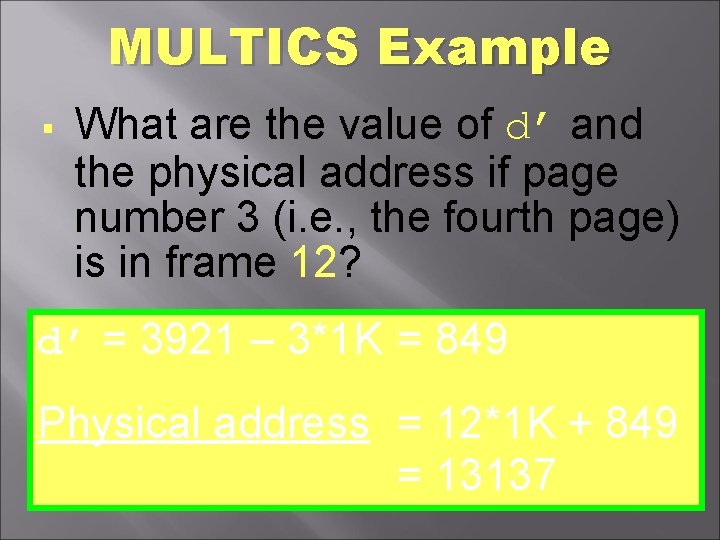

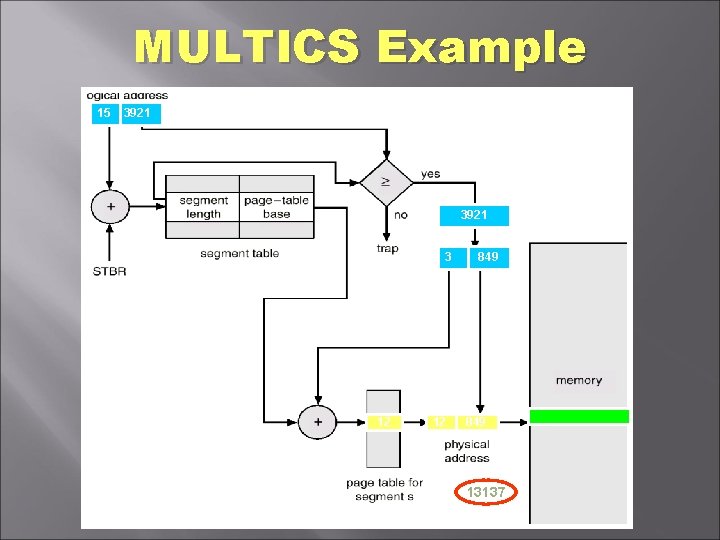

MULTICS Example § What are the value of d’ and the physical address if page number 3 (i. e. , the fourth page) is in frame 12? d’ = 3921 – 3*1 K = 849 Physical address = 12*1 K + 849 = 13137

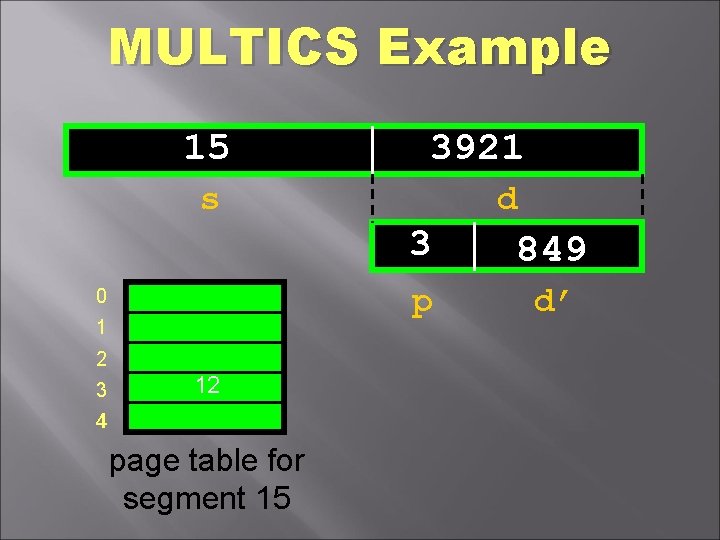

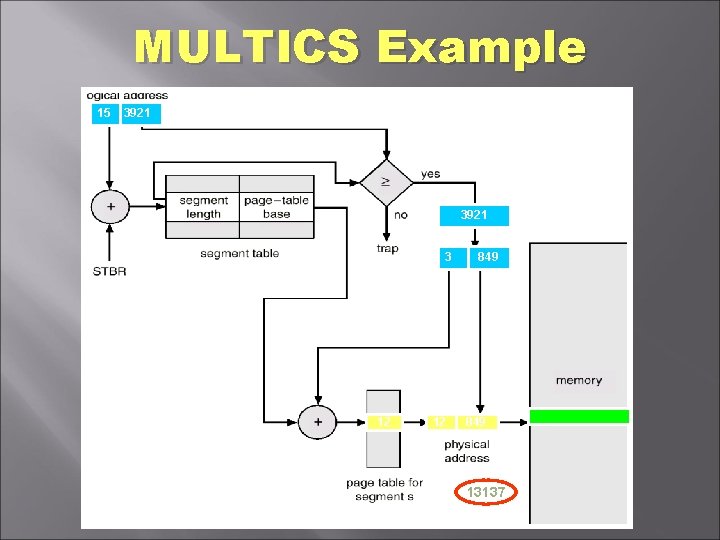

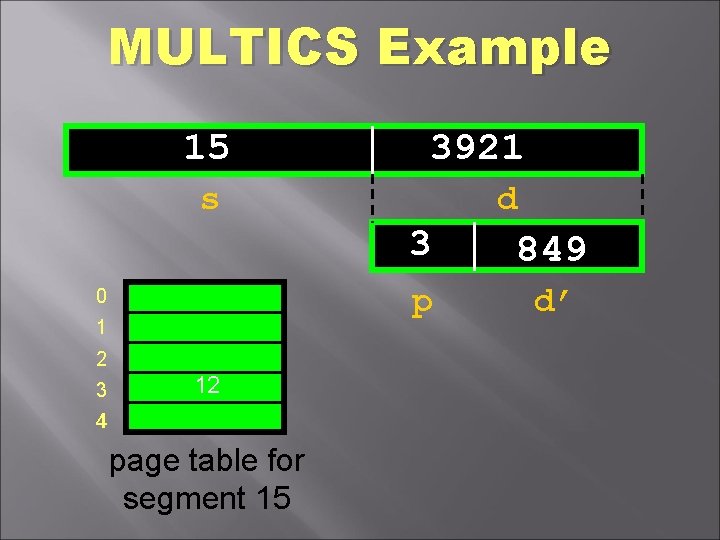

MULTICS Example 15 3921 s d 0 1 2 3 12 4 page table for segment 15 3 849 p d’

MULTICS Example 15 3921 3 12 12 849 13137

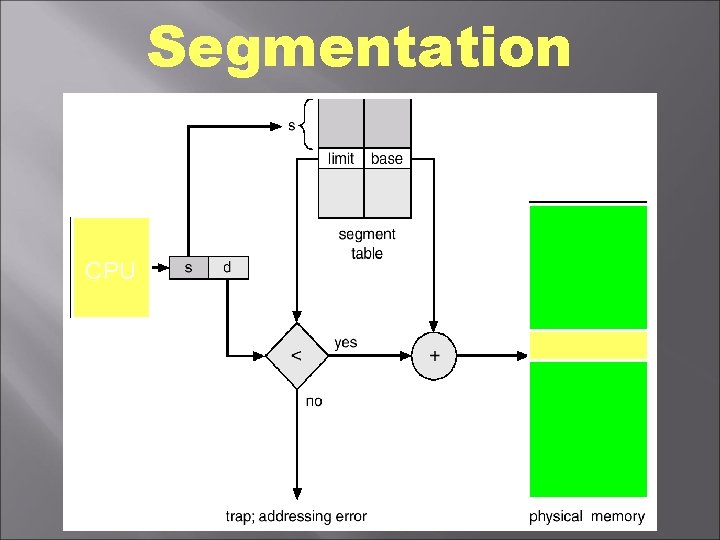

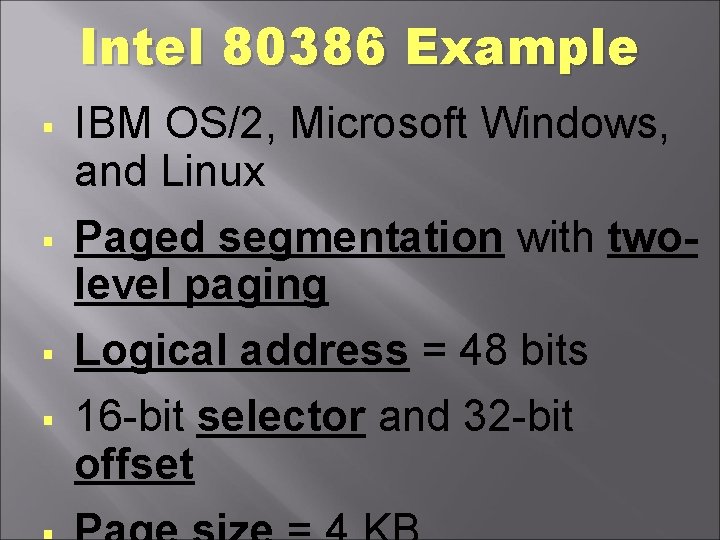

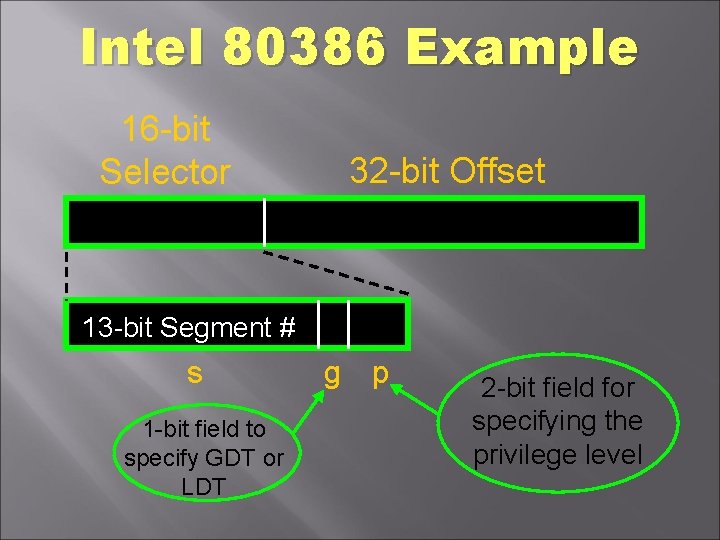

Intel 80386 Example § § IBM OS/2, Microsoft Windows, and Linux Paged segmentation with twolevel paging Logical address = 48 bits 16 -bit selector and 32 -bit offset

Intel 80386 Example § 4 -byte page table entry § 32 -entry TLB, covering 32*4 K (128 KB) memory … TLB Reach

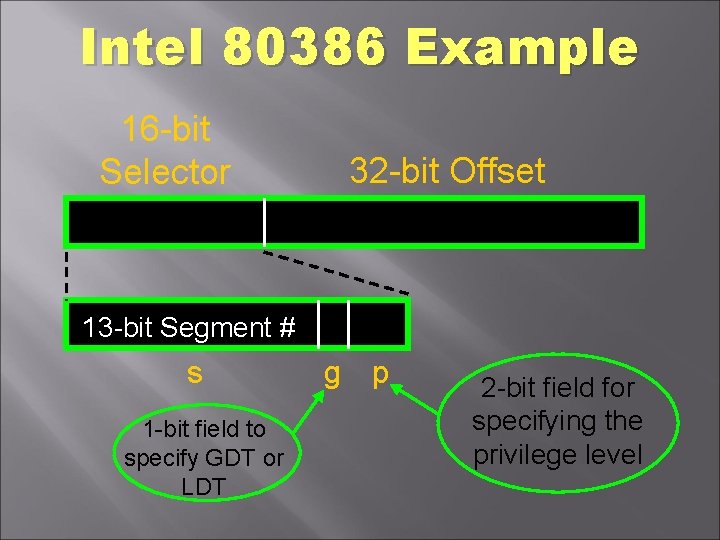

Intel 80386 Example 16 -bit Selector 32 -bit Offset 13 -bit Segment # s 1 -bit field to specify GDT or LDT g p 2 -bit field for specifying the privilege level

Intel 80386 Example § Real Mode 20 -bit physical address is obtained by shifting left the Selector value by four bits and adding to it the 16 -bit effective address