Operating systems and processors and storage Revision Storage

- Slides: 55

Operating systems and processors and storage Revision Storage media Microprocessors Operating systems

l l l The data on a disk is stored in a binary form as magnetic dots along the tracks. The read/write head (R/W head) detects the polarity, because there are only two polarities, there are only two states. The pattern of pulses produced by the R/W head in relation to the drive timing is translated into data and sent to the CPU.

Optical media l l l Disk has holes burnt in it by a laser to record the binary code. A hole or pit on the disk reflects less light than the surface of the disk. By detecting the difference in reflected light in relation to the time of the drive, a pattern of pulse is produced and this is translated into data sent to the CPU.

Compact Disks and DVD l CDs – – – l optical media storing approximately 650 MB of data. Use basic principle on previous slide. DVD – – the same basic principle as a CD, data is packed more densely it has a larger capacity (4. 7 GB) as compared to a CDs 650 MB, smaller and narrower pits. quicker transfer rate than a CD. Better compression algorithms help to improve the capacity.

Microprocessors

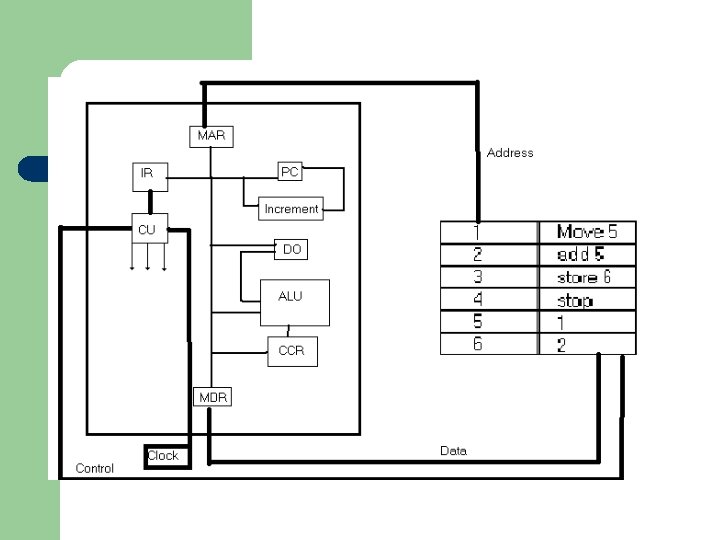

Fetch l All programs are stored in memory, and have to be ‘fetched’ from memory before they can be carried out (executed). l Before the CPU can use an instruction, the instruction must be brought to the CPU from the memory.

Starting with a program counter (PC) this points to the memory location/address of the next instruction to be executed. Therefore, if the contents of the PC were 5, the next instruction to be executed is stored in memory location 5.

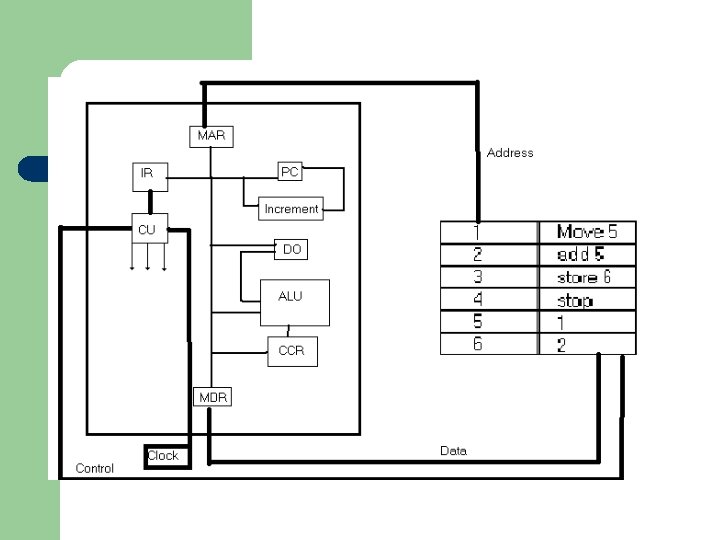

l l The contents of the program counter are copied to the memory address register (MAR). The program counter contents are then incremented to the next instruction. The MAR holds the address of the memory location where in memory the data is to be used is located. Note: The MAR does not just do this in the fetch part. If you taking something out of memory or putting something into memory the address of the memory location has to be there

l The contents of MAR during this part of the cycle contains address of the instruction to be executed, the contents of this memory location are placed into the memory data register (MDR).

l l During this part of the cycle the data that is passed from memory is an instruction. The instruction is moved from the MDR to the instruction register (IR) where it is divided into two fields.

l One field is the operation code often shortened to opcode, which tells the CPU the instruction to carry out. l The second field is the operand field, which contains the address/data (or addresses) of data used by the instruction. Sometimes the operand field is not used.

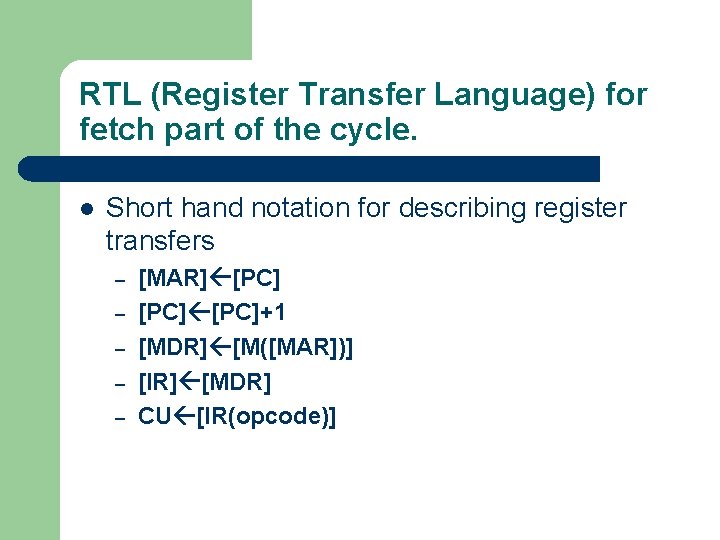

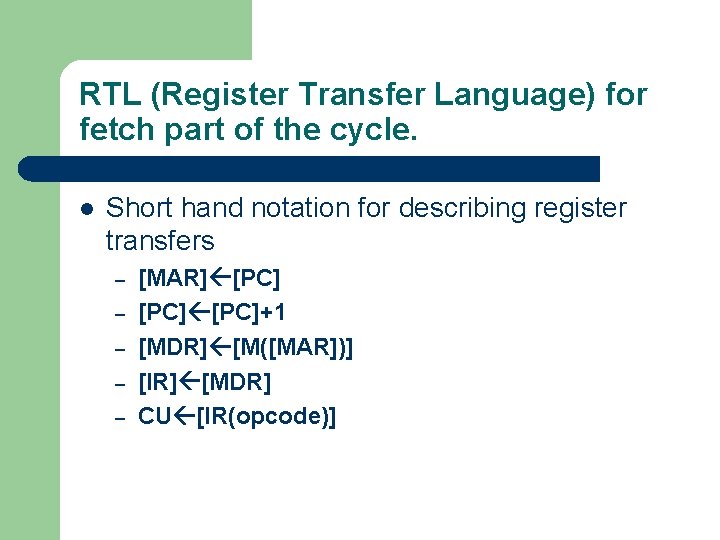

RTL (Register Transfer Language) for fetch part of the cycle. l Short hand notation for describing register transfers – – – [MAR] [PC]+1 [MDR] [M([MAR])] [IR] [MDR] CU [IR(opcode)]

l The next stage is the decode-execute cycle where the control unit takes the opcode from the instruction register, and generates the control signals to control the various parts of the CPU. The control unit is responsible during the fetch cycle for all the operations to make the fetch happen

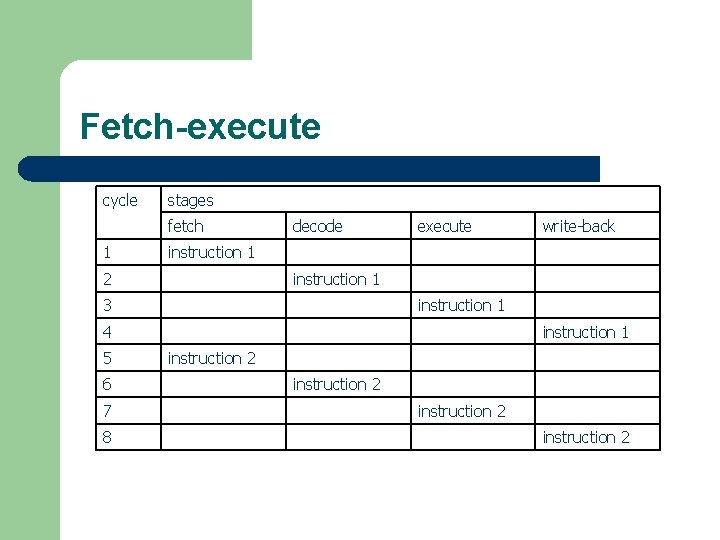

l l l Pipelining is a key technique used to make faster CPUs. Processors allow instructions to be executed in stages; stages implemented using separate hardware. Stages connected together forming an instruction pipeline, allowing more than one instruction to be processed at the same time.

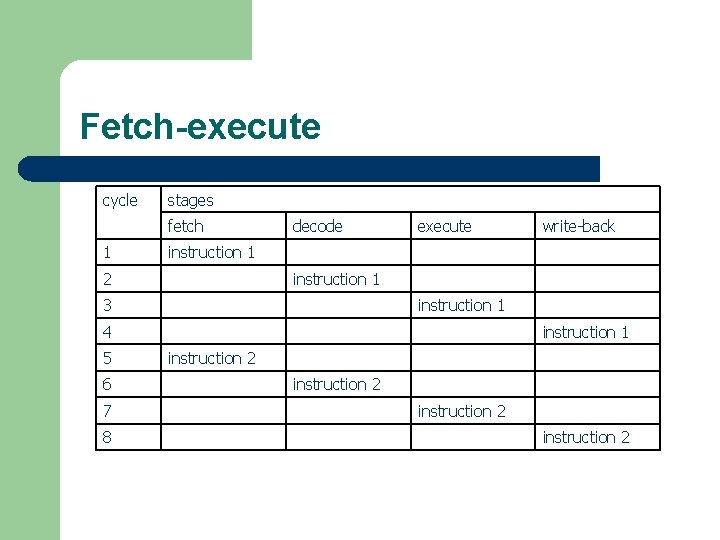

Fetch-execute cycle stages fetch 1 decode execute instruction 1 2 instruction 1 3 instruction 1 4 5 6 7 8 write-back instruction 1 instruction 2

Pipelining

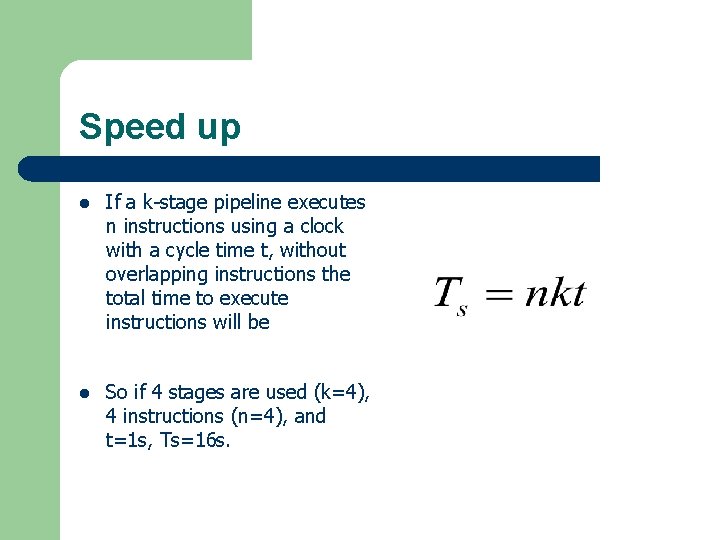

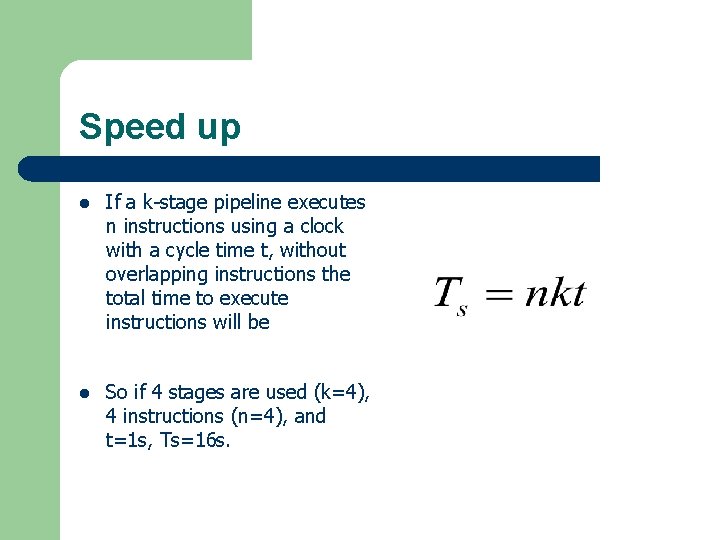

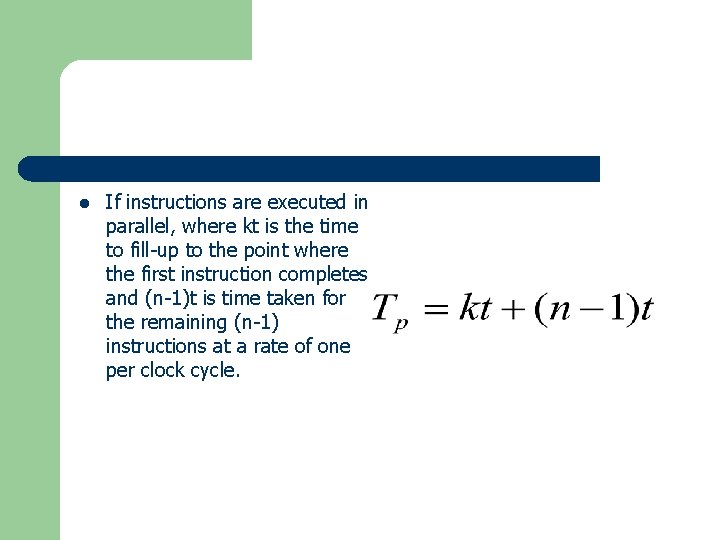

Speed up l If a k-stage pipeline executes n instructions using a clock with a cycle time t, without overlapping instructions the total time to execute instructions will be l So if 4 stages are used (k=4), 4 instructions (n=4), and t=1 s, Ts=16 s.

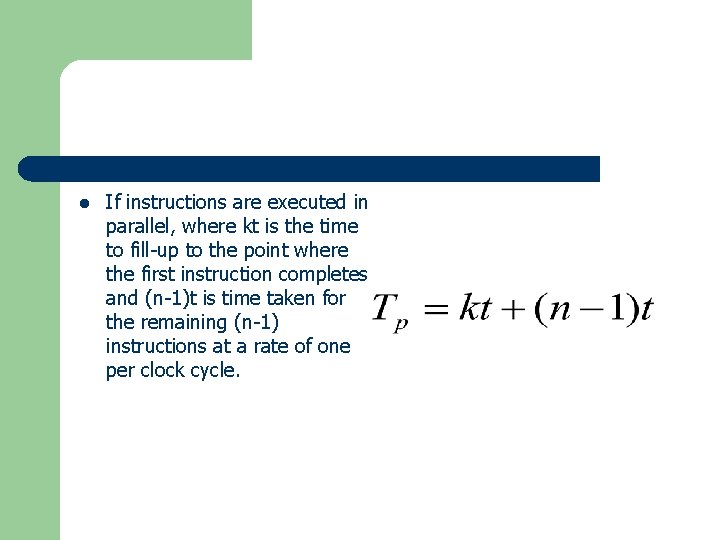

l If instructions are executed in parallel, where kt is the time to fill-up to the point where the first instruction completes and (n-1)t is time taken for the remaining (n-1) instructions at a rate of one per clock cycle.

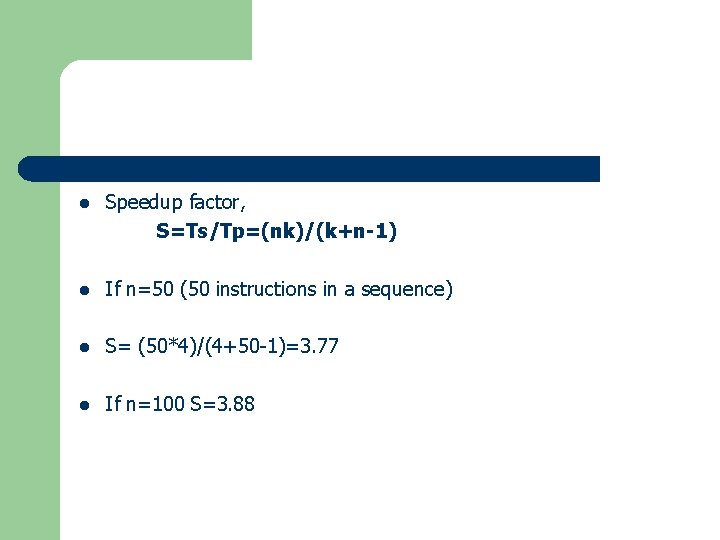

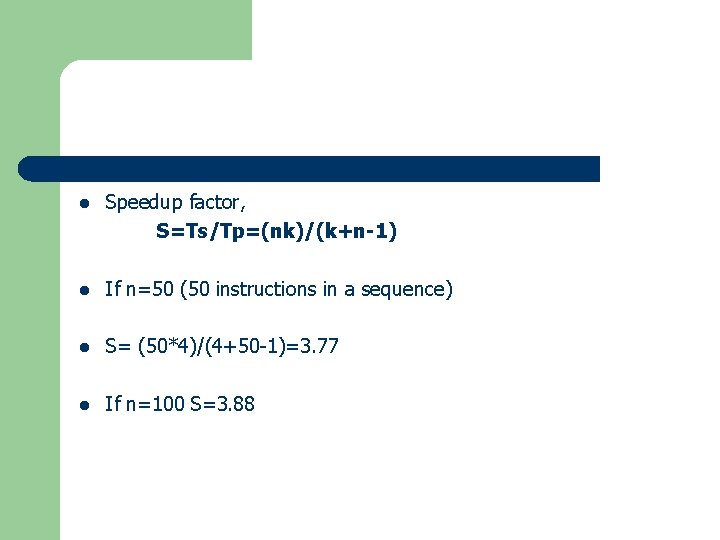

l Speedup factor, S=Ts/Tp=(nk)/(k+n-1) l If n=50 (50 instructions in a sequence) l S= (50*4)/(4+50 -1)=3. 77 l If n=100 S=3. 88

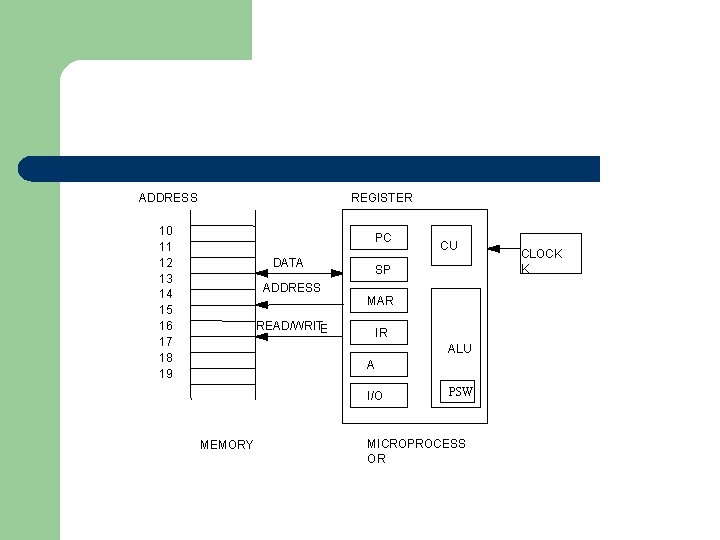

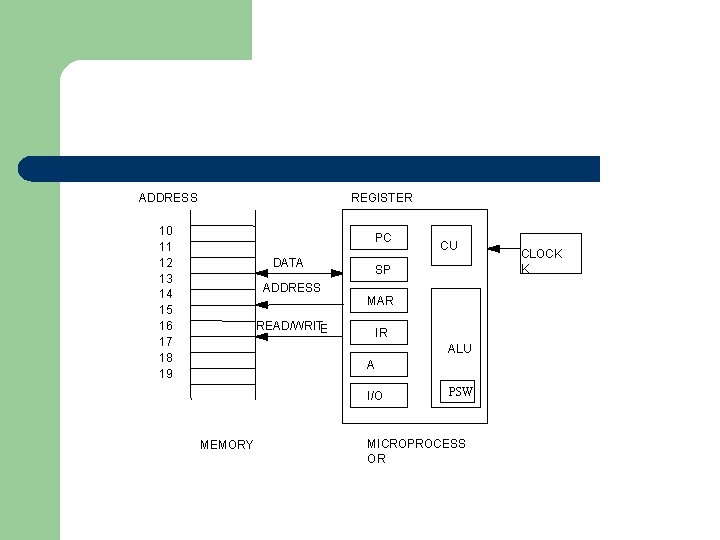

ADDRESS REGISTER 10 11 12 13 14 15 16 17 18 19 PC DATA ADDRESS READ/WRITE CU SP MAR IR ALU A I/O MEMORY PSW MICROPROCESS OR CLOCK K

l l Arithmetic and Logic Unit (ALU) This carries out arithmetic operations such as adding or subtracting, and logical operations. Control Unit (CU) This controls the execution of instructions. Input and Output Ports (I/O) Communicates with the outside world, either reading in data or sending data out. Clock This produces regular pulses which controls the rate at which instructions are carried out.

Registers l l A register is a small storage unit which holds a single piece of data. Program status word: This register contains information about the result of operations such as if the result is negative or zero.

Complex instructions l l Early computers had small, simple instructions. Computers that are more powerful were wanted, so more powerful and complicated instructions were needed. Complex instructions often lead to faster program execution, but the time taken to perform an instruction may take longer. Complex instructions were also better because the execution of individual operations could be overlapped, or otherwise executed in parallel.

l Initially these processors were designed with a smaller number of instructions around 50, so name Reduced Instruction set computer (RISC) in contrast with Complex instruction set Computer (CISC) (VAX, etc). Later RISC processors may have larger set of instructions.

Why has RISC not replaced CISC completely? l l l Backward compatibility, billons pounds (or dollars) have been invested in software for the Intel line Intel employed some of the RISC ideas in the 486 s upwards. It contained a RISC core to execute simplest and most common instructions, while the more complicated instructions in the usual CISC way. So common instructions are generally fast and less common instructions are slow. hybrid approach not a pure RISC design. This allows higher performance but still allowing old software to run unmodified.

ALU l Arithmetic Logic Unit l Carries out all arithmetic operations l Carries out all logic operations, including comparison (>, <. equal to, not equal to, etc) not just ANDs, Ors, etc.

General principles l l l All instructions are directly executed by hardware Maximise rate at which instructions are issued Instructions should be easy to decode Only load and stores should reference memory Plenty of registers

All instructions are directly executed by hardware l All common instructions are directly executed by the hardware, eliminating the interpretation provides higher speed for instructions. CISC (Complex Instruction Sets) instruction sets, complex instructions are broken down into simpler instructions, extra steps slow down, if these instructions are not frequently used it may be acceptable

Maximise rate at which instructions are issued: Parallelism is a powerful way to improve performance by using multiple instructions executed at once.

Instructions should be easy to decode l A limit on the rate of instructions decode is determine by what resources are needed. Making instructions regular, fixed length, and having small number of fields, are methods that can aid this process.

Only load and stores should reference memory: l l Using main memory is slower than registers. Operations of moving memory to register can be performed in separate instructions. Only the load and store instructions should reference memory.

Plenty of registers l Accessing memory is slow, so many registers (over 32) may be needed, and so once data is fetched, it can be kept in a register until it is no longer needed. Running out of registers, and having to send data into memory, only to reload them is undesirable and should be avoided as much as possible. An adequate number of registers are needed.

Example AVR instructions l l ldi ldi r 18, 0 xff r 18, 0 b 1111 r 18, 255 These all do the same thing they put the value (load) of 255 into register r 18, as either a hexadecimal, binary, or decimal number. Look up some of these other instructions you used in the practical.

Operating systems

What is an operating system? l A short definition of an operating system: An operating system is a collection of system programs that manage the resources of a computer and control the running of user programs.

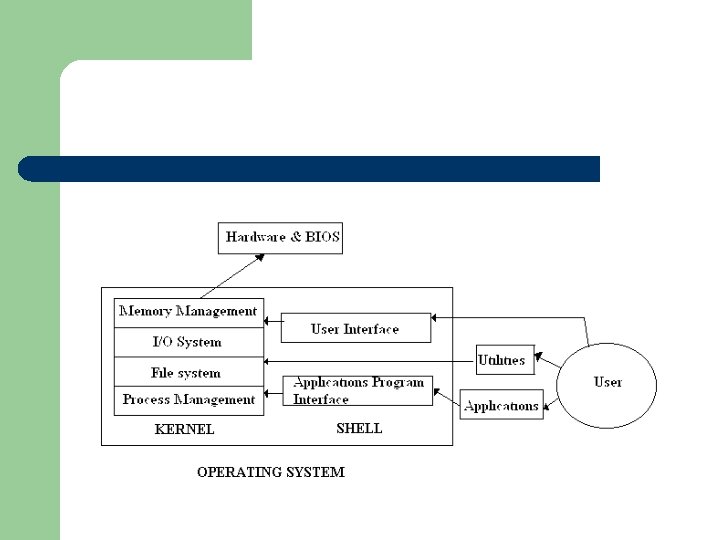

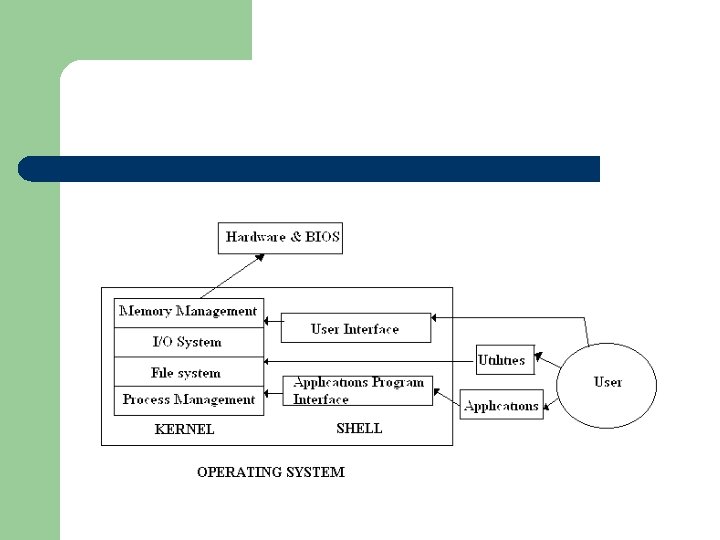

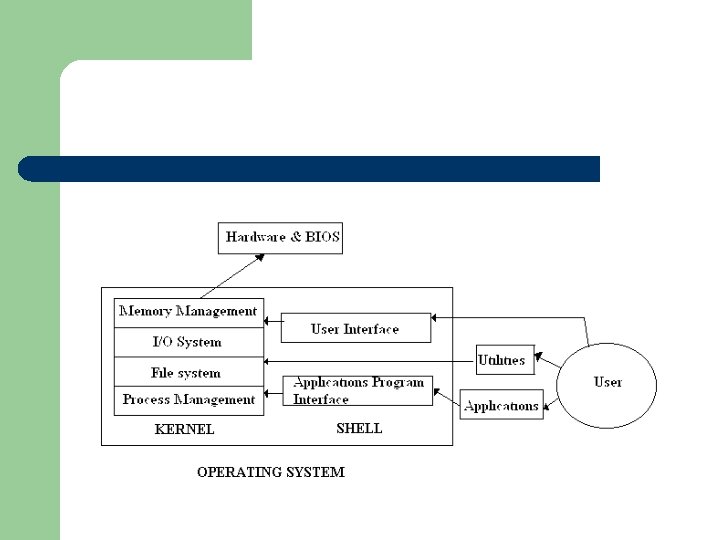

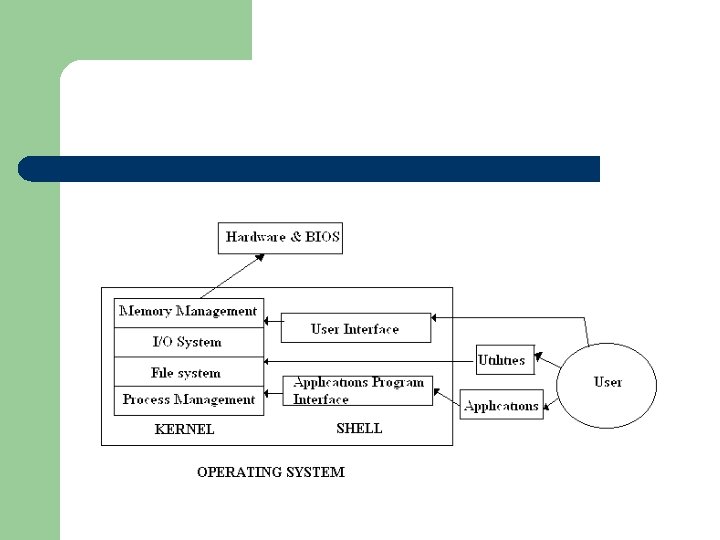

l Kernel – – l Central part of the operating system. All hardware requests go through the kernel as system calls Shell – The interfaces for the applications programs and users, with the operating system.

l Process manager deals with – – hardware/software interrupts. Processor errors Scheduling tasks Communication between tasks

l Memory Management – – – Allocate memory Ensures processes (see next week’s lecture) stay memory boundaries Controlling virtual memory

l I/0 System – – Communicates with peripherals and hardware components Co-ordinates i/o systems such as interrupts and direct memory access

l Files system – – – Organises and accesses files Maintains on a multi-user system user file quotas Controls file/record access

l Application Program Interface – – Provides systems services for applications An interface between the applications and the operating system.

l User interface – – – Allows the user access to programs Allows the user to view and change system settings. A consistent interface between the user and the operating system.

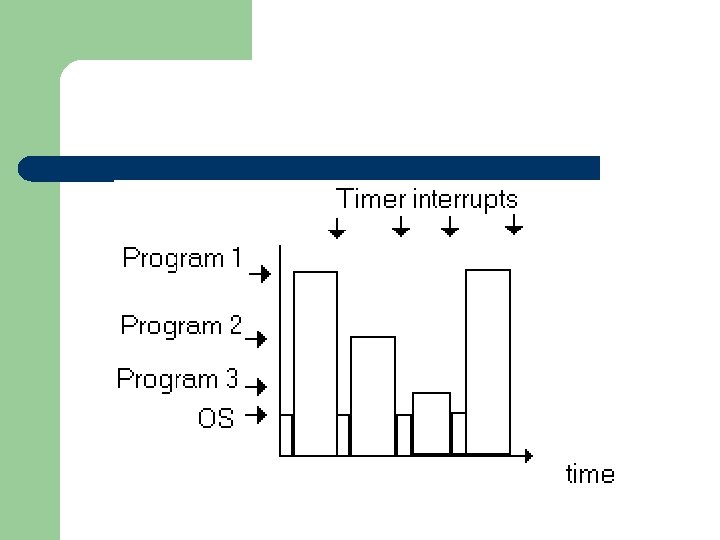

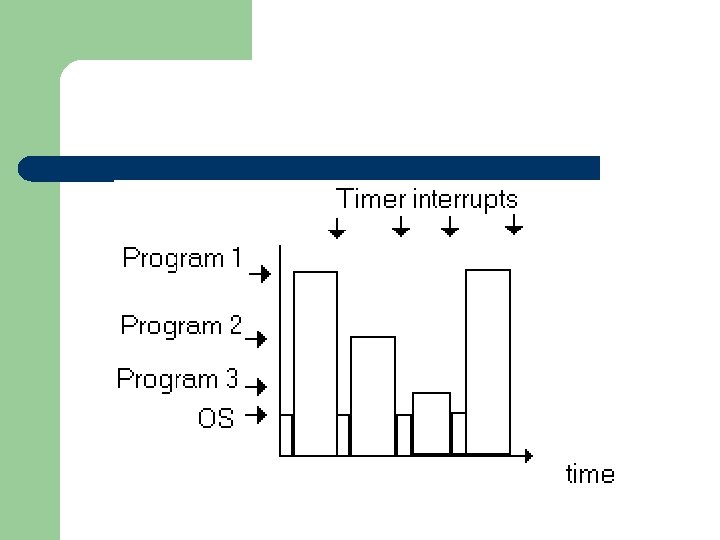

l Most modern operating systems have the ability to execute several programs at once, although there is usually one processor in the system. This is multiprogramming and is made possible by rapidly switching the processor between programs. Interrupting the processor periodically, gives the programs control of the processor for a short period.

l This switching is triggered by a piece of hardware called the interval timer, which generates an interrupt (a time-out interrupt) when the programmed period has elapsed. The interrupt handler, then saves the context of the processor. The context is the contents of registers that may be overwritten by other programs. Control is passed over to the dispatcher/low-level scheduler.

l The dispatcher searches a set of potentially 'runnable' program using a scheduling algorithm to select a suitable program to run next. The context of the processor, which existed when that program last ran, is restored to the registers.

l A process consists of an executable program, the data associated with the program, and it’s execution context. The execution context includes the processor context, but also information such as the process identifier, priority level, and a process state

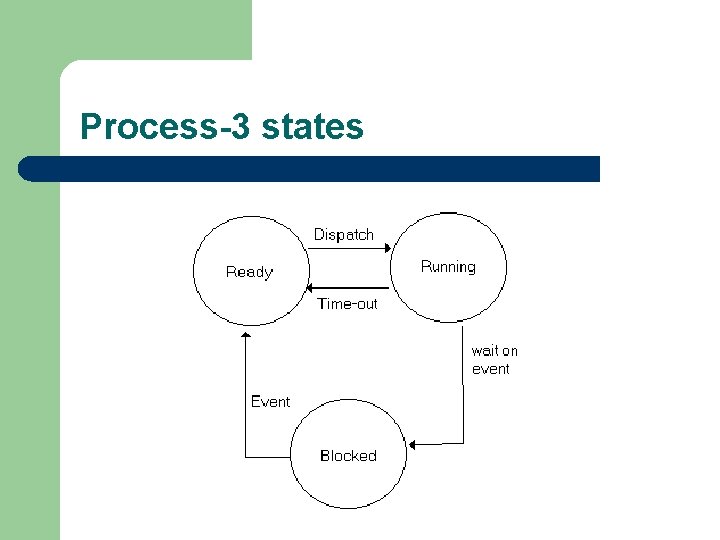

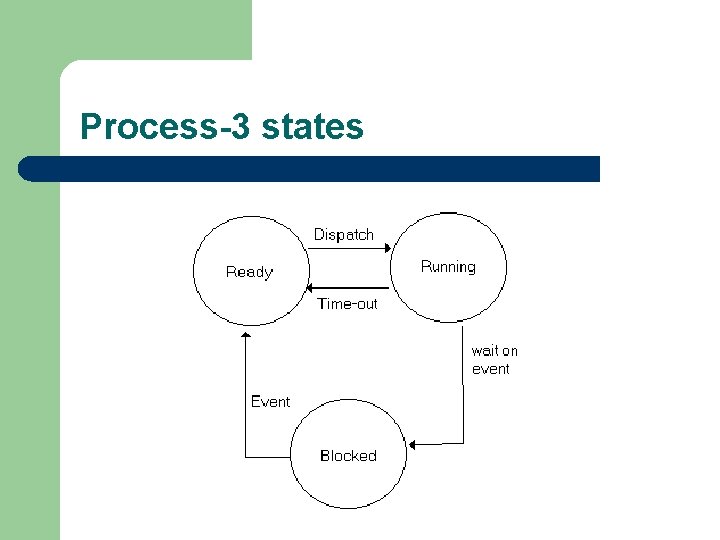

Process-3 states

l When a user process is in the running state, the processor is executing the program code. If a timer interrupt occurs, the running process is moved into ready state, and another process form the list of processes in the ready state is moved into the running state.

l If a process in the running state requests an operating system service and it must wait for it, then the process is moved into the blocked state.

l A process will remain in the blocked state until the event required has taken place, the process can then be moved back into the ready state. If a process is blocked the operating system is free to reschedule another processor.

Virtual Memory 1 l l l If a system does not have enough physical space to store data/program it can create space on the hard disk to acts as memory. Treated as a file on the disk – swap file. Slow memory, but better than nothing. This virtual memory Less physical memory, more virtual memory is used, reducing performance.