Operasi Unit Kontrol Organisasi Komputer II STMIK AUB

Operasi Unit Kontrol Organisasi Komputer II STMIK – AUB Surakarta

Micro-Operations z Fungsi sebuah komputer adalah mengeksekusi program. z Siklus Fetch/execute selalu terjadi z Tiap siklus memiliki sejumlah langkah yang terdiri dari register-register CPU y Ingat pipelining! z Tiap langkah disebut operasi mikro (micro-operation) z Tiap langkah berupa langkah sederhana (Atomic operation of CPU)

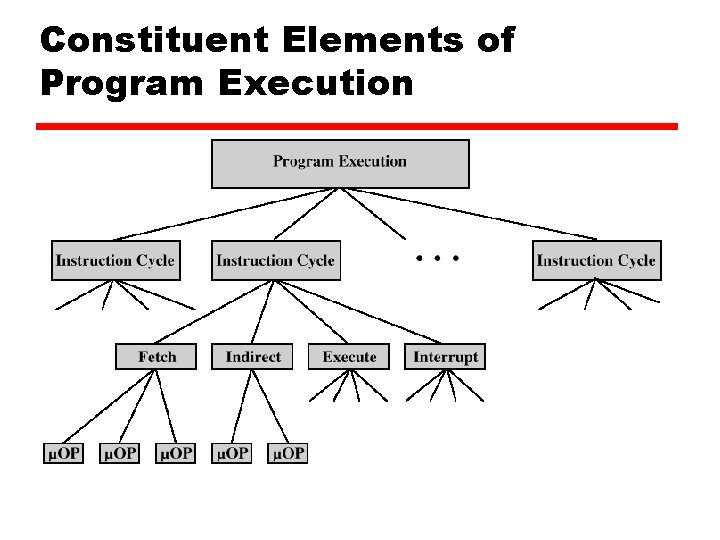

Constituent Elements of Program Execution

Fetch - 4 Registers z Memory Address Register (MAR) y. Connected to address bus y. Specifies address for read or write op z Memory Buffer Register (MBR) y. Connected to data bus y. Berisi data yang akan disimpan atau nilai terakhir yang dibaca z Program Counter (PC) y. Holds address of next instruction to be fetched z Instruction Register (IR) y. Holds last instruction fetched

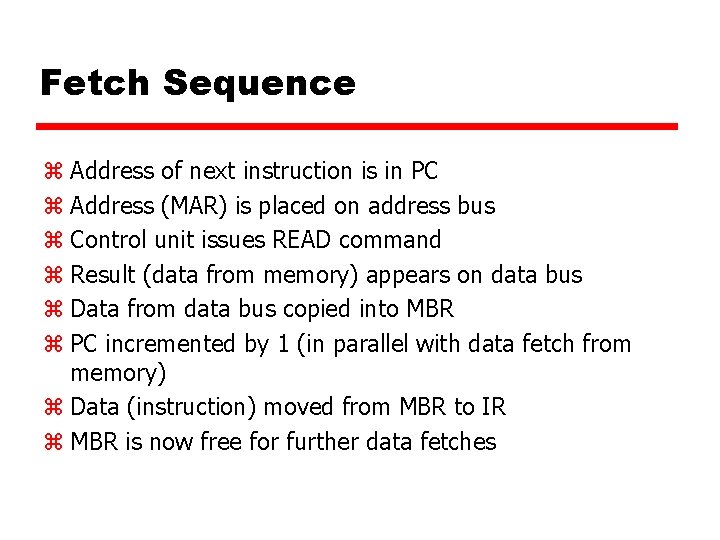

Fetch Sequence z Address of next instruction is in PC z Address (MAR) is placed on address bus z Control unit issues READ command z Result (data from memory) appears on data bus z Data from data bus copied into MBR z PC incremented by 1 (in parallel with data fetch from memory) z Data (instruction) moved from MBR to IR z MBR is now free for further data fetches

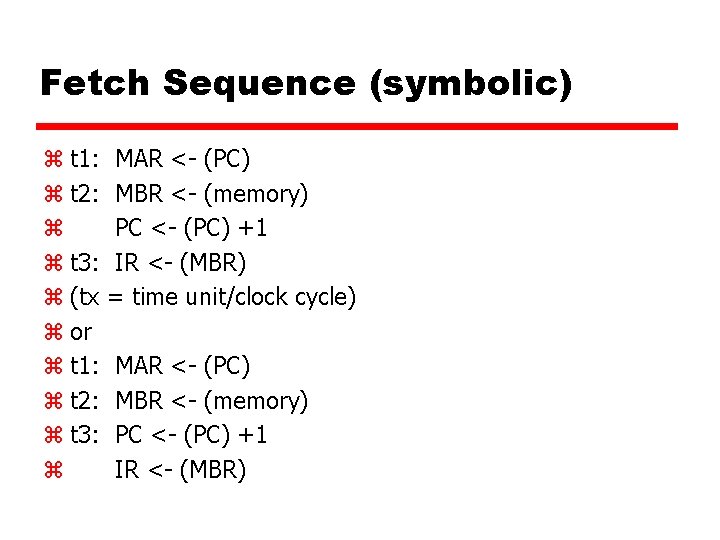

Fetch Sequence (symbolic) z t 1: MAR <- (PC) z t 2: MBR <- (memory) z PC <- (PC) +1 z t 3: IR <- (MBR) z (tx = time unit/clock cycle) z or z t 1: MAR <- (PC) z t 2: MBR <- (memory) z t 3: PC <- (PC) +1 z IR <- (MBR)

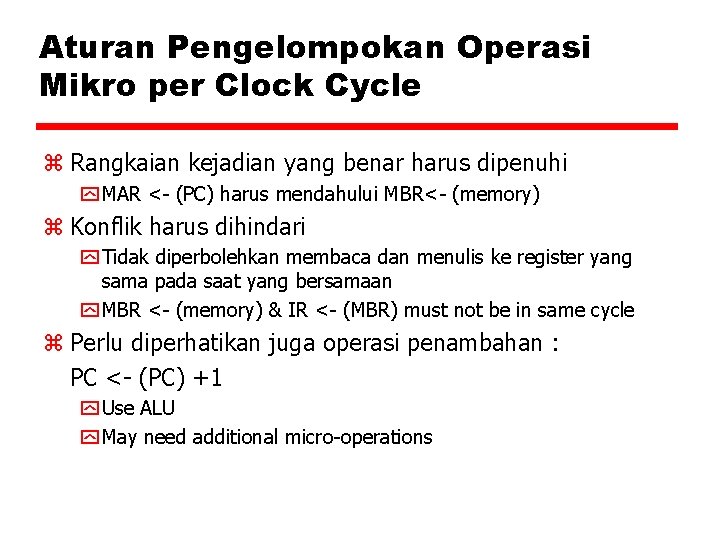

Aturan Pengelompokan Operasi Mikro per Clock Cycle z Rangkaian kejadian yang benar harus dipenuhi y MAR <- (PC) harus mendahului MBR<- (memory) z Konflik harus dihindari y Tidak diperbolehkan membaca dan menulis ke register yang sama pada saat yang bersamaan y MBR <- (memory) & IR <- (MBR) must not be in same cycle z Perlu diperhatikan juga operasi penambahan : PC <- (PC) +1 y Use ALU y May need additional micro-operations

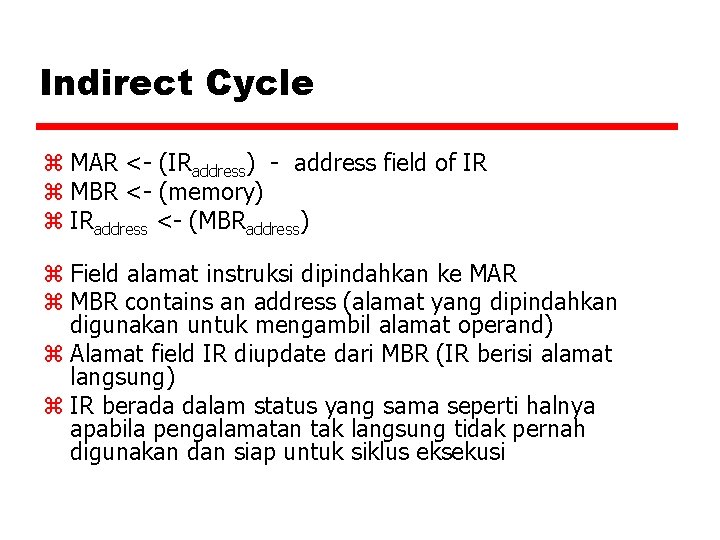

Indirect Cycle z MAR <- (IRaddress) - address field of IR z MBR <- (memory) z IRaddress <- (MBRaddress) z Field alamat instruksi dipindahkan ke MAR z MBR contains an address (alamat yang dipindahkan digunakan untuk mengambil alamat operand) z Alamat field IR diupdate dari MBR (IR berisi alamat langsung) z IR berada dalam status yang sama seperti halnya apabila pengalamatan tak langsung tidak pernah digunakan dan siap untuk siklus eksekusi

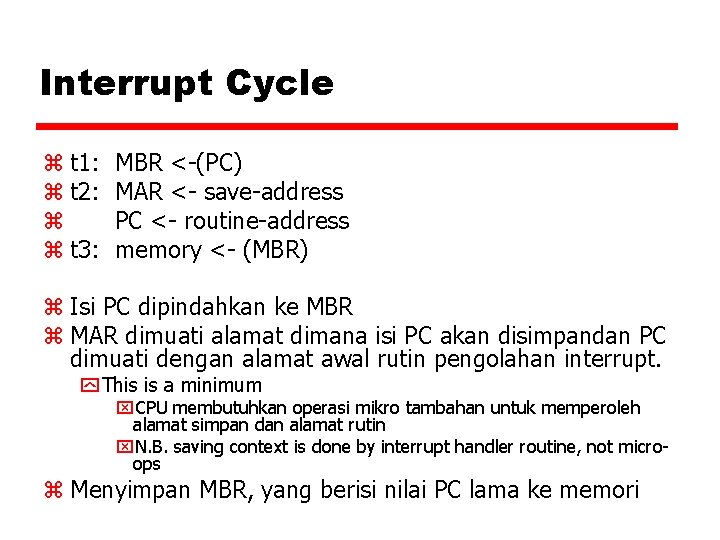

Interrupt Cycle z t 1: z t 2: z z t 3: MBR <-(PC) MAR <- save-address PC <- routine-address memory <- (MBR) z Isi PC dipindahkan ke MBR z MAR dimuati alamat dimana isi PC akan disimpandan PC dimuati dengan alamat awal rutin pengolahan interrupt. y This is a minimum x. CPU membutuhkan operasi mikro tambahan untuk memperoleh alamat simpan dan alamat rutin x. N. B. saving context is done by interrupt handler routine, not microops z Menyimpan MBR, yang berisi nilai PC lama ke memori

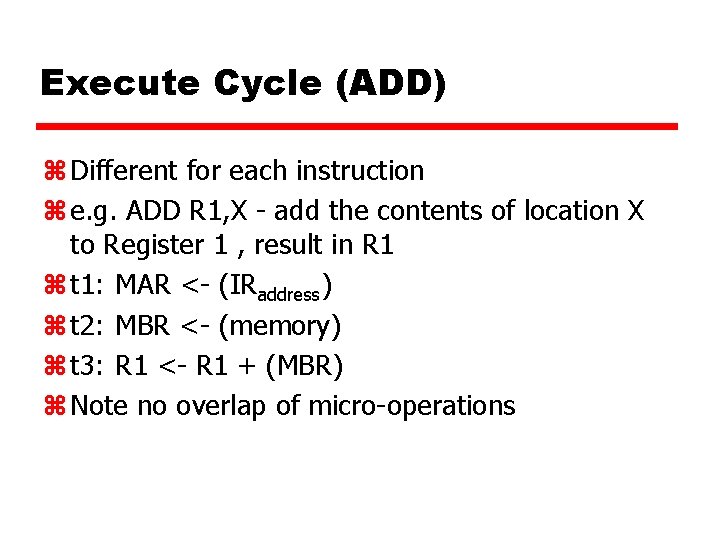

Execute Cycle (ADD) z Different for each instruction z e. g. ADD R 1, X - add the contents of location X to Register 1 , result in R 1 z t 1: MAR <- (IRaddress) z t 2: MBR <- (memory) z t 3: R 1 <- R 1 + (MBR) z Note no overlap of micro-operations

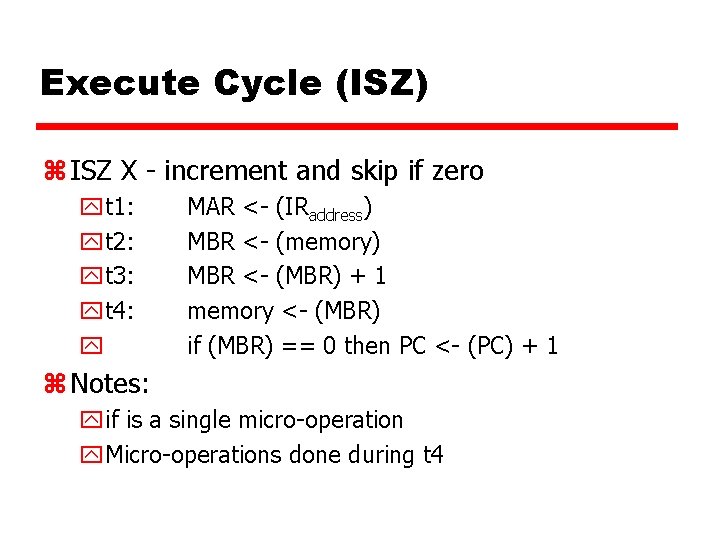

Execute Cycle (ISZ) z ISZ X - increment and skip if zero yt 1: yt 2: yt 3: yt 4: y MAR <- (IRaddress) MBR <- (memory) MBR <- (MBR) + 1 memory <- (MBR) if (MBR) == 0 then PC <- (PC) + 1 z Notes: yif is a single micro-operation y. Micro-operations done during t 4

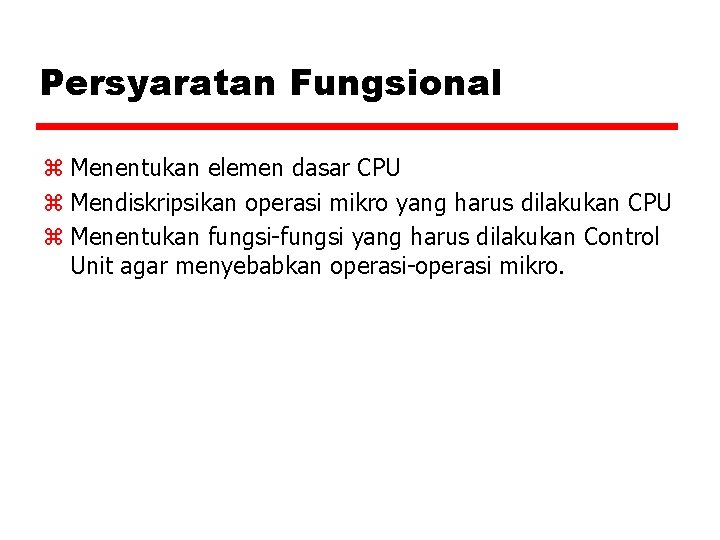

Persyaratan Fungsional z Menentukan elemen dasar CPU z Mendiskripsikan operasi mikro yang harus dilakukan CPU z Menentukan fungsi-fungsi yang harus dilakukan Control Unit agar menyebabkan operasi-operasi mikro.

Elemen Dasar Prosesor z ALU y elemen komputer paling dasar z Register y menyimpan data (informasi status program, memori, register dan modul I/O) z System Interconnection y Internal Data Path xmemindahkan data antar register dan antara register dan ALU y External Data Path xmenghubungkan register ke memori dan modul I/O dan terkadang dengan bus sistem z Control Unit y menyebabkan operasi dalam CPU

FUNGSI CONTROL UNIT z Sequencing (mengurutkan operasi) y Membuat CPU menuju sejumlah operasi mikro dalamurutan operasi tertentu yang benar, yang didasarkan pada program yang sedang dieksekusi z Mengeksekusi y Membuat kinerja setiap operasi mikro selesai dengan menggunakan sinyal kontrol tertentu

Types of Micro-operation z Transfer data between registers z Transfer data from register to external z Transfer data from external to register z Perform arithmetic or logical ops

Control Signals – Input (1) z Clock Cara unit kontrol dalam “menjaga waktu”nya. y. One micro-instruction (or set of parallel microinstructions) per clock cycle y. Disebut clock cycle time atau processor cycle time z Instruction register y. Op-code instruksi saat itu digunakan untuk menentukan operasi mikro mana yang akan dilakukan selama siklus eksekusi

Control Signals – Input (2) z Flags y. Flag diperlukan untuk menentukan status CPU dan hasil sebelumnya yang diperoleh dari operasi-operasi ALU. z From control bus y. Interrupts y. Acknowledgements

Control Signals - output z Within CPU (Sinyal Kontrol dalam CPU) y. Cause data movement (dari satu register ke register lainya) y. Activate specific ALU functions z Via control bus (Sinyal Kontrol bagi Bus Kendali) y. To memory y. To I/O modules

Example Control Signal Sequence - Fetch z MAR <- (PC) y. Control unit activates signal to open gates between PC and MAR z MBR <- (memory) y. Open gates between MAR and address bus y. Memory read control signal y. Open gates between data bus and MBR

Organisasi Internal CPU z Biasanya menggunakan susunan bus single internal z Gates mengontrol perpindahan data dari setiap register dari dan ke bus z Control signals mengontrol perpindahan data dari dan ke bus sistem (eksternal) dan operasi ALU z Temporary registers needed for properation of ALU

Organisasi Internal CPU z Penggunaan lintasan data memudahkan layout interkoneksi dan kontrol CPU z Pemakaian bus internal menghemat ruang (secara fisik)

Hardwired Implementation (1) z Mengontrol input-input unit z Flag dan sinyal-sinyal kontrol bus y. Umumnya, tiap bit memiliki arti tertentu. z Instruction register y. Unit control menggunakan op-code dan tiap op-code akan melakukan aksi yang berbeda (sejumlah kombinasi sinyal-sinyal kontrol) instruksi berlainan y. Input logika unik bagi setiap op-code y. Decoder mengambil input yang didekode dan menghasilkan sebuah output y. Umumnya, dekoder memiliki n input biner and 2 n outputs biner

Hardwired Implementation (2) z Clock y. Mengeluarkan rangkaian pulsa yang berulang-ulang y. Berguna untuk mengukur durasi operasi mikro y. Harus cukup panjang untuk memungkinkan terjadinya perambatan sinyal di sepanjang lintasan data dan merambat ke rangkaian CPU. y. Sinyal kontrol yang berlainan dalam satuan waktu yang berbeda pada sebuah siklus instruksi tunggalnya y. Dibutuhkan penghitung sebagai input bagi unit kontrol dengan input kontrol yang berbeda untuk tiap satuan waktunya.

Problems With Hard Wired Designs z Complex sequencing & micro-operation logic z Difficult to design and test z Inflexible design z Difficult to add new instructions

- Slides: 24