Open ROAD Open RTLtoGDS Update https theopenroadproject org

- Slides: 34

Open. ROAD Open RTL-to-GDS Update https: //theopenroadproject. org https: //github. com/The-Open. ROAD-Project Andrew B. Kahng UC San Diego abk@eng. ucsd. edu https: //vlsicad. ucsd. edu/~abk Mohamed Kassem Efabless. com mkk@efabless. com https: //info. efabless. com/the-team/ Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop

What is Open. ROAD? • 4 -year project (2018 – 2022) • RTL-to-GDS EDA tool • Seed for open-source EDA innovation • Support for open-source HW community • And … Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 2

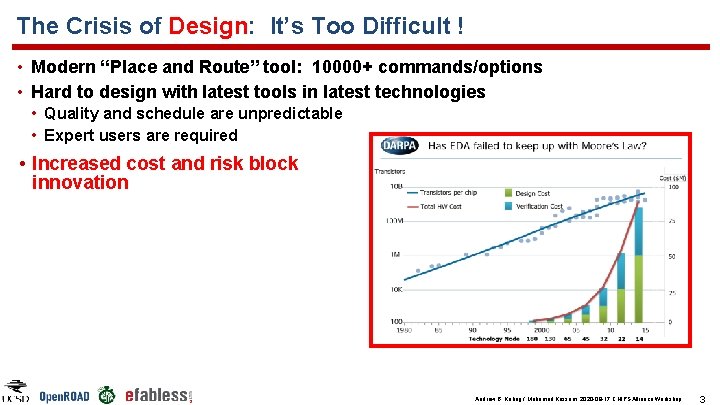

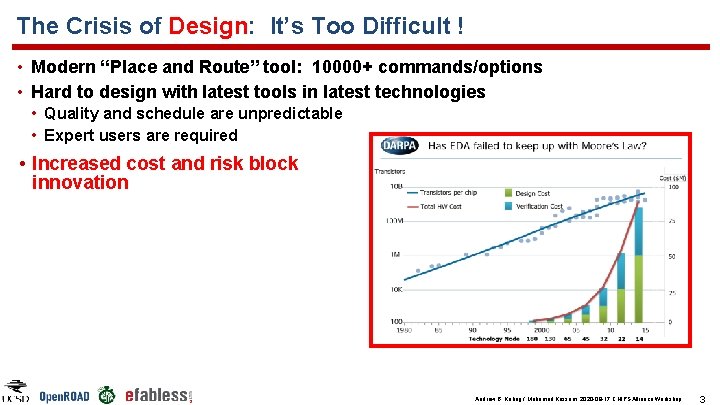

The Crisis of Design: It’s Too Difficult ! • Modern “Place and Route” tool: 10000+ commands/options • Hard to design with latest tools in latest technologies • Quality and schedule are unpredictable • Expert users are required • Increased cost and risk block innovation Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 3

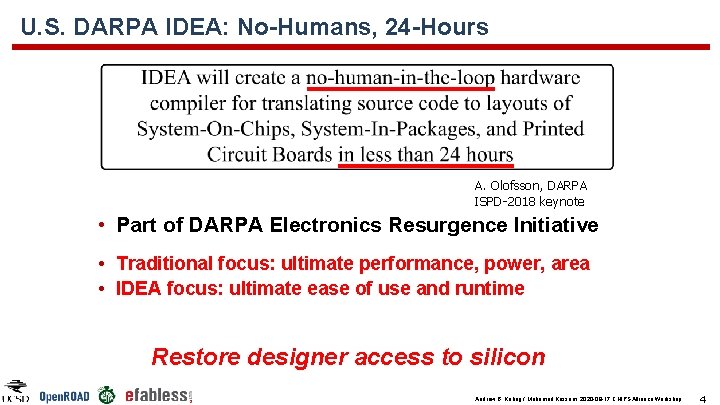

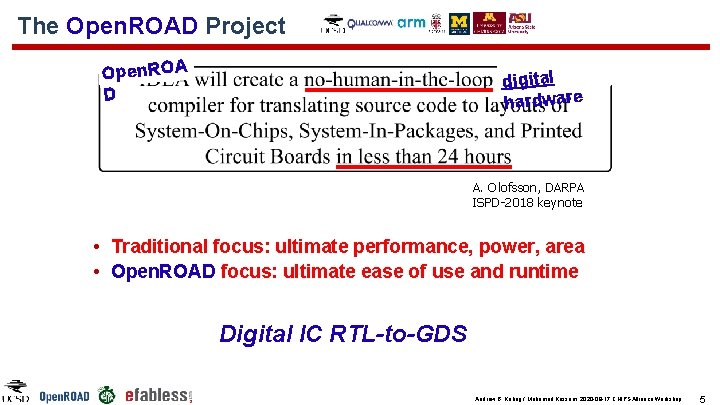

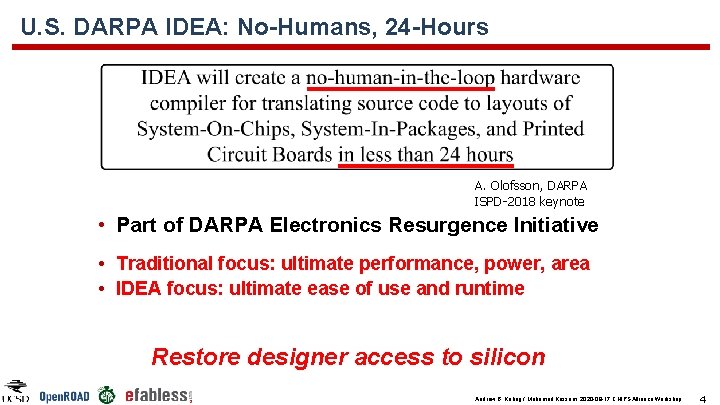

U. S. DARPA IDEA: No-Humans, 24 -Hours A. Olofsson, DARPA ISPD-2018 keynote • Part of DARPA Electronics Resurgence Initiative • Traditional focus: ultimate performance, power, area • IDEA focus: ultimate ease of use and runtime Restore designer access to silicon Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 4

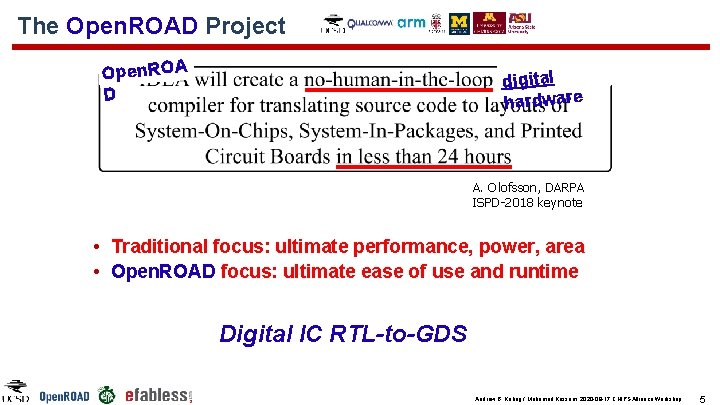

The Open. ROAD Project Open. ROA D digital hardware A. Olofsson, DARPA ISPD-2018 keynote • Traditional focus: ultimate performance, power, area • Open. ROAD focus: ultimate ease of use and runtime Digital IC RTL-to-GDS Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 5

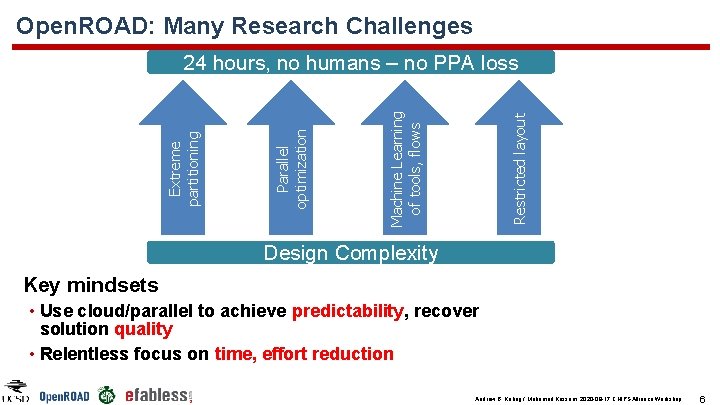

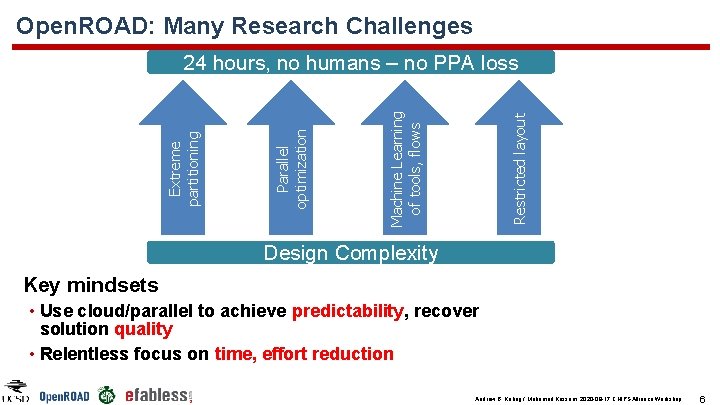

Open. ROAD: Many Research Challenges Restricted layout Machine Learning of tools, flows Parallel optimization Extreme partitioning 24 hours, no humans – no PPA loss Design Complexity Key mindsets • Use cloud/parallel to achieve predictability, recover solution quality • Relentless focus on time, effort reduction Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 6

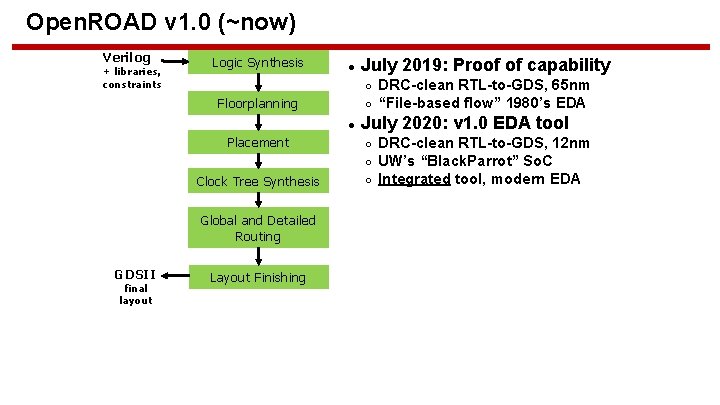

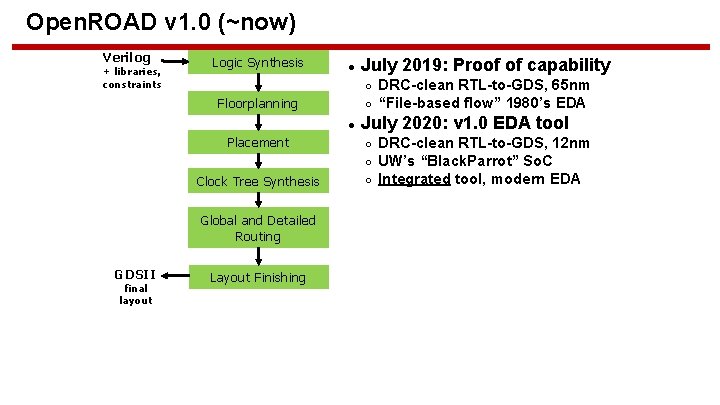

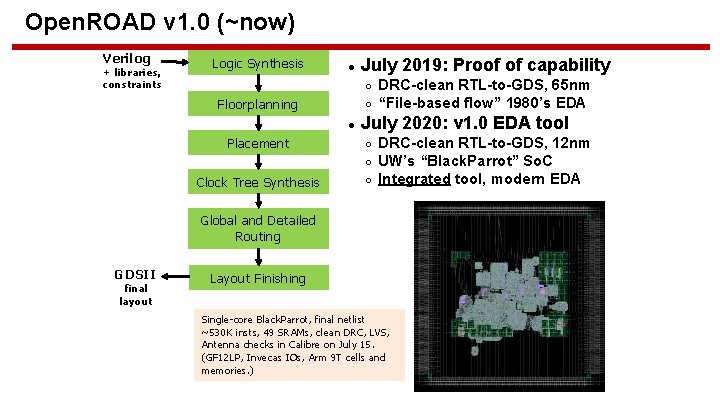

Open. ROAD v 1. 0 (~now) Verilog + libraries, constraints Logic Synthesis ● ○ Floorplanning ○ ● Placement Clock Tree Synthesis Global and Detailed Routing GDSII final layout July 2019: Proof of capability Layout Finishing DRC-clean RTL-to-GDS, 65 nm “File-based flow” 1980’s EDA July 2020: v 1. 0 EDA tool ○ ○ ○ DRC-clean RTL-to-GDS, 12 nm UW’s “Black. Parrot” So. C Integrated tool, modern EDA

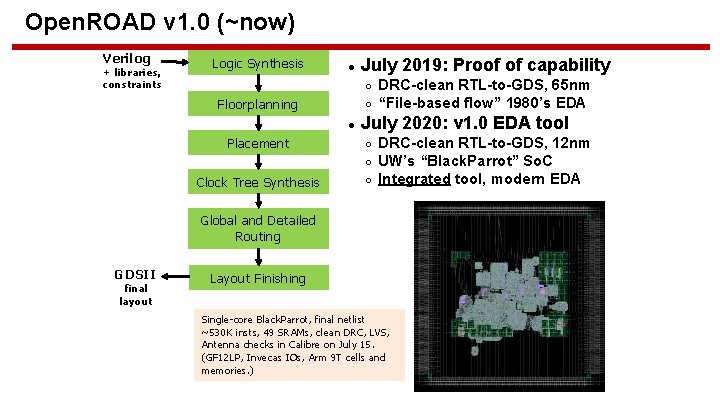

Open. ROAD v 1. 0 (~now) Verilog + libraries, constraints Logic Synthesis ● July 2019: Proof of capability ○ Floorplanning ○ ● Placement Clock Tree Synthesis DRC-clean RTL-to-GDS, 65 nm “File-based flow” 1980’s EDA July 2020: v 1. 0 EDA tool ○ ○ ○ DRC-clean RTL-to-GDS, 12 nm UW’s “Black. Parrot” So. C Integrated tool, modern EDA Global and Detailed Routing GDSII final layout Layout Finishing Single-core Black. Parrot, final netlist ~530 K insts, 49 SRAMs, clean DRC, LVS, Antenna checks in Calibre on July 15. (GF 12 LP, Invecas IOs, Arm 9 T cells and memories. )

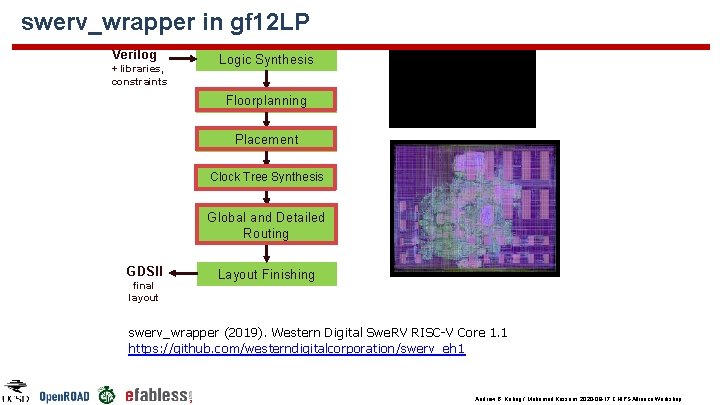

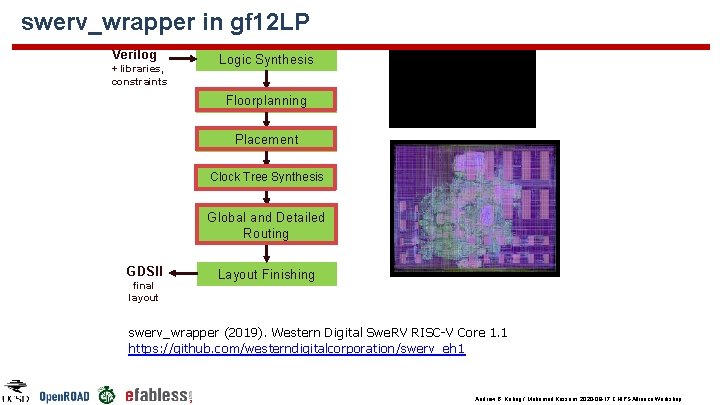

swerv_wrapper in gf 12 LP Verilog + libraries, constraints Logic Synthesis Floorplanning Placement Clock Tree Synthesis Global and Detailed Routing GDSII final layout Layout Finishing swerv_wrapper (2019). Western Digital Swe. RV RISC-V Core 1. 1 https: //github. com/westerndigitalcorporation/swerv_eh 1 Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop

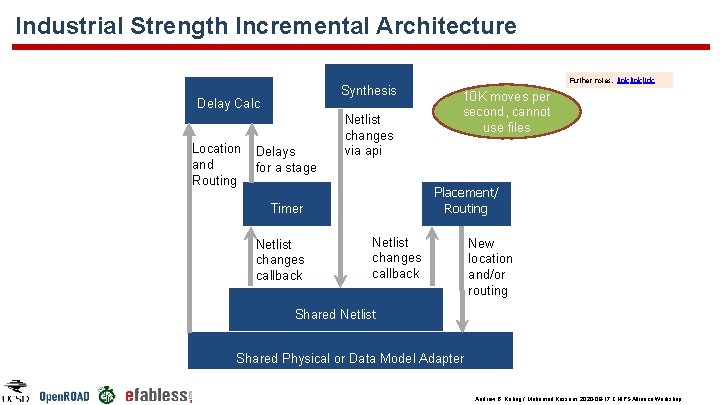

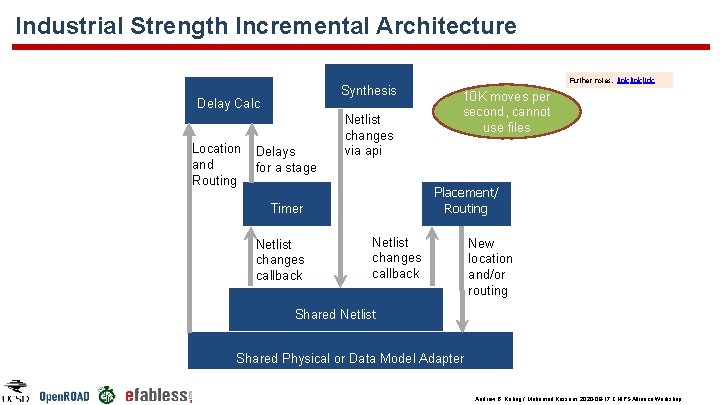

Industrial Strength Incremental Architecture Synthesis Delay Calc Location and Routing Delays for a stage Netlist changes via api 10 K moves per second, cannot use files Placement/ Routing Timer Netlist changes callback Further notes: link Netlist changes callback New location and/or routing Shared Netlist Shared Physical or Data Model Adapter Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop

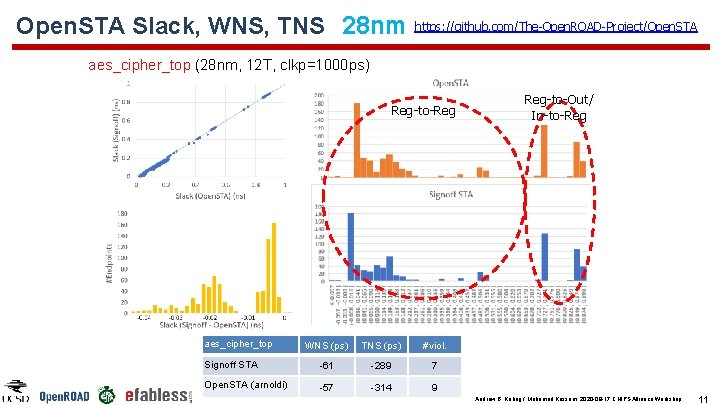

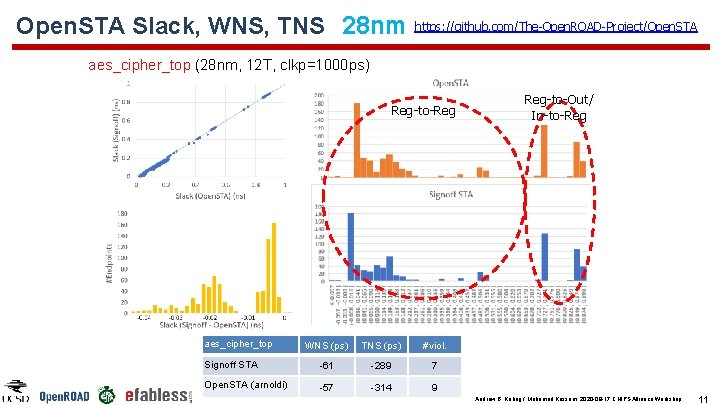

Open. STA Slack, WNS, TNS 28 nm https: //github. com/The-Open. ROAD-Project/Open. STA aes_cipher_top (28 nm, 12 T, clkp=1000 ps) Reg-to-Reg aes_cipher_top WNS (ps) TNS (ps) #viol. Signoff STA -61 -289 7 Open. STA (arnoldi) -57 -314 9 Reg-to-Out/ In-to-Reg Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 11

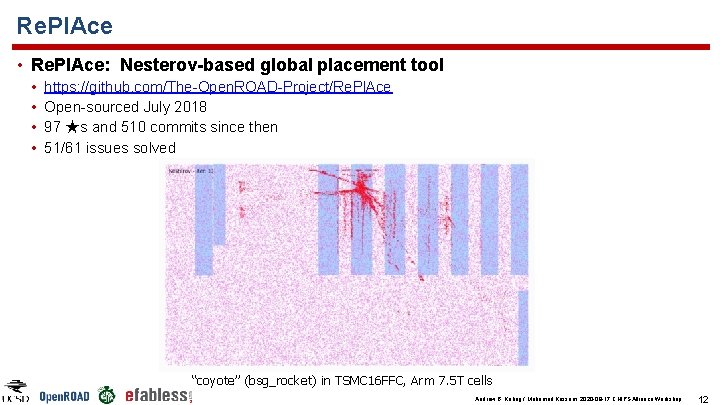

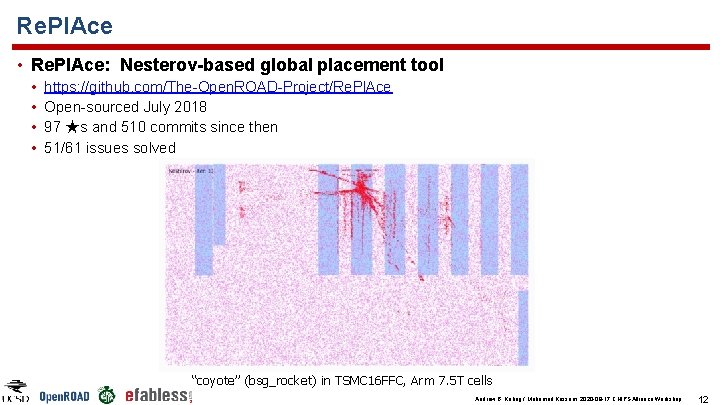

Re. Pl. Ace • Re. Pl. Ace: Nesterov-based global placement tool • • https: //github. com/The-Open. ROAD-Project/Re. Pl. Ace Open-sourced July 2018 97 ★s and 510 commits since then 51/61 issues solved “coyote” (bsg_rocket) in TSMC 16 FFC, Arm 7. 5 T cells Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 12

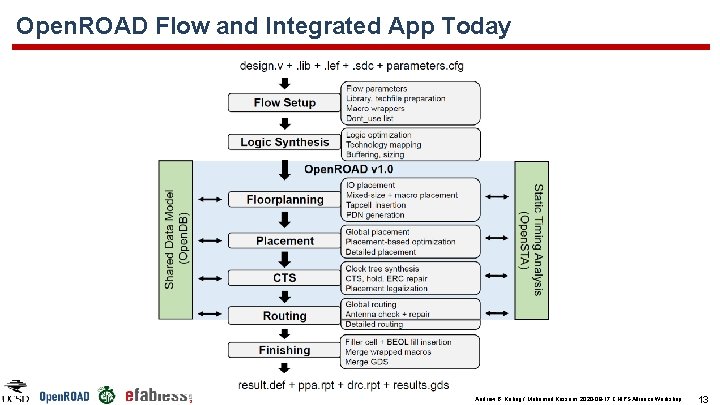

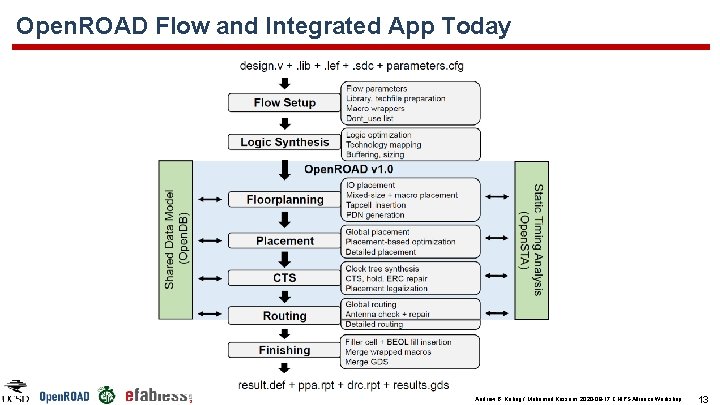

Open. ROAD Flow and Integrated App Today Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 13

theopenroadproject. org Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 14

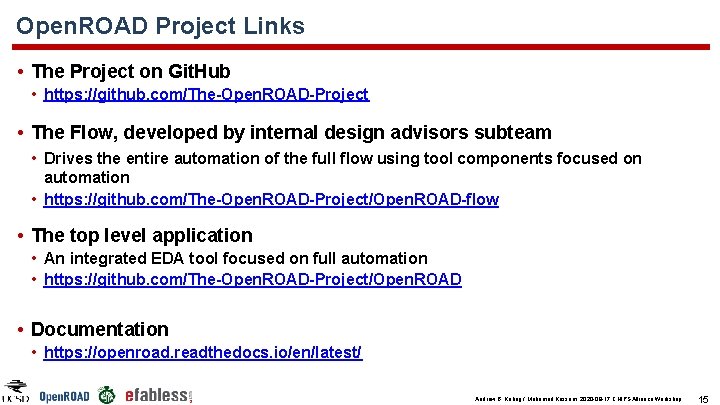

Open. ROAD Project Links • The Project on Git. Hub • https: //github. com/The-Open. ROAD-Project • The Flow, developed by internal design advisors subteam • Drives the entire automation of the full flow using tool components focused on automation • https: //github. com/The-Open. ROAD-Project/Open. ROAD-flow • The top level application • An integrated EDA tool focused on full automation • https: //github. com/The-Open. ROAD-Project/Open. ROAD • Documentation • https: //openroad. readthedocs. io/en/latest/ Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 15

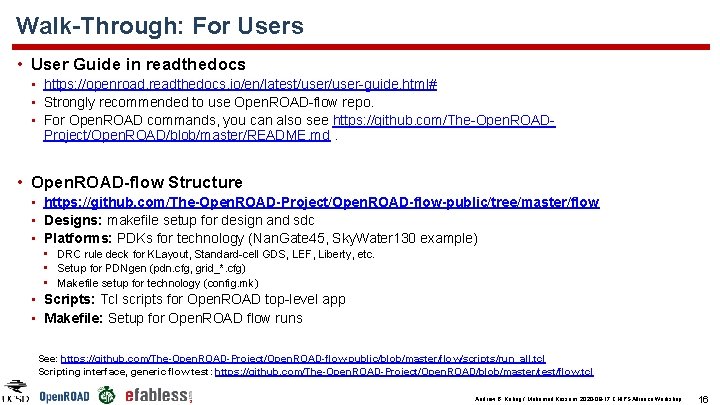

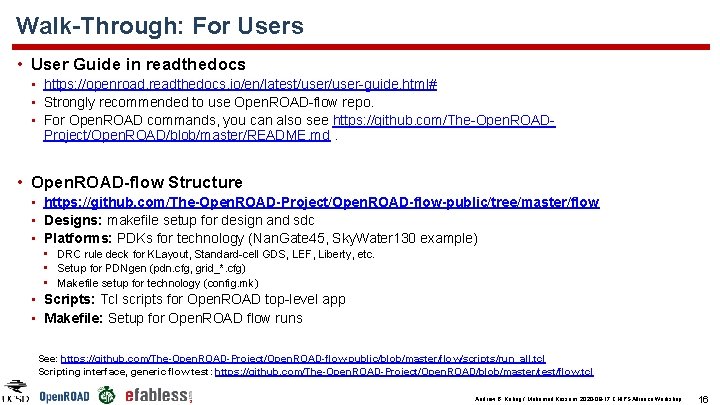

Walk-Through: For Users • User Guide in readthedocs • https: //openroad. readthedocs. io/en/latest/user-guide. html# • Strongly recommended to use Open. ROAD-flow repo. • For Open. ROAD commands, you can also see https: //github. com/The-Open. ROADProject/Open. ROAD/blob/master/README. md. • Open. ROAD-flow Structure • https: //github. com/The-Open. ROAD-Project/Open. ROAD-flow-public/tree/master/flow • Designs: makefile setup for design and sdc • Platforms: PDKs for technology (Nan. Gate 45, Sky. Water 130 example) • DRC rule deck for KLayout, Standard-cell GDS, LEF, Liberty, etc. • Setup for PDNgen (pdn. cfg, grid_*. cfg) • Makefile setup for technology (config. mk) • Scripts: Tcl scripts for Open. ROAD top-level app • Makefile: Setup for Open. ROAD flow runs See: https: //github. com/The-Open. ROAD-Project/Open. ROAD-flow-public/blob/master/flow/scripts/run_all. tcl Scripting interface, generic flow test: https: //github. com/The-Open. ROAD-Project/Open. ROAD/blob/master/test/flow. tcl Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 16

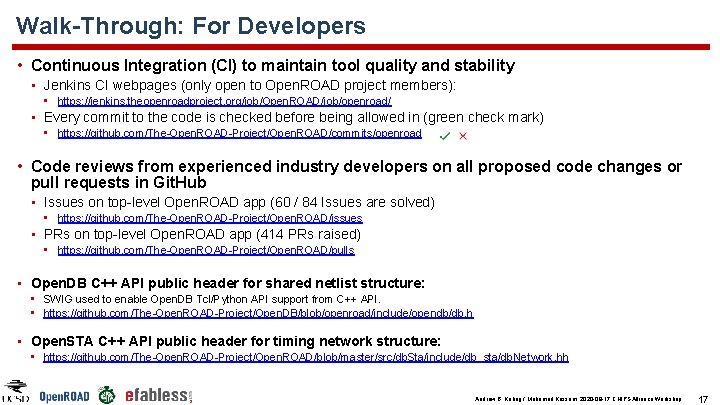

Walk-Through: For Developers • Continuous Integration (CI) to maintain tool quality and stability • Jenkins CI webpages (only open to Open. ROAD project members): • https: //jenkins. theopenroadproject. org/job/Open. ROAD/job/openroad/ • Every commit to the code is checked before being allowed in (green check mark) • https: //github. com/The-Open. ROAD-Project/Open. ROAD/commits/openroad • Code reviews from experienced industry developers on all proposed code changes or pull requests in Git. Hub • Issues on top-level Open. ROAD app (60 / 84 Issues are solved) • https: //github. com/The-Open. ROAD-Project/Open. ROAD/issues • PRs on top-level Open. ROAD app (414 PRs raised) • https: //github. com/The-Open. ROAD-Project/Open. ROAD/pulls • Open. DB C++ API public header for shared netlist structure: • SWIG used to enable Open. DB Tcl/Python API support from C++ API. • https: //github. com/The-Open. ROAD-Project/Open. DB/blob/openroad/include/opendb/db. h • Open. STA C++ API public header for timing network structure: • https: //github. com/The-Open. ROAD-Project/Open. ROAD/blob/master/src/db. Sta/include/db_sta/db. Network. hh Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 17

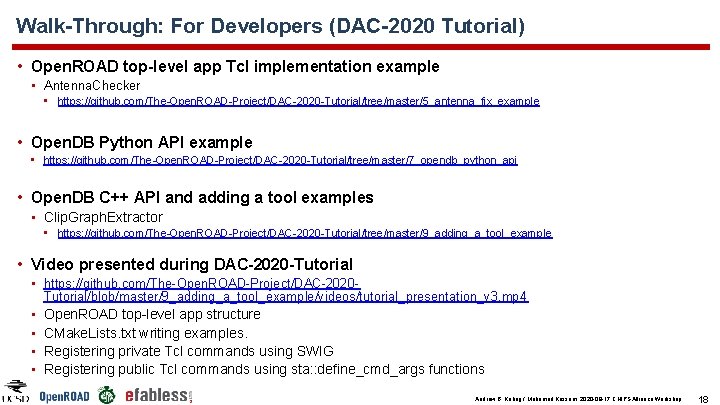

Walk-Through: For Developers (DAC-2020 Tutorial) • Open. ROAD top-level app Tcl implementation example • Antenna. Checker • https: //github. com/The-Open. ROAD-Project/DAC-2020 -Tutorial/tree/master/5_antenna_fix_example • Open. DB Python API example • https: //github. com/The-Open. ROAD-Project/DAC-2020 -Tutorial/tree/master/7_opendb_python_api • Open. DB C++ API and adding a tool examples • Clip. Graph. Extractor • https: //github. com/The-Open. ROAD-Project/DAC-2020 -Tutorial/tree/master/9_adding_a_tool_example • Video presented during DAC-2020 -Tutorial • https: //github. com/The-Open. ROAD-Project/DAC-2020 Tutorial/blob/master/9_adding_a_tool_example/videos/tutorial_presentation_v 3. mp 4 • Open. ROAD top-level app structure • CMake. Lists. txt writing examples. • Registering private Tcl commands using SWIG • Registering public Tcl commands using sta: : define_cmd_args functions Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 18

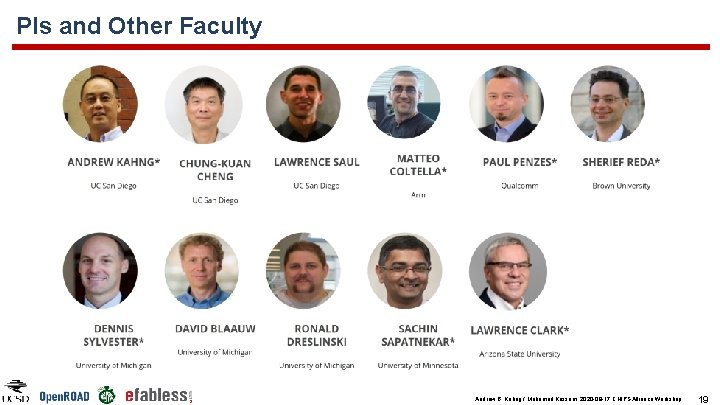

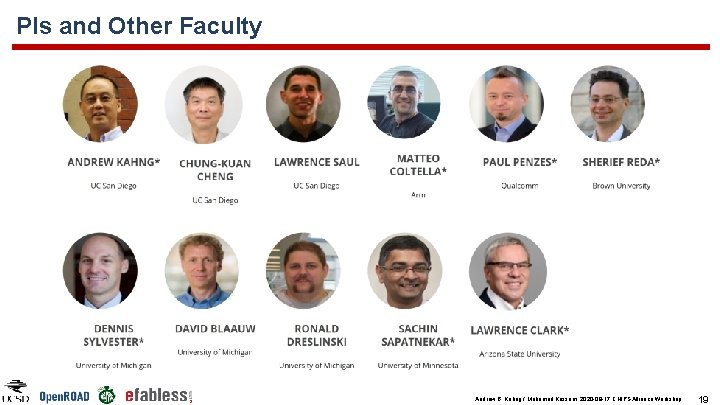

PIs and Other Faculty Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 19

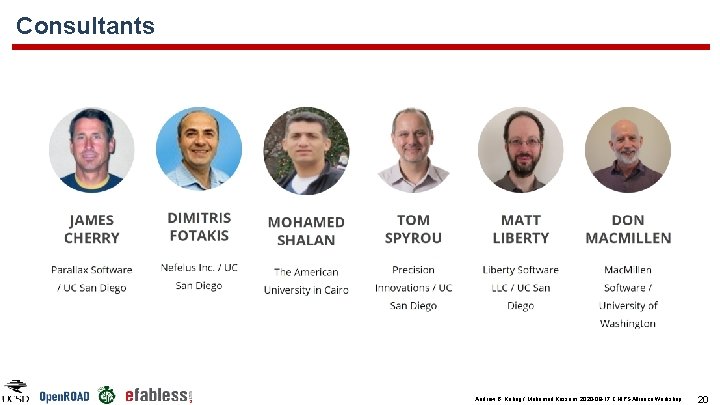

Consultants Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 20

Team Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 21

What is Open. ROAD? • 4 -year project (2018 – 2022) • RTL-to-GDS EDA tool • Seed for open-source EDA innovation • Support for open-source HW community • And … Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 22

NEXT UP: First So. C Design on SKY 130 Mohamed Kassem CTO Open. ROAD: Many thanks to the team https: //theopenroadproject. org/our-team/ and to Tim Ansell (Google) Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 23

The OS PDK - GEN 1 - SKY 130 from Sky. Water Foundry June 30, 2020 Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 24

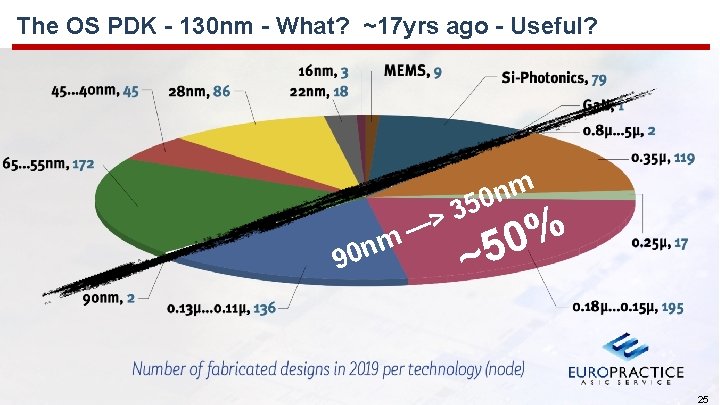

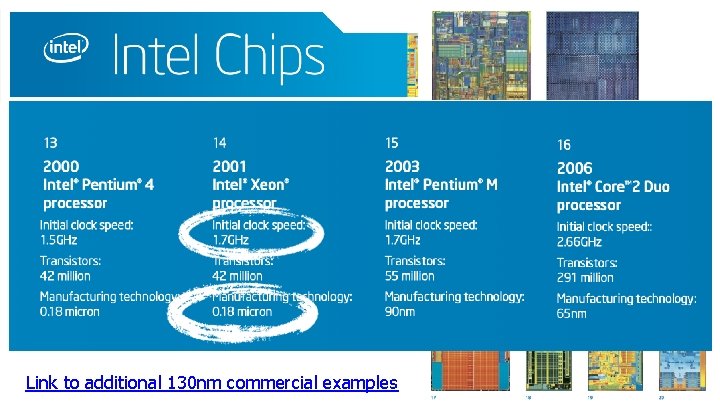

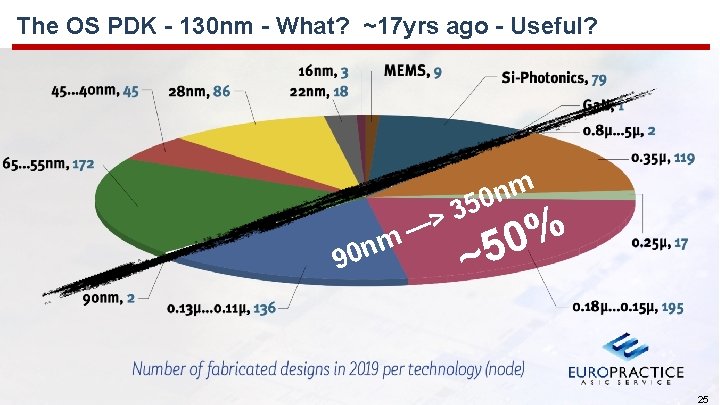

The OS PDK - 130 nm - What? ~17 yrs ago - Useful? 90 n > — m m n 0 35 % 0 ~5 Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 25

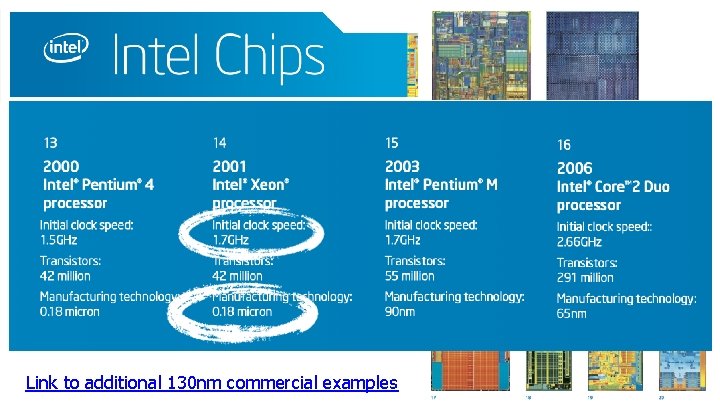

Link to additional 130 nm commercial examples © 2020 EFABLESS CORPORATION

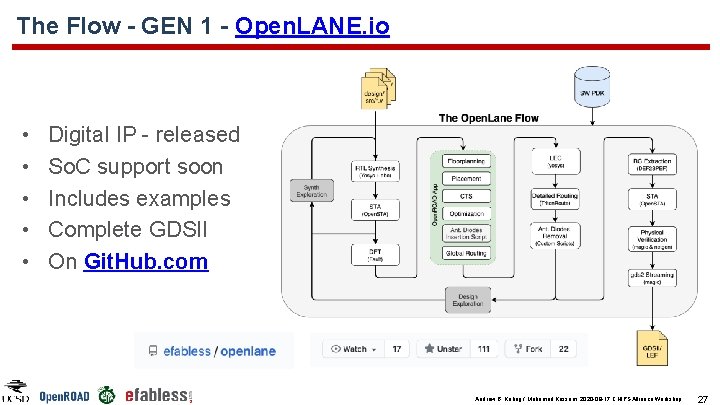

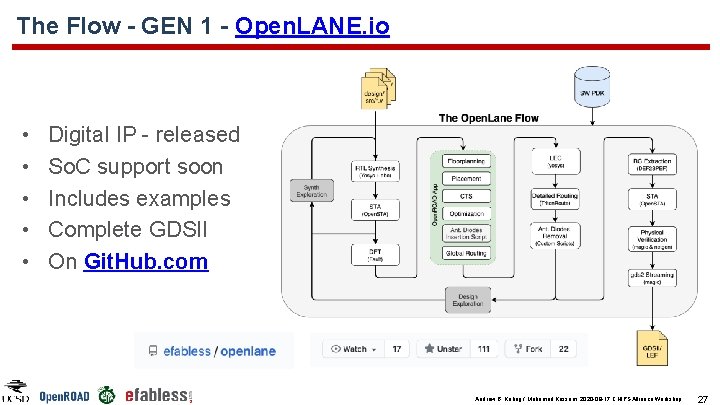

The PDK The Flow - GEN 1 - Open. LANE. io • • • Digital IP - released So. C support soon Includes examples Complete GDSII On Git. Hub. com Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 27

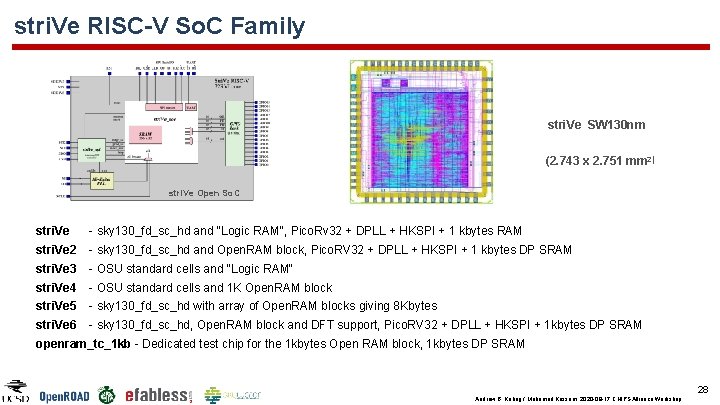

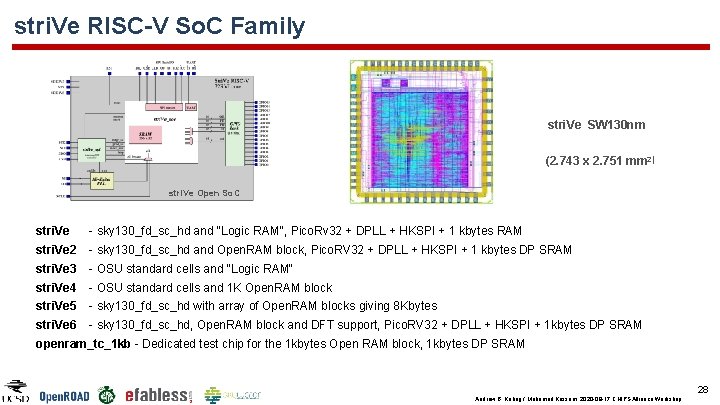

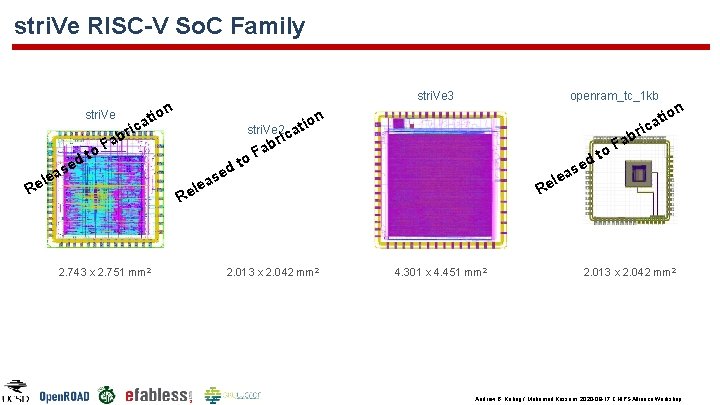

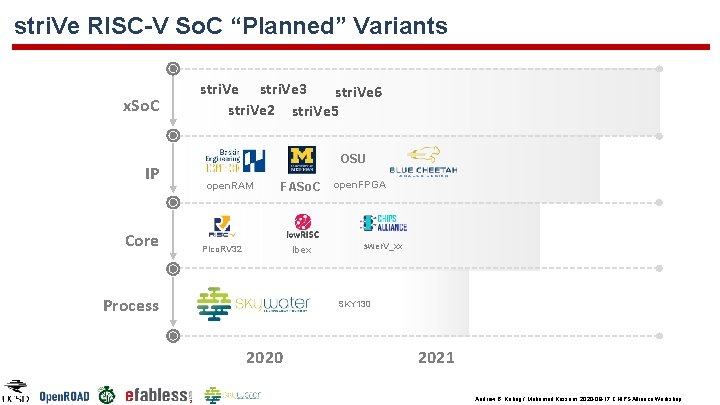

stri. Ve RISC-V So. C Family stri. Ve SW 130 nm (2. 743 x 2. 751 mm 2) stri. Ve Open So. C stri. Ve - sky 130_fd_sc_hd and "Logic RAM", Pico. Rv 32 + DPLL + HKSPI + 1 kbytes RAM stri. Ve 2 - sky 130_fd_sc_hd and Open. RAM block, Pico. RV 32 + DPLL + HKSPI + 1 kbytes DP SRAM stri. Ve 3 - OSU standard cells and "Logic RAM" stri. Ve 4 - OSU standard cells and 1 K Open. RAM block stri. Ve 5 - sky 130_fd_sc_hd with array of Open. RAM blocks giving 8 Kbytes stri. Ve 6 - sky 130_fd_sc_hd, Open. RAM block and DFT support, Pico. RV 32 + DPLL + HKSPI + 1 kbytes DP SRAM openram_tc_1 kb - Dedicated test chip for the 1 kbytes Open RAM block, 1 kbytes DP SRAM 28 Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop

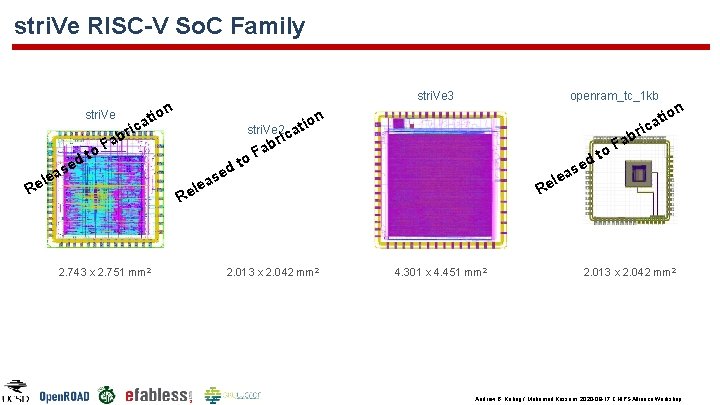

stri. Ve RISC-V So. C Family on ati c i br stri. Ve d se stri. Ve 3 a o. F t lea e R 2. 743 x 2. 751 mm 2 ed s lea openram_tc_1 kb on stri. Ve 2 ati ric b Fa to br a le Re Re 2. 013 x 2. 042 mm 2 on ti ica 4. 301 x 4. 451 mm 2 d se a o. F t 2. 013 x 2. 042 mm 2 Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop

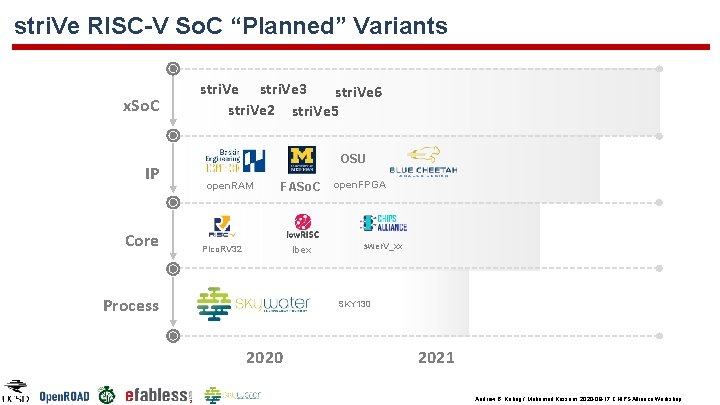

stri. Ve RISC-V So. C “Planned” Variants x. So. C IP Core stri. Ve 3 stri. Ve 6 stri. Ve 2 stri. Ve 5 OSU open. RAM FASo. C Pico. RV 32 Ibex Process open. FPGA swer. V_xx SKY 130 2021 Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop

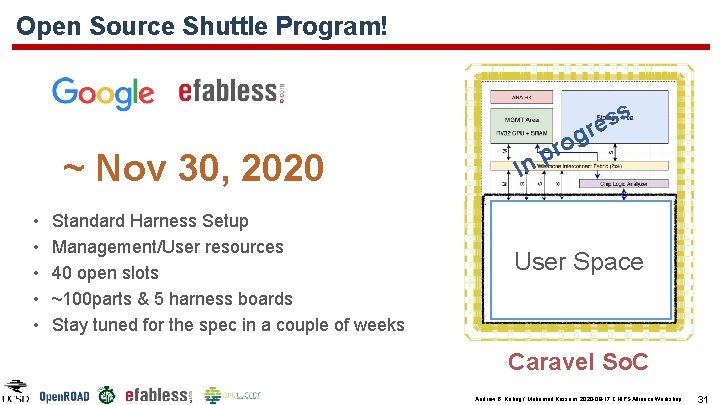

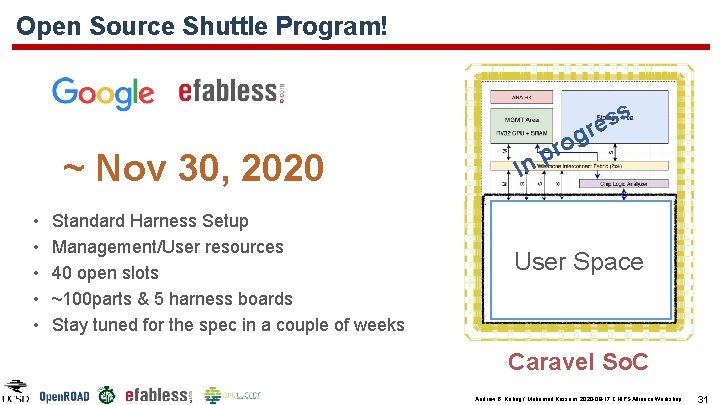

Open Source Shuttle Program! s ~ Nov 30, 2020 • • • Standard Harness Setup Management/User resources 40 open slots ~100 parts & 5 harness boards Stay tuned for the spec in a couple of weeks s e r g ro p n I User Space Caravel So. C Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 31

Join the skywater-pdk project - The Sky. Water PDK Slack Space - https: //join. skywater. tools - The Open. Lane flow for digital Pn. R can be found at https: //openlane. io - The documentation is at https: //docs. skywater. tools Open Source Manufacturable 130 nm PDK https: //github. com/google/skywater-pdk Full Open Source RTL 2 GDS Compiler https: //github. com/efabless/openlane Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 32

More Information – FOSSi Dialup 1) Tim Ansell - Google Kick-off Presentation of Open Source Foundry Fully open source manufacturable PDK for a 130 nm process Video: https: //youtu. be/Ecz. W 2 IWdn. OM Slides: https: //ef. link/5 s. B 6 b (GDOC) 2) Mohamed Shalan - efabless’ Presentation Open. Lane, A Digital ASIC Flow for Sky. Water 130 nm Open PDK Video: https: //youtu. be/Vhyv 0 eq_m. LU Slides: https: //ef. link/cyg. ME (PDF) 3) Mohamed Kassem - efabless’ Presentation The stri. Ve RISC-V So. C Family on Sky. Water 130 nm Apache 2. 0 -Licensed Software to Silicon Video: https: //youtu. be/Hv. Wve. K 2 f. Zt 0 Slides: https: //ef. link/fossi-pdf (PDF) 4) James Stine – OSU Presentation Designing new 130 nm cells for Sky. Water 130 nm Video: https: //youtu. be/Svus 4 u. Q_CAA https: //fossi-foundation. org/dial-up/ Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 33

THANK YOU ! Andrew B. Kahng / Mohamed Kassem, 2020 -09 -17 CHIPS Alliance Workshop 34