One Hot State Machine vs BinaryGray Code State

One Hot State Machine vs Binary/Gray Code State Machine Danny Mok Altera HK FAE (dmok@altera. com) Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 1

One Hot State Machine n What is One Hot – each state within the State Machine is represent by ONE BIT • e. g. Four State Machine : state 0, state 1, state 2, state 3 can be represented by – 4 bits : 1000 0100 0010 0001 (One Hot) n One Hot State Machine – mainly gives us performance – but it consume more logic Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 2

Binary State Machine n What is Binary State Machine – each state within the State Machine is encode by bits • e. g. Four State Machine : state 0, state 1, state 2, state 3 can be represented by – 2 bits : 00 01 10 11 (Binary) n Binary State Machine – mainly consume less logic – but the performance usually is slower – can be more than one bit change from state to state • (01 -> 10) both bits changed Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 3

Gray Code State Machine n What is Grey Code State Machine – each state within the State Machine is encode by bits • e. g. Four State Machine : state 0, state 1, state 2, state 3 can be represented by – 2 bits : 00 01 11 10 (Grey Code) n Gray Code State Machine – mainly consume less logic – but the performance usually is slower – ONLY one bit change from state to state • (01 -> 11) one bit changed Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 4

Default in Max+Plus II n In Max+Plus II, the State Machine will be coding as – AHDL/VHDL Input • One Hot for FLEX (no option to turn on or off) – because FLEX having a lot of LC(DFF) – so LC is not a problem – most likely is performance problem • Binary Encoding for MAX (option to change to One Hot) – because MAX having limited MC (DFF) – so MC is a problem – most likely the performance is not a problem Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 5

AHDL Design Entry Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 6

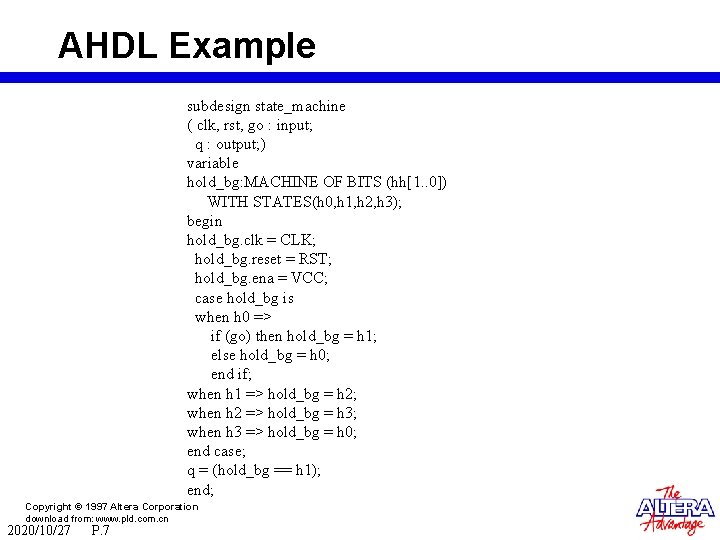

AHDL Example subdesign state_machine ( clk, rst, go : input; q : output; ) variable hold_bg: MACHINE OF BITS (hh[1. . 0]) WITH STATES(h 0, h 1, h 2, h 3); begin hold_bg. clk = CLK; hold_bg. reset = RST; hold_bg. ena = VCC; case hold_bg is when h 0 => if (go) then hold_bg = h 1; else hold_bg = h 0; end if; when h 1 => hold_bg = h 2; when h 2 => hold_bg = h 3; when h 3 => hold_bg = h 0; end case; q = (hold_bg == h 1); end; Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 7

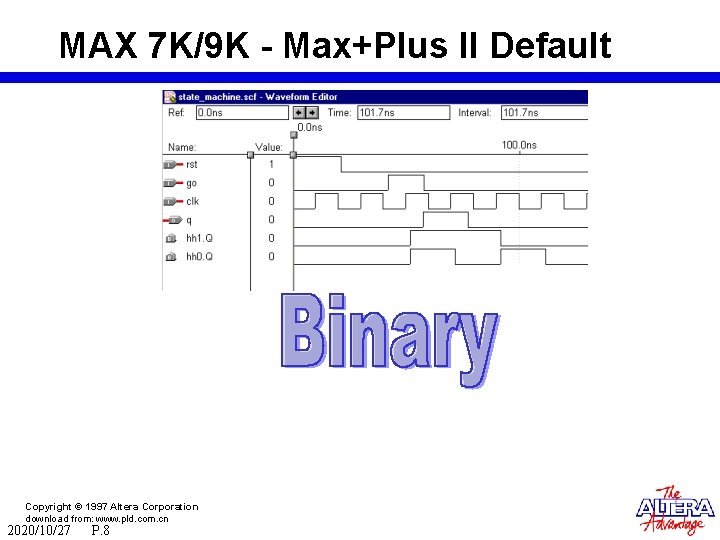

MAX 7 K/9 K - Max+Plus II Default Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 8

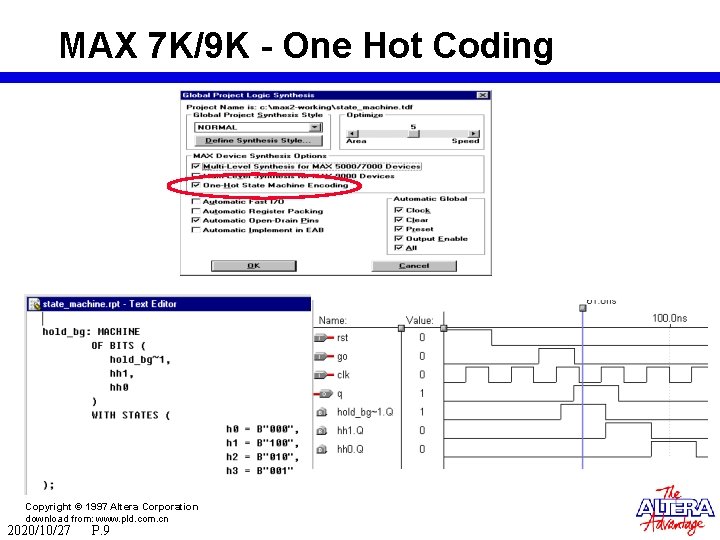

MAX 7 K/9 K - One Hot Coding Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 9

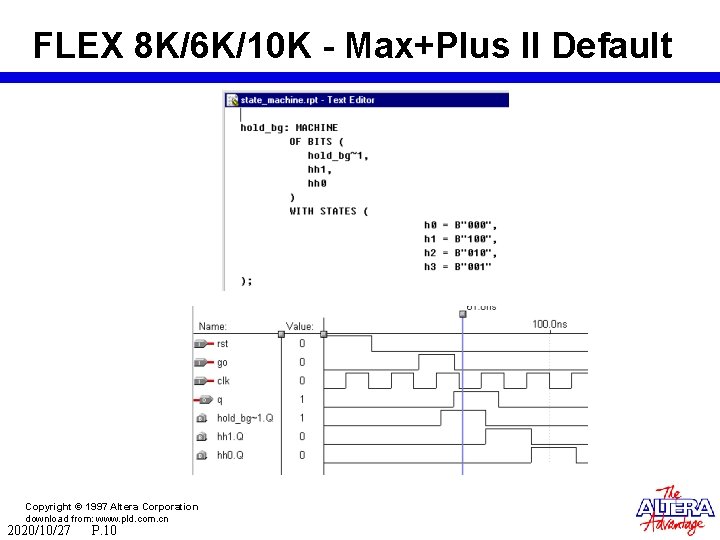

FLEX 8 K/6 K/10 K - Max+Plus II Default Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 10

VHDL Design Entry Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 11

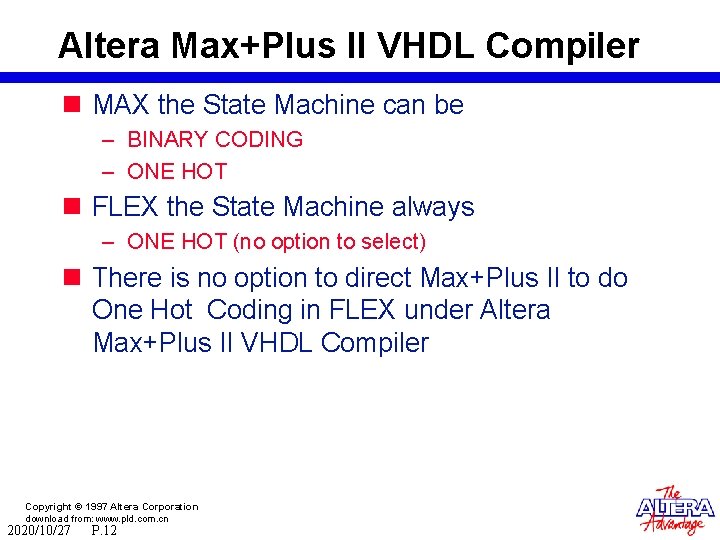

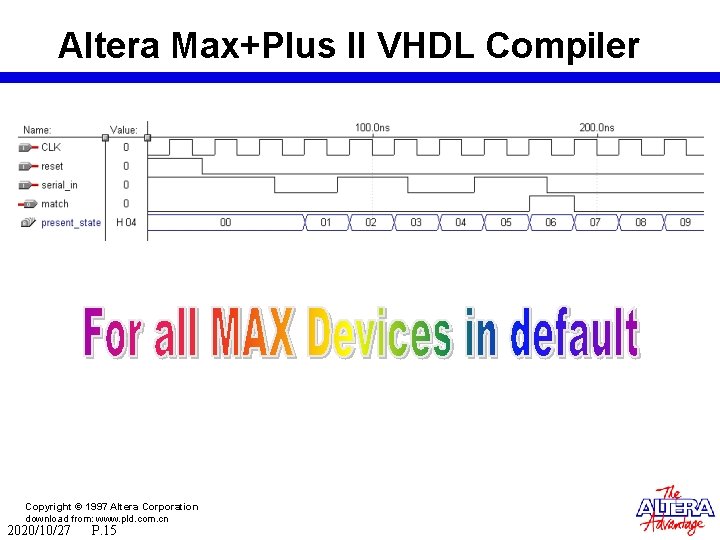

Altera Max+Plus II VHDL Compiler n MAX the State Machine can be – BINARY CODING – ONE HOT n FLEX the State Machine always – ONE HOT (no option to select) n There is no option to direct Max+Plus II to do One Hot Coding in FLEX under Altera Max+Plus II VHDL Compiler Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 12

Solution n Work around solution – use 3 rd compiler to generate EDIF • Binary, Gray Code, One Hot or Random – import the EDIF to Max+Plus II – now Max+Plus II doesn’t know it is State Machine, then it will do what EDIF is Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 13

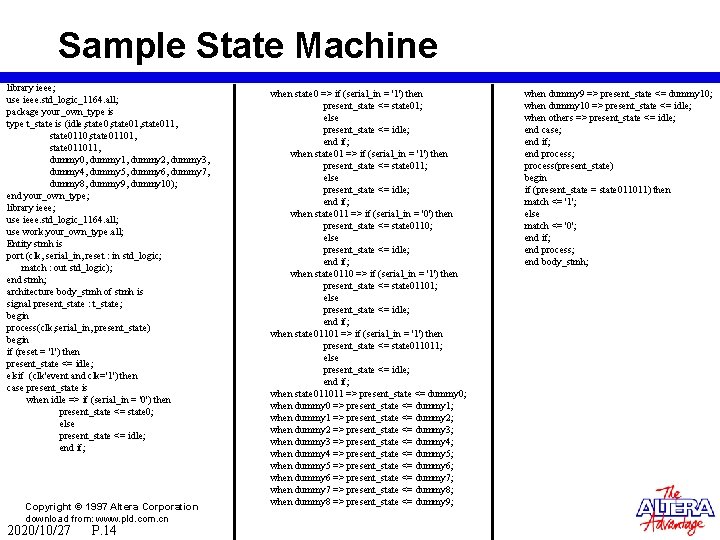

Sample State Machine library ieee; use ieee. std_logic_1164. all; package your_own_type is type t_state is (idle, state 01, state 0110, state 011011, dummy 0, dummy 1, dummy 2, dummy 3, dummy 4, dummy 5, dummy 6, dummy 7, dummy 8, dummy 9, dummy 10); end your_own_type; library ieee; use ieee. std_logic_1164. all; use work. your_own_type. all; Entity stmh is port (clk, serial_in, reset : in std_logic; match : out std_logic); end stmh; architecture body_stmh of stmh is signal present_state : t_state; begin process(clk, serial_in, present_state) begin if (reset = '1') then present_state <= idle; elsif (clk'event and clk='1') then case present_state is when idle => if (serial_in = '0') then present_state <= state 0; else present_state <= idle; end if; Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 14 when state 0 => if (serial_in = '1') then present_state <= state 01; else present_state <= idle; end if; when state 01 => if (serial_in = '1') then present_state <= state 011; else present_state <= idle; end if; when state 011 => if (serial_in = '0') then present_state <= state 0110; else present_state <= idle; end if; when state 0110 => if (serial_in = '1') then present_state <= state 01101; else present_state <= idle; end if; when state 01101 => if (serial_in = '1') then present_state <= state 011011; else present_state <= idle; end if; when state 011011 => present_state <= dummy 0; when dummy 0 => present_state <= dummy 1; when dummy 1 => present_state <= dummy 2; when dummy 2 => present_state <= dummy 3; when dummy 3 => present_state <= dummy 4; when dummy 4 => present_state <= dummy 5; when dummy 5 => present_state <= dummy 6; when dummy 6 => present_state <= dummy 7; when dummy 7 => present_state <= dummy 8; when dummy 8 => present_state <= dummy 9; when dummy 9 => present_state <= dummy 10; when dummy 10 => present_state <= idle; when others => present_state <= idle; end case; end if; end process; process(present_state) begin if (present_state = state 011011) then match <= '1'; else match <= '0'; end if; end process; end body_stmh;

Altera Max+Plus II VHDL Compiler Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 15

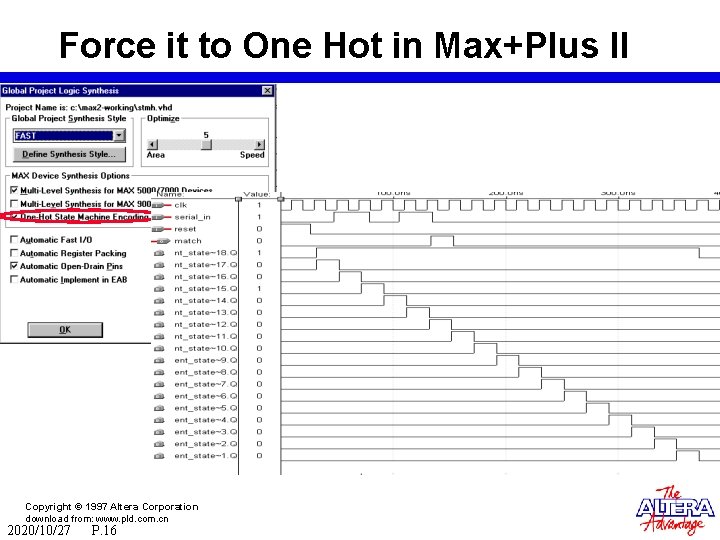

Force it to One Hot in Max+Plus II Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 16

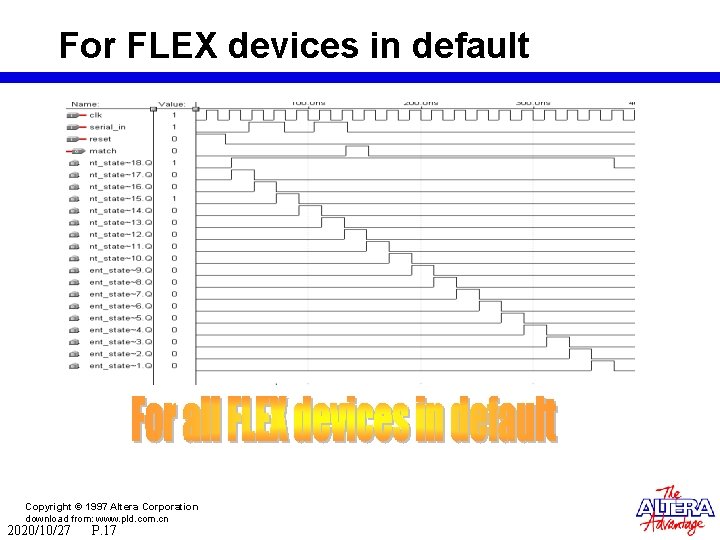

For FLEX devices in default Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 17

Work Around with 3 rd VHDL Compiler Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 18

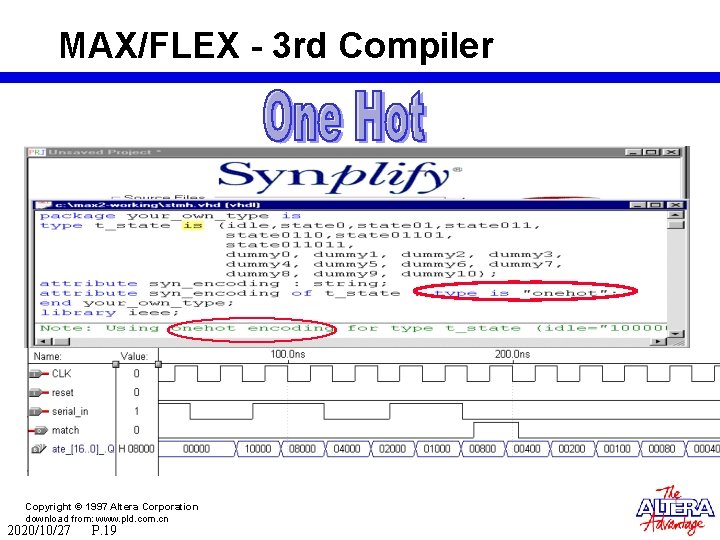

MAX/FLEX - 3 rd Compiler Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 19

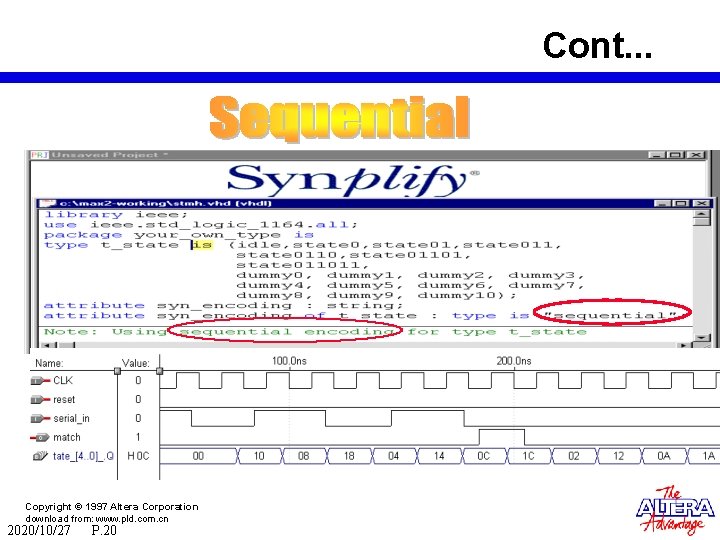

Cont. . . Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 20

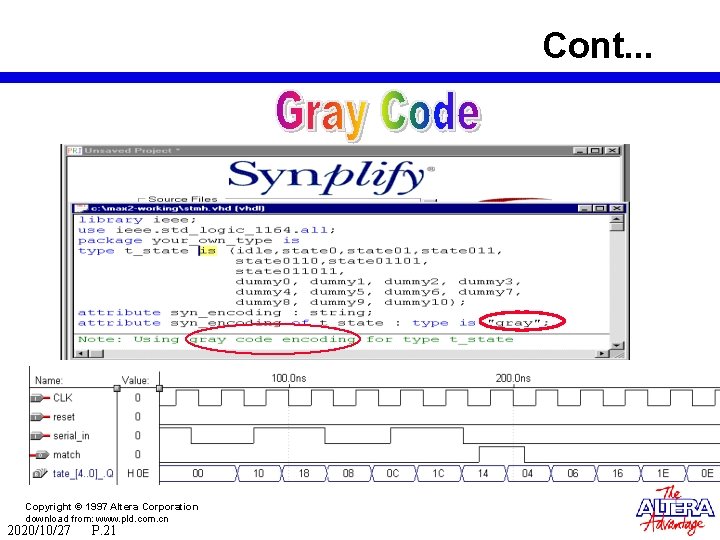

Cont. . . Copyright © 1997 Altera Corporation download from: www. pld. com. cn 2020/10/27 P. 21

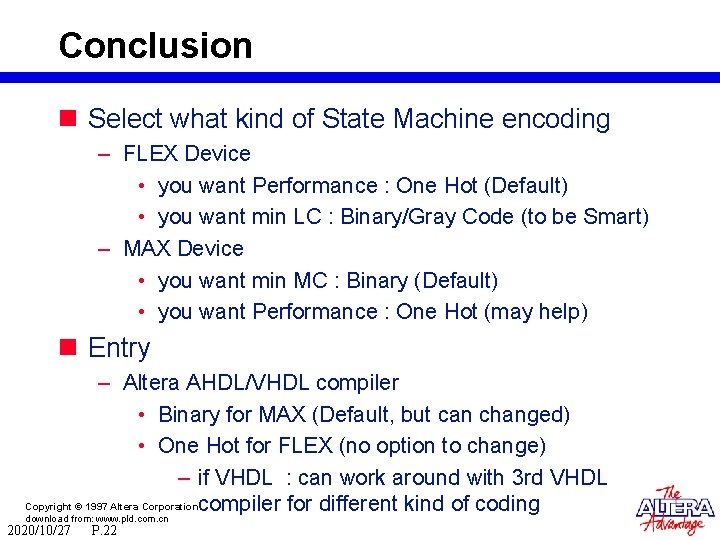

Conclusion n Select what kind of State Machine encoding – FLEX Device • you want Performance : One Hot (Default) • you want min LC : Binary/Gray Code (to be Smart) – MAX Device • you want min MC : Binary (Default) • you want Performance : One Hot (may help) n Entry – Altera AHDL/VHDL compiler • Binary for MAX (Default, but can changed) • One Hot for FLEX (no option to change) – if VHDL : can work around with 3 rd VHDL Copyright © 1997 Altera Corporationcompiler for different kind of coding download from: www. pld. com. cn 2020/10/27 P. 22

- Slides: 22