Onderzoeksgroep PARIS Koen De Bosschere Woensdag 10 november

Onderzoeksgroep PARIS Koen De Bosschere Woensdag 10 november 1999 8/11/1999 Onderzoeksgroep PARIS

RUG informaticavakgroepen q Toegepaste wetenschappen – ELIS, Jan Van Campenhout – INTEC, Paul Lagasse – TELIN, Herwig Bruneel q Wetenschappen – TWI, Gilbert Crombez – CAGE, Joseph Thas 8/11/1999 Onderzoeksgroep PARIS

Vakgroep ELIS q 134 personeelsleden – 19 ZAP – 20 ATP – 95 WP (10 postdocs) q Activiteitsdomeinen – Fysische elektronica – Toegepaste elektronica – Informatiesystemen 8/11/1999 Onderzoeksgroep PARIS

Vakgroep ELIS: activiteiten q Fysische elektronica – LCD-displays – Zonnecellen – Thermo-elektronica – Magnetisme q Toegepaste elektronica q Informatiesystemen 8/11/1999 Onderzoeksgroep PARIS

Vakgroep ELIS: activiteiten q Fysische elektronica q Toegepaste elektronica – VLSI-ontwerp – Display-technologie (LCD) – Interconnectie-technologie – Analoog circuit- en systeemontwerp – Elektrochemische cellen q Informatiesystemen 8/11/1999 Onderzoeksgroep PARIS

8/11/1999 Onderzoeksgroep PARIS

Vakgroep ELIS: activiteiten q Fysische elektronica q Toegepaste elektronica q Informatiesystemen – Spraakverwerking – Medische beeldverwerking – Parallelle Informatiesystemen 8/11/1999 Onderzoeksgroep PARIS

Informatiesystemen q Spraakverwerking – spraakherkenning – spraaksynthese – Technologie & Integratie bvba q Medische beeldverwerking q Parallelle Informatiesystemen 8/11/1999 Onderzoeksgroep PARIS

Informatiesystemen q Spraakverwerking q Medische beeldverwerking – Compressie – Reconstructie – Extractie van informatie – Drukvoorbereiding q Parallelle Informatiesystemen 8/11/1999 Onderzoeksgroep PARIS

Informatiesystemen q Spraakverwerking q Medische beeldverwerking q Parallelle Informatiesystemen – Automatische parallellisering – Ontwerp van digitale systemen – De hardware-software interface 8/11/1999 Onderzoeksgroep PARIS

Paris: automatische parallellisering q Detectie van parallellisme in bestaande programma’s q Codegeneratie voor – systemen met gemeenschappelijk geheugen – gedistribueerde systemen: PVM, MPI, DSM – Multicasting, broadcasting 8/11/1999 Onderzoeksgroep PARIS

Paris: ontwerp van digitale systemen q FPGA’s q VHDL-modellering q Opto-elektronische interconnecties q Topologische eigenschappen van grote circuits 8/11/1999 Onderzoeksgroep PARIS

Paris: hardware-software interface q Hardware-zijde q Software-zijde 8/11/1999 Onderzoeksgroep PARIS

Paris: hardware-software interface q Hardware-zijde – modellering van benchmarks – waardevoorspelling – cache-architecturen – blokgestructureerde architecturen – herconfigureerbare architecturen q Software-zijde 8/11/1999 Onderzoeksgroep PARIS

Paris: hardware-software interface q Hardware-zijde q Software-zijde – optimaliserende linkers • Compaq alpha • Data layout voor DSP’s – parallel debugging • Jiti • Java data race detectie 8/11/1999 Onderzoeksgroep PARIS

Modellering van. Benchmarks q Architectuurbenchmarks: Spec q Moderne processors: > 500 MHz q IPC = 2 q 109 instructies/seconde q Simulatie = 10 000 instructies/seconde q 27 uur simulatie voor 1 s uitvoeringstijd q Effect van optimalisatie op benchmark soms zeer moeilijk te voorspellen 8/11/1999 Onderzoeksgroep PARIS

Modellering van. Benchmarks Doelstelling – karakterisering van benchmarktraces • grootte basisblokken • afhankelijkheidsafstanden • working set, enz. . . – generatie van synthetische benchmarktraces (20% nauwkeurigheid) 8/11/1999 Onderzoeksgroep PARIS

Waardevoorspelling q Veel berekende waarden kunnen voorspeld worden – adressen – opgeladen waarden q Herhoogt het parallellisme op instructieniveau 8/11/1999 Onderzoeksgroep PARIS

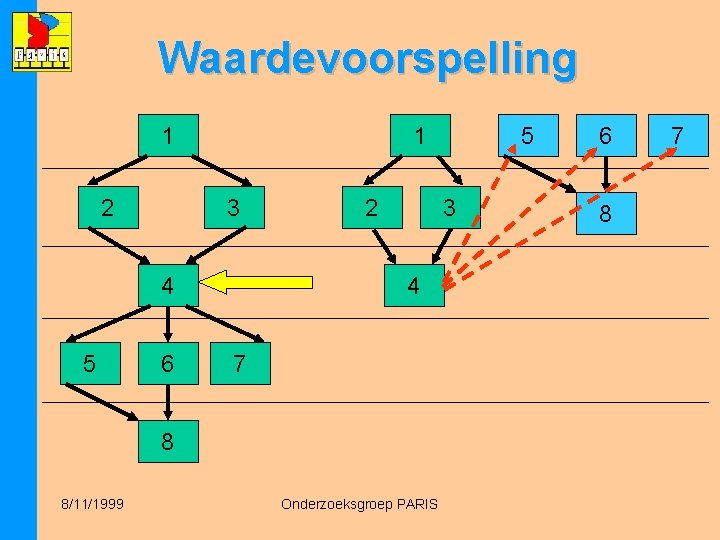

Waardevoorspelling 1 2 1 3 4 5 6 2 3 4 7 8 8/11/1999 5 Onderzoeksgroep PARIS 6 8 7

Waardevoorspelling q Probleem – de meeste instructies kunnen voorspeld worden – voor 64 -bit architectuur n x 64 bit nodig voor de historiek q Oplossing – enkel betrouwbare voorspellingen – enkel instructies in kritisch pad 8/11/1999 Onderzoeksgroep PARIS

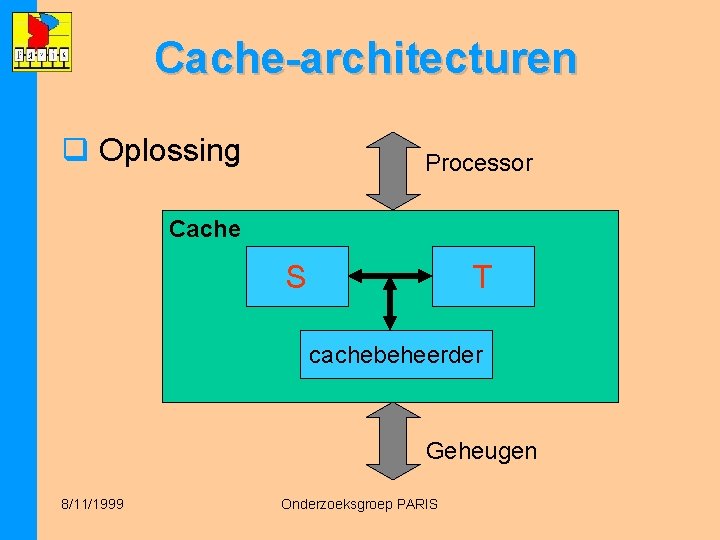

Cache-architecturen q Kloof tussen processorsnelheid en geheugensnelheid neemt exponentieel toe (geheugen >100 keer trager) q Oplossing: hiërarchie van caches (tot 3) q Technologische beperking: snelle cache = kleine cache q Dus: hoe sneller de processor, hoe kleiner de cache moet zijn 8/11/1999 Onderzoeksgroep PARIS

Cache-architecturen q Vaststelling – cachelijnen zeer ongelijk gebruikt – overbevraging in bepaalde gebieden – ongebruikt in andere gebieden q Lokaliteit – gegevens met spatiale lokaliteit kunnen gegevens met temporele lokaliteit verdringen 8/11/1999 Onderzoeksgroep PARIS

Cache-architecturen q Oplossing Processor Cache S T cachebeheerder Geheugen 8/11/1999 Onderzoeksgroep PARIS

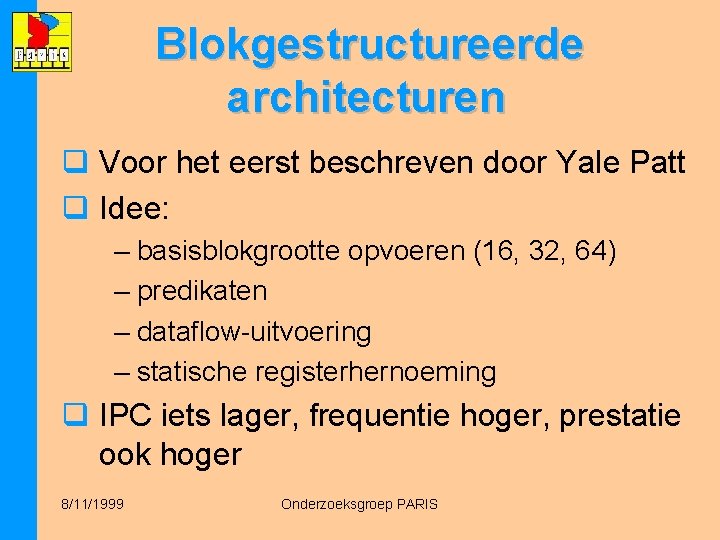

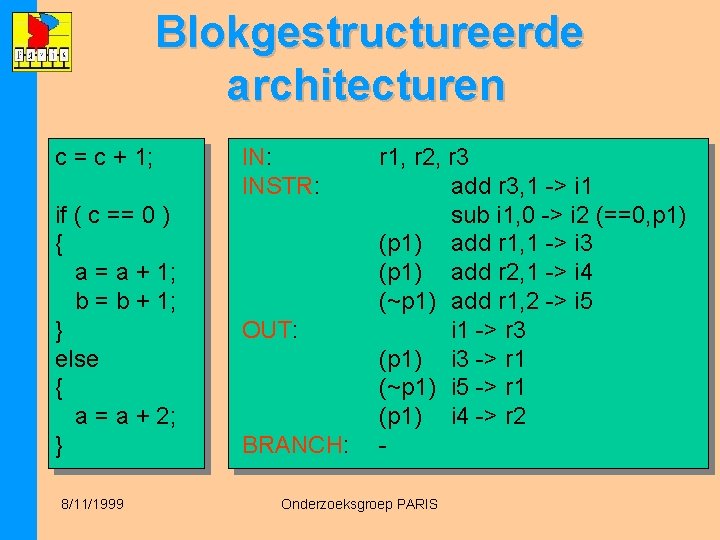

Blokgestructureerde architecturen q Voor het eerst beschreven door Yale Patt q Idee: – basisblokgrootte opvoeren (16, 32, 64) – predikaten – dataflow-uitvoering – statische registerhernoeming q IPC iets lager, frequentie hoger, prestatie ook hoger 8/11/1999 Onderzoeksgroep PARIS

Blokgestructureerde architecturen c = c + 1; if ( c == 0 ) { a = a + 1; b = b + 1; } else { a = a + 2; } 8/11/1999 IN: INSTR: OUT: BRANCH: r 1, r 2, r 3 add r 3, 1 -> i 1 sub i 1, 0 -> i 2 (==0, p 1) (p 1) add r 1, 1 -> i 3 (p 1) add r 2, 1 -> i 4 (~p 1) add r 1, 2 -> i 5 i 1 -> r 3 (p 1) i 3 -> r 1 (~p 1) i 5 -> r 1 (p 1) i 4 -> r 2 - Onderzoeksgroep PARIS

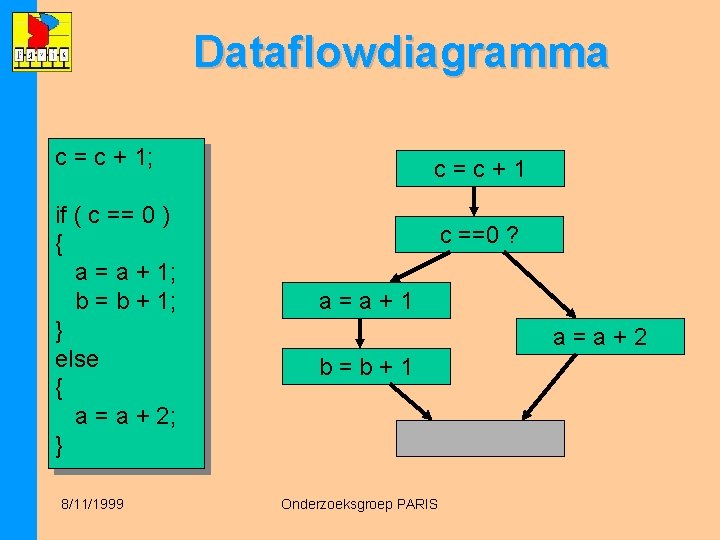

Dataflowdiagramma c = c + 1; if ( c == 0 ) { a = a + 1; b = b + 1; } else { a = a + 2; } 8/11/1999 c=c+1 c ==0 ? a=a+1 a=a+2 b=b+1 Onderzoeksgroep PARIS

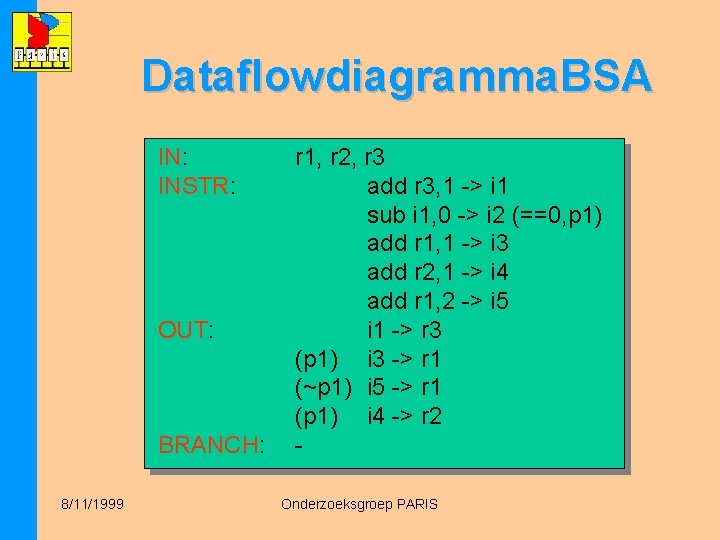

Dataflowdiagramma. BSA IN: INSTR: OUT: BRANCH: 8/11/1999 r 1, r 2, r 3 add r 3, 1 -> i 1 sub i 1, 0 -> i 2 (==0, p 1) add r 1, 1 -> i 3 add r 2, 1 -> i 4 add r 1, 2 -> i 5 i 1 -> r 3 (p 1) i 3 -> r 1 (~p 1) i 5 -> r 1 (p 1) i 4 -> r 2 Onderzoeksgroep PARIS

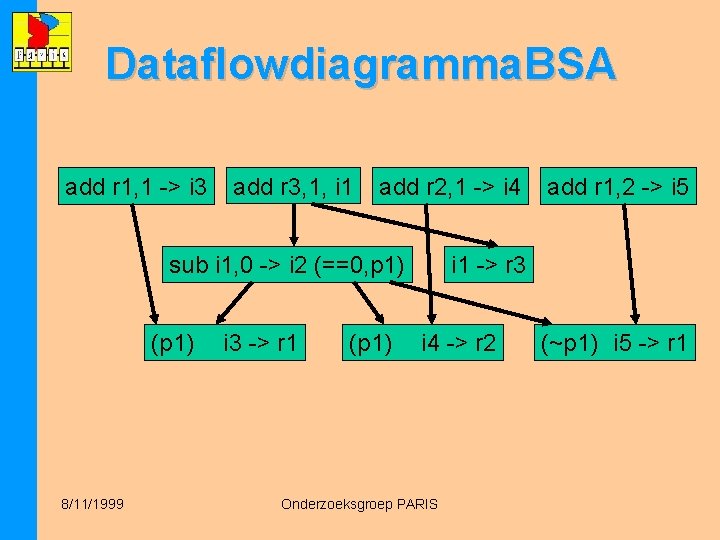

Dataflowdiagramma. BSA add r 1, 1 -> i 3 add r 3, 1, i 1 add r 2, 1 -> i 4 sub i 1, 0 -> i 2 (==0, p 1) (p 1) 8/11/1999 i 3 -> r 1 (p 1) add r 1, 2 -> i 5 i 1 -> r 3 i 4 -> r 2 Onderzoeksgroep PARIS (~p 1) i 5 -> r 1

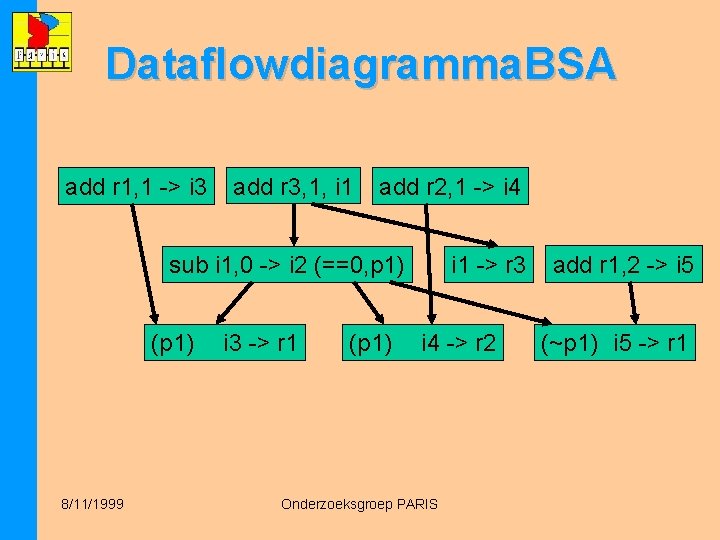

Dataflowdiagramma. BSA add r 1, 1 -> i 3 add r 3, 1, i 1 add r 2, 1 -> i 4 sub i 1, 0 -> i 2 (==0, p 1) (p 1) 8/11/1999 i 3 -> r 1 (p 1) i 1 -> r 3 i 4 -> r 2 Onderzoeksgroep PARIS add r 1, 2 -> i 5 (~p 1) i 5 -> r 1

Herconfigureerbare processors q Nu > 100 miljoen transistors per chip q Geregeld uitbreidingen (b. v. multimedia) q Herconfigureerbaarheid: laat de gebruiker toe om zelf instructies te definiëren (fpga) – signaalverwerking – bitmanipulaties –. . . 8/11/1999 Onderzoeksgroep PARIS

Optimaliserende linkers q Compiler heeft nooit zicht op het complete programma q b. v. sqrt(2) data-layout (caches, banken) inlining van bibliotheekroutines q Alto: Another Link-Time Optimizer q 20% snelheidswinst 8/11/1999 Onderzoeksgroep PARIS

Parallel Debugging q Parallelle programma’s worden niet steeds deterministisch uitgevoerd q Cyclisch debuggen onbruikbaar (Heisenbugs) q Oplossing: opnemen van een uitvoering en deze gebruiken om latere uitvoeringen te controleren 8/11/1999 Onderzoeksgroep PARIS

Parallel Debugging q Probleem: traces die alle nietdeterminisme bevatten zijn extreem groot q Compromis: enkel synchronisatieoperaties tracen. q Probleem: data-races kunnen niet heruitgevoerd worden 8/11/1999 Onderzoeksgroep PARIS

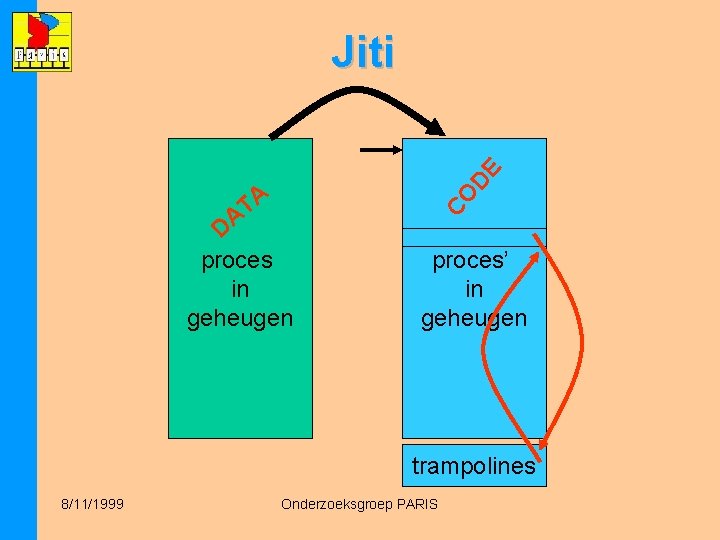

Parallel Debugging q Oplossing: data-race detectie tijdens de heruitvoering: eerste data race wordt gegarandeerd gedetecteerd q Implementatie: Jiti 8/11/1999 Onderzoeksgroep PARIS

D proces in geheugen CO A T A DE Jiti proces’ in geheugen trampolines 8/11/1999 Onderzoeksgroep PARIS

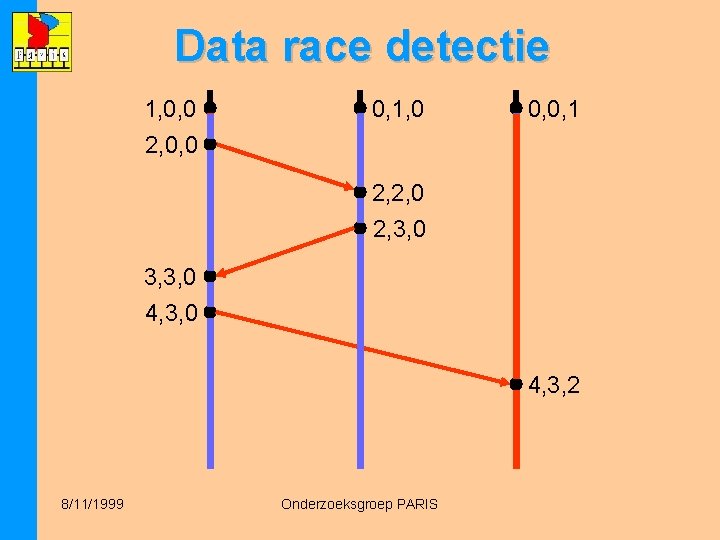

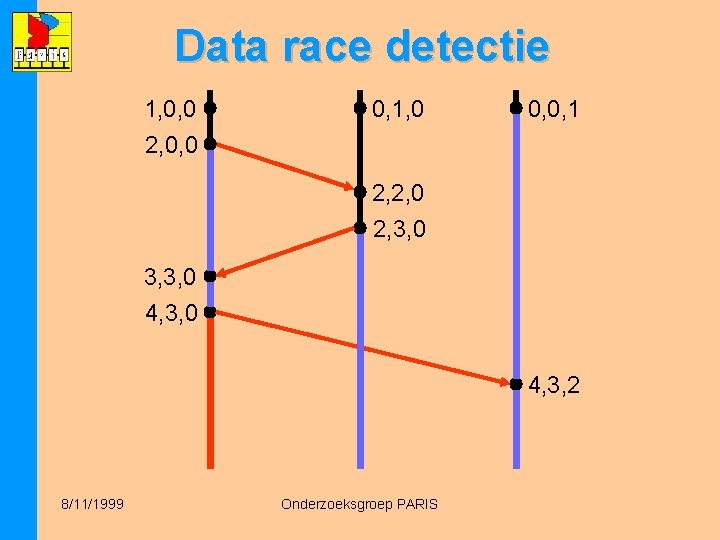

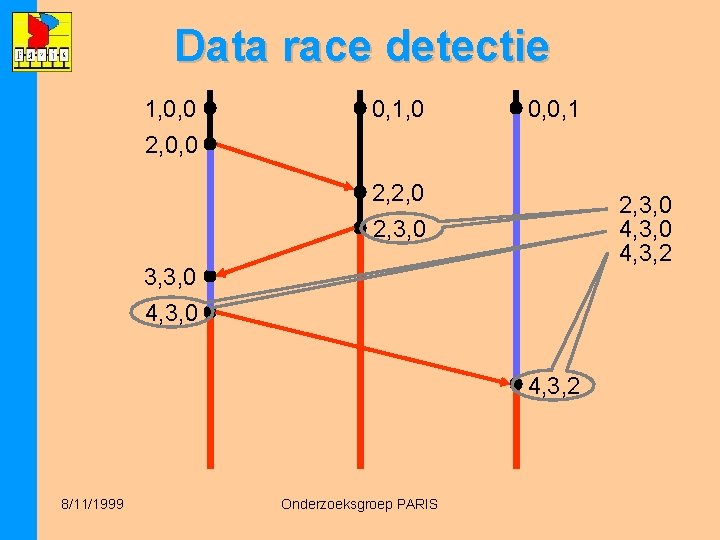

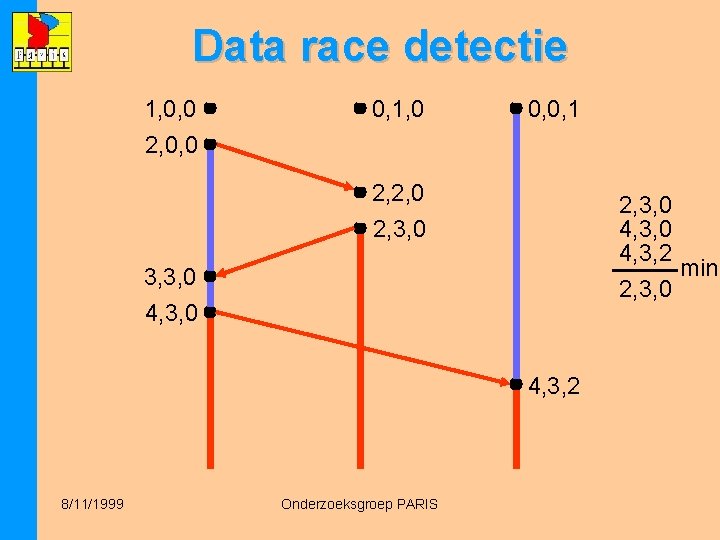

Data race detectie 1, 0, 0 0, 1, 0 0, 0, 1 2, 0, 0 2, 2, 0 2, 3, 0 3, 3, 0 4, 3, 2 8/11/1999 Onderzoeksgroep PARIS

Data race detectie 1, 0, 0 0, 1, 0 0, 0, 1 2, 0, 0 2, 2, 0 2, 3, 0 3, 3, 0 4, 3, 2 8/11/1999 Onderzoeksgroep PARIS

Data race detectie 1, 0, 0 0, 1, 0 0, 0, 1 2, 0, 0 2, 2, 0 2, 3, 0 4, 3, 2 3, 3, 0 4, 3, 2 8/11/1999 Onderzoeksgroep PARIS

Data race detectie 1, 0, 0 0, 1, 0 0, 0, 1 2, 0, 0 2, 2, 0 2, 3, 0 4, 3, 2 min 2, 3, 0 3, 3, 0 4, 3, 2 8/11/1999 Onderzoeksgroep PARIS

Data race detectie q Nadeel van Jiti: alle geheugenlocaties worden vergeleken q In de praktijk hoeft dit niet – read-only geheugenlocaties kunnen nooit een race veroorzaken – proces-lokale data kunnen nooit een race veroorzaken – b. v. Java 8/11/1999 Onderzoeksgroep PARIS

Java data race detectie q JVM laat toe te achterhalen welke Java objecten manipuleerbaar zijn q Enkel objecten manipuleerbaar door minstens twee draden vereisen data race detectie q Sterke reductie van het aantal te tracen objecten en geheugenlocaties 8/11/1999 Onderzoeksgroep PARIS

Conclusie q Centrale thema: hardware-software interface – parallellisme – architecturale verbeteringen – efficiënte tools (compilers, linkers, debuggers) q Symposium over nieuwe tendensen in de computer architectuur 16 december. 8/11/1999 Onderzoeksgroep PARIS

- Slides: 42