OnChip Sensors for Process Aging and Temperature Variation

- Slides: 14

On-Chip Sensors for Process, Aging, and Temperature Variation Kaushik Mazumdar Jared Robertson

Overview • • • Motivation Existing Methods Test Circuit Simulations Summary References

Motivation • Local Process Variation • Global Process Variation • Temperature Variation • NBTI/PBTI Degradation [1]

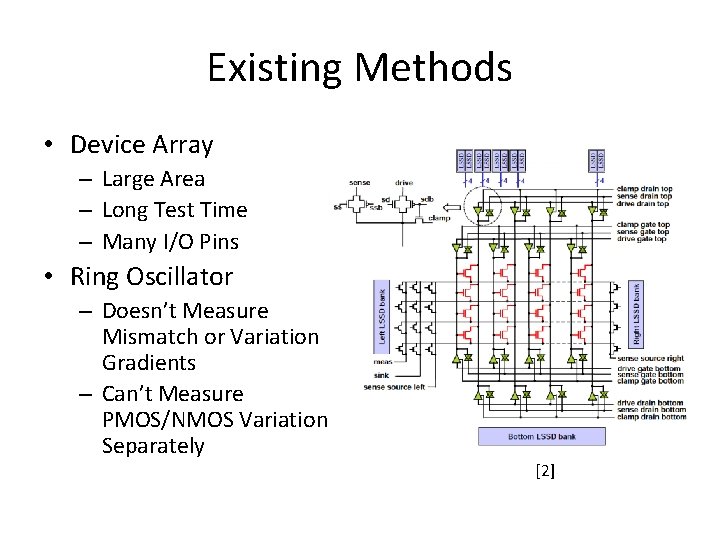

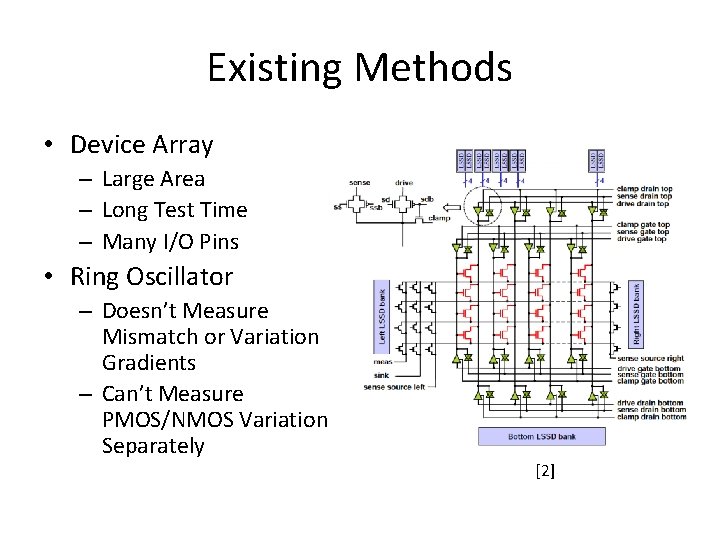

Existing Methods • Device Array – Large Area – Long Test Time – Many I/O Pins • Ring Oscillator – Doesn’t Measure Mismatch or Variation Gradients – Can’t Measure PMOS/NMOS Variation Separately [2]

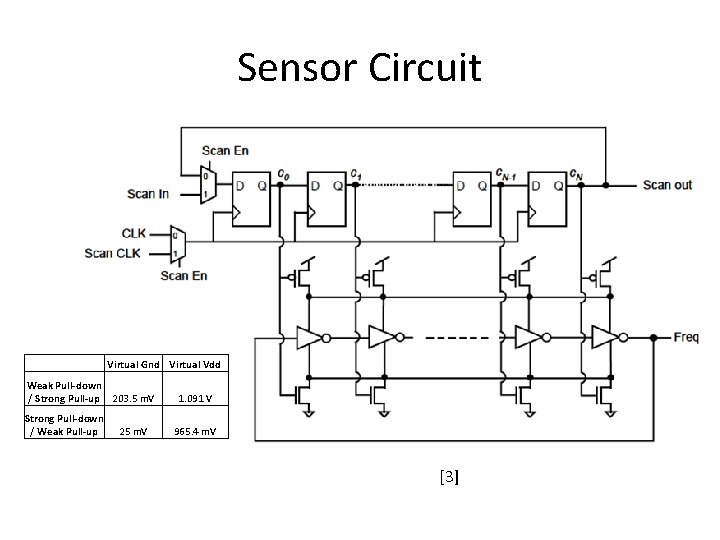

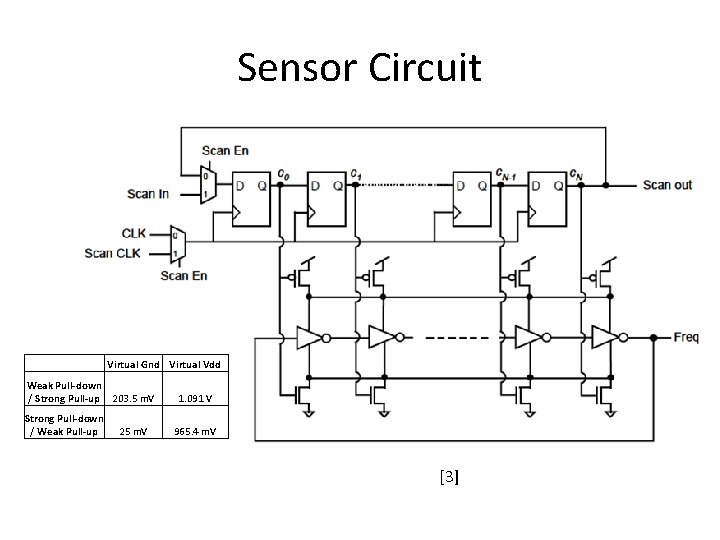

Sensor Circuit Virtual Gnd Virtual Vdd Weak Pull-down / Strong Pull-up 203. 5 m. V Strong Pull-down / Weak Pull-up 25 m. V 1. 091 V 965. 4 m. V [3]

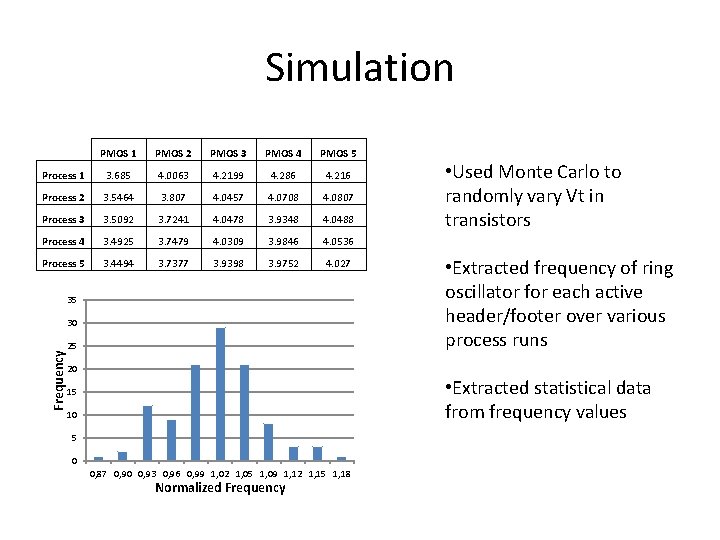

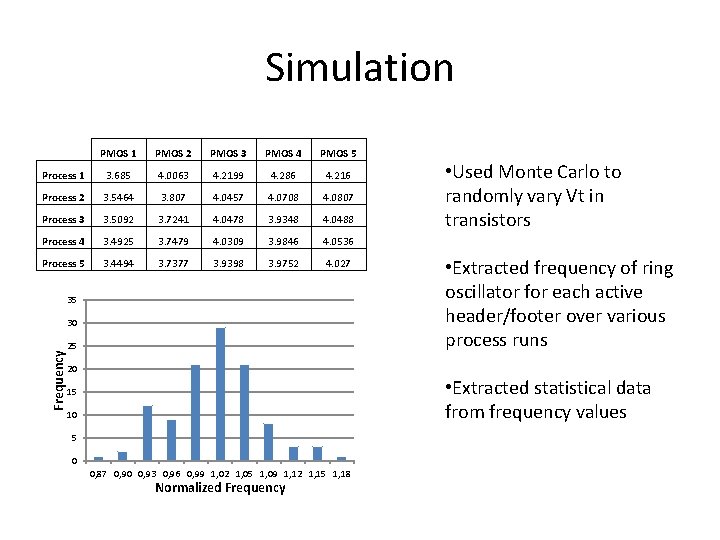

Simulation PMOS 1 PMOS 2 PMOS 3 PMOS 4 PMOS 5 Process 1 3. 685 4. 0063 4. 2199 4. 286 4. 216 Process 2 3. 5464 3. 807 4. 0457 4. 0708 4. 0807 Process 3 3. 5092 3. 7241 4. 0478 3. 9348 4. 0488 Process 4 3. 4925 3. 7479 4. 0309 3. 9846 4. 0536 Process 5 3. 4494 3. 7377 3. 9398 3. 9752 4. 027 35 Frequency 30 25 • Used Monte Carlo to randomly vary Vt in transistors • Extracted frequency of ring oscillator for each active header/footer over various process runs 20 • Extracted statistical data from frequency values 15 10 5 0 0, 87 0, 90 0, 93 0, 96 0, 99 1, 02 1, 05 1, 09 1, 12 1, 15 1, 18 Normalized Frequency

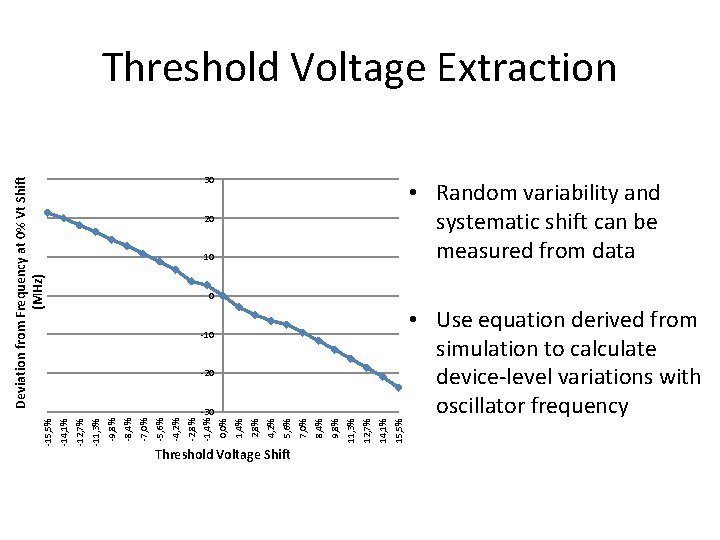

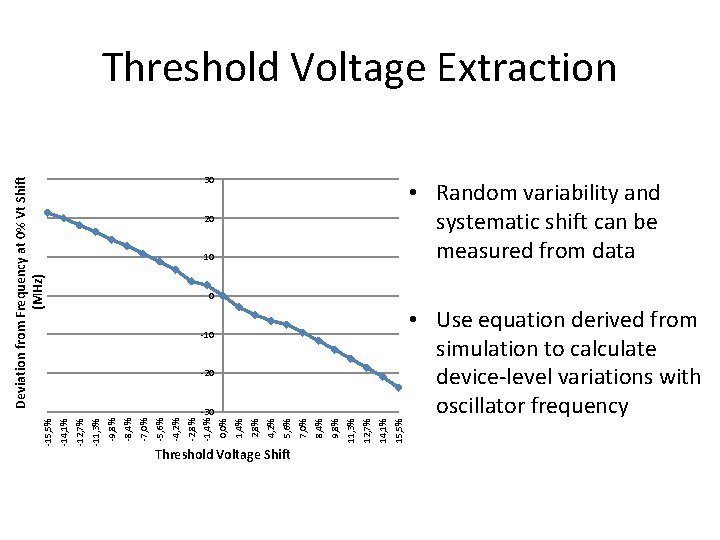

Threshold Voltage Extraction • Random variability and systematic shift can be measured from data 20 10 0 -10 -20 Threshold Voltage Shift 15, 5% 14, 1% 12, 7% 11, 3% 9, 8% 8, 4% 7, 0% 5, 6% 4, 2% 2, 8% 1, 4% 0, 0% -1, 4% -2, 8% -4, 2% -5, 6% -7, 0% -8, 4% -9, 8% -11, 3% -12, 7% -30 -14, 1% -15, 5% Deviation from Frequency at 0% Vt Shift (MHz) 30 • Use equation derived from simulation to calculate device-level variations with oscillator frequency

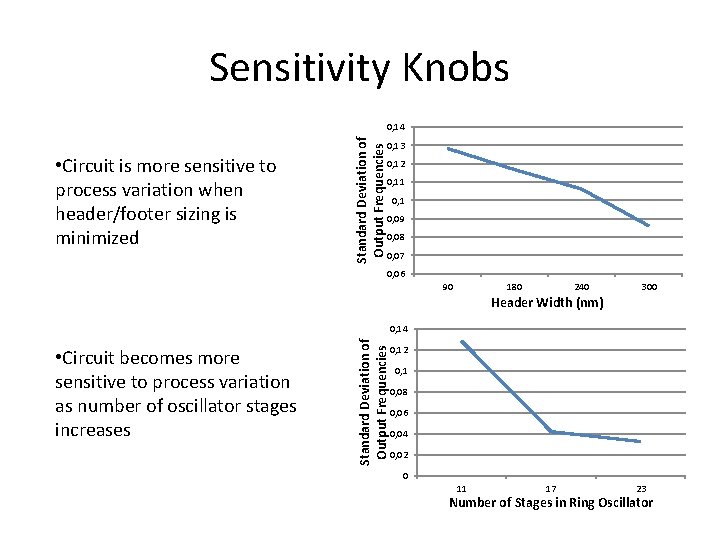

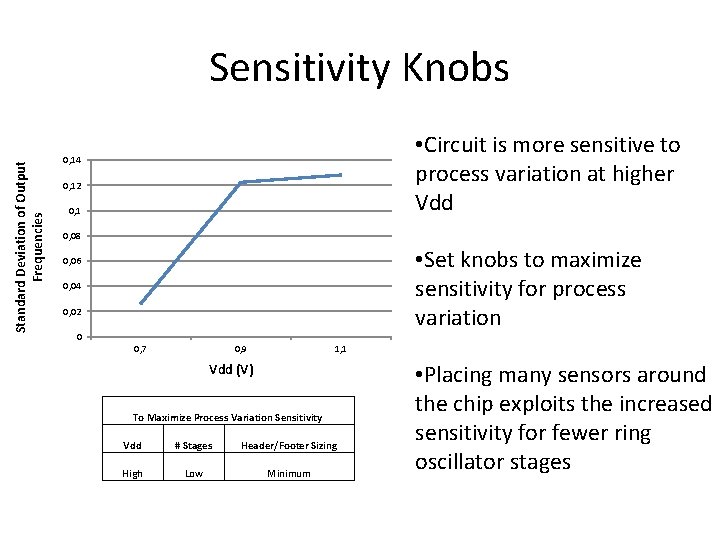

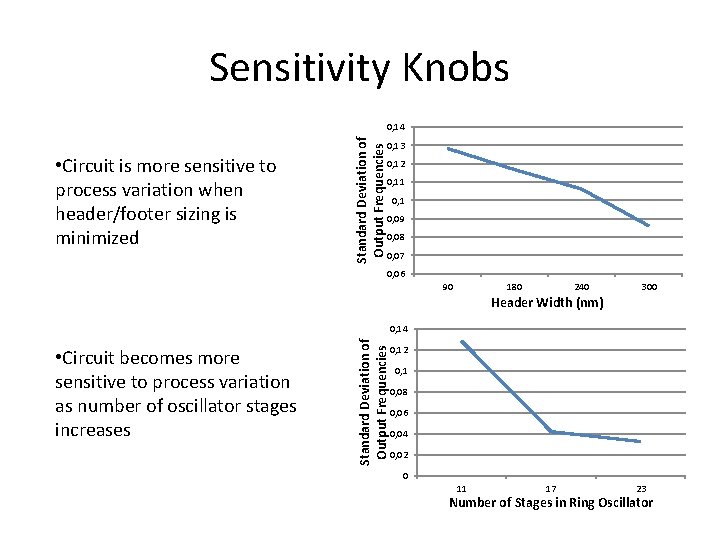

Sensitivity Knobs • Circuit is more sensitive to process variation when header/footer sizing is minimized Standard Deviation of Output Frequencies 0, 14 0, 13 0, 12 0, 11 0, 09 0, 08 0, 07 0, 06 90 180 240 300 Header Width (nm) • Circuit becomes more sensitive to process variation as number of oscillator stages increases Standard Deviation of Output Frequencies 0, 14 0, 12 0, 1 0, 08 0, 06 0, 04 0, 02 0 11 17 23 Number of Stages in Ring Oscillator

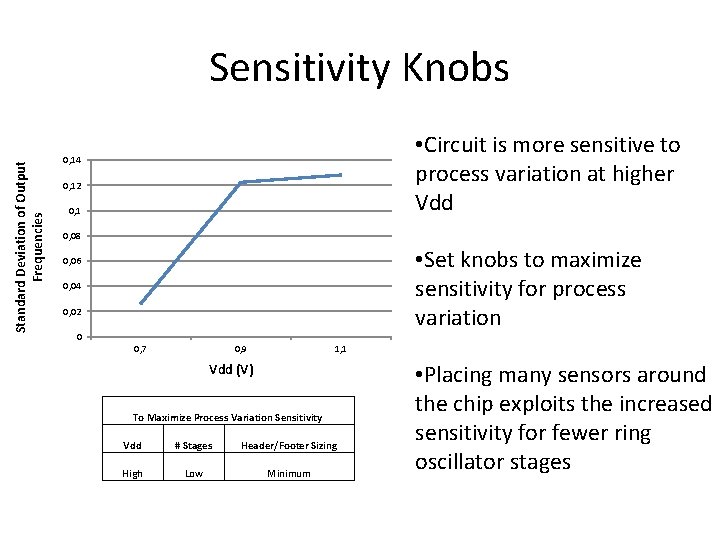

Standard Deviation of Output Frequencies Sensitivity Knobs • Circuit is more sensitive to process variation at higher Vdd 0, 14 0, 12 0, 1 0, 08 • Set knobs to maximize sensitivity for process variation 0, 06 0, 04 0, 02 0 0, 7 0, 9 1, 1 Vdd (V) To Maximize Process Variation Sensitivity Vdd # Stages Header/Footer Sizing High Low Minimum • Placing many sensors around the chip exploits the increased sensitivity for fewer ring oscillator stages

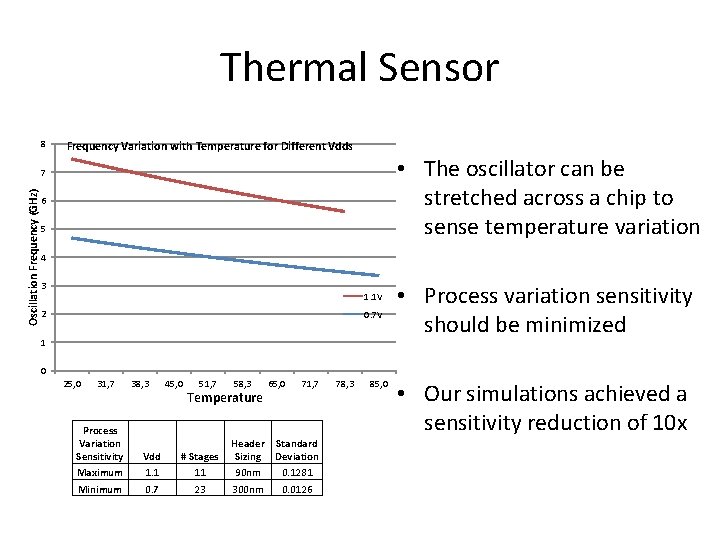

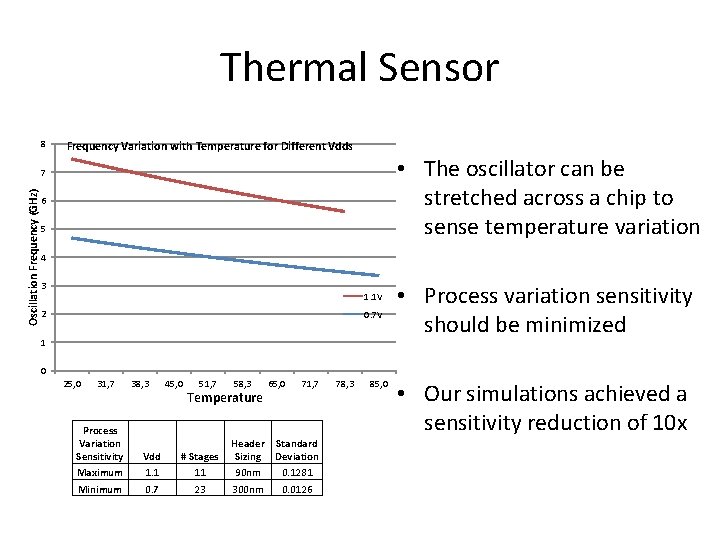

Thermal Sensor 8 Frequency Variation with Temperature for Different Vdds • The oscillator can be stretched across a chip to sense temperature variation Oscillation Frequency (GHz) 7 6 5 4 3 1. 1 V 2 0. 7 V 1 • Process variation sensitivity should be minimized 0 25, 0 31, 7 Process Variation Sensitivity Maximum Minimum 38, 3 Vdd 1. 1 0. 7 45, 0 51, 7 58, 3 Temperature # Stages 11 23 65, 0 71, 7 Header Standard Sizing Deviation 90 nm 0. 1281 300 nm 0. 0126 78, 3 85, 0 • Our simulations achieved a sensitivity reduction of 10 x

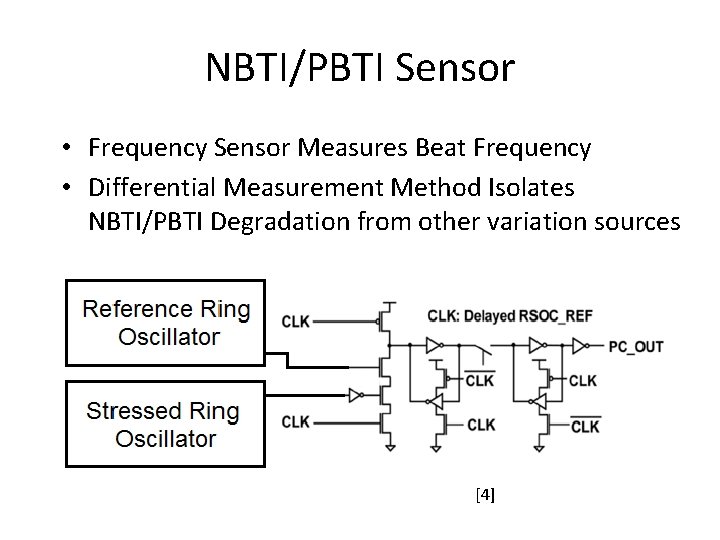

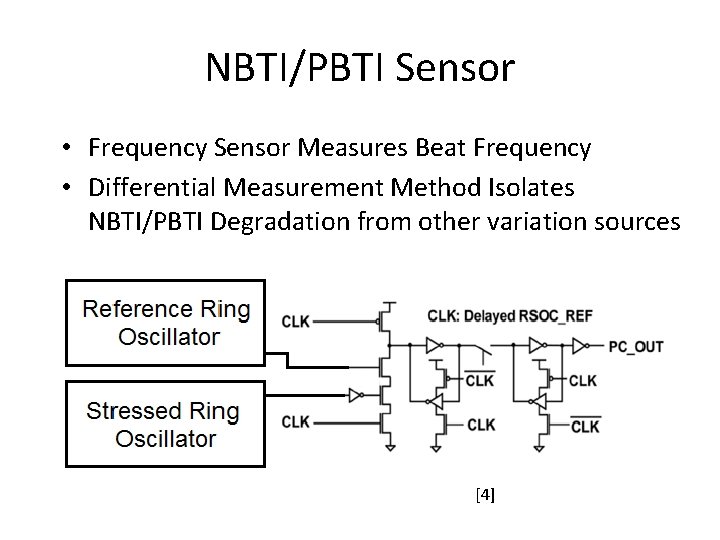

NBTI/PBTI Sensor • Frequency Sensor Measures Beat Frequency • Differential Measurement Method Isolates NBTI/PBTI Degradation from other variation sources [4]

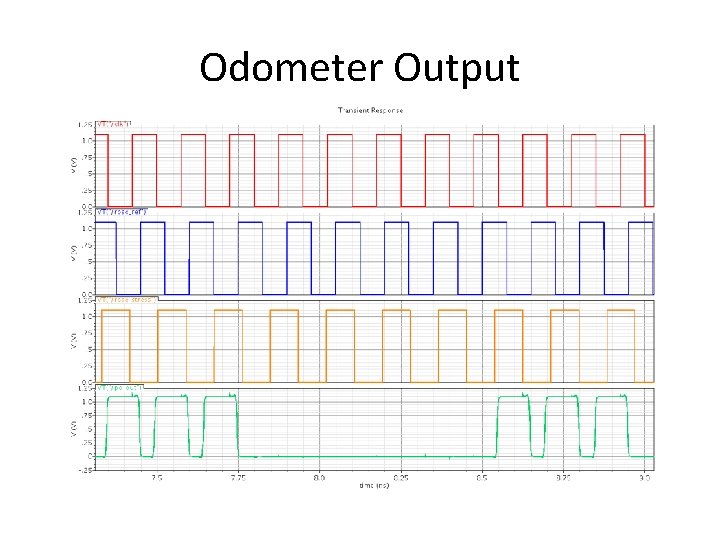

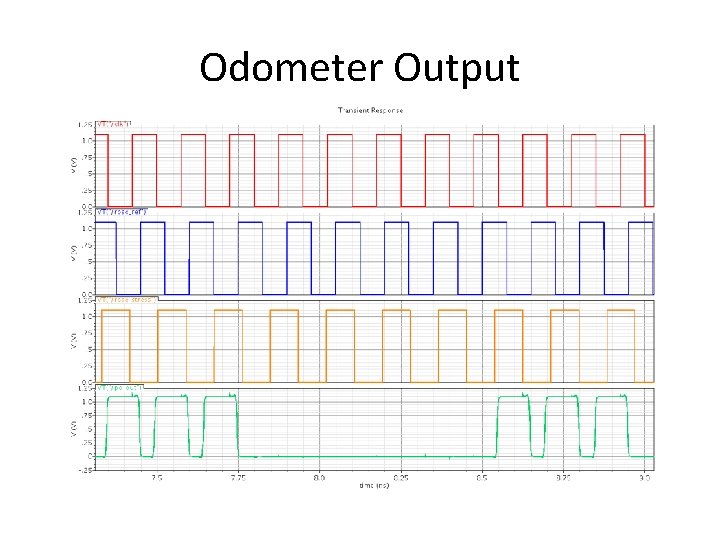

Odometer Output

Summary • Analyzed variation issues and existing solutions • Showed simulation methodology and results • Tuned oscillator circuit to isolate process variation from temperature • Displayed how circuit can be used as a temperature sensor • Developed NBTI/PBTI degradation detection method • Discussion of possible future work

References 1. M. A. Alam, S. Mahapatra, "A comprehensive model of PMOS NBTI degradation, " Microelectronics Reliability, vol. 45, pp. 71 --81, 2005. 2. Kanak Agarwal; Kanak Sani Nassif; “Characterizing process variation in nanometer CMOS”, Proceedings of the 44 th annual conference on Design automation, June 04 -08, 2007, San Diego, California. 3. Agarwal, Kanak, “On-die sensors for measuring process and environmental variation in integrated circuits. ” IBM Corps. Austin, TX. 2010. 4. Tae-Hyoung Kim; Persaud, R. ; Kim, C. H. ; "Silicon Odometer: An On-Chip Reliability Monitor for Measuring Frequency Degradation of Digital Circuits, " Solid-State Circuits, IEEE Journal of , vol. 43, no. 4, pp. 874 -880, April 2008. 5. Wei Zhao; Liu, F. ; Agarwal, K. ; Acharyya, D. ; Nassif, S. R. ; Nowka, K. J. ; Yu Cao; , "Rigorous Extraction of Process Variations for 65 -nm CMOS Design, " Semiconductor Manufacturing, IEEE Transactions on , vol. 22, no. 1, pp. 196 -203, Feb. 2009. 6. Kumar, R. ; Kursun, V. ; , "Temperature Variation Insensitive Energy Efficient CMOS Circuits in a 65 nm CMOS Technology, " Circuits and Systems, 2006. MWSCAS '06. 49 th IEEE International Midwest Symposium on , vol. 2, no. , pp. 226 -230, 6 -9 Aug. 2006.