On the Size and Generation of Minimal NDetection

- Slides: 17

On the Size and Generation of Minimal N-Detection Tests Kalyana R. Kantipudi Vishwani D. Agrawal Department of Electrical and Computer Engineering Auburn University, AL 36849 USA 19 th International Conference on VLSI Design, Hyderabad, January 3 -7, 2006 Jan. 6, 2006 VLSI Design '06

Motivation for This Work • N-detection vectors are known to have a higher coverage of “real defects”. • Increased test length for N-detection tests directly impacts testing cost. • Efficient ways to find minimal N-detection test set are still evolving. • There is no proven lower bound on the size of the N-detection vectors. Jan. 6, 2006 VLSI Design '06 2

Outline • Introduction • Theoretical minimum for an N-detection test set • ILP based N-detection approach • Results • Conclusions Jan. 6, 2006 VLSI Design '06 3

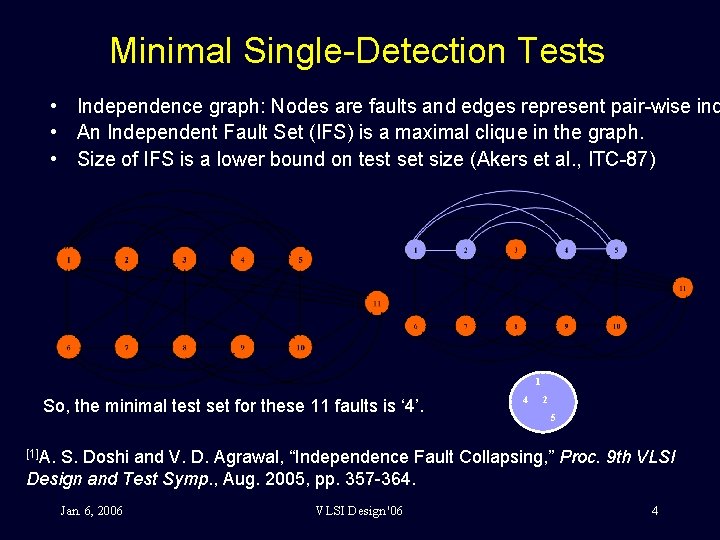

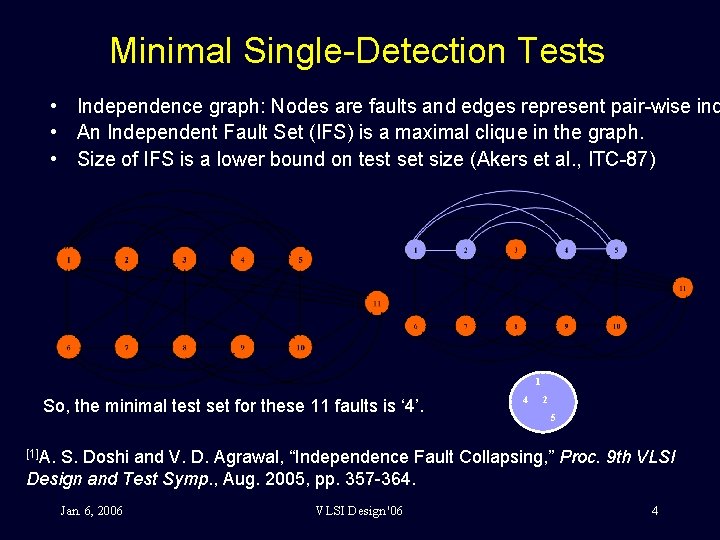

Minimal Single-Detection Tests • Independence graph: Nodes are faults and edges represent pair-wise ind • An Independent Fault Set (IFS) is a maximal clique in the graph. • Size of IFS is a lower bound on test set size (Akers et al. , ITC-87) 1 So, the minimal test set for these 11 faults is ‘ 4’. 4 2 5 [1]A. S. Doshi and V. D. Agrawal, “Independence Fault Collapsing, ” Proc. 9 th VLSI Design and Test Symp. , Aug. 2005, pp. 357 -364. Jan. 6, 2006 VLSI Design '06 4

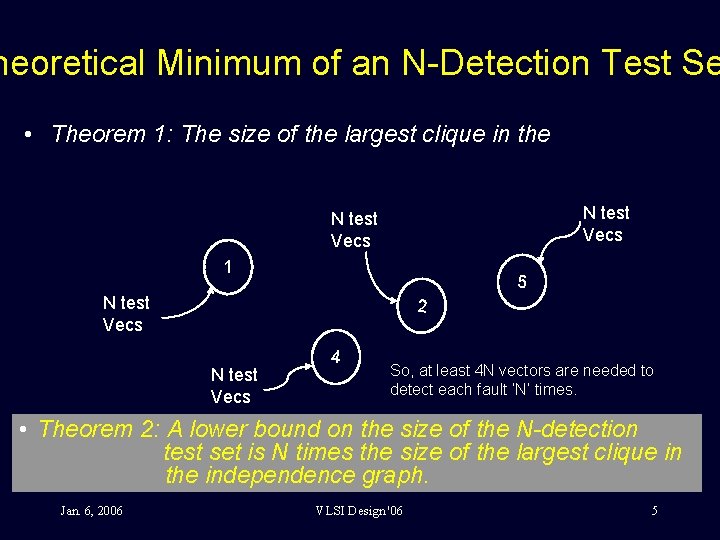

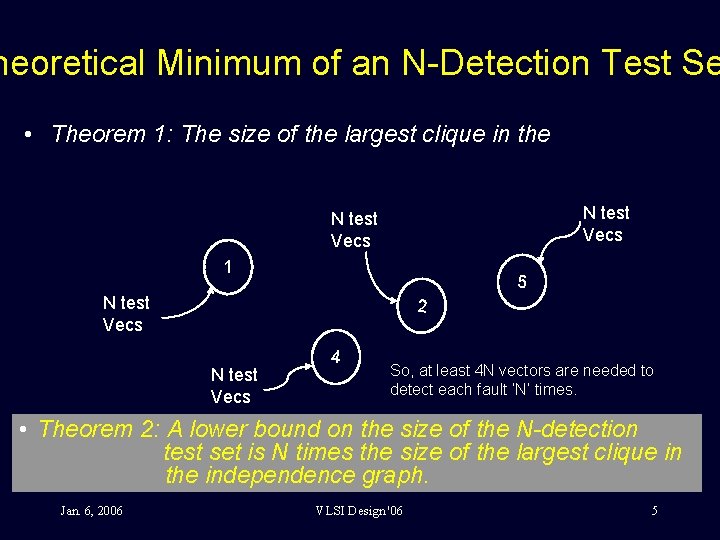

heoretical Minimum of an N-Detection Test Se • Theorem 1: The size of the largest clique in the N test Vecs 1 5 N test Vecs 2 N test Vecs 4 So, at least 4 N vectors are needed to detect each fault ‘N’ times. • Theorem 2: A lower bound on the size of the N-detection test set is N times the size of the largest clique in the independence graph. Jan. 6, 2006 VLSI Design '06 5

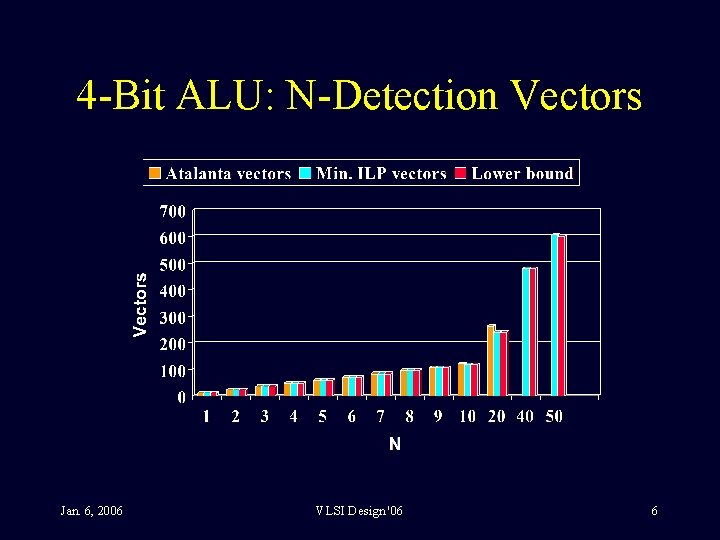

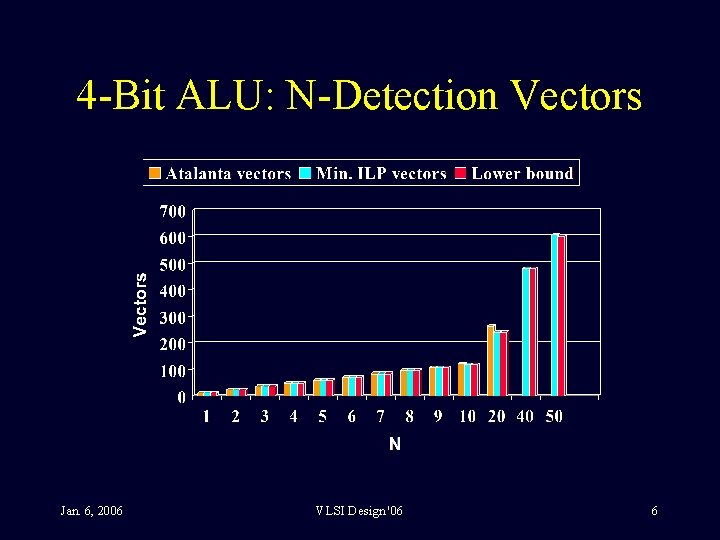

4 -Bit ALU: N-Detection Vectors Jan. 6, 2006 VLSI Design '06 6

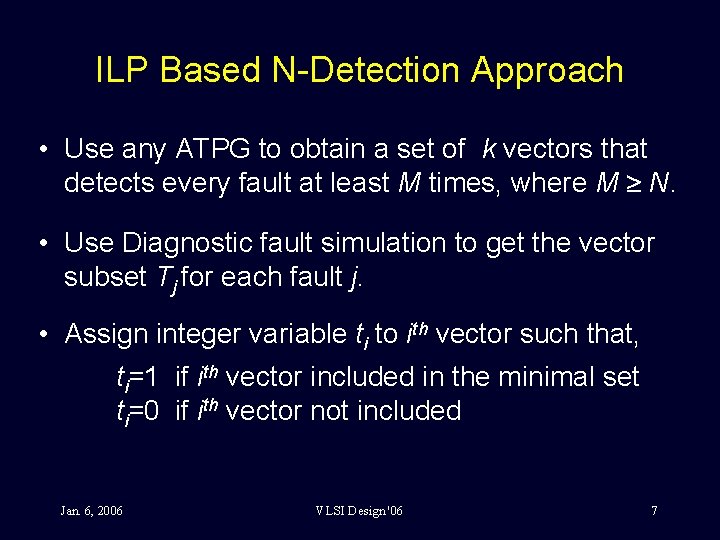

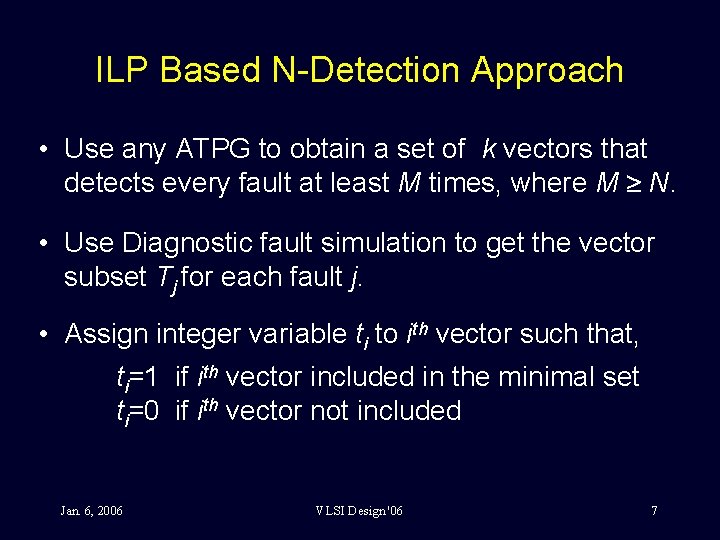

ILP Based N-Detection Approach • Use any ATPG to obtain a set of k vectors that detects every fault at least M times, where M N. • Use Diagnostic fault simulation to get the vector subset Tj for each fault j. • Assign integer variable ti to ith vector such that, ti=1 if ith vector included in the minimal set ti=0 if ith vector not included Jan. 6, 2006 VLSI Design '06 7

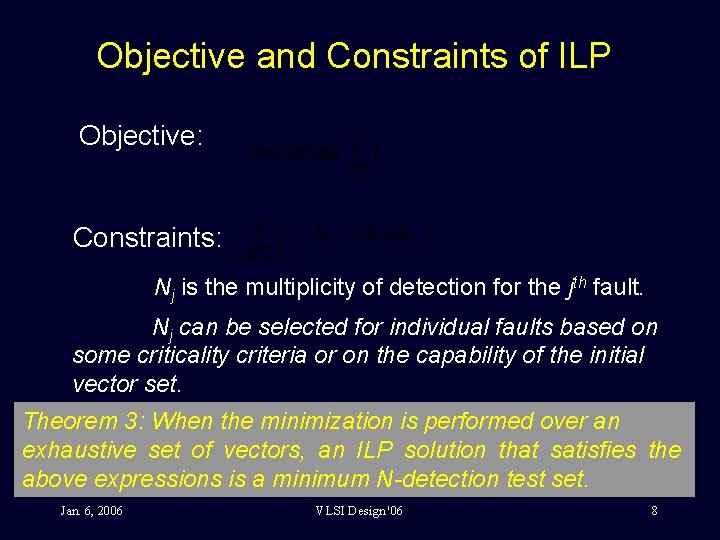

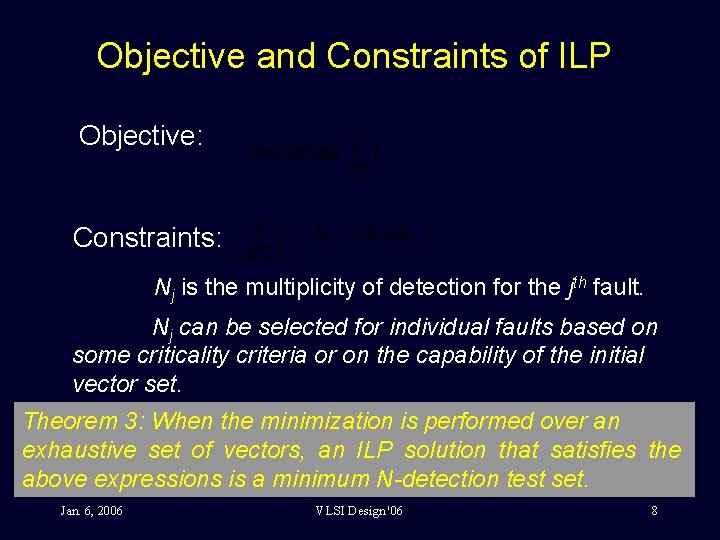

Objective and Constraints of ILP Objective: Constraints: Nj is the multiplicity of detection for the jth fault. Nj can be selected for individual faults based on some criticality criteria or on the capability of the initial vector set. Theorem 3: When the minimization is performed over an exhaustive set of vectors, an ILP solution that satisfies the above expressions is a minimum N-detection test set. Jan. 6, 2006 VLSI Design '06 8

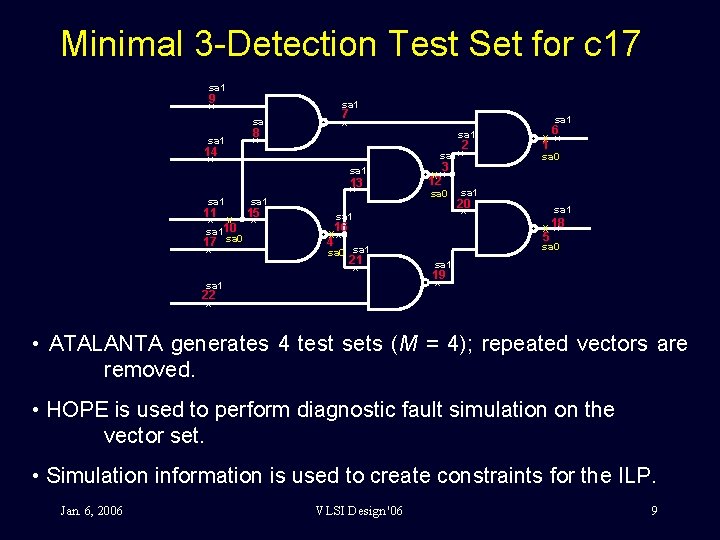

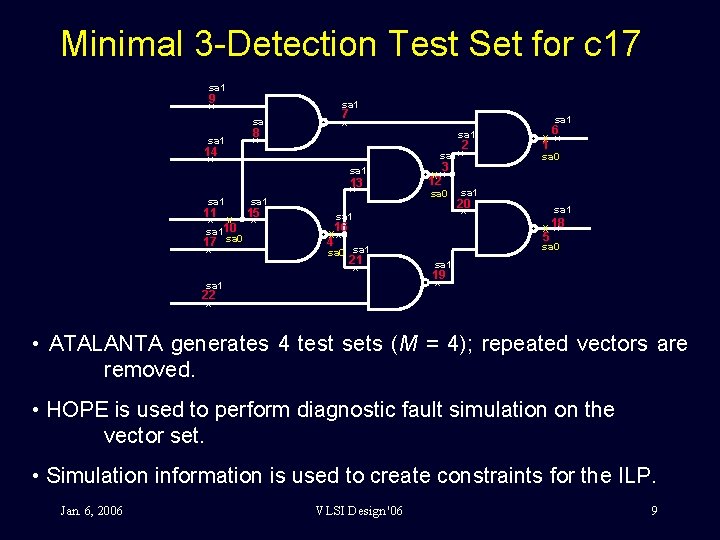

Minimal 3 -Detection Test Set for c 17 sa 1 9 sa 1 x 7 sa 1 14 sa 1 x 8 sa 1 x 2 sa 1 x x sa 1 13 x sa 1 11 sa 1 15 x x X sa 110 17 sa 0 x 3 Xx 12 sa 0 sa 1 X x 1 sa 0 sa 1 20 x sa 1 18 X x 5 16 Xx 4 sa 0 sa 1 21 x 6 sa 0 sa 1 19 x sa 1 22 x • ATALANTA generates 4 test sets (M = 4); repeated vectors are removed. • HOPE is used to perform diagnostic fault simulation on the vector set. • Simulation information is used to create constraints for the ILP. Jan. 6, 2006 VLSI Design '06 9

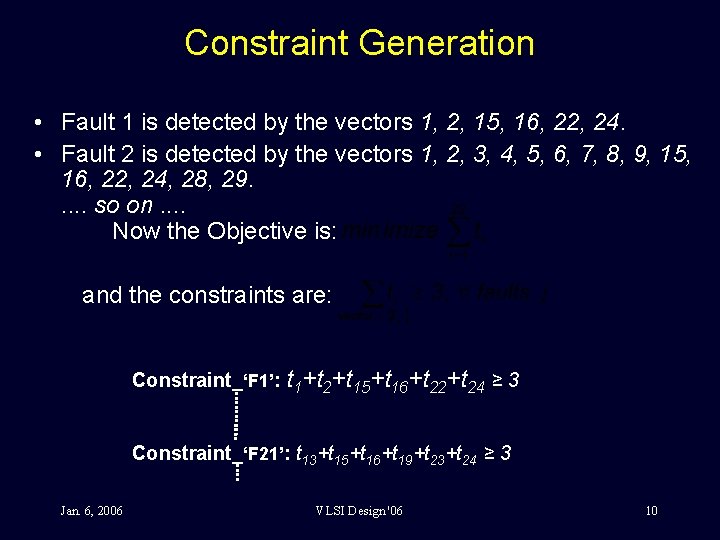

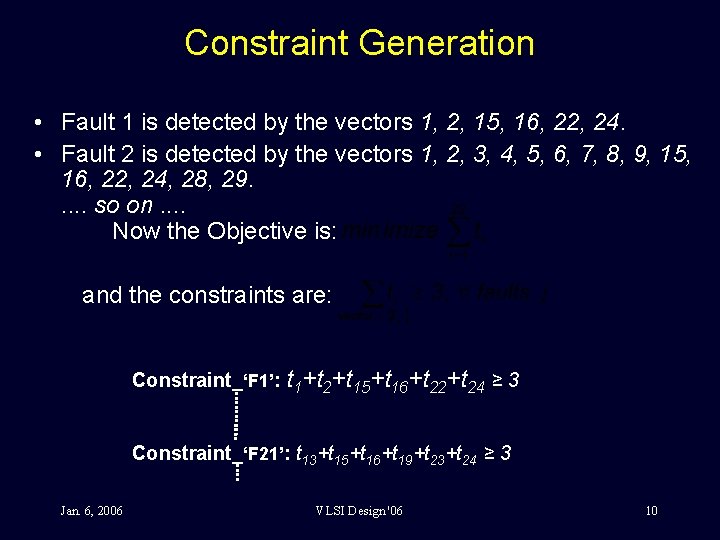

Constraint Generation • Fault 1 is detected by the vectors 1, 2, 15, 16, 22, 24. • Fault 2 is detected by the vectors 1, 2, 3, 4, 5, 6, 7, 8, 9, 15, 16, 22, 24, 28, 29. . . so on. . Now the Objective is: and the constraints are: Constraint_‘F 1’: t 1+t 2+t 15+t 16+t 22+t 24 ≥ 3 Constraint_‘F 21’: t 13+t 15+t 16+t 19+t 23+t 24 ≥ 3 Jan. 6, 2006 VLSI Design '06 10

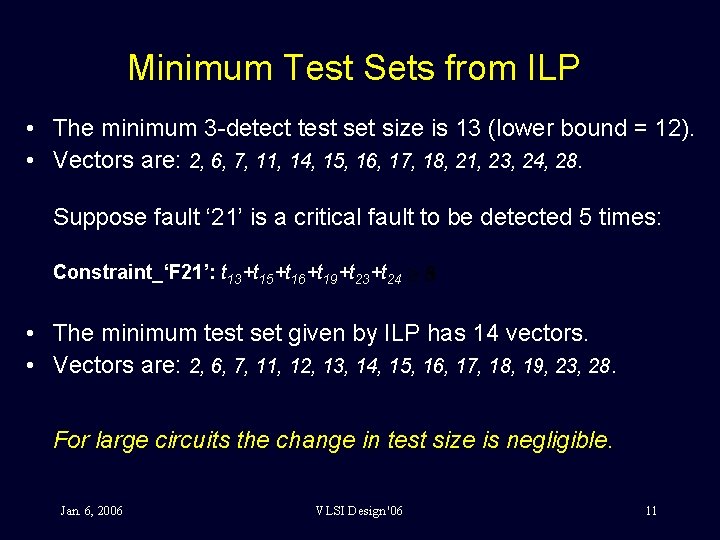

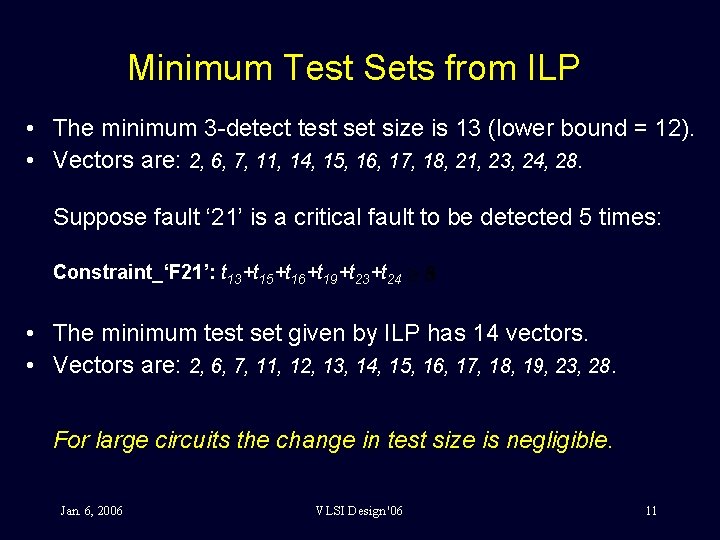

Minimum Test Sets from ILP • The minimum 3 -detect test set size is 13 (lower bound = 12). • Vectors are: 2, 6, 7, 11, 14, 15, 16, 17, 18, 21, 23, 24, 28. Suppose fault ‘ 21’ is a critical fault to be detected 5 times: Constraint_‘F 21’: t 13+t 15+t 16+t 19+t 23+t 24 • The minimum test set given by ILP has 14 vectors. • Vectors are: 2, 6, 7, 11, 12, 13, 14, 15, 16, 17, 18, 19, 23, 28. For large circuits the change in test size is negligible. Jan. 6, 2006 VLSI Design '06 11

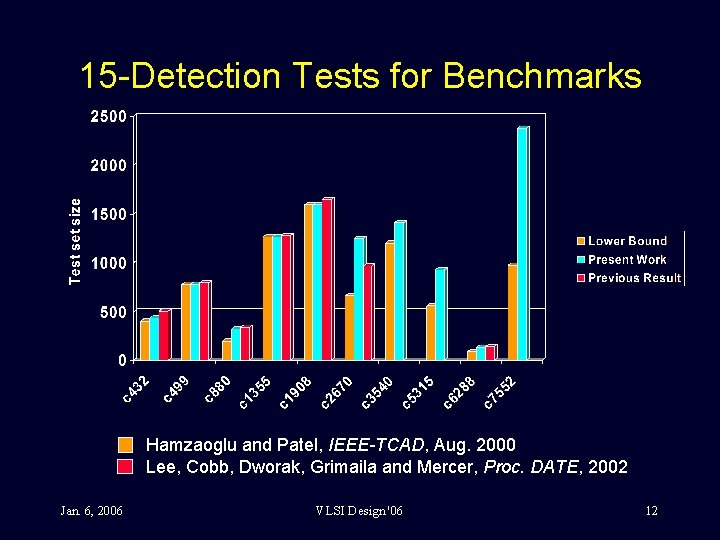

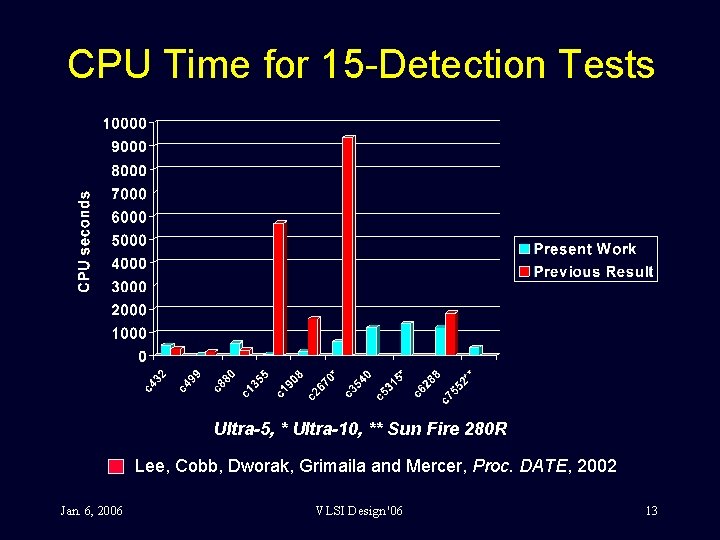

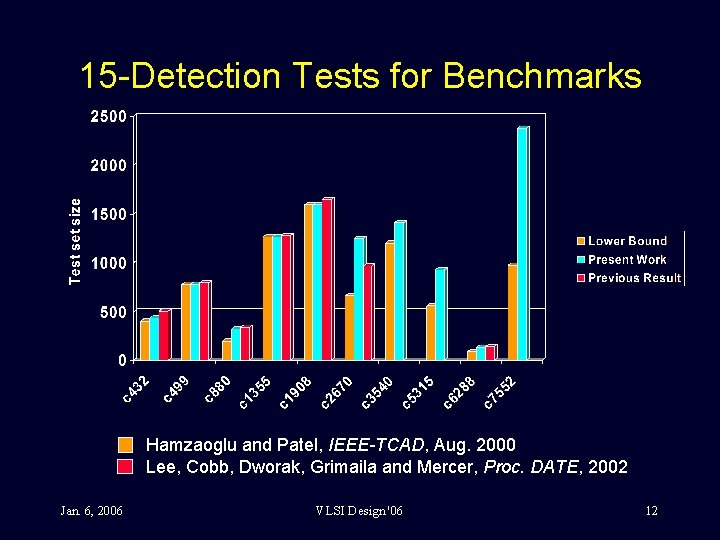

15 -Detection Tests for Benchmarks Hamzaoglu and Patel, IEEE-TCAD, Aug. 2000 Lee, Cobb, Dworak, Grimaila and Mercer, Proc. DATE, 2002 Jan. 6, 2006 VLSI Design '06 12

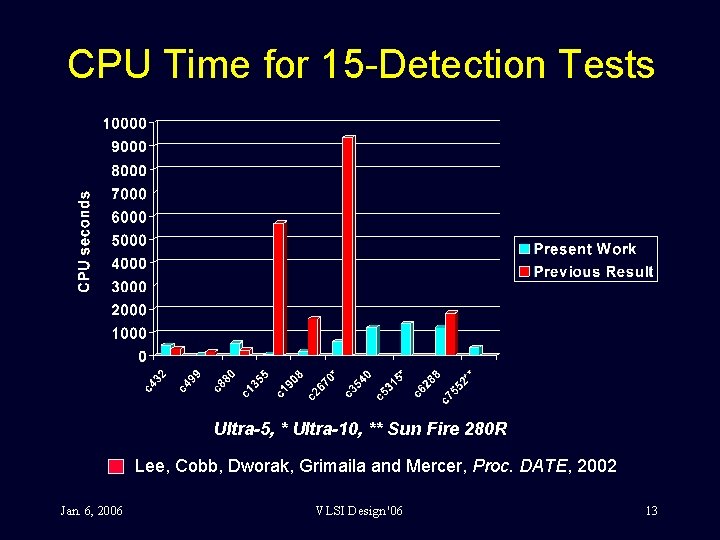

CPU Time for 15 -Detection Tests Ultra-5, * Ultra-10, ** Sun Fire 280 R Lee, Cobb, Dworak, Grimaila and Mercer, Proc. DATE, 2002 Jan. 6, 2006 VLSI Design '06 13

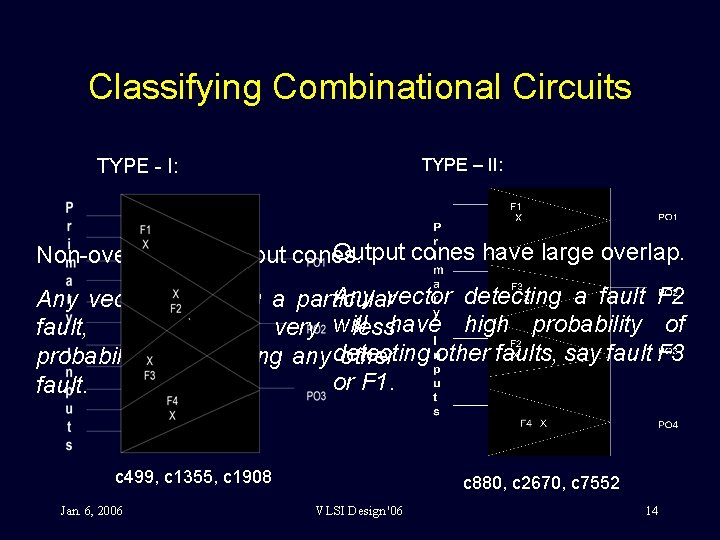

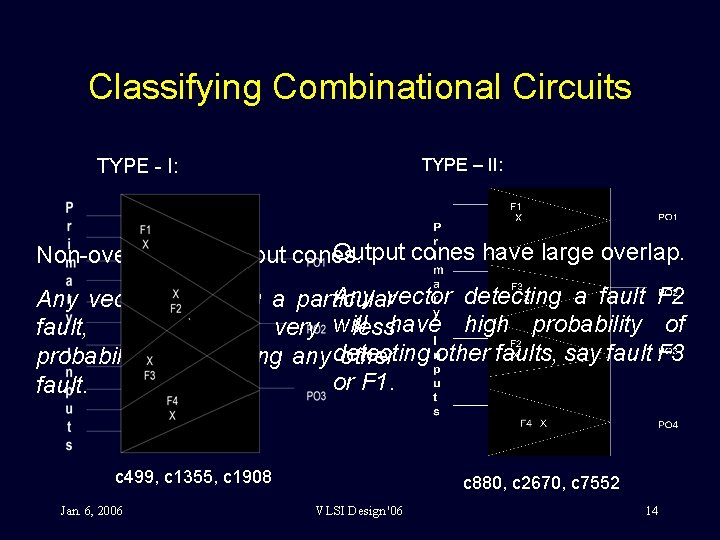

Classifying Combinational Circuits TYPE – II: TYPE - I: Output cones have large overlap. Non-overlapping output cones. Any vector detecting a fault F 2 Any vector detecting a particular fault, will have very will lesshave high probability of other faults, say fault F 3 probability of detecting any detecting other or F 1. fault. c 499, c 1355, c 1908 Jan. 6, 2006 c 880, c 2670, c 7552 VLSI Design '06 14

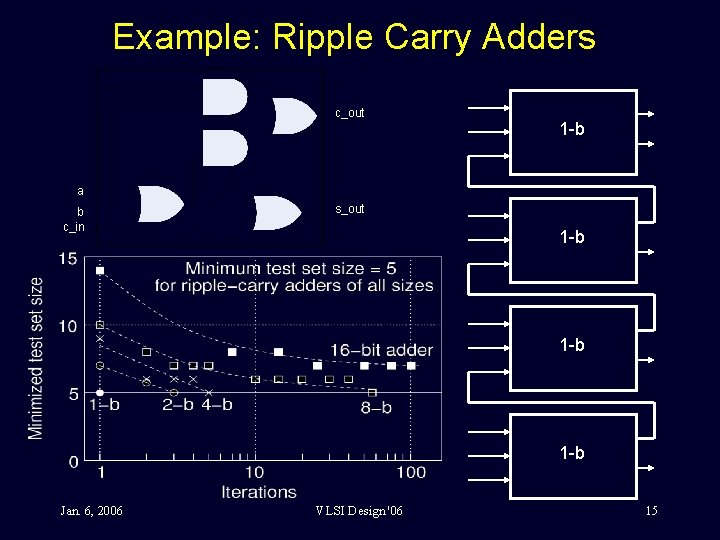

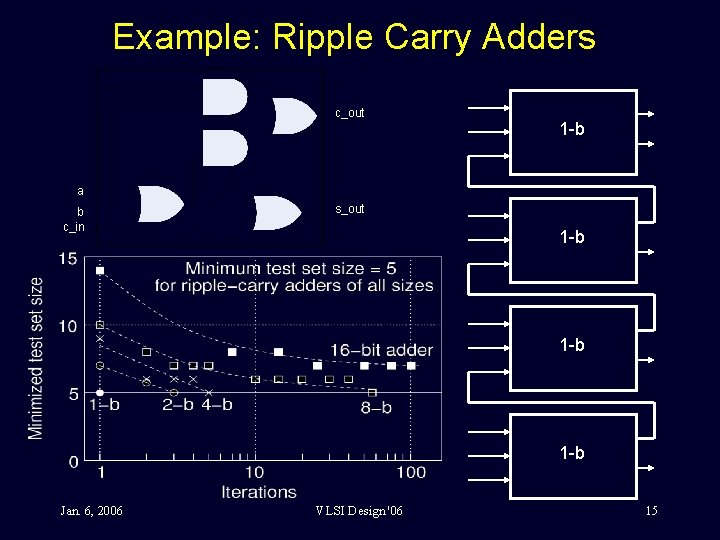

Example: Ripple Carry Adders c_out 1 -b a b c_in s_out 1 -b 1 -b Jan. 6, 2006 VLSI Design '06 15

Conclusion • The theoretical lower bound on the N-detection tests is useful in assessing the minimality of such tests. • ILP is an effective method for minimizing tests, though further improvement is possible. • The formulation of ILP allows custom selection of multiplicity of detection for individual faults. • Contributions of this work: – Theoretical lower bound on N-detection tests. – ILP method for deriving minimal N-detection tests. Jan. 6, 2006 VLSI Design '06 16

Thank You. . . Jan. 6, 2006 VLSI Design '06 17