On Chip Bus Speaker National Taiwan University Adopted

On Chip Bus Speaker: 沈文中 National Taiwan University Adopted from National Taiwan University SOC Course Material SOC Consortium Course Material

Outline q AMBA Bus – Advanced System Bus – Advanced High-performance Bus – Advanced Peripheral Bus q IP Design flow q FPGA design flow SOC Consortium Course Material 2

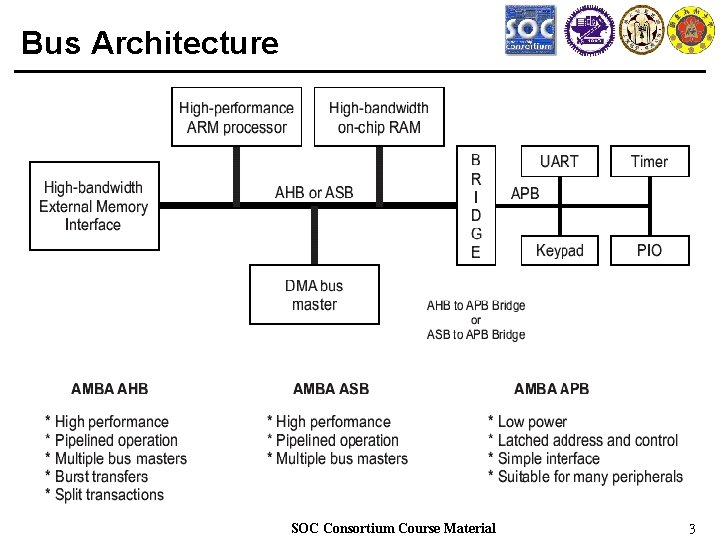

Bus Architecture SOC Consortium Course Material 3

Outline q AMBA Bus – Advanced System Bus • High performance • Pipelined operation • Multiple bus master – Advanced High-performance Bus – Advanced Peripheral Bus q IP Design flow q FPGA design flow SOC Consortium Course Material 4

ASB characters q Negative edge trigger q Tri-state bus – Drawback: More effort used to control timing – Advantage: cost less area SOC Consortium Course Material 5

Outline q AMBA Bus – Advanced System Bus – Advanced High-performance Bus • • • High performance Pipelined operation Multiple bus master Burst transfers Split transactions – Advanced Peripheral Bus q IP Design flow q FPGA design flow SOC Consortium Course Material 6

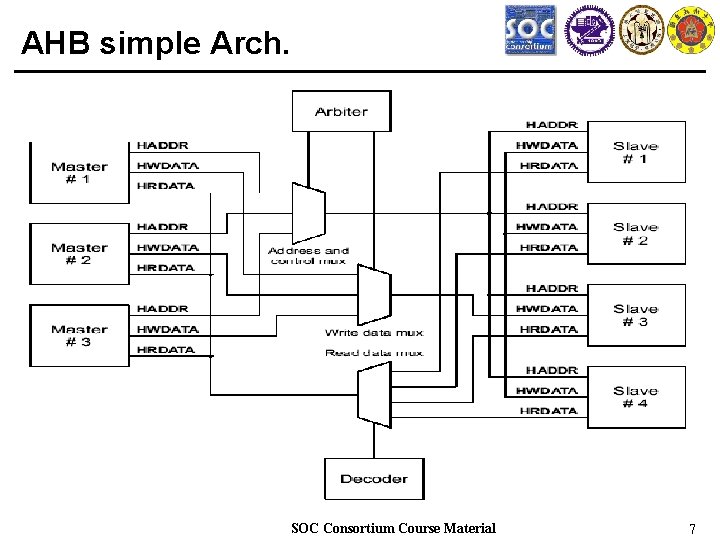

AHB simple Arch. SOC Consortium Course Material 7

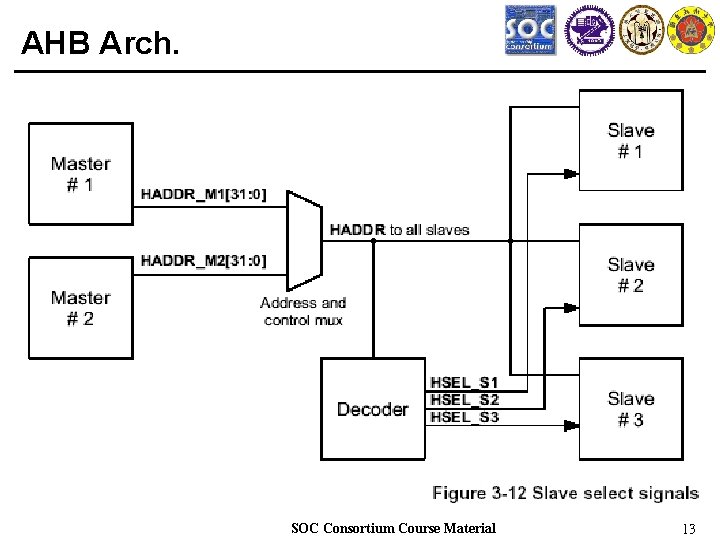

AHB Components q AHB Components – AHB master is able to initiate read and write operations by providing an address and control information. Only one bus master is allowed to actively use the bus at any one time. (max. 16) – AHB slave responds to a read or write operation within a given address-space range. The bus slave signals back to the active master the success, failure or waiting of the data transfer. SOC Consortium Course Material 8

AHB Components(ii) q AHB Components – AHB arbiter ensures that only one bus master at a time is allowed to initiate data transfers. – AHB decoder is used to decode the address of each transfer and provide a select signal for the slave that is involved in the transfer. A single centralized decoder is required in all AHB implementations. SOC Consortium Course Material 9

AHB Signals(i) q AHB Signals can be classified as – Clock (HCLK) – Address and read/write data (HADDR, HRDATA, HWDATA) – Arbitration (HGRANTx, HMASTER, HMASTLOCK, …) – Control signal (HRESETn, …) – Response signal(HREADY, HRESP) SOC Consortium Course Material 10

AHB Signals(ii) q Transfer signals – HCLK • bus clock. All signal timings are related to the rising edge. – HADDR[31: 0] • 32 bits system bus – HWDATA/HRDATA [31: 0] • 32 bits write/read data bus – HWRITE • High: write data • Low: read data – HREADY • Transfer done SOC Consortium Course Material 11

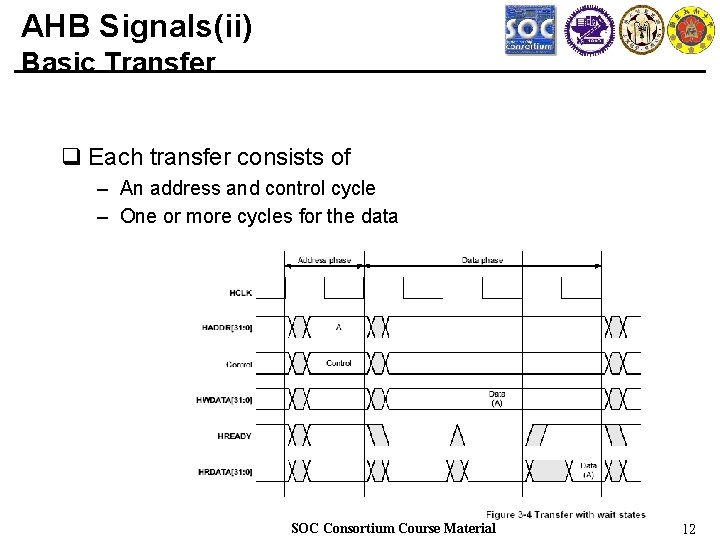

AHB Signals(ii) Basic Transfer q Each transfer consists of – An address and control cycle – One or more cycles for the data SOC Consortium Course Material 12

AHB Arch. SOC Consortium Course Material 13

![AHB Signals(iii) q Control signals – HTRANS[1: 0] • Current transfer type – HBURST[2: AHB Signals(iii) q Control signals – HTRANS[1: 0] • Current transfer type – HBURST[2:](http://slidetodoc.com/presentation_image/20d01ff6329e14b13c545a3bf022aa23/image-14.jpg)

AHB Signals(iii) q Control signals – HTRANS[1: 0] • Current transfer type – HBURST[2: 0] • When sequential transfer, control transfer relation – HSIZE[2: 0] • Control transfer size=2^HSIZE bytes(max=1024 bits) – HPROT[3: 0] • Protection data SOC Consortium Course Material 14

![AHB Signals(iii)-HTRANS q HTRANS[1: 0] – IDLE: master don’t need data to be transfered AHB Signals(iii)-HTRANS q HTRANS[1: 0] – IDLE: master don’t need data to be transfered](http://slidetodoc.com/presentation_image/20d01ff6329e14b13c545a3bf022aa23/image-15.jpg)

AHB Signals(iii)-HTRANS q HTRANS[1: 0] – IDLE: master don’t need data to be transfered – BUSY: allows bus masters to insert IDLE cycles in the middle of bursts of transfers. – NONSEQ: The address and control signals are unrelated to the previous transfer. – SEQ: the address is related to the previous transfer. SOC Consortium Course Material 15

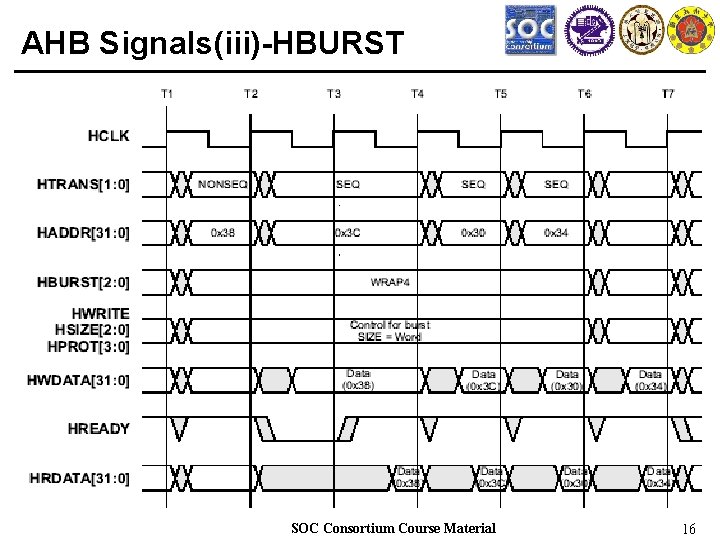

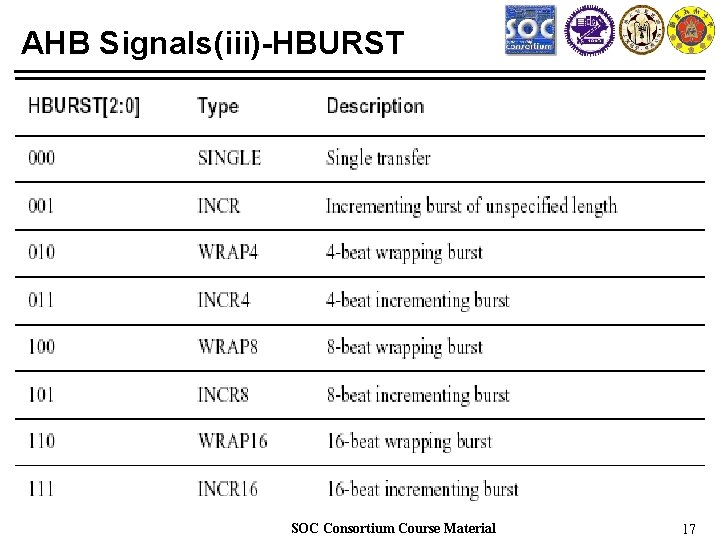

AHB Signals(iii)-HBURST SOC Consortium Course Material 16

AHB Signals(iii)-HBURST SOC Consortium Course Material 17

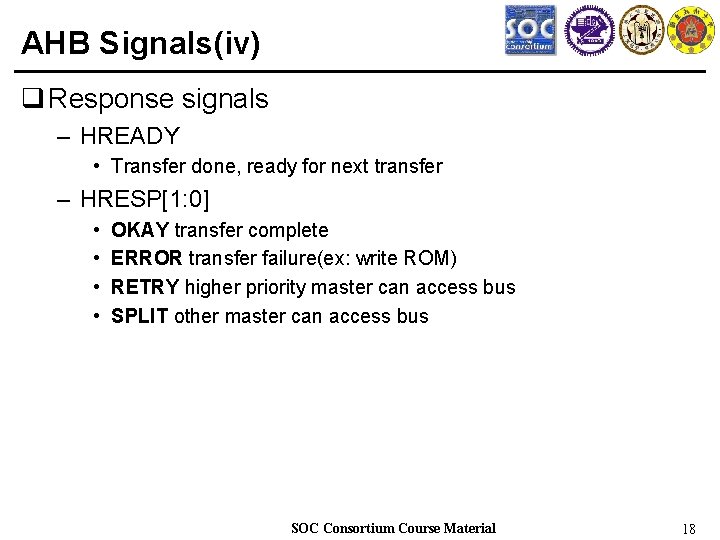

AHB Signals(iv) q Response signals – HREADY • Transfer done, ready for next transfer – HRESP[1: 0] • • OKAY transfer complete ERROR transfer failure(ex: write ROM) RETRY higher priority master can access bus SPLIT other master can access bus SOC Consortium Course Material 18

AHB Signals(v) q Arbiter signals – HGRANTx • Select active bus master – HMASTER[3: 0] • Multiplex signals that sent from master to slave – HMASTLOCK • Locked sequence SOC Consortium Course Material 19

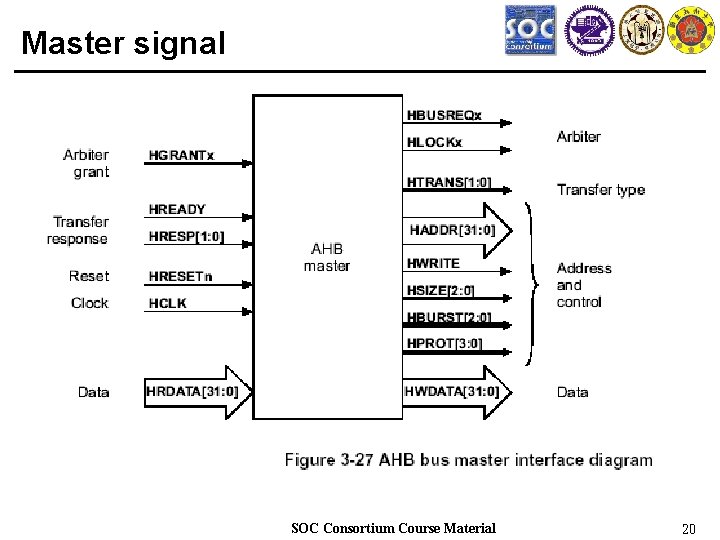

Master signal SOC Consortium Course Material 20

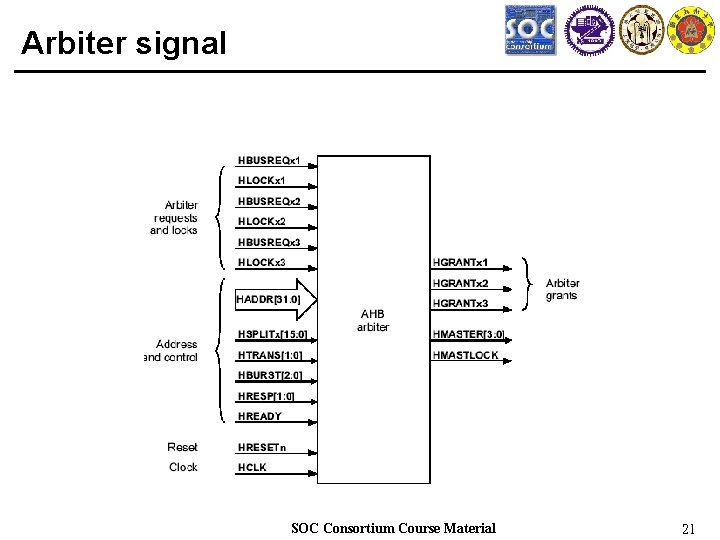

Arbiter signal SOC Consortium Course Material 21

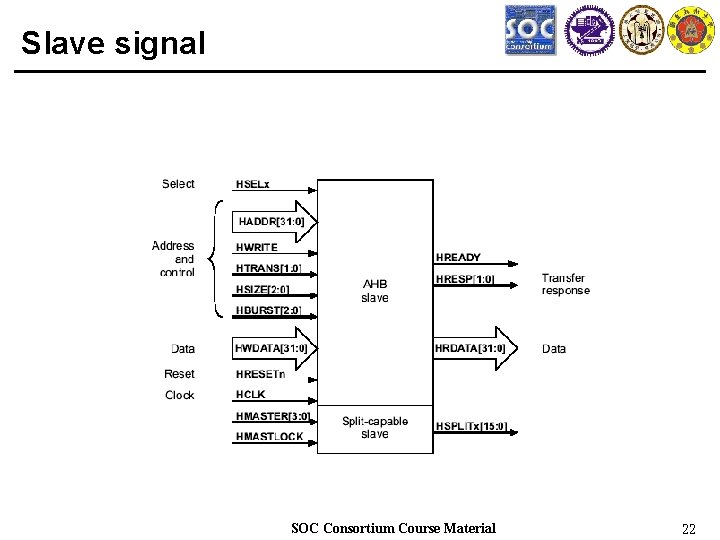

Slave signal SOC Consortium Course Material 22

Outline q AMBA Bus – Advanced System Bus – Advanced High-performance Bus – Advanced Peripheral Bus • • Low power Latched address and control Simple interface Suitable for many peripherals q IP Design flow q FPGA design flow SOC Consortium Course Material 23

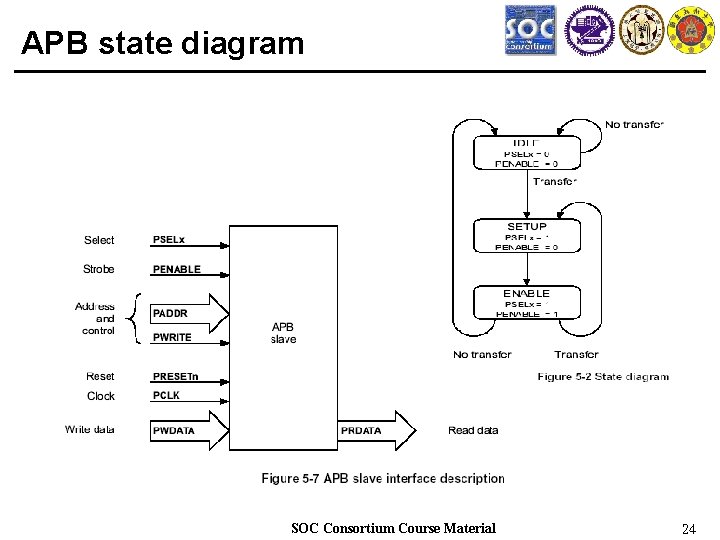

APB state diagram SOC Consortium Course Material 24

APB signals q APB character – Always two cycle transfer – No wait cycle and response signal q APB signals – PCLK Bus clock,rising edge is used to time all transfers. – PRESETn APB reset。active Low. SOC Consortium Course Material 25

![APB signals q PADDR[31: 0] APB address bus. q PSELx Indicates that the slave APB signals q PADDR[31: 0] APB address bus. q PSELx Indicates that the slave](http://slidetodoc.com/presentation_image/20d01ff6329e14b13c545a3bf022aa23/image-26.jpg)

APB signals q PADDR[31: 0] APB address bus. q PSELx Indicates that the slave device is selected. There is a PSELx signal for each slave. q PENABLE Indicates the second cycle of an APB transfer. q PWRITE Transfer direction. High for write access, Low for read access. q PRDATA Read data bus q PWDATA Write data bus SOC Consortium Course Material 26

Outline q AMBA Bus – Advanced System Bus – Advanced High-performance Bus – Advanced Peripheral Bus q IP Design flow – Memory definition – IP design-SW – IP design-HW q FPGA design flow SOC Consortium Course Material 27

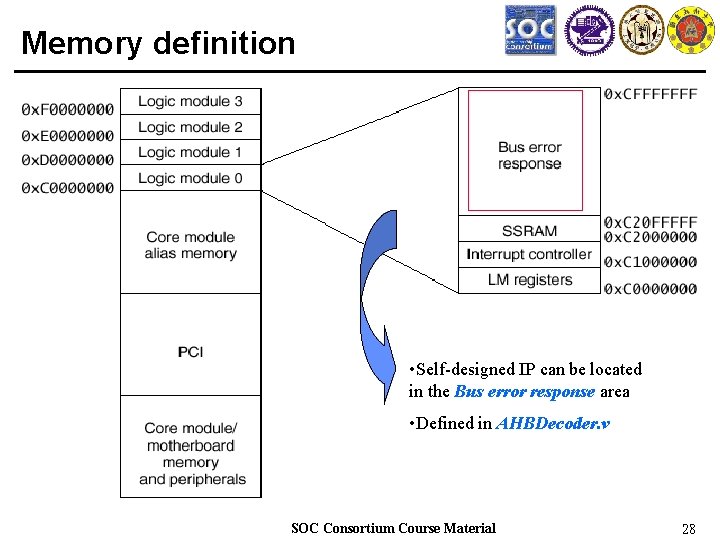

Memory definition • Self-designed IP can be located in the Bus error response area • Defined in AHBDecoder. v SOC Consortium Course Material 28

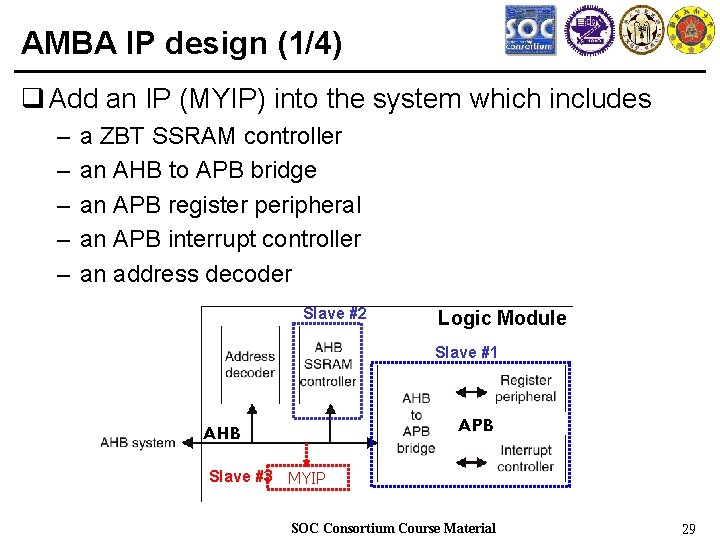

AMBA IP design (1/4) q Add an IP (MYIP) into the system which includes – – – a ZBT SSRAM controller an AHB to APB bridge an APB register peripheral an APB interrupt controller an address decoder Slave #2 Logic Module Slave #1 APB AHB Slave #3 MYIP SOC Consortium Course Material 29

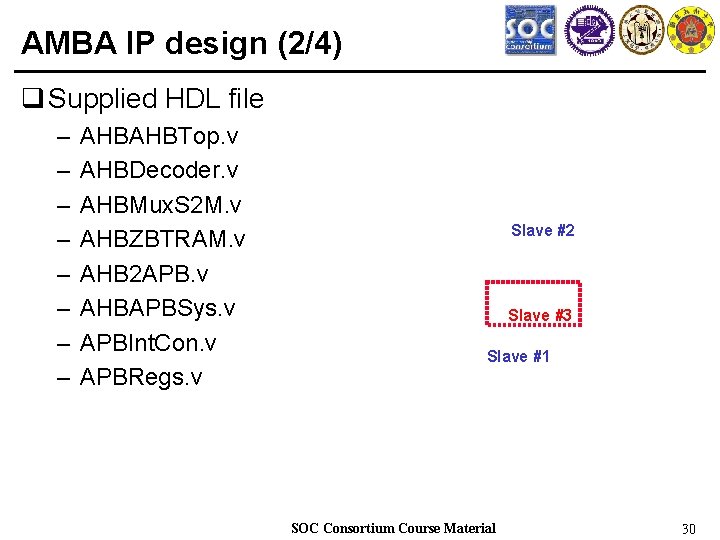

AMBA IP design (2/4) q Supplied HDL file – – – – AHBAHBTop. v AHBDecoder. v AHBMux. S 2 M. v AHBZBTRAM. v AHB 2 APB. v AHBAPBSys. v APBInt. Con. v APBRegs. v Slave #2 Slave #3 Slave #1 SOC Consortium Course Material 30

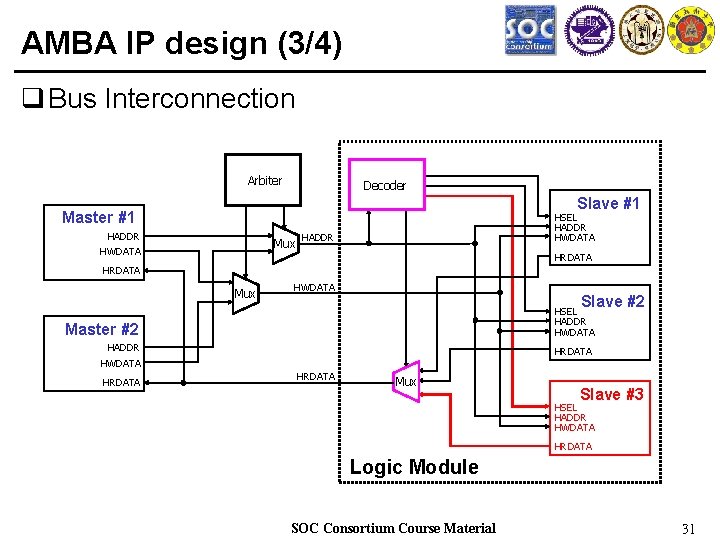

AMBA IP design (3/4) q Bus Interconnection Arbiter Decoder Slave #1 Master #1 HADDR HWDATA Mux HSEL HADDR HWDATA HADDR HRDATA Mux HWDATA Slave #2 Master #2 HSEL HADDR HWDATA HADDR HRDATA HWDATA HRDATA Mux Slave #3 HSEL HADDR HWDATA HRDATA Logic Module SOC Consortium Course Material 31

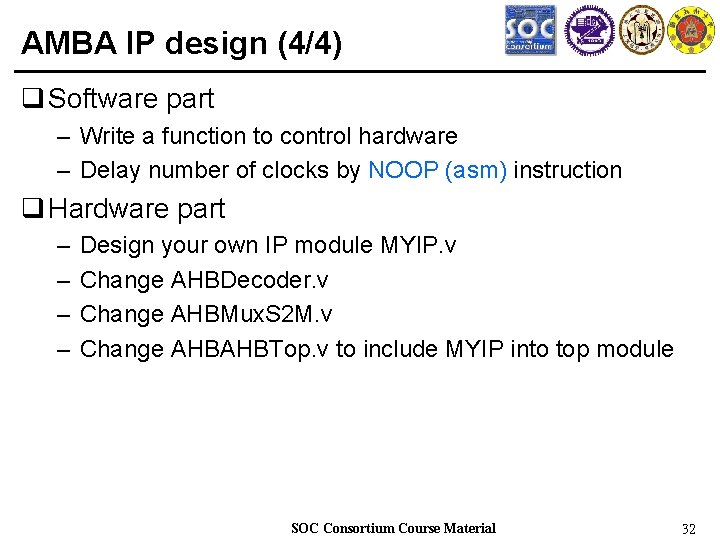

AMBA IP design (4/4) q Software part – Write a function to control hardware – Delay number of clocks by NOOP (asm) instruction q Hardware part – – Design your own IP module MYIP. v Change AHBDecoder. v Change AHBMux. S 2 M. v Change AHBAHBTop. v to include MYIP into top module SOC Consortium Course Material 32

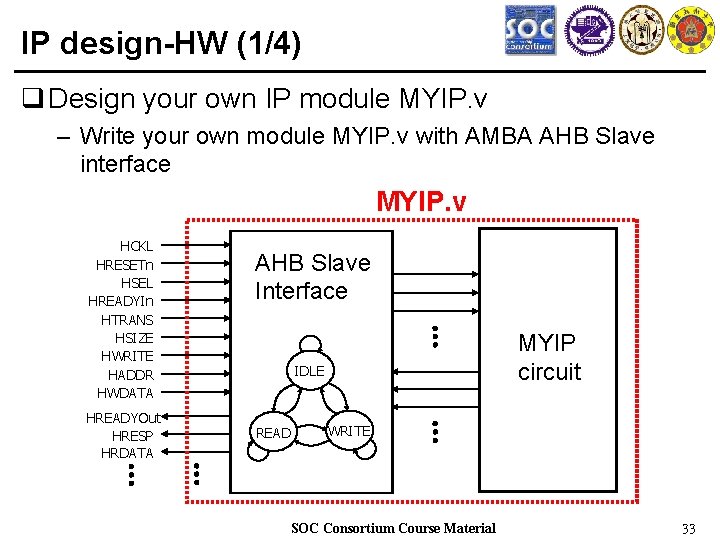

IP design-HW (1/4) q Design your own IP module MYIP. v – Write your own module MYIP. v with AMBA AHB Slave interface MYIP. v HCKL HRESETn HSEL HREADYIn HTRANS HSIZE HWRITE HADDR HWDATA HREADYOut HRESP HRDATA AHB Slave Interface MYIP circuit IDLE READ WRITE SOC Consortium Course Material 33

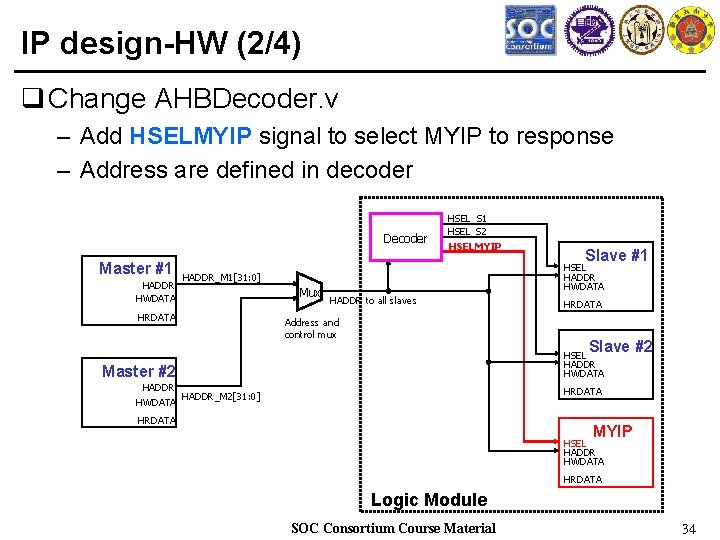

IP design-HW (2/4) q Change AHBDecoder. v – Add HSELMYIP signal to select MYIP to response – Address are defined in decoder Decoder Master #1 HADDR HWDATA HSEL_S 1 HSEL_S 2 HSELMYIP HADDR_M 1[31: 0] HRDATA Mux Slave #1 HSEL HADDR HWDATA HADDR to all slaves Address and control mux HRDATA Slave #2 HSEL HADDR HWDATA Master #2 HADDR_M 2[31: 0] HWDATA HRDATA MYIP HSEL HADDR HWDATA HRDATA Logic Module SOC Consortium Course Material 34

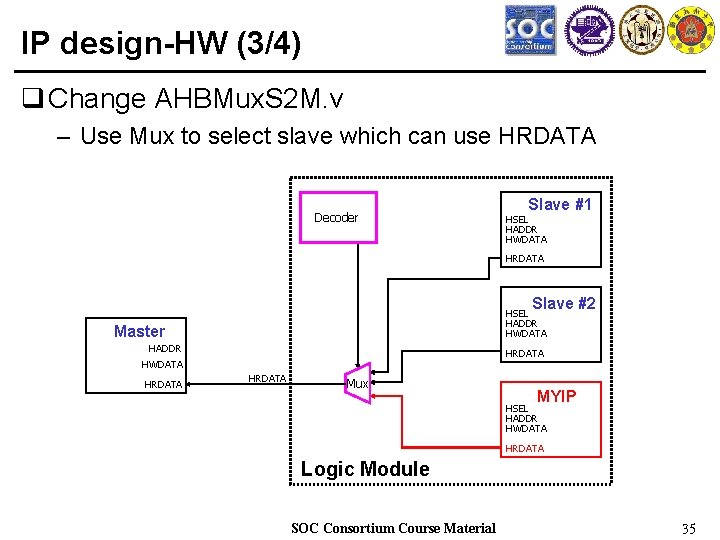

IP design-HW (3/4) q Change AHBMux. S 2 M. v – Use Mux to select slave which can use HRDATA Decoder Slave #1 HSEL HADDR HWDATA HRDATA Slave #2 HSEL HADDR HWDATA Master HADDR HRDATA HWDATA HRDATA Mux MYIP HSEL HADDR HWDATA HRDATA Logic Module SOC Consortium Course Material 35

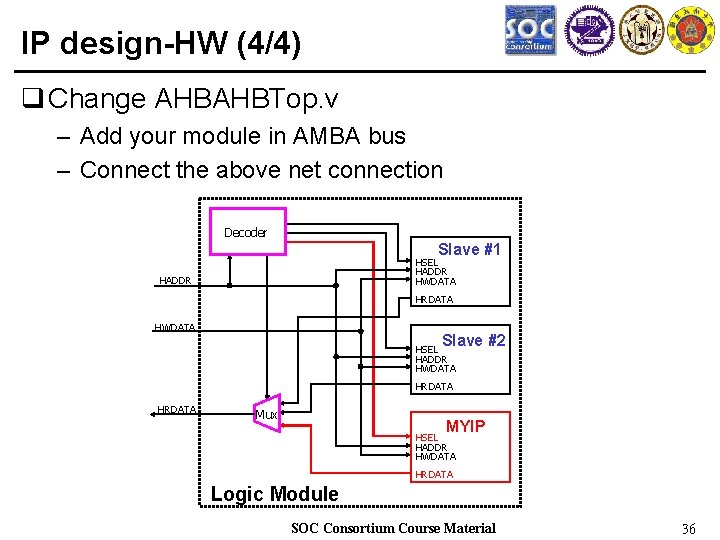

IP design-HW (4/4) q Change AHBAHBTop. v – Add your module in AMBA bus – Connect the above net connection Decoder Slave #1 HSEL HADDR HWDATA HADDR HRDATA HWDATA Slave #2 HSEL HADDR HWDATA HRDATA Mux MYIP HSEL HADDR HWDATA HRDATA Logic Module SOC Consortium Course Material 36

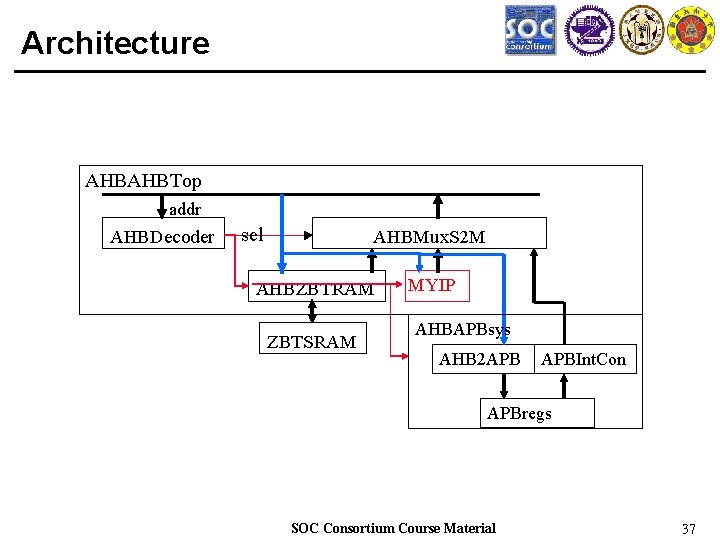

Architecture AHBAHBTop addr AHBDecoder sel AHBMux. S 2 M AHBZBTRAM ZBTSRAM MYIP AHBAPBsys AHB 2 APB APBInt. Con APBregs SOC Consortium Course Material 37

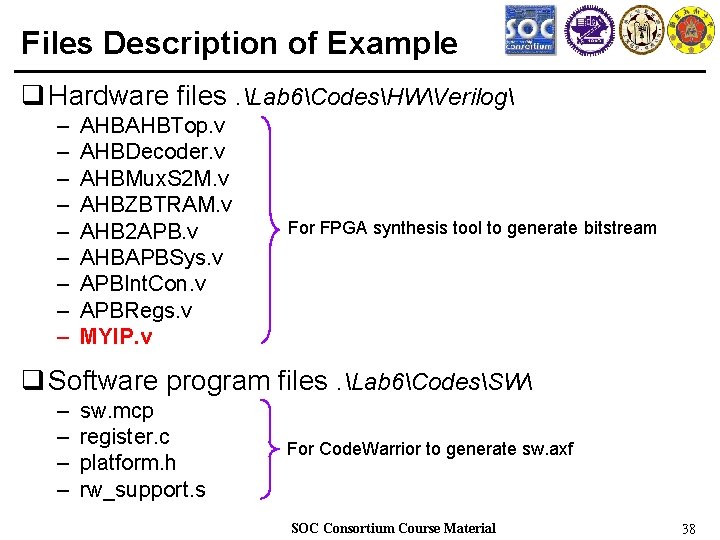

Files Description of Example q Hardware files. Lab 6CodesHWVerilog – – – – – AHBAHBTop. v AHBDecoder. v AHBMux. S 2 M. v AHBZBTRAM. v AHB 2 APB. v AHBAPBSys. v APBInt. Con. v APBRegs. v MYIP. v For FPGA synthesis tool to generate bitstream q Software program files. Lab 6CodesSW – – sw. mcp register. c platform. h rw_support. s For Code. Warrior to generate sw. axf SOC Consortium Course Material 38

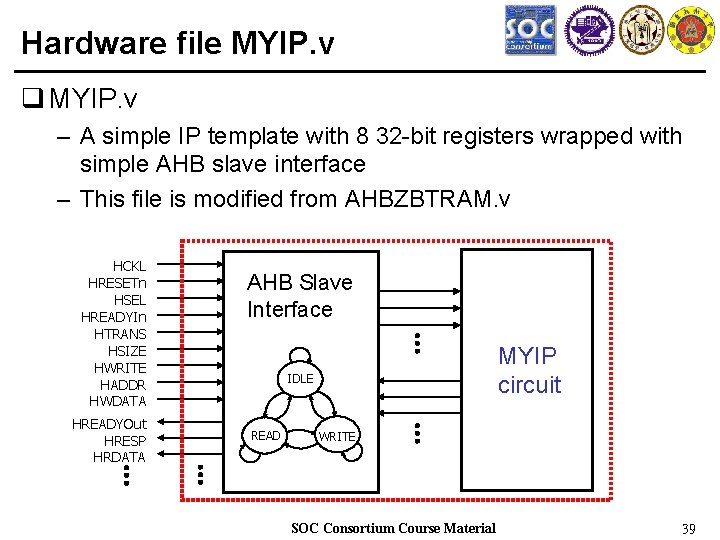

Hardware file MYIP. v q MYIP. v – A simple IP template with 8 32 -bit registers wrapped with simple AHB slave interface – This file is modified from AHBZBTRAM. v HCKL HRESETn HSEL HREADYIn HTRANS HSIZE HWRITE HADDR HWDATA HREADYOut HRESP HRDATA AHB Slave Interface MYIP circuit IDLE READ WRITE SOC Consortium Course Material 39

Outline q AMBA Bus – Advanced System Bus – Advanced High-performance Bus – Advanced Peripheral Bus q IP Design flow q FPGA design flow – Compile flow & Download flow (Xilinx) – Compile flow & Download flow (Altera) SOC Consortium Course Material 40

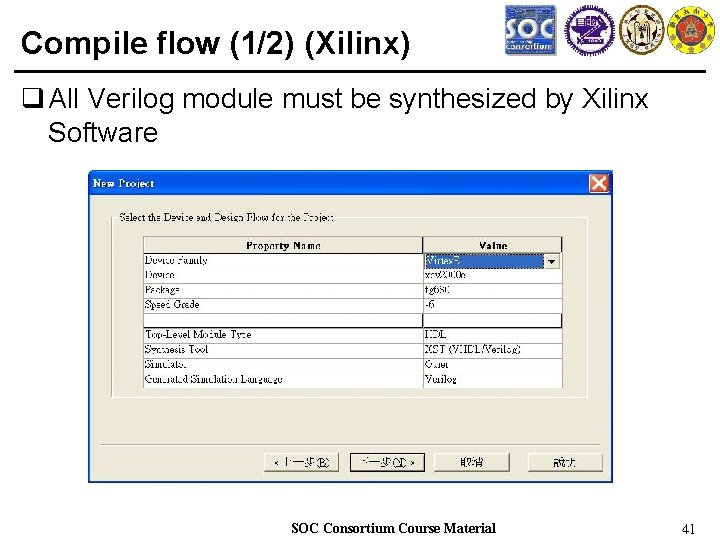

Compile flow (1/2) (Xilinx) q All Verilog module must be synthesized by Xilinx Software SOC Consortium Course Material 41

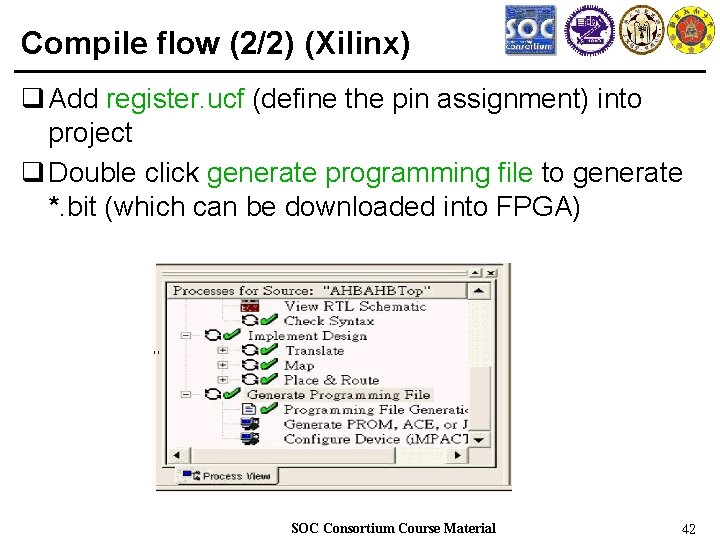

Compile flow (2/2) (Xilinx) q Add register. ucf (define the pin assignment) into project q Double click generate programming file to generate *. bit (which can be downloaded into FPGA) SOC Consortium Course Material 42

Download flow (Xilinx) q Connect config link q Connect Multi-ICE to Logic Module q Power on q Use progcards. exe to download register. bit file q Remove config link q Power off SOC Consortium Course Material 43

Outline q AMBA Bus – Advanced System Bus – Advanced High-performance Bus – Advanced Peripheral Bus q IP Design flow q FPGA design flow – Compile flow & Download flow (Xilinx) – Compile flow & Download flow (Altera) SOC Consortium Course Material 44

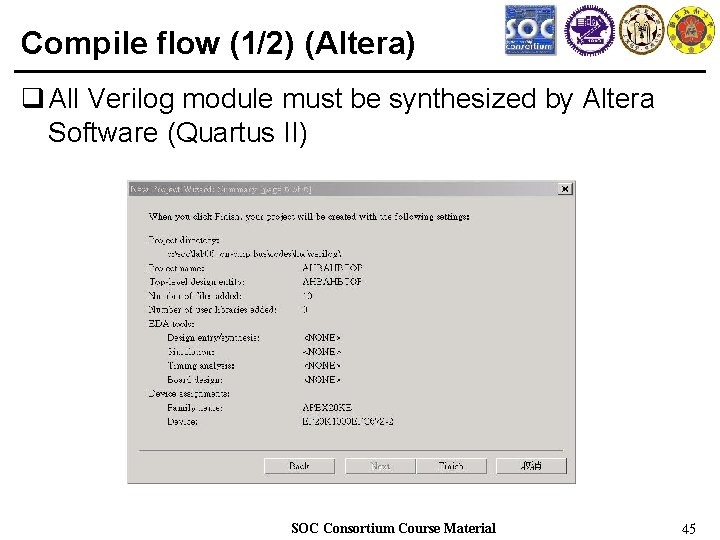

Compile flow (1/2) (Altera) q All Verilog module must be synthesized by Altera Software (Quartus II) SOC Consortium Course Material 45

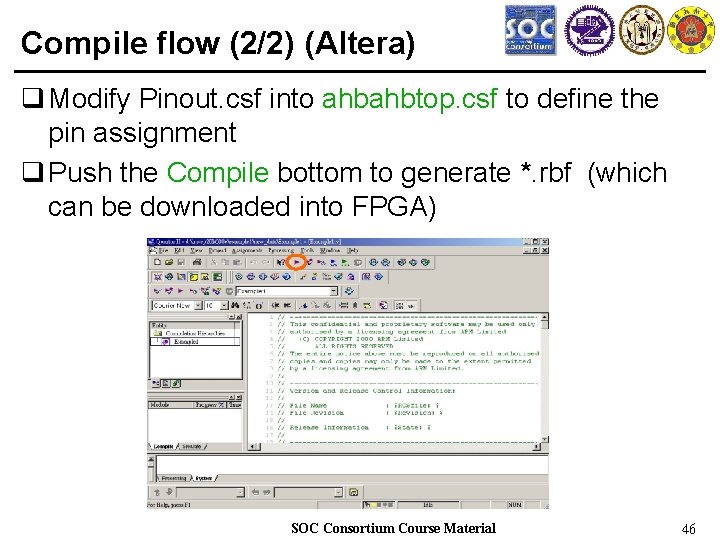

Compile flow (2/2) (Altera) q Modify Pinout. csf into ahbahbtop. csf to define the pin assignment q Push the Compile bottom to generate *. rbf (which can be downloaded into FPGA) SOC Consortium Course Material 46

Download flow (Altera) q Use the text-editor to produce a. brd file (configuration file for progcards. exe) q Power off q Connect Multi-ICE to Logic Module q Set the LM in Config Mode q Power on q Auto-config again in the Multi. ICE Server program q Use progcards. exe to download bitstream SOC Consortium Course Material 47

- Slides: 47