On Applying ELAN Strategies in Simulating Processors over

![Overview • Applying rewriting techniques in hardware design [Arvind et al] – specification of Overview • Applying rewriting techniques in hardware design [Arvind et al] – specification of](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-2.jpg)

![Rewriting l => r if C One-step rewriting relation: t[s l ] t[r ] Rewriting l => r if C One-step rewriting relation: t[s l ] t[r ]](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-6.jpg)

![Specifying Processors Jz(r 1, r 2) • Defining instructions as rules [Jz] Sys(m, Proc(ia, Specifying Processors Jz(r 1, r 2) • Defining instructions as rules [Jz] Sys(m, Proc(ia,](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-10.jpg)

![Specifying Processors Set of rewrite rules RB [Loadc] Sys(m, Proc(ia, rf, prog)) => Sys(m, Specifying Processors Set of rewrite rules RB [Loadc] Sys(m, Proc(ia, rf, prog)) => Sys(m,](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-11.jpg)

![Specifying Processors Speculative Processor [Ps. Op] Sys(m, Proc(ia, rf, ITB(ia 1, k, t(k)|-Op(v, v Specifying Processors Speculative Processor [Ps. Op] Sys(m, Proc(ia, rf, ITB(ia 1, k, t(k)|-Op(v, v](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-16.jpg)

![Specifying Processors Speculative Processor [Ps. Jump. Correct. Spec] Sys(m, Proc(ia, rf, ITB(ia 1, k, Specifying Processors Speculative Processor [Ps. Jump. Correct. Spec] Sys(m, Proc(ia, rf, ITB(ia 1, k,](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-17.jpg)

- Slides: 36

On Applying ELAN Strategies in Simulating Processors over Simple Architectures R. M. Neto 1, M. Ayala-Rincón 1, R. P. Jacobi 1, C. Llanos 1, R. Hartenstein 2 1 Instituto de Ciências Exatas Universidade de Brasília, Brasília D. F. Brasil 2 Fachbereich Informatik Universität Kaiserslautern, Kaiserslautern Germany WRS’ 02 Copenhagen 21 -07 -2002 Simulating Processors with ELAN(WRS’ 02) 1

![Overview Applying rewriting techniques in hardware design Arvind et al specification of Overview • Applying rewriting techniques in hardware design [Arvind et al] – specification of](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-2.jpg)

Overview • Applying rewriting techniques in hardware design [Arvind et al] – specification of correct processors; formulation of simple logical digital circuits; cache protocols over memory systems – Correct specification of new features to processors • Reorder buffers - ROB • Speculative execution Simulating Processors with ELAN(WRS’ 02) 2

Overview • In Arvind’s approach rewriting is neither applied for simulation nor for verification. Proposal Translate to Verilog! • Simulation and performance estimations using a rewriting-logic environment – logic plus rewriting allows for: • Discrimination of architectural components • Execution of assembly programs descriptions Simulating Processors with ELAN(WRS’ 02) 3

Overview • Once correctness is proved, simulations allow for a statistical analysis of different implementations. Simulating Processors with ELAN(WRS’ 02) 4

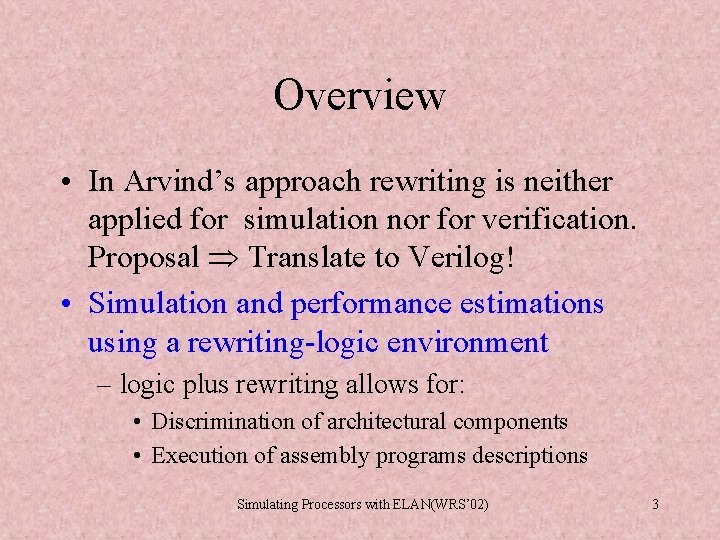

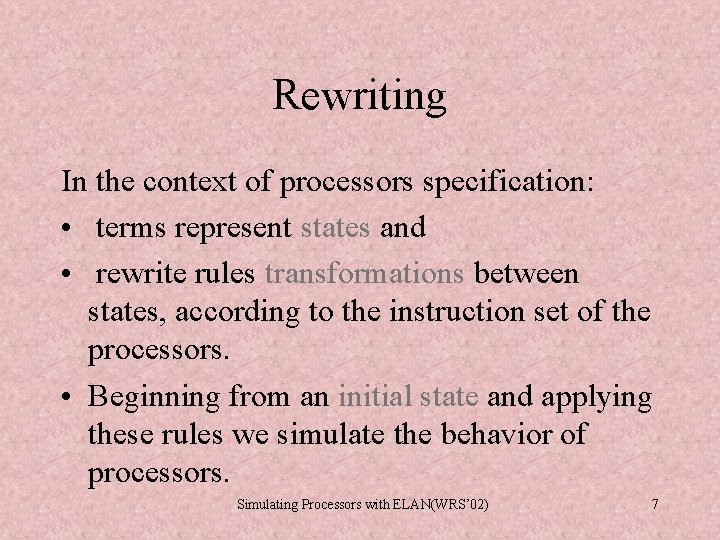

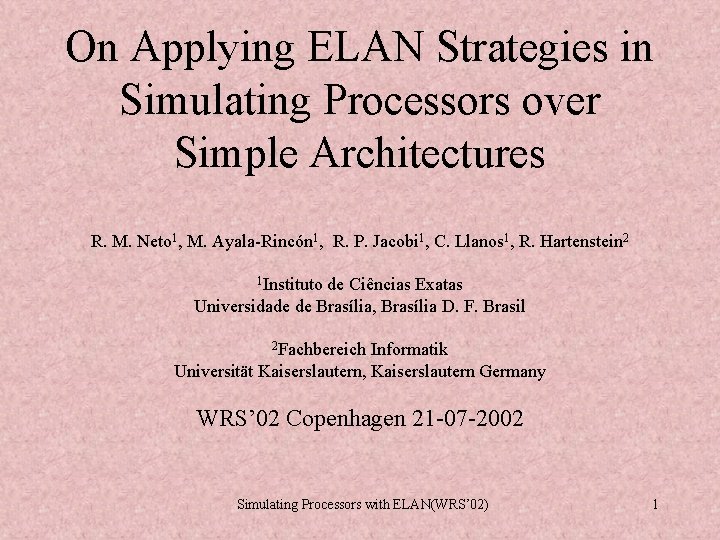

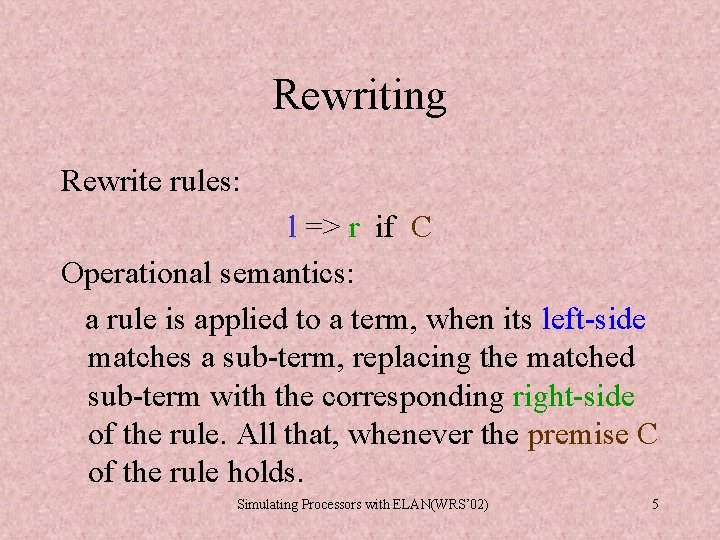

Rewriting Rewrite rules: l => r if C Operational semantics: a rule is applied to a term, when its left-side matches a sub-term, replacing the matched sub-term with the corresponding right-side of the rule. All that, whenever the premise C of the rule holds. Simulating Processors with ELAN(WRS’ 02) 5

![Rewriting l r if C Onestep rewriting relation ts l tr Rewriting l => r if C One-step rewriting relation: t[s l ] t[r ]](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-6.jpg)

Rewriting l => r if C One-step rewriting relation: t[s l ] t[r ] whenever C Important rewriting properties: termination and confluence Notation: * “ zero or more steps of rewriting” relation; s “normal or canonical form” of s; ! Simulating rewriting to a. ELAN(WRS’ 02) normal form; Processors with 6

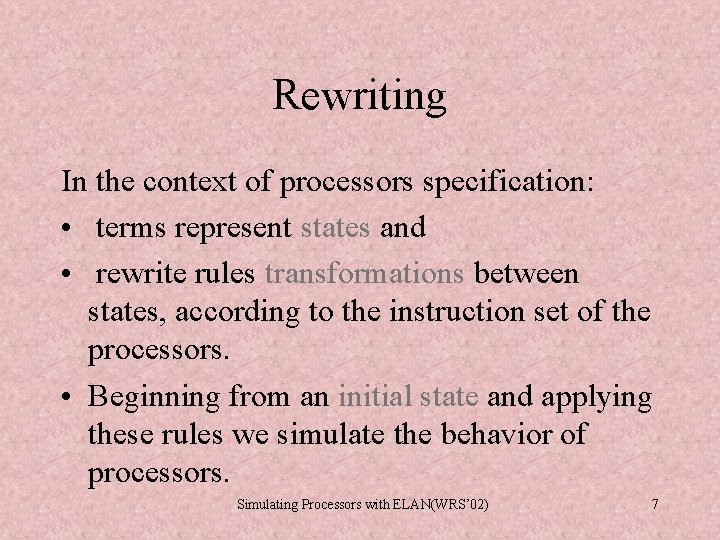

Rewriting In the context of processors specification: • terms represent states and • rewrite rules transformations between states, according to the instruction set of the processors. • Beginning from an initial state and applying these rules we simulate the behavior of processors. Simulating Processors with ELAN(WRS’ 02) 7

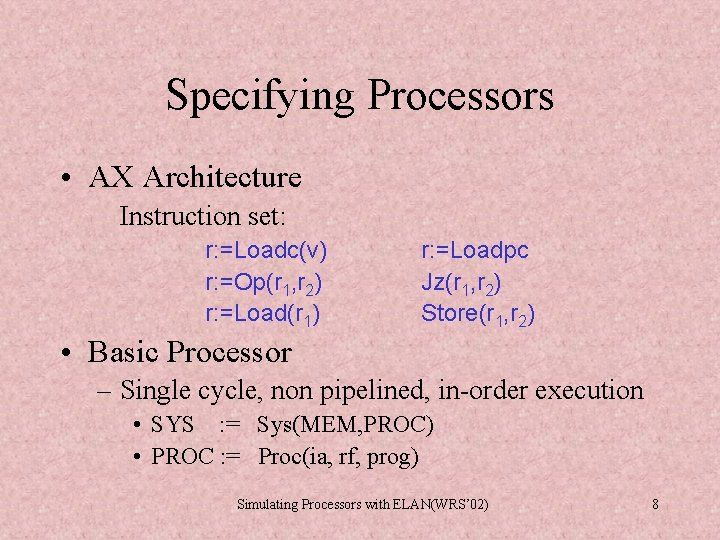

Specifying Processors • AX Architecture Instruction set: r: =Loadc(v) r: =Op(r 1, r 2) r: =Load(r 1) r: =Loadpc Jz(r 1, r 2) Store(r 1, r 2) • Basic Processor – Single cycle, non pipelined, in-order execution • SYS : = Sys(MEM, PROC) • PROC : = Proc(ia, rf, prog) Simulating Processors with ELAN(WRS’ 02) 8

Specifying Processors Basic Processor SYS(mem, Proc) Data Mem +1 PC PROC(ia, rf, prog) Int Mem Register File Simulating Processors with ELAN(WRS’ 02) ALU 9

![Specifying Processors Jzr 1 r 2 Defining instructions as rules Jz Sysm Procia Specifying Processors Jz(r 1, r 2) • Defining instructions as rules [Jz] Sys(m, Proc(ia,](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-10.jpg)

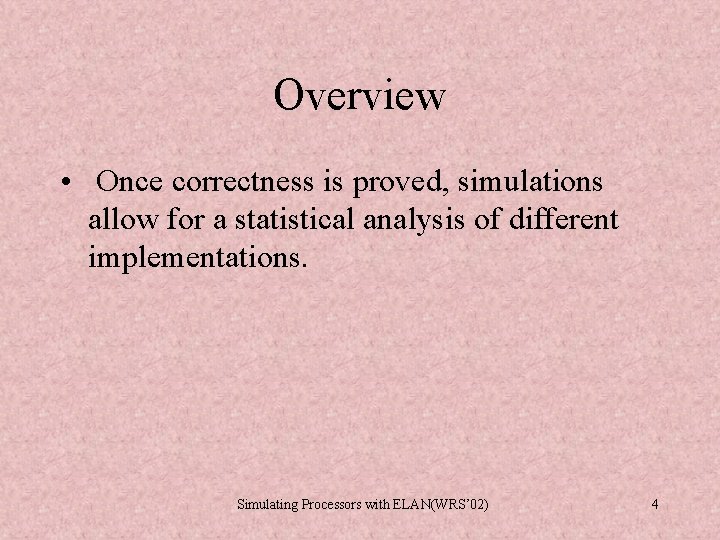

Specifying Processors Jz(r 1, r 2) • Defining instructions as rules [Jz] Sys(m, Proc(ia, rf, prog)) => Sys(m, Proc(nia, rf, prog)) ia nia where inst. Ia: =() selectinst(prog, ia) if isinst. Jz(inst. Ia) where r 1: =()reg 1 of. Jz(inst. Ia) where r 2: =()reg 2 of. Jz(inst. Ia) choose try where nia: =()ia+1 if valueof. Reg(r 1, rf)!=0 try where nia: =()valueof. Reg(r 2, rf) if valueof. Reg(r 1, rf)==0 end Simulating Processors with ELAN(WRS’ 02) 10 end

![Specifying Processors Set of rewrite rules RB Loadc Sysm Procia rf prog Sysm Specifying Processors Set of rewrite rules RB [Loadc] Sys(m, Proc(ia, rf, prog)) => Sys(m,](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-11.jpg)

Specifying Processors Set of rewrite rules RB [Loadc] Sys(m, Proc(ia, rf, prog)) => Sys(m, Proc(ia+1, insert. RF(rf, r, v), prog)) where inst. Ia : =() selectinst(prog, ia) if isinst. Loadc(inst. Ia) where r : =() nameof. Loadc(inst. Ia) where v : =() valueof. Loadc(inst. Ia) end [Loadpc] Sys(m, Proc(ia, rf, prog)) => Sys(m, Proc(ia+1, insert. RF(rf, r, ia), prog)) where inst. Ia : =() selectinst(prog, ia) if isinst. Loadpc(inst. Ia) where r : =() nameof. Loadpc(inst. Ia) end [Op] Sys(m, Proc(ia, rf, prog)) => Sys(m, Proc(ia+1, insert. RF(rf, r, v), prog)) where inst. Ia : =() selectinst(prog, ia) if isinst. Op(inst. Ia) where r 1 : =() reg 1 of. Op(inst. Ia) where r 2 : =() reg 2 of. Op(inst. Ia) where r : =() nameof. Op(inst. Ia) where v : =() valueof. Op(r 1, r 2, rf) end [Jz] Sys(m, Proc(ia, rf, prog)) => Sys(m, Proc(nia, rf, prog)) where inst. Ia : =() selectinst(prog, ia) if isinst. Jz(inst. Ia) where r 1: =() reg 1 of. Jz(inst. Ia) where r 2: =() reg 2 of. Jz(inst. Ia) choose try where nia: =()ia+1 if valueof. Reg(r 1, rf) != 0 try where nia: =()valueof. Reg(r 2, rf) if valueof. Reg(r 1, rf) == 0 end [Load] Sys(m, Proc(ia, rf, prog)) => Sys(m, Proc(ia+1, insert. RF(rf, r 0, v 0), prog)) where inst : =() selectinst(prog, ia) if isinst. Load(inst) where r 0 : =() nameof. Load(inst) where v 0 : =() get. Mem(inst, rf, m) end [Store] Sys(m, Proc(ia, rf, prog)) => Sys(insert. MEM(m, valueof. Reg(r. A, rf), valueof. Reg(r. B, rf)), Proc(ia+1, rf, prog)) where inst : =() selectinst(prog, ia) if isinst. Store(inst) where r. A : =() nameof. Store. R 1(inst) where r. B : =() nameof. Store. R 2(inst) end Simulating Processors with ELAN(WRS’ 02) 11

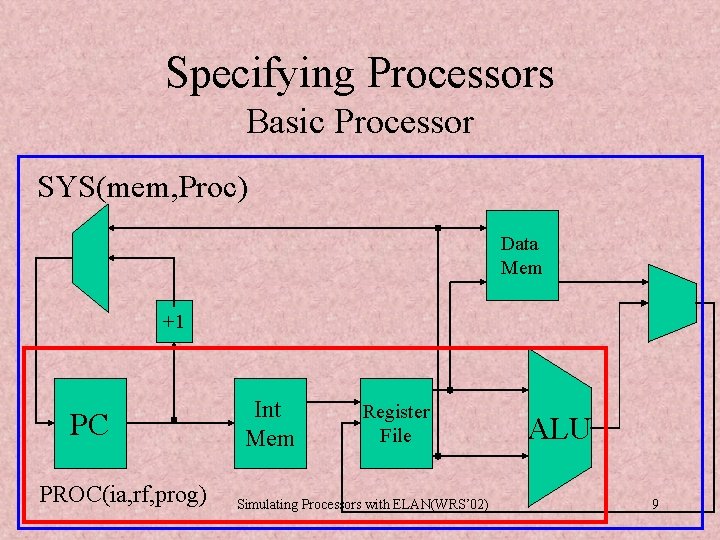

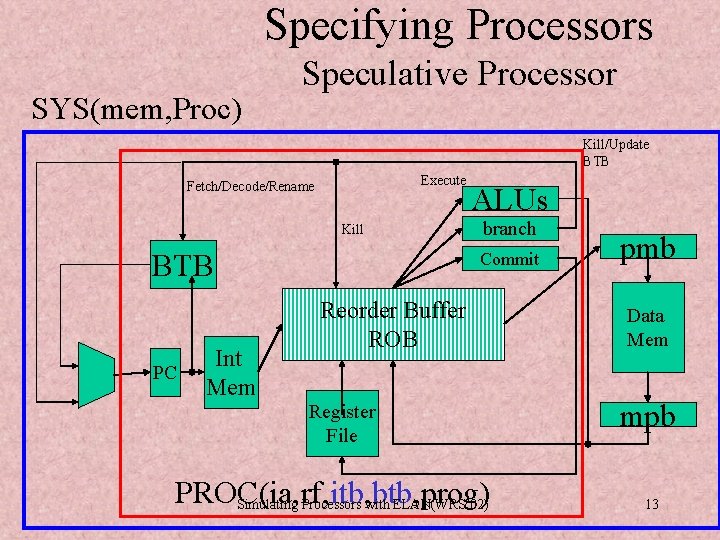

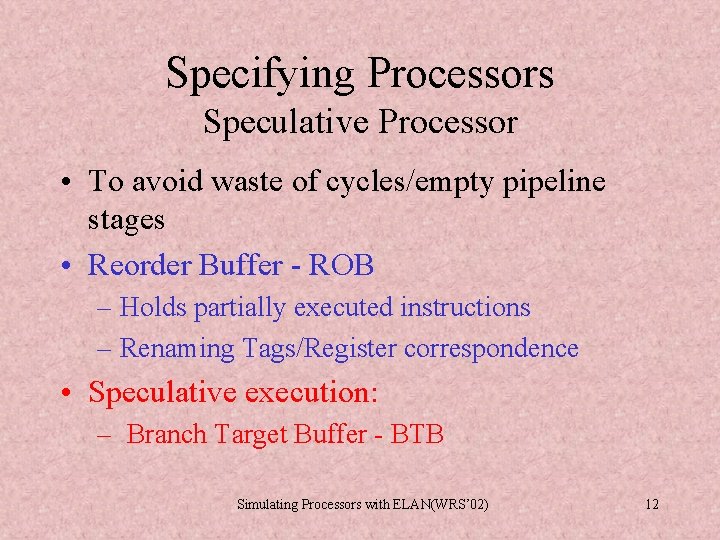

Specifying Processors Speculative Processor • To avoid waste of cycles/empty pipeline stages • Reorder Buffer - ROB – Holds partially executed instructions – Renaming Tags/Register correspondence • Speculative execution: – Branch Target Buffer - BTB Simulating Processors with ELAN(WRS’ 02) 12

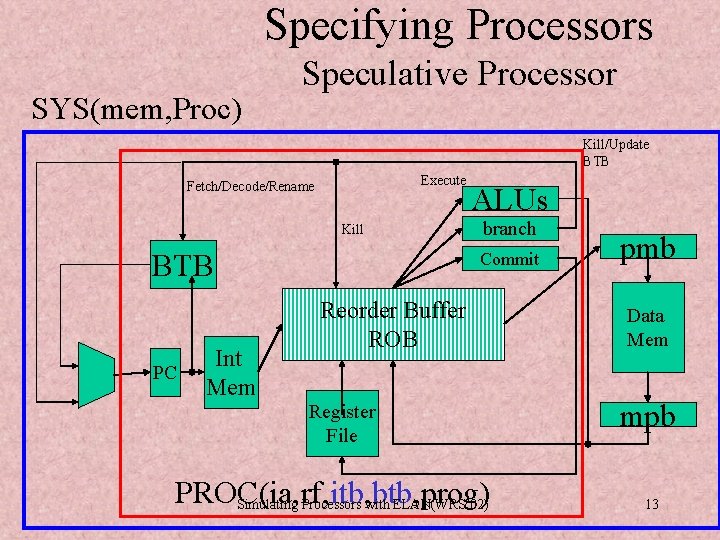

Specifying Processors SYS(mem, Proc) Speculative Processor Kill/Update BTB Execute Fetch/Decode/Rename Kill BTB PC Int Mem ALUs branch Commit Reorder Buffer ROB Register File PROC(ia, rf, itb, btb, prog) Simulating Processors with ELAN(WRS’ 02) pmb Data Mem mpb 13

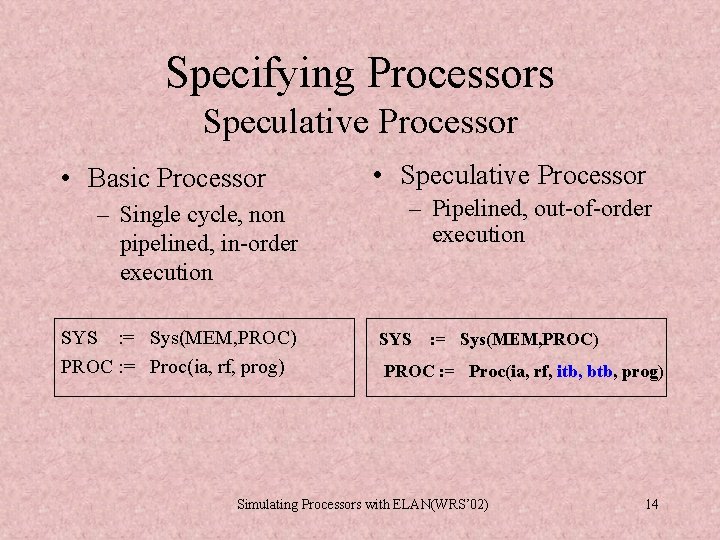

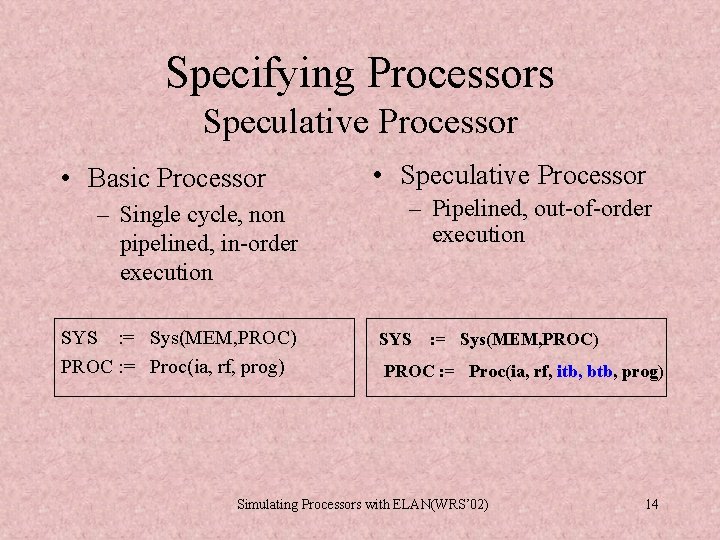

Specifying Processors Speculative Processor • Basic Processor – Single cycle, non pipelined, in-order execution SYS : = Sys(MEM, PROC) PROC : = Proc(ia, rf, prog) • Speculative Processor – Pipelined, out-of-order execution SYS : = Sys(MEM, PROC) PROC : = Proc(ia, rf, itb, btb, prog) Simulating Processors with ELAN(WRS’ 02) 14

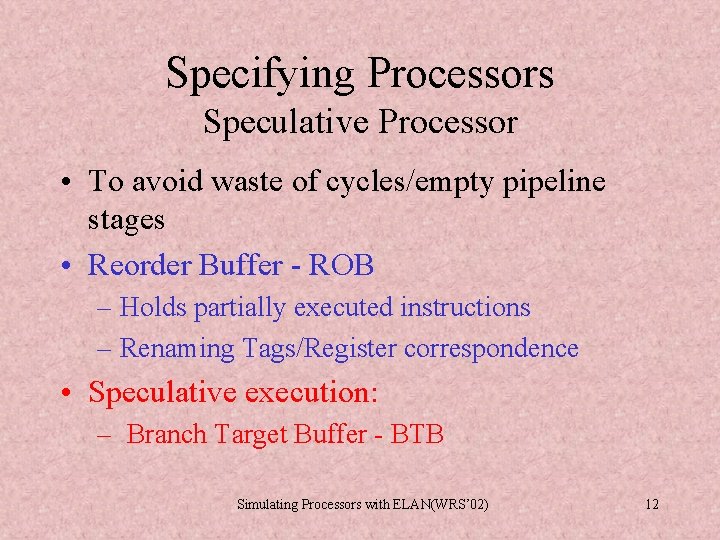

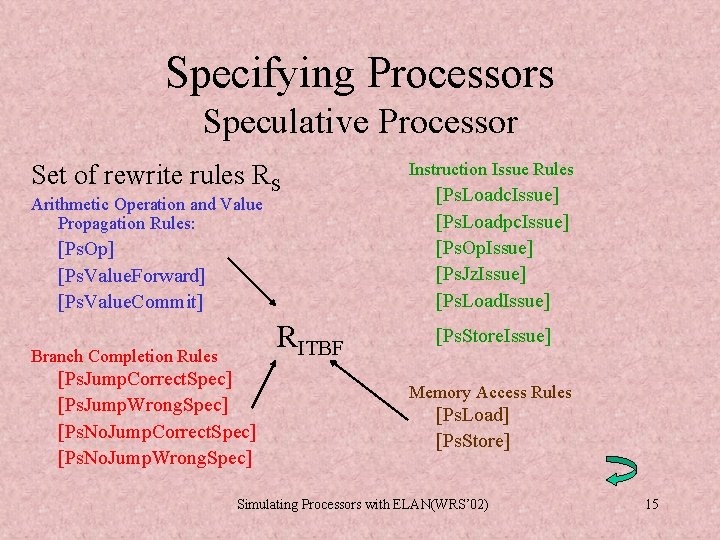

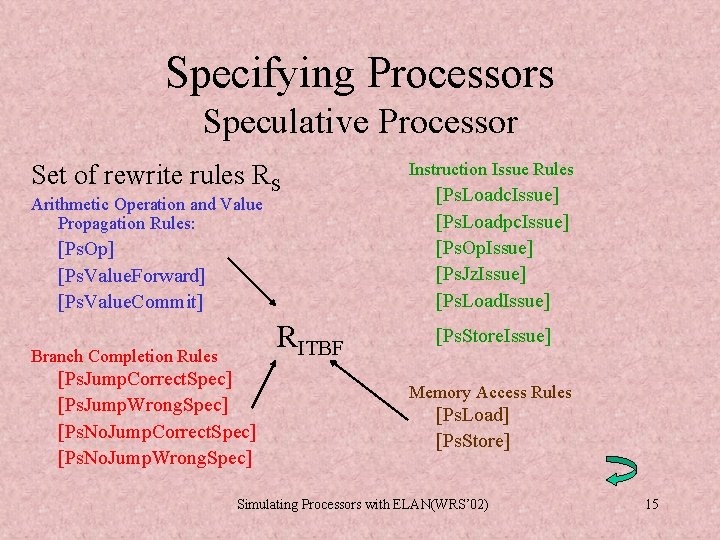

Specifying Processors Speculative Processor Set of rewrite rules RS Arithmetic Operation and Value Propagation Rules: [Ps. Op] [Ps. Value. Forward] [Ps. Value. Commit] RITBF Branch Completion Rules [Ps. Jump. Correct. Spec] [Ps. Jump. Wrong. Spec] [Ps. No. Jump. Correct. Spec] [Ps. No. Jump. Wrong. Spec] Instruction Issue Rules [Ps. Loadc. Issue] [Ps. Loadpc. Issue] [Ps. Op. Issue] [Ps. Jz. Issue] [Ps. Load. Issue] [Ps. Store. Issue] Memory Access Rules [Ps. Load] [Ps. Store] Simulating Processors with ELAN(WRS’ 02) 15

![Specifying Processors Speculative Processor Ps Op Sysm Procia rf ITBia 1 k tkOpv v Specifying Processors Speculative Processor [Ps. Op] Sys(m, Proc(ia, rf, ITB(ia 1, k, t(k)|-Op(v, v](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-16.jpg)

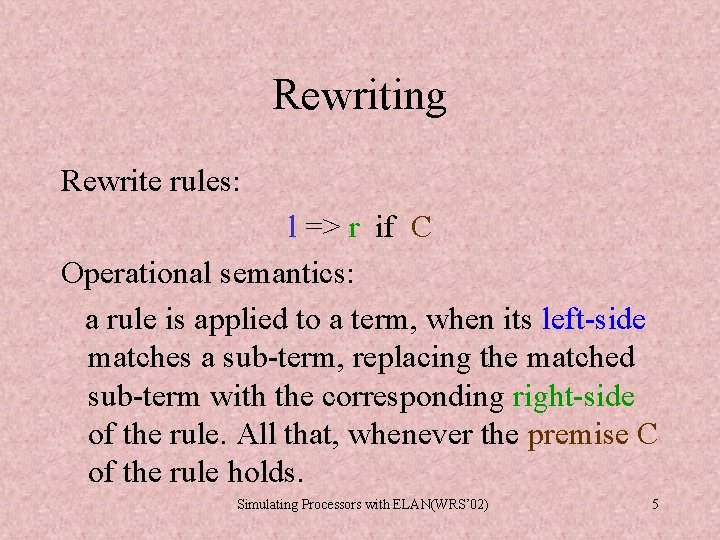

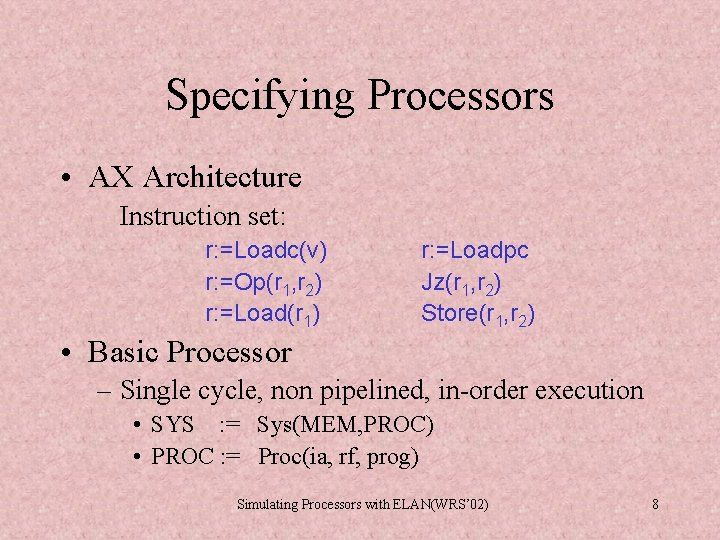

Specifying Processors Speculative Processor [Ps. Op] Sys(m, Proc(ia, rf, ITB(ia 1, k, t(k)|-Op(v, v 1), wf, sf). itbs 2, btb, prog)) => Sys(m, Proc(ia, rf, ITB(ia 1, k, t(k)|-exec. Oponval(v, v 1), wf, sf). itbs 2, btb, prog)) end [Ps. Jz. Issue] Sys(m, Proc(ia, rf, => Sys(m, Proc(pia, rf, ia itbs, btb, prog)) itbs pia ins. End. ITBs(ITB(ia, k, Jz(k 0, k 1), No. Wreg, Spec(pia)), itbs), (k 0, k 1), btb, prog)) where inst. Ia : =() selectinst(prog, ia) if isinst. Jz(inst. Ia) where r 1 : =() reg 1 of. Jz(inst. Ia) where r 2 : =() reg 2 of. Jz(inst. Ia) where k : =() lengthof(itbs)+1 where k 0 : =() searchfor. Last. Tag(r 1, rf, itbs) where k 1: =()searchfor. Last. Tag(r 2, rf, itbs) where pia: =()getbtb(ia, btb) end Simulating Processors with ELAN(WRS’ 02) 16

![Specifying Processors Speculative Processor Ps Jump Correct Spec Sysm Procia rf ITBia 1 k Specifying Processors Speculative Processor [Ps. Jump. Correct. Spec] Sys(m, Proc(ia, rf, ITB(ia 1, k,](https://slidetodoc.com/presentation_image_h2/de795f78ba107e0f589812f46bf8ead9/image-17.jpg)

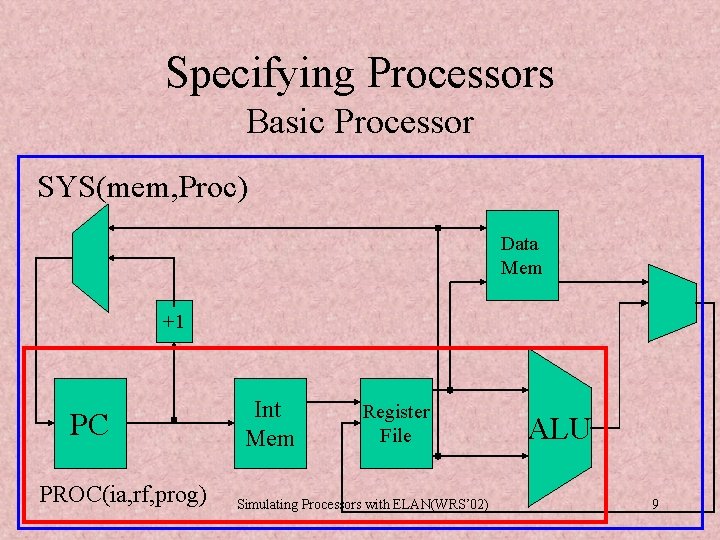

Specifying Processors Speculative Processor [Ps. Jump. Correct. Spec] Sys(m, Proc(ia, rf, ITB(ia 1, k, Jz(0, nia), wf, Spec(pia)). itbs, btb, prog)) => ), Sys(m, Proc(ia, rf, itbs, btb, prog)) itbs if pia==nia end Simulating Processors with ELAN(WRS’ 02) 17

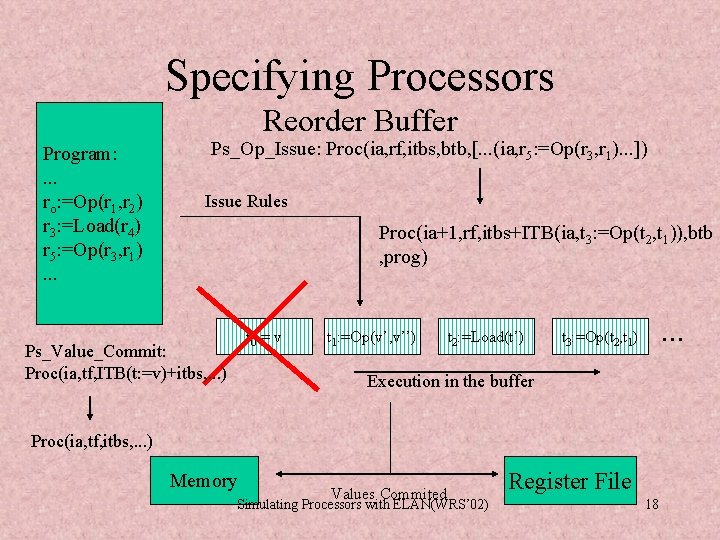

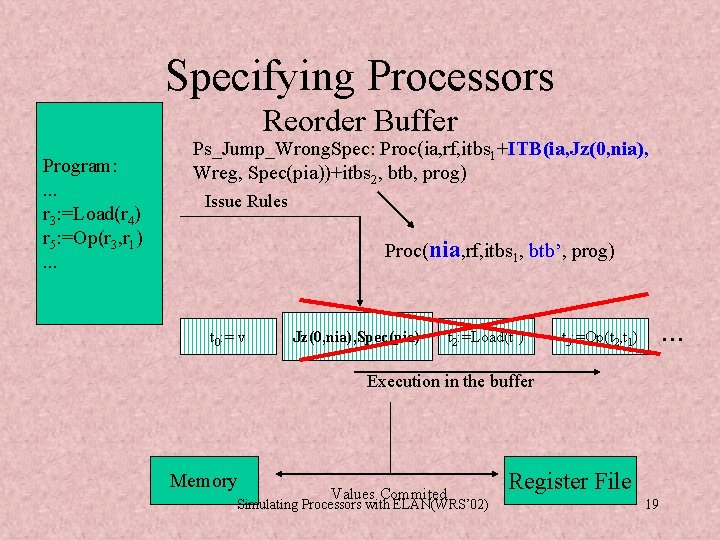

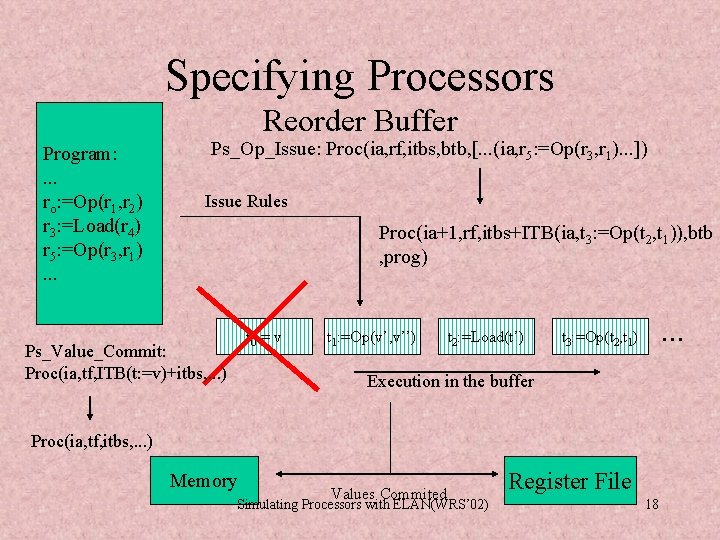

Specifying Processors Reorder Buffer Program: . . . ro: =Op(r 1, r 2) r 3: =Load(r 4) r 5: =Op(r 3, r 1). . . Ps_Op_Issue: Proc(ia, rf, itbs, btb, [. . . (ia, r 5: =Op(r 3, r 1). . . ]) Issue Rules Proc(ia+1, rf, itbs+ITB(ia, t 3: =Op(t 2, t 1)), btb , prog) t 0: = v Ps_Value_Commit: Proc(ia, tf, ITB(t: =v)+itbs, . . . ) t 1: =Op(v’, v’’) t 2: =Load(t’) . . . t 3: =Op(t 2, t 1) Execution in the buffer Proc(ia, tf, itbs, . . . ) Memory Values Commited Simulating Processors with ELAN(WRS’ 02) Register File 18

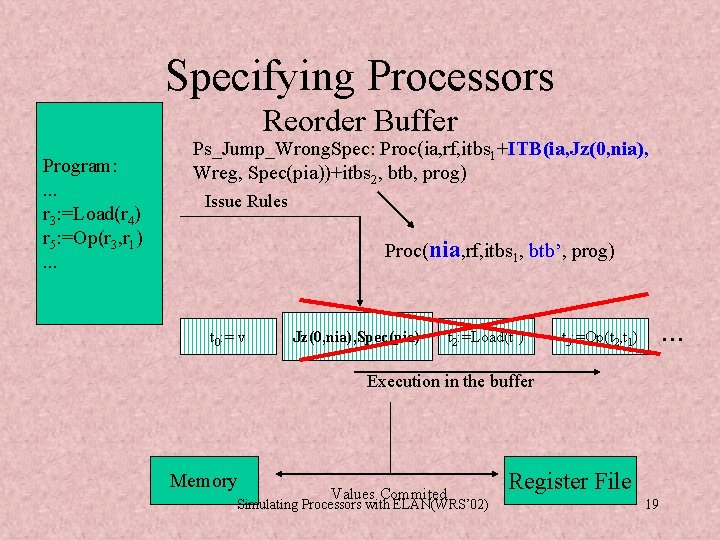

Specifying Processors Reorder Buffer Program: . . . r 3: =Load(r 4) r 5: =Op(r 3, r 1). . . Ps_Jump_Wrong. Spec: Proc(ia, rf, itbs 1+ITB(ia, Jz(0, nia), Wreg, Spec(pia))+itbs 2, btb, prog) Issue Rules Proc(nia, rf, itbs 1, btb’, prog) t 0: = v Jz(0, nia), Spec(pia) t 2: =Load(t’) . . . t 3: =Op(t 2, t 1) Execution in the buffer Memory Values Commited Simulating Processors with ELAN(WRS’ 02) Register File 19

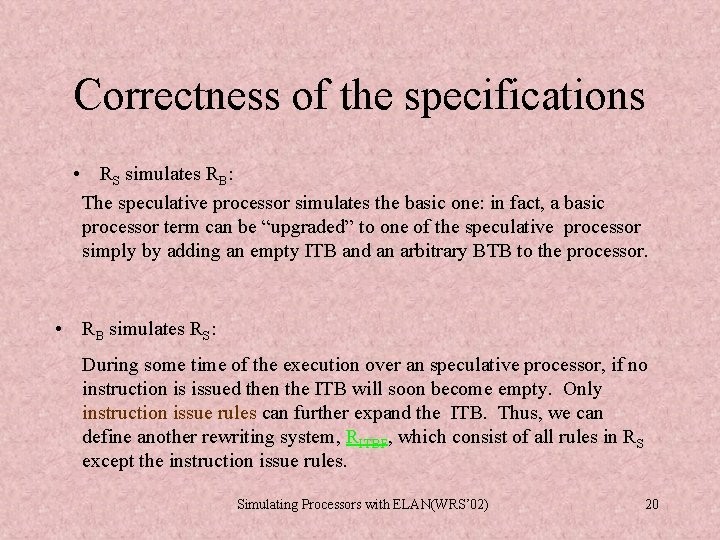

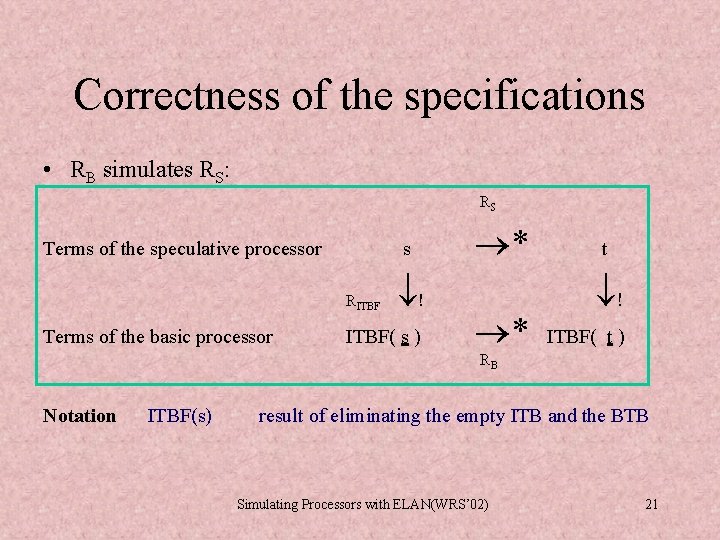

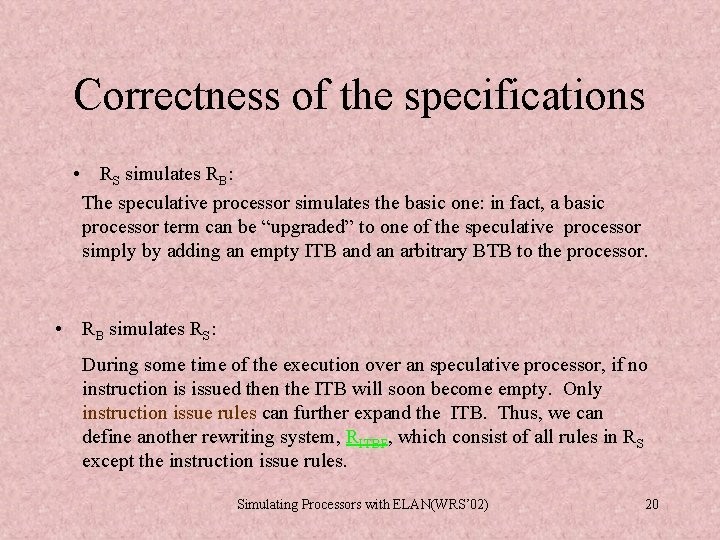

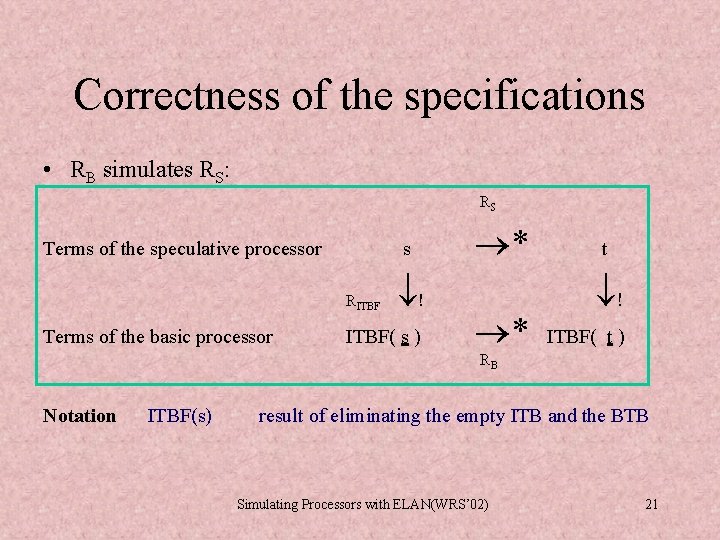

Correctness of the specifications • RS simulates RB: The speculative processor simulates the basic one: in fact, a basic processor term can be “upgraded” to one of the speculative processor simply by adding an empty ITB and an arbitrary BTB to the processor. • RB simulates RS: During some time of the execution over an speculative processor, if no instruction is issued then the ITB will soon become empty. Only instruction issue rules can further expand the ITB. Thus, we can define another rewriting system, RITBF, which consist of all rules in RS except the instruction issue rules. Simulating Processors with ELAN(WRS’ 02) 20

Correctness of the specifications • RB simulates RS: RS Terms of the speculative processor s RITBF Terms of the basic processor ! ITBF( s ) * * t ! ITBF( t ) RB Notation ITBF(s) result of eliminating the empty ITB and the BTB Simulating Processors with ELAN(WRS’ 02) 21

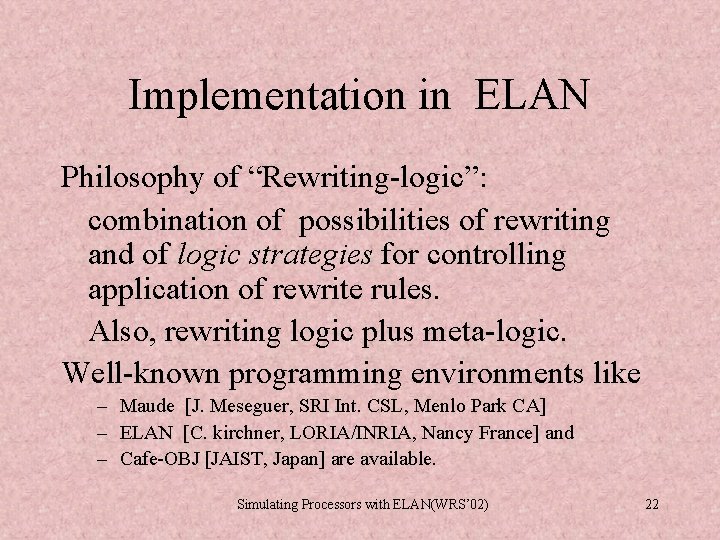

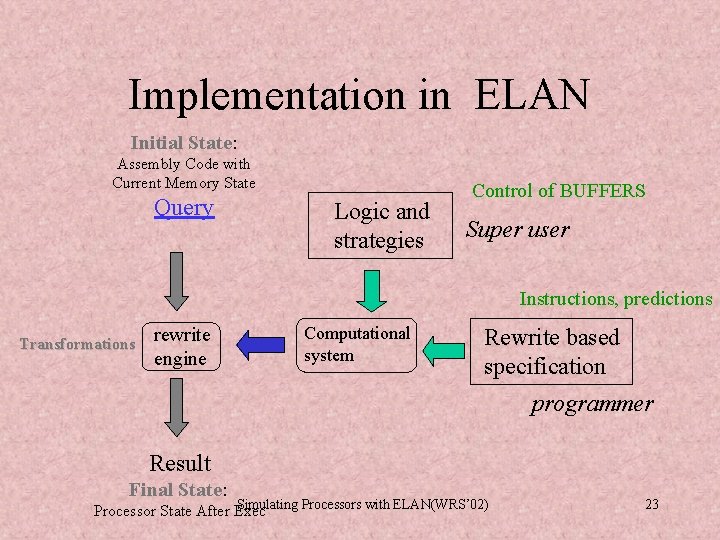

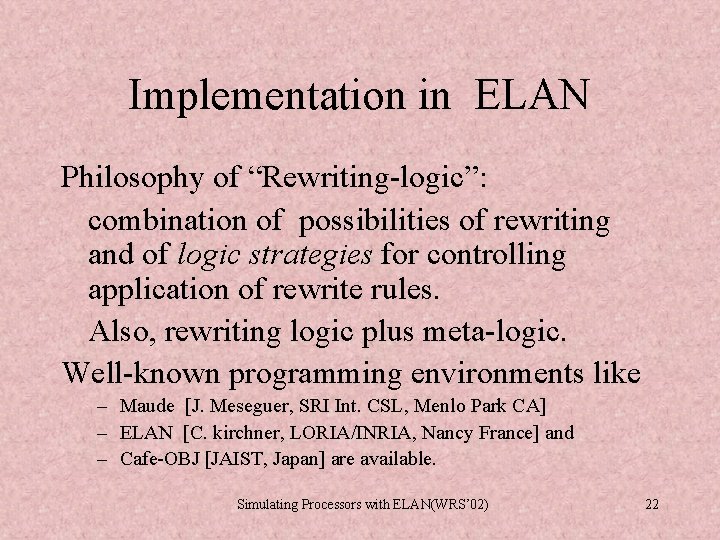

Implementation in ELAN Philosophy of “Rewriting-logic”: combination of possibilities of rewriting and of logic strategies for controlling application of rewrite rules. Also, rewriting logic plus meta-logic. Well-known programming environments like – Maude [J. Meseguer, SRI Int. CSL, Menlo Park CA] – ELAN [C. kirchner, LORIA/INRIA, Nancy France] and – Cafe-OBJ [JAIST, Japan] are available. Simulating Processors with ELAN(WRS’ 02) 22

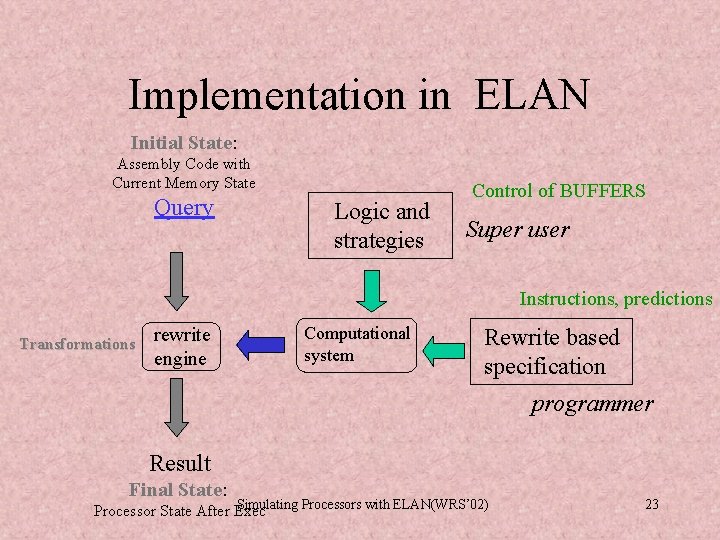

Implementation in ELAN Initial State: Assembly Code with Current Memory State Query Logic and strategies Control of BUFFERS Super user Instructions, predictions Transformations rewrite engine Computational system Rewrite based specification programmer Result Final State: Simulating Processors with ELAN(WRS’ 02) Processor State After Exec 23

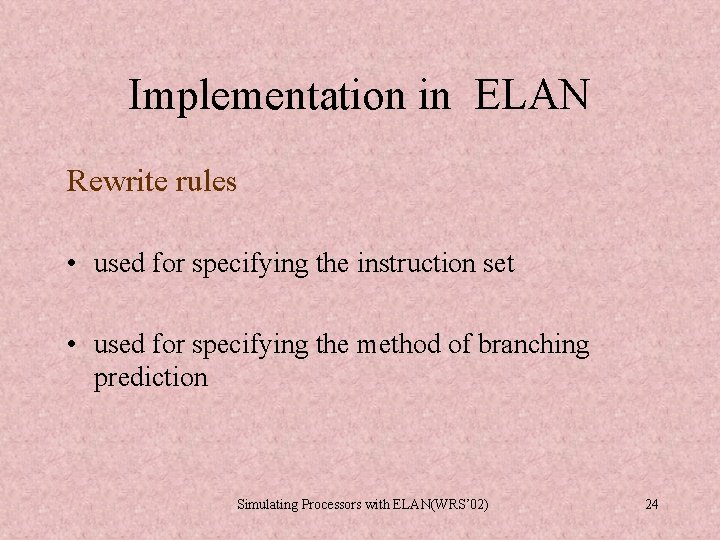

Implementation in ELAN Rewrite rules • used for specifying the instruction set • used for specifying the method of branching prediction Simulating Processors with ELAN(WRS’ 02) 24

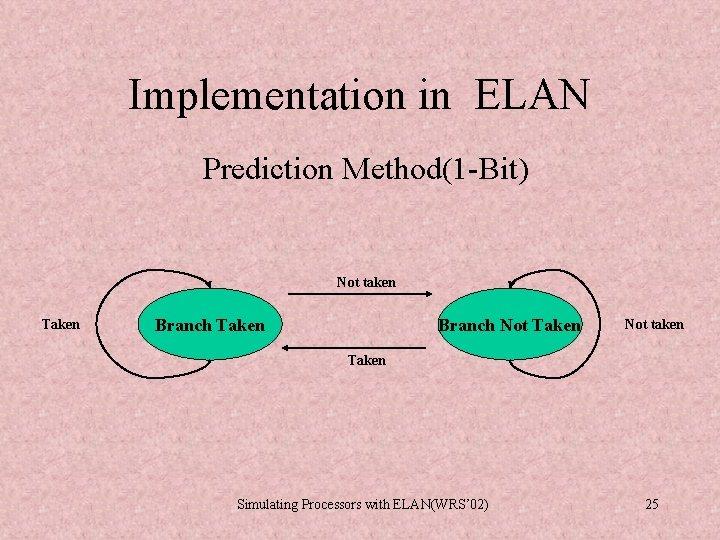

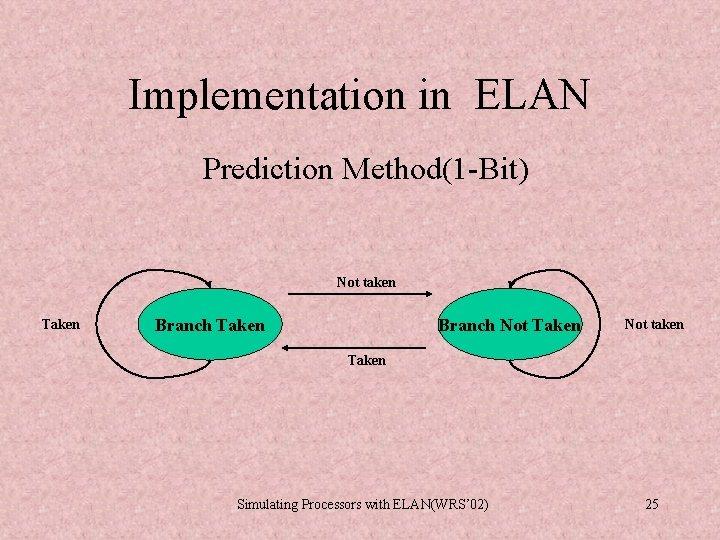

Implementation in ELAN Prediction Method(1 -Bit) Not taken Taken Branch Not Taken Not taken Taken Simulating Processors with ELAN(WRS’ 02) 25

Implementation in ELAN • Branching prediction: BTB : (1, 2). (2, 3). . . (n, m). . nth instruction: Jz(r 1, r 2) [Ps. Jump. Wrong. Spec] Sys(m, Proc(ia, rf, ITB(ia 1, k, Jz(0, nia), wf, Spec(pia)). itbs, btb, prog)) => Sys(m, Proc(nia, rf, nilitb, btb 1, prog)) if pia != nia where btb 1 : = ()changebtb(ia 1, nia, btb) end Simulating Processors with ELAN(WRS’ 02) 26

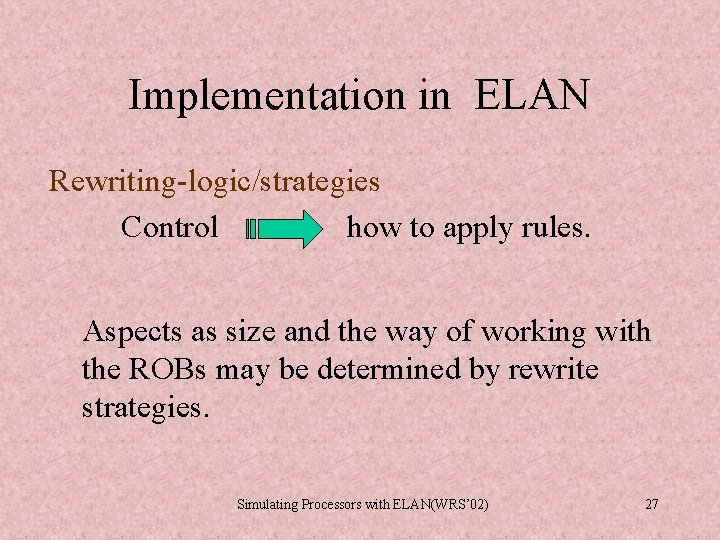

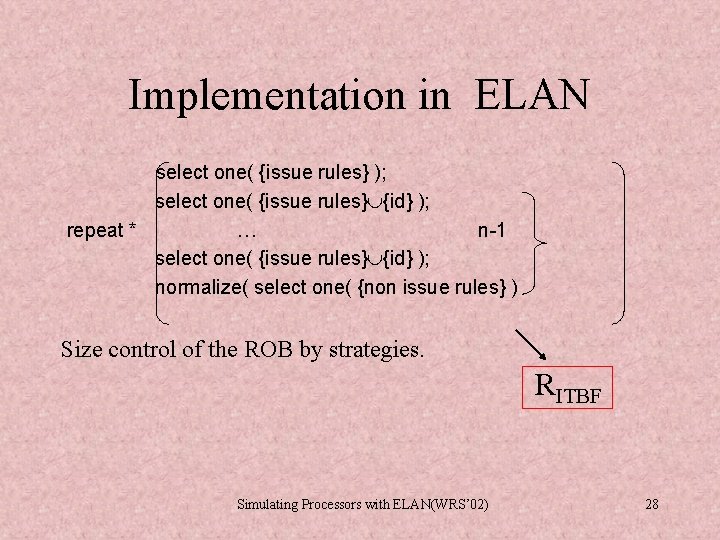

Implementation in ELAN Rewriting-logic/strategies Control how to apply rules. Aspects as size and the way of working with the ROBs may be determined by rewrite strategies. Simulating Processors with ELAN(WRS’ 02) 27

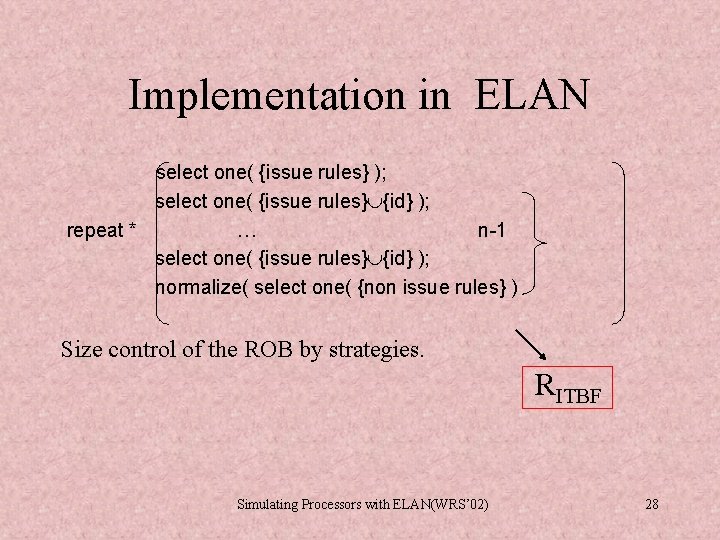

Implementation in ELAN select one( {issue rules} ); select one( {issue rules} {id} ); repeat * n-1 select one( {issue rules} {id} ); normalize( select one( {non issue rules} ) Size control of the ROB by strategies. RITBF Simulating Processors with ELAN(WRS’ 02) 28

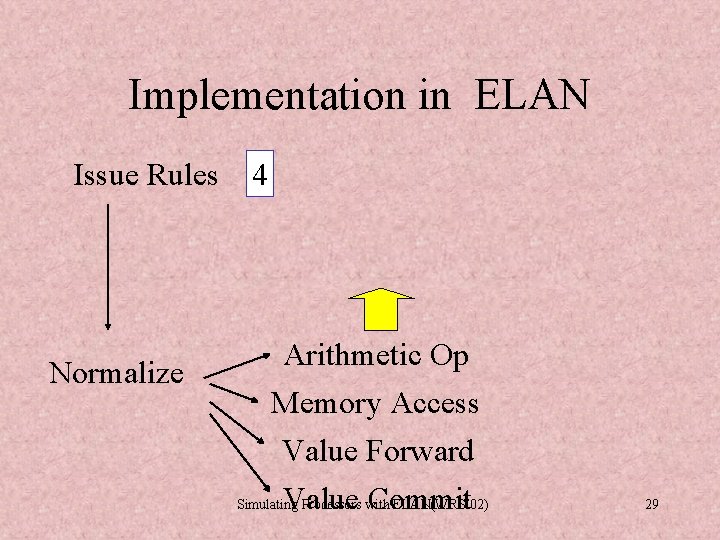

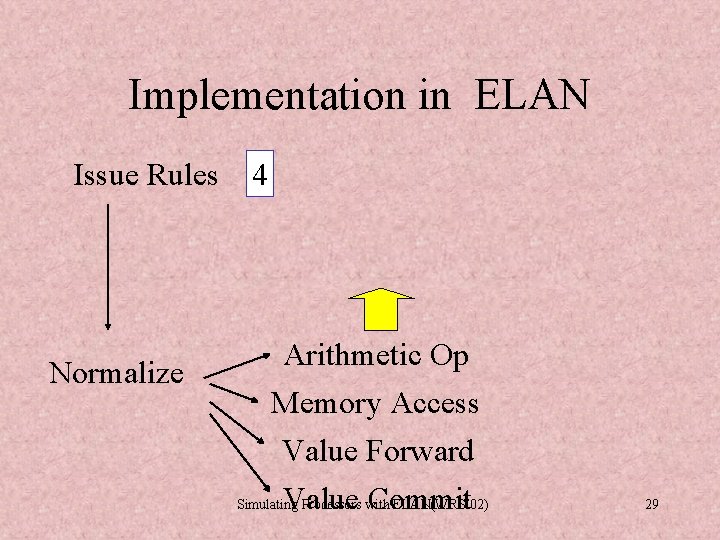

Implementation in ELAN Issue Rules 1 4 3 2 ITB Normalize ITB Arithmetic Op Memory Access Value Forward Value Commit Simulating Processors with ELAN(WRS’ 02) ITB 29

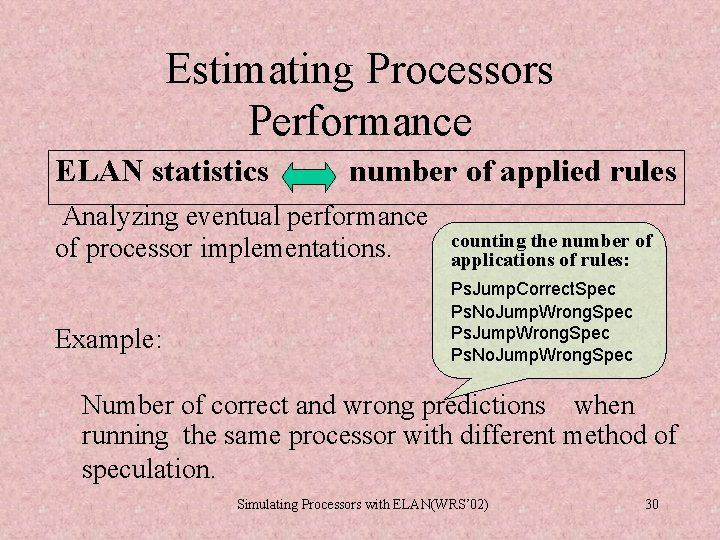

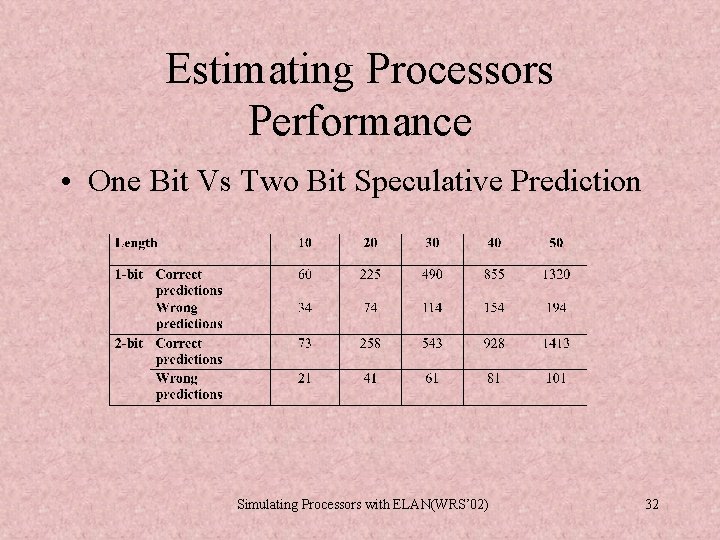

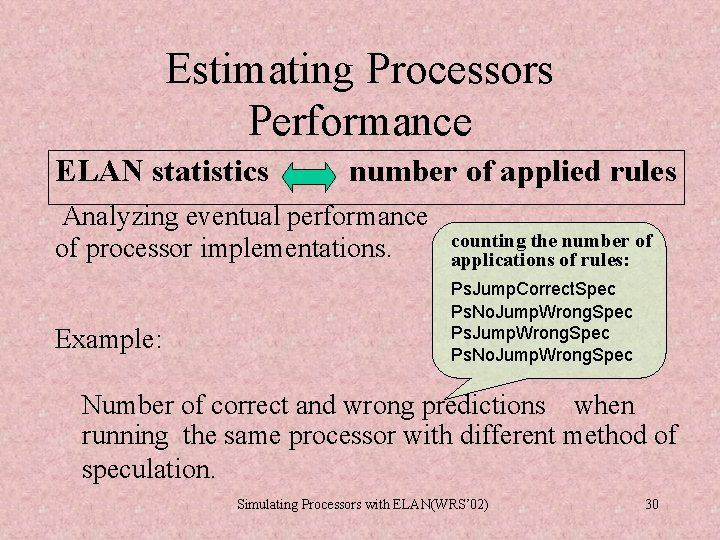

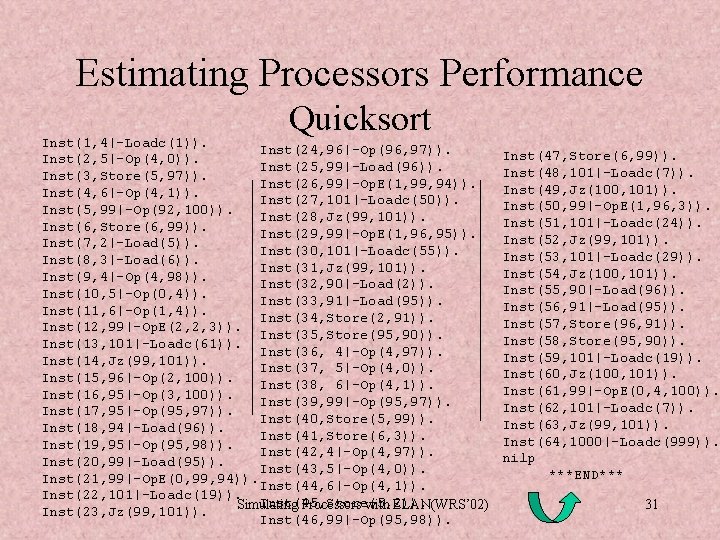

Estimating Processors Performance ELAN statistics number of applied rules Analyzing eventual performance of processor implementations. Example: counting the number of applications of rules: Ps. Jump. Correct. Spec Ps. No. Jump. Wrong. Spec Number of correct and wrong predictions when running the same processor with different method of speculation. Simulating Processors with ELAN(WRS’ 02) 30

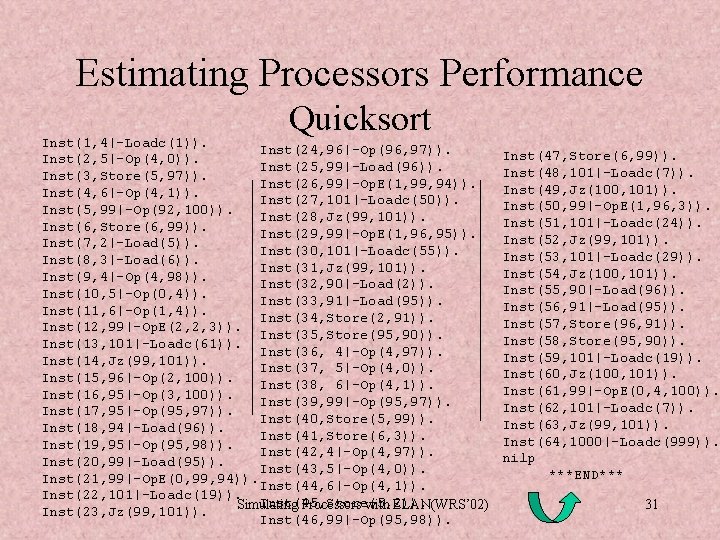

Estimating Processors Performance Quicksort Inst(1, 4|-Loadc(1)). Inst(24, 96|-Op(96, 97)). Inst(2, 5|-Op(4, 0)). Inst(25, 99|-Load(96)). Inst(3, Store(5, 97)). Inst(26, 99|-Op. E(1, 99, 94)). Inst(4, 6|-Op(4, 1)). Inst(27, 101|-Loadc(50)). Inst(5, 99|-Op(92, 100)). Inst(28, Jz(99, 101)). Inst(6, Store(6, 99)). Inst(29, 99|-Op. E(1, 96, 95)). Inst(7, 2|-Load(5)). Inst(30, 101|-Loadc(55)). Inst(8, 3|-Load(6)). Inst(31, Jz(99, 101)). Inst(9, 4|-Op(4, 98)). Inst(32, 90|-Load(2)). Inst(10, 5|-Op(0, 4)). Inst(33, 91|-Load(95)). Inst(11, 6|-Op(1, 4)). Inst(34, Store(2, 91)). Inst(12, 99|-Op. E(2, 2, 3)). Inst(35, Store(95, 90)). Inst(13, 101|-Loadc(61)). Inst(36, 4|-Op(4, 97)). Inst(14, Jz(99, 101)). Inst(37, 5|-Op(4, 0)). Inst(15, 96|-Op(2, 100)). Inst(38, 6|-Op(4, 1)). Inst(16, 95|-Op(3, 100)). Inst(39, 99|-Op(95, 97)). Inst(17, 95|-Op(95, 97)). Inst(40, Store(5, 99)). Inst(18, 94|-Load(96)). Inst(41, Store(6, 3)). Inst(19, 95|-Op(95, 98)). Inst(42, 4|-Op(4, 97)). Inst(20, 99|-Load(95)). Inst(43, 5|-Op(4, 0)). Inst(21, 99|-Op. E(0, 99, 94)). Inst(44, 6|-Op(4, 1)). Inst(22, 101|-Loadc(19)). Inst(45, Store(5, 2)). Simulating Processors with ELAN(WRS’ 02) Inst(23, Jz(99, 101)). Inst(46, 99|-Op(95, 98)). Inst(47, Store(6, 99)). Inst(48, 101|-Loadc(7)). Inst(49, Jz(100, 101)). Inst(50, 99|-Op. E(1, 96, 3)). Inst(51, 101|-Loadc(24)). Inst(52, Jz(99, 101)). Inst(53, 101|-Loadc(29)). Inst(54, Jz(100, 101)). Inst(55, 90|-Load(96)). Inst(56, 91|-Load(95)). Inst(57, Store(96, 91)). Inst(58, Store(95, 90)). Inst(59, 101|-Loadc(19)). Inst(60, Jz(100, 101)). Inst(61, 99|-Op. E(0, 4, 100)). Inst(62, 101|-Loadc(7)). Inst(63, Jz(99, 101)). Inst(64, 1000|-Loadc(999)). nilp ***END*** 31

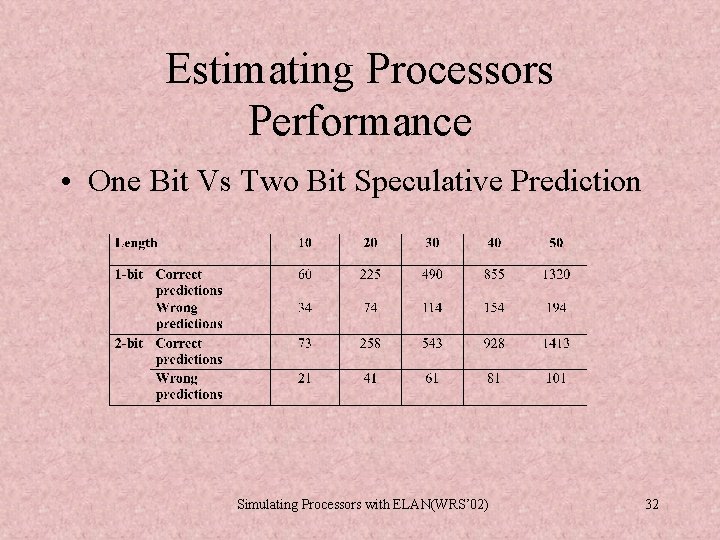

Estimating Processors Performance • One Bit Vs Two Bit Speculative Prediction Simulating Processors with ELAN(WRS’ 02) 32

Conclusions and Future Work • Rewriting-logic is useful for specifying correctly processors, but also for testing their performance. • Going down more levels – Execution stages: fetch-decode-execute by atomizing the current implemented rules. Describing in this way more accurately processors behavior. • Going down more levels: – Logic circuit layout design. Simulating Processors with ELAN(WRS’ 02) 33

Conclusions and Future Work • Important natural aspects of rewriting theory, nowadays hard to resolve and implement in programming and proof assistants environments, may be useful for testing accurately new proposed technologies: Like a real non deterministic out-of-order execution. Simulating Processors with ELAN(WRS’ 02) 34

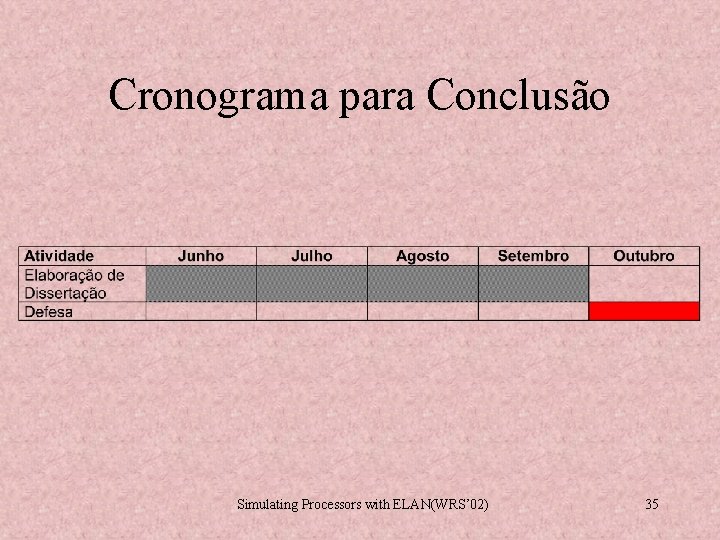

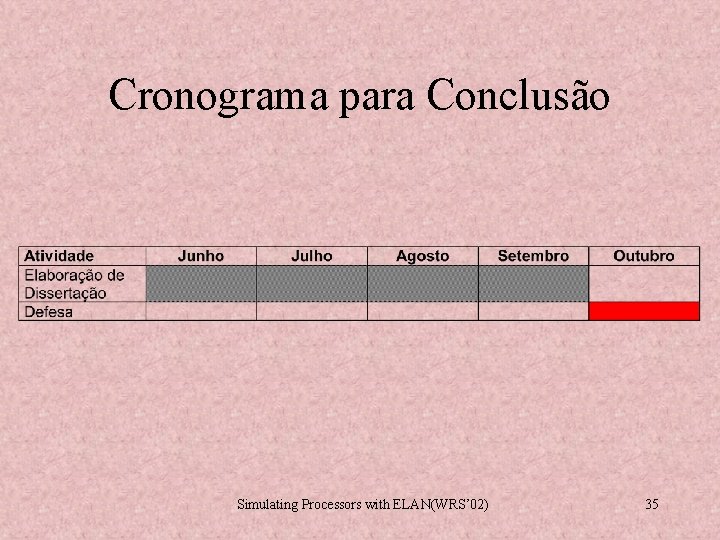

Cronograma para Conclusão Simulating Processors with ELAN(WRS’ 02) 35

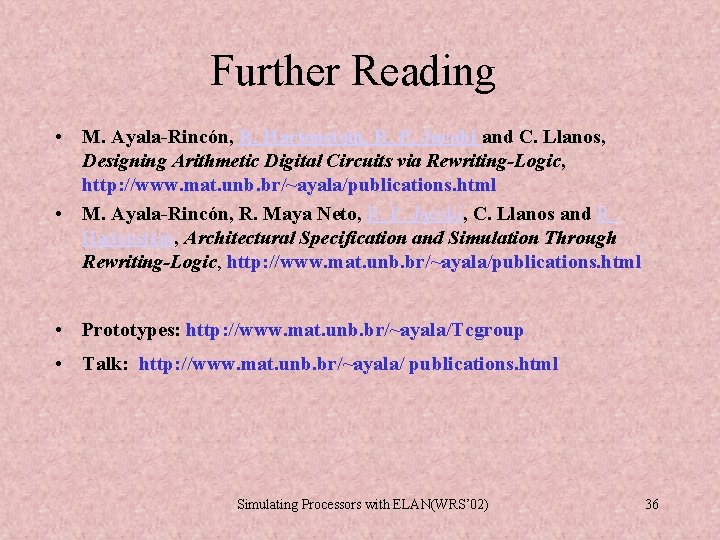

Further Reading • M. Ayala-Rincón, R. Hartenstein, R. P. Jacobi and C. Llanos, Designing Arithmetic Digital Circuits via Rewriting-Logic, http: //www. mat. unb. br/~ayala/publications. html • M. Ayala-Rincón, R. Maya Neto, R. P. Jacobi, C. Llanos and R. Hartenstein, Architectural Specification and Simulation Through Rewriting-Logic, http: //www. mat. unb. br/~ayala/publications. html • Prototypes: http: //www. mat. unb. br/~ayala/Tcgroup • Talk: http: //www. mat. unb. br/~ayala/ publications. html Simulating Processors with ELAN(WRS’ 02) 36