OC192 communications system block diagram Laser 10 Gbs

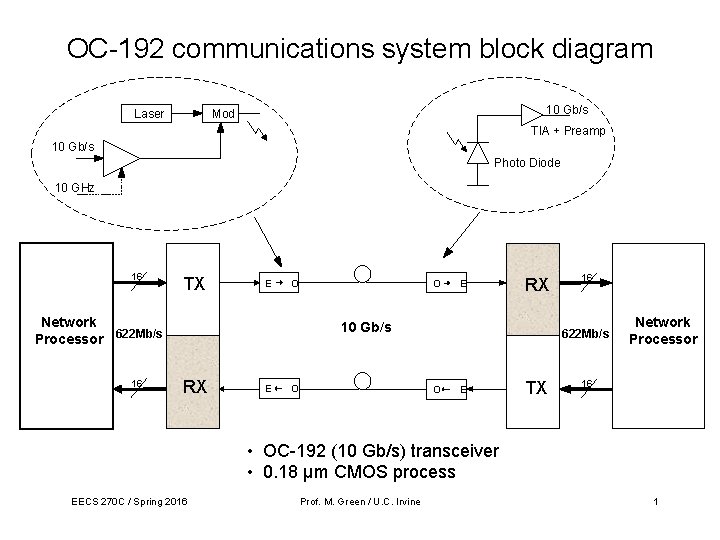

OC-192 communications system block diagram Laser 10 Gb/s Mod TIA + Preamp 10 Gb/s Photo Diode 10 GHz 16 TX E O Network Processor 622 Mb/s 16 O E RX 10 Gb/s RX E O 16 622 Mb/s O E TX Network Processor 16 • OC-192 (10 Gb/s) transceiver • 0. 18 µm CMOS process EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 1

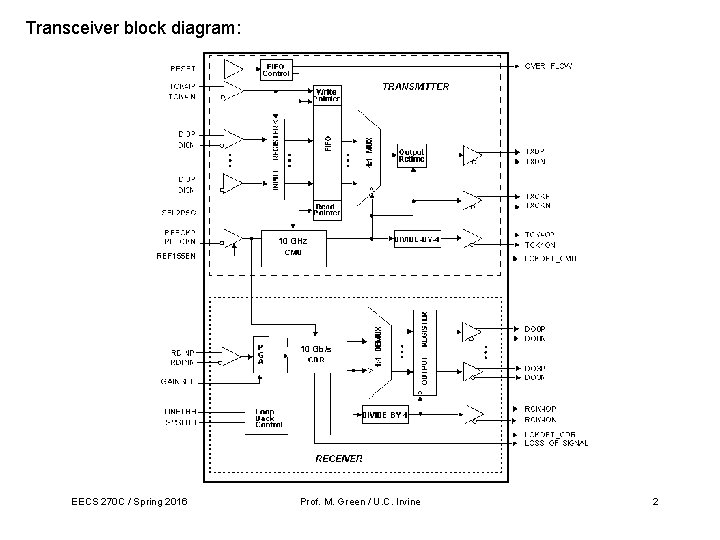

Transceiver block diagram: 10 GHz 10 Gb/s EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 2

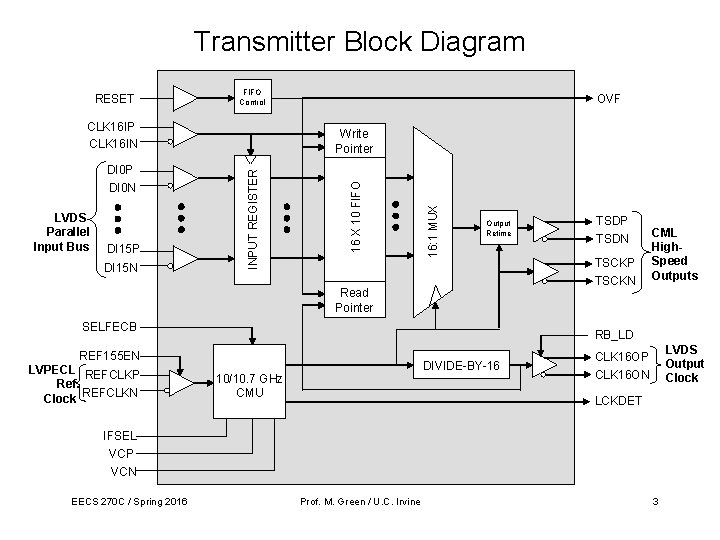

Transmitter Block Diagram FIFO Control CLK 16 IP CLK 16 IN DI 15 P DI 15 N 16: 1 MUX LVDS Parallel Input Bus Write Pointer INPUT REGISTER DI 0 P DI 0 N OVF 16 X 10 FIFO RESET Output Retime Read Pointer SELFECB TSCKP TSCKN CML High. Speed Outputs RB_LD REF 155 EN LVPECL REFCLKP Ref. REFCLKN Clock TSDP TSDN DIVIDE-BY-16 10/10. 7 GHz CMU LVDS Output Clock CLK 16 OP CLK 16 ON LCKDET IFSEL VCP VCN EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 3

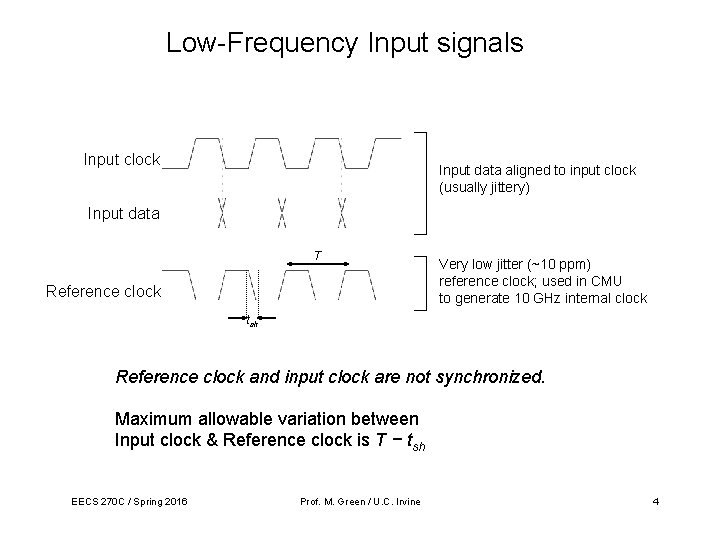

Low-Frequency Input signals Input clock Input data aligned to input clock (usually jittery) Input data T Reference clock Very low jitter (~10 ppm) reference clock; used in CMU to generate 10 GHz internal clock tsh Reference clock and input clock are not synchronized. Maximum allowable variation between Input clock & Reference clock is T − tsh EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 4

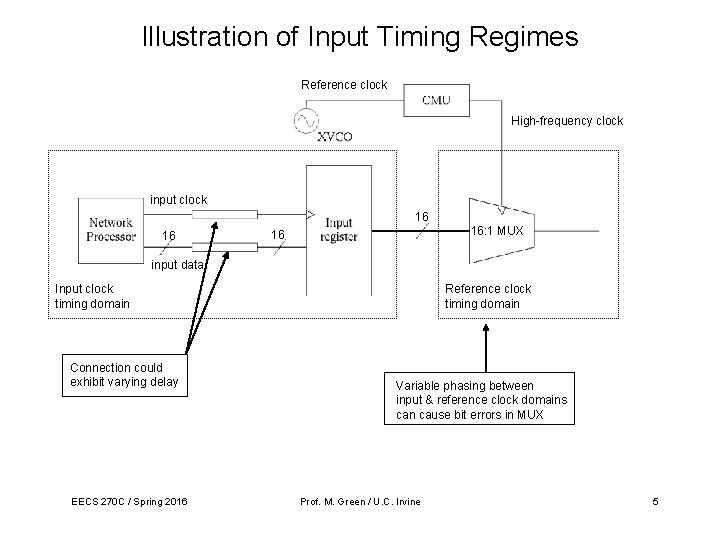

Illustration of Input Timing Regimes Reference clock High-frequency clock input clock 16 16 16: 1 MUX 16 input data Input clock timing domain Connection could exhibit varying delay EECS 270 C / Spring 2016 Reference clock timing domain Variable phasing between input & reference clock domains can cause bit errors in MUX Prof. M. Green / U. C. Irvine 5

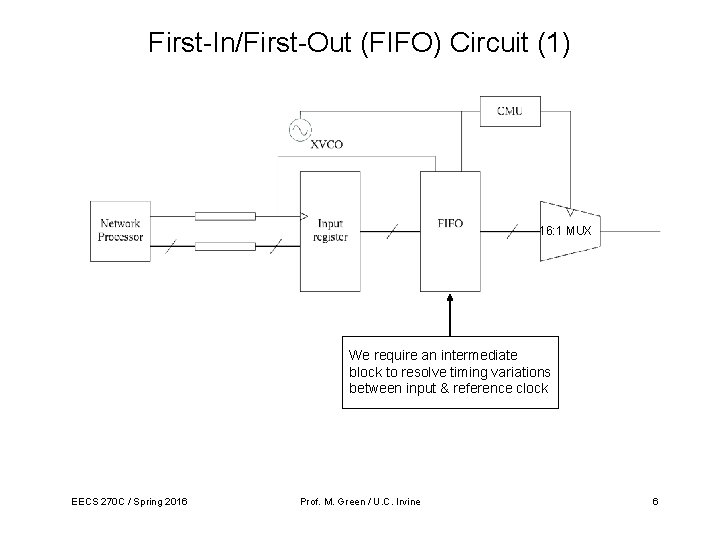

First-In/First-Out (FIFO) Circuit (1) 16: 1 MUX We require an intermediate block to resolve timing variations between input & reference clock EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 6

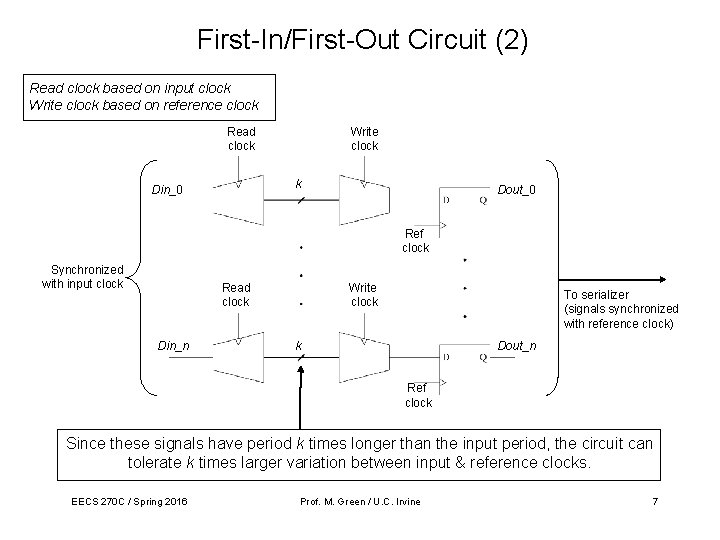

First-In/First-Out Circuit (2) Read clock based on input clock Write clock based on reference clock Read clock Write clock k Din_0 Dout_0 Ref clock Synchronized with input clock Read clock Din_n Write clock To serializer (signals synchronized with reference clock) k Dout_n Ref clock Since these signals have period k times longer than the input period, the circuit can tolerate k times larger variation between input & reference clocks. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 7

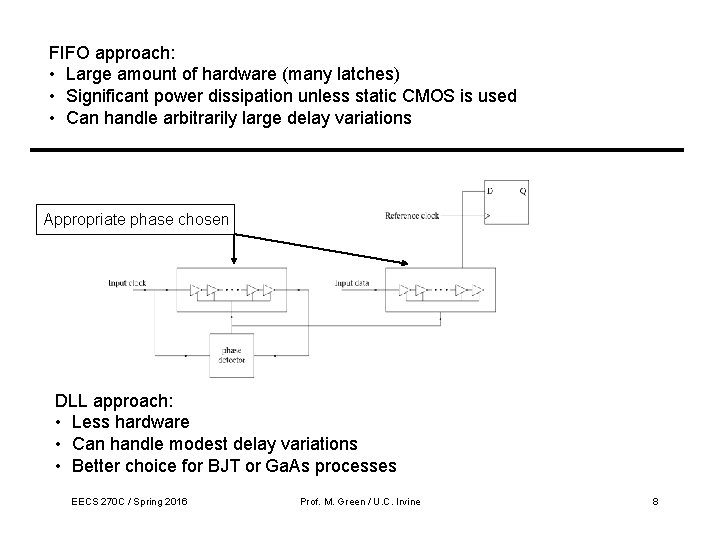

FIFO approach: • Large amount of hardware (many latches) • Significant power dissipation unless static CMOS is used • Can handle arbitrarily large delay variations Appropriate phase chosen DLL approach: • Less hardware • Can handle modest delay variations • Better choice for BJT or Ga. As processes EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 8

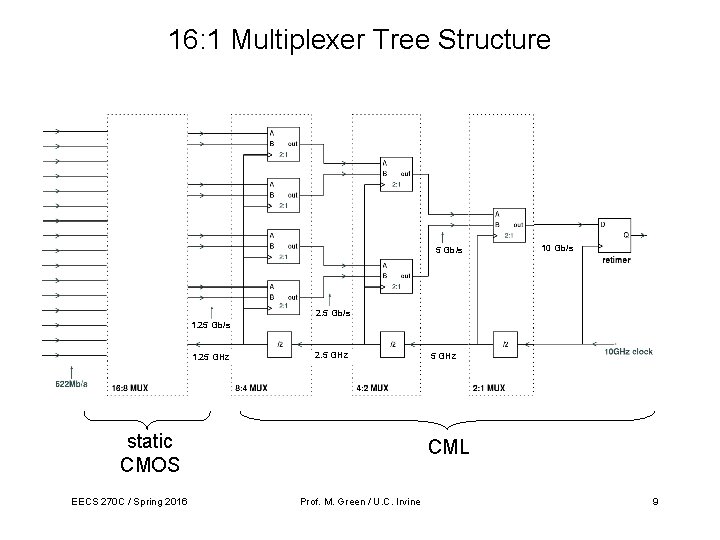

16: 1 Multiplexer Tree Structure 5 Gb/s 10 Gb/s 2. 5 Gb/s 1. 25 GHz 2. 5 GHz static CMOS EECS 270 C / Spring 2016 5 GHz CML Prof. M. Green / U. C. Irvine 9

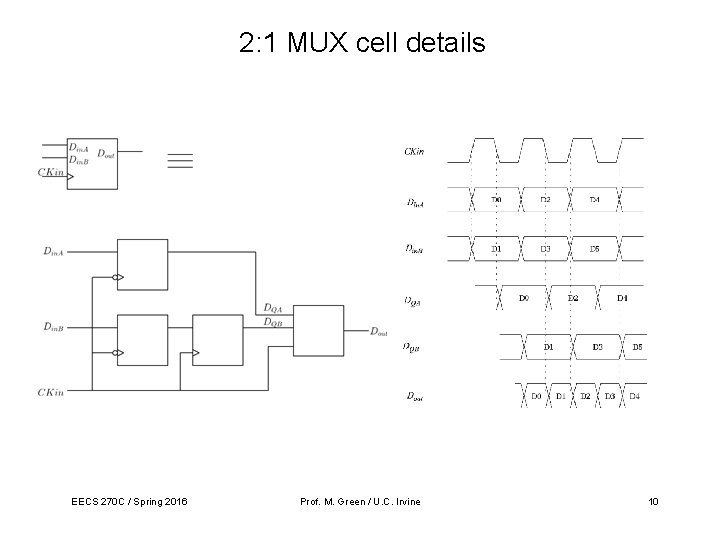

2: 1 MUX cell details EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 10

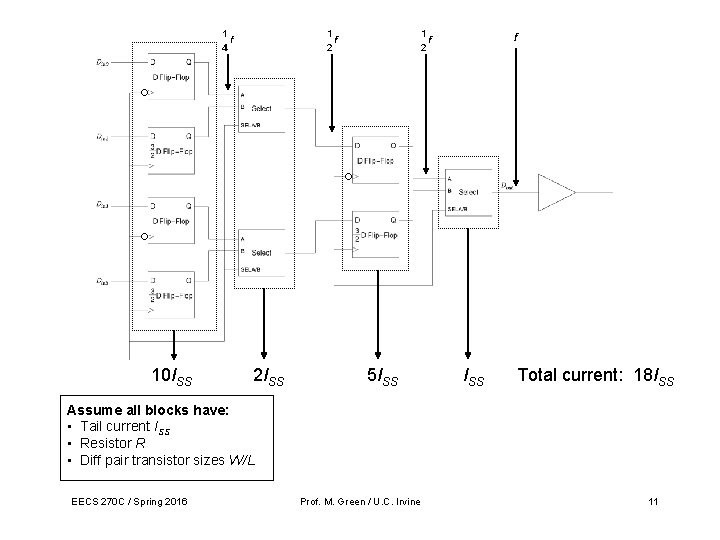

10 ISS 2 ISS 5 ISS Total current: 18 ISS Assume all blocks have: • Tail current ISS • Resistor R • Diff pair transistor sizes W/L EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 11

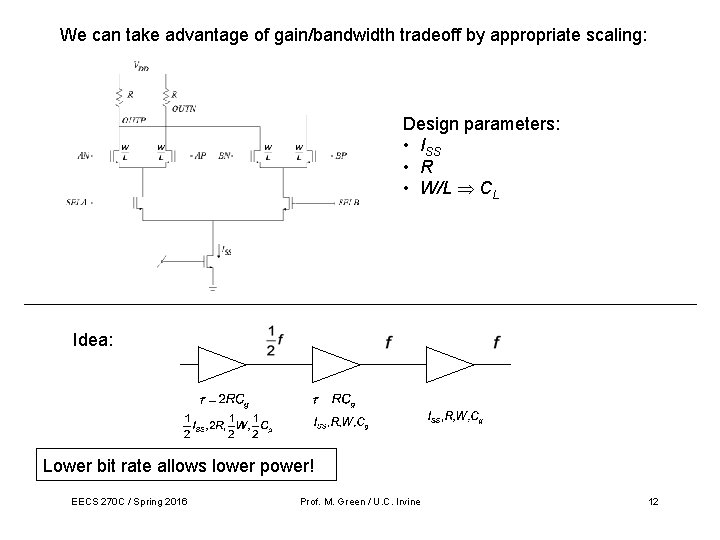

We can take advantage of gain/bandwidth tradeoff by appropriate scaling: Design parameters: • ISS • R • W/L CL Idea: Lower bit rate allows lower power! EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 12

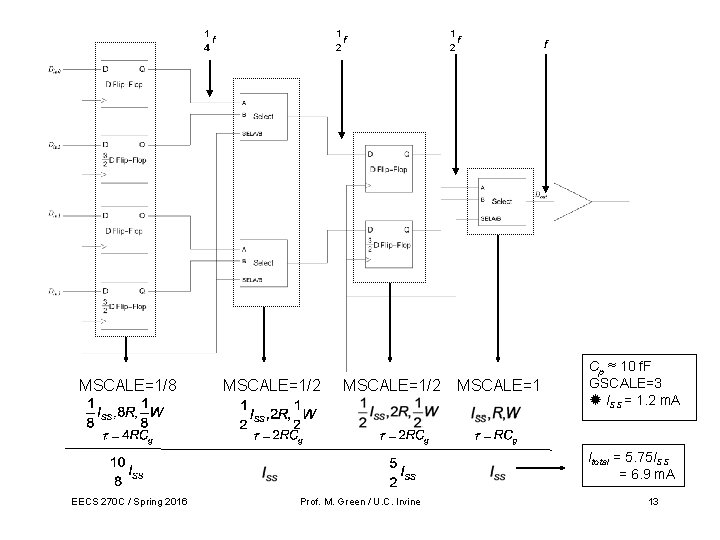

MSCALE=1/8 MSCALE=1/2 MSCALE=1 Cp ≈ 10 f. F GSCALE=3 ISS = 1. 2 m. A Itotal = 5. 75 ISS = 6. 9 m. A EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 13

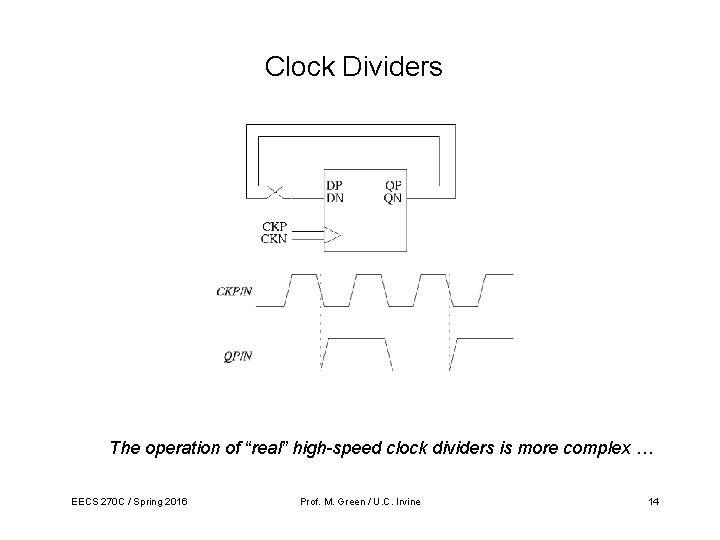

Clock Dividers The operation of “real” high-speed clock dividers is more complex … EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 14

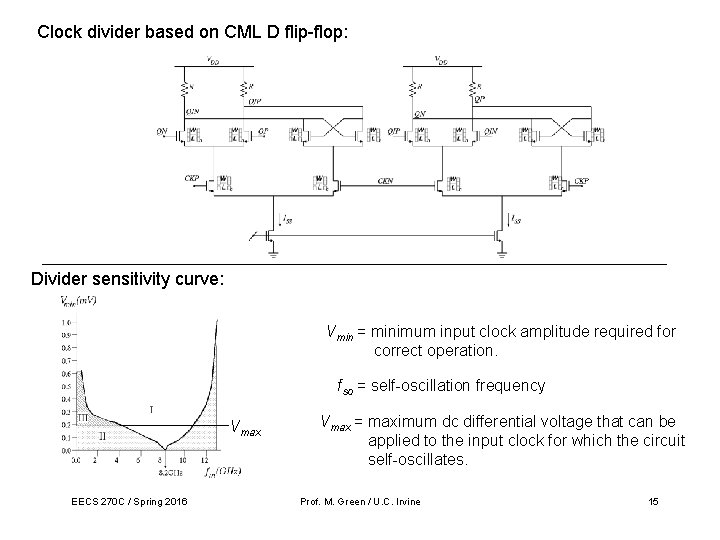

Clock divider based on CML D flip-flop: Divider sensitivity curve: Vmin = minimum input clock amplitude required for correct operation. fso = self-oscillation frequency Vmax EECS 270 C / Spring 2016 Vmax = maximum dc differential voltage that can be applied to the input clock for which the circuit self-oscillates. Prof. M. Green / U. C. Irvine 15

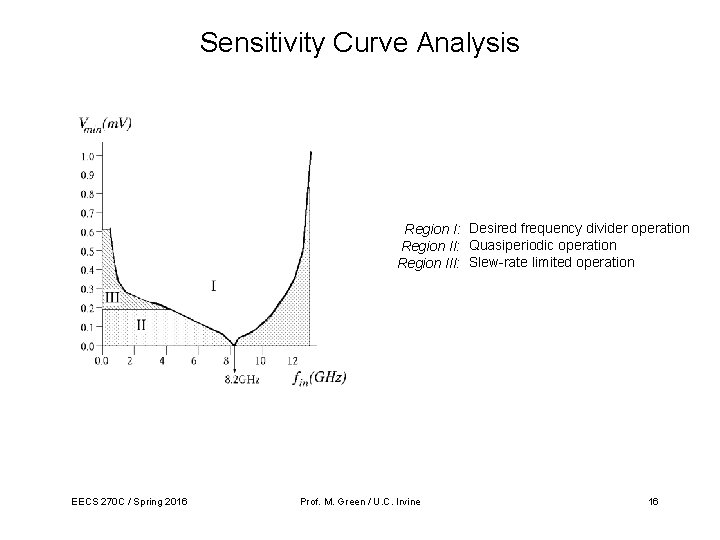

Sensitivity Curve Analysis Region I: Desired frequency divider operation Region II: Quasiperiodic operation Region III: Slew-rate limited operation EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 16

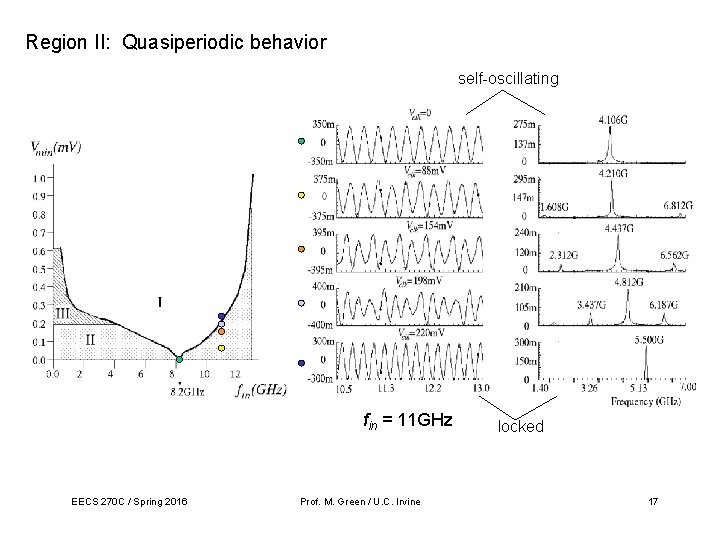

Region II: Quasiperiodic behavior self-oscillating fin = 11 GHz EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine locked 17

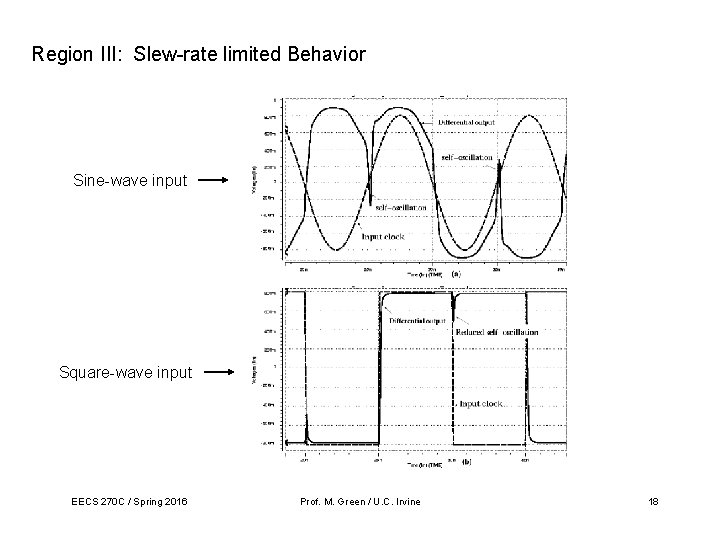

Region III: Slew-rate limited Behavior Sine-wave input Square-wave input EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 18

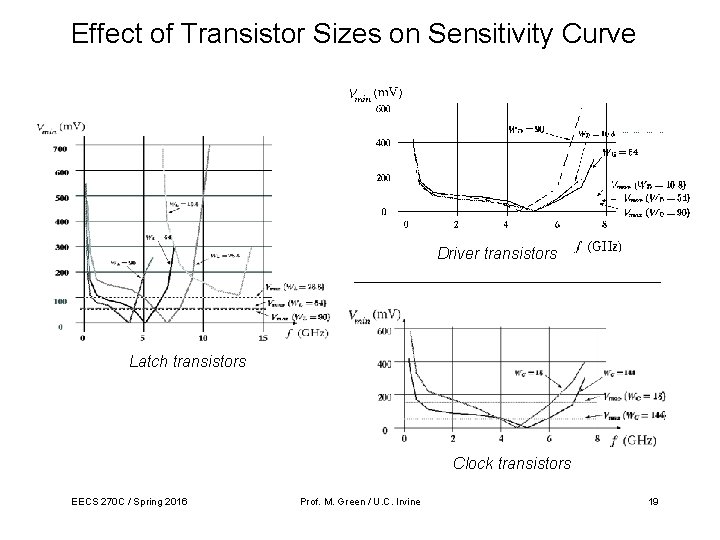

Effect of Transistor Sizes on Sensitivity Curve Driver transistors Latch transistors Clock transistors EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 19

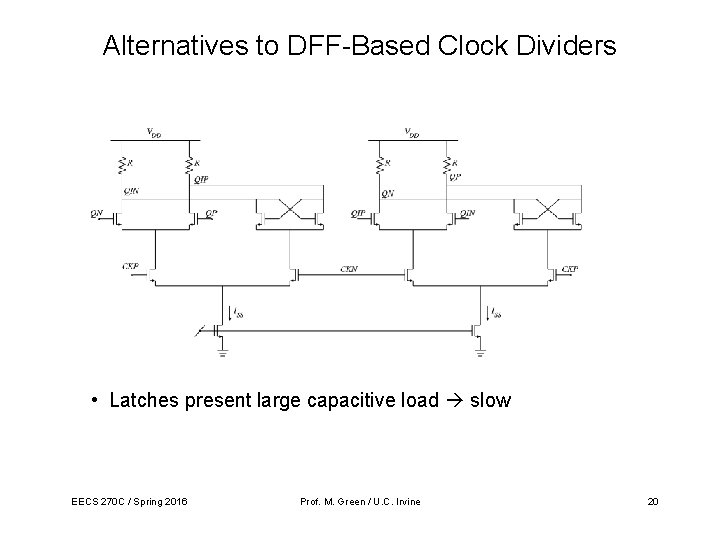

Alternatives to DFF-Based Clock Dividers • Latches present large capacitive load slow EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 20

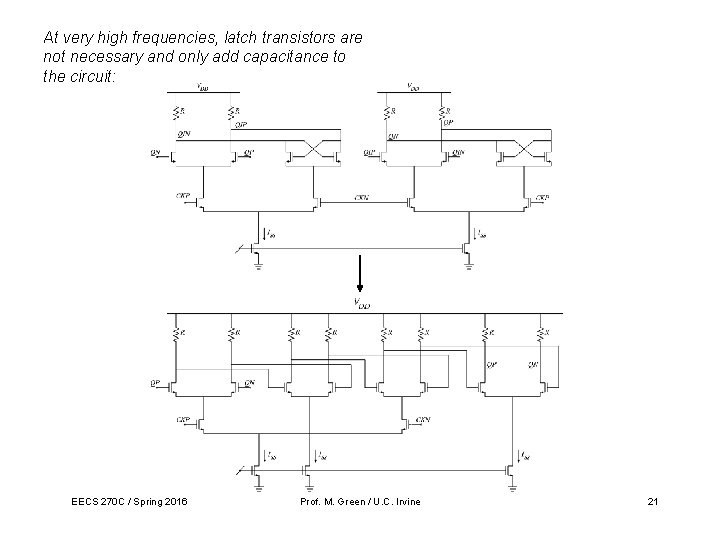

At very high frequencies, latch transistors are not necessary and only add capacitance to the circuit: EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 21

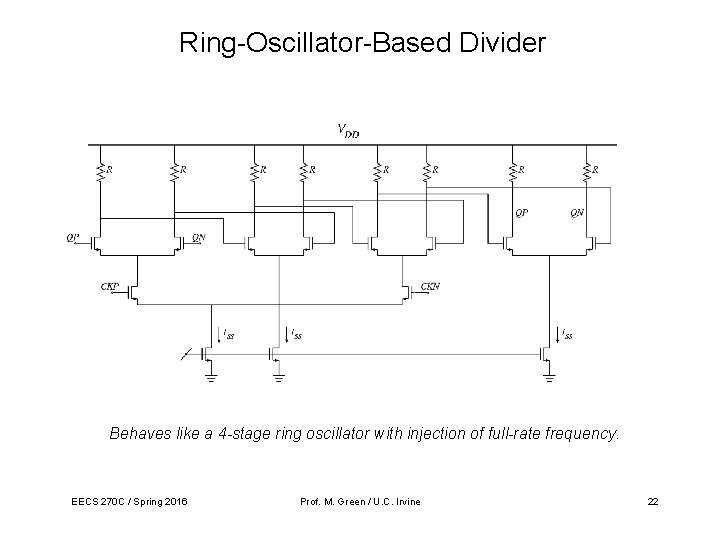

Ring-Oscillator-Based Divider Behaves like a 4 -stage ring oscillator with injection of full-rate frequency. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 22

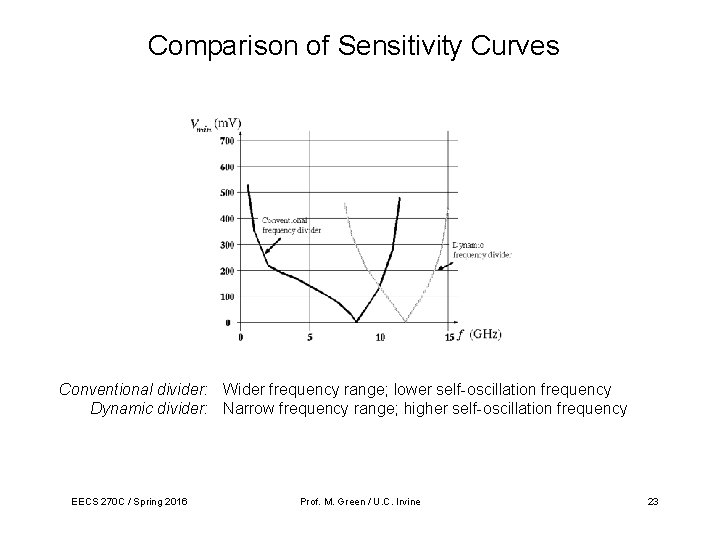

Comparison of Sensitivity Curves Conventional divider: Wider frequency range; lower self-oscillation frequency Dynamic divider: Narrow frequency range; higher self-oscillation frequency EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 23

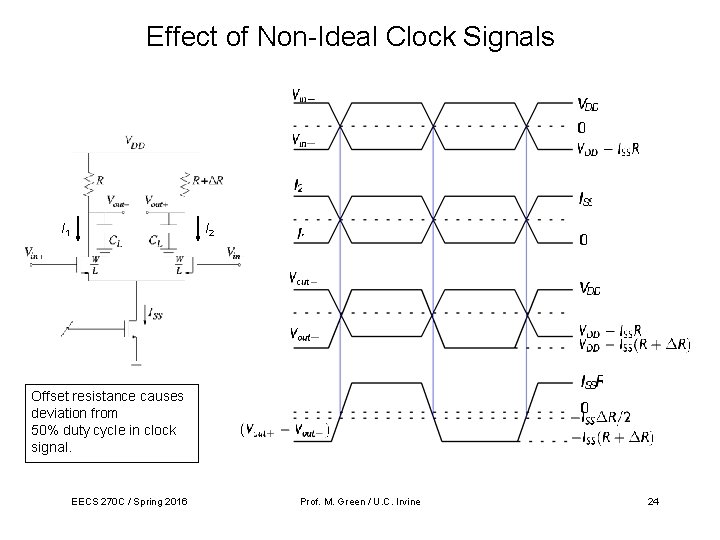

Effect of Non-Ideal Clock Signals I 1 I 2 Offset resistance causes deviation from 50% duty cycle in clock signal. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 24

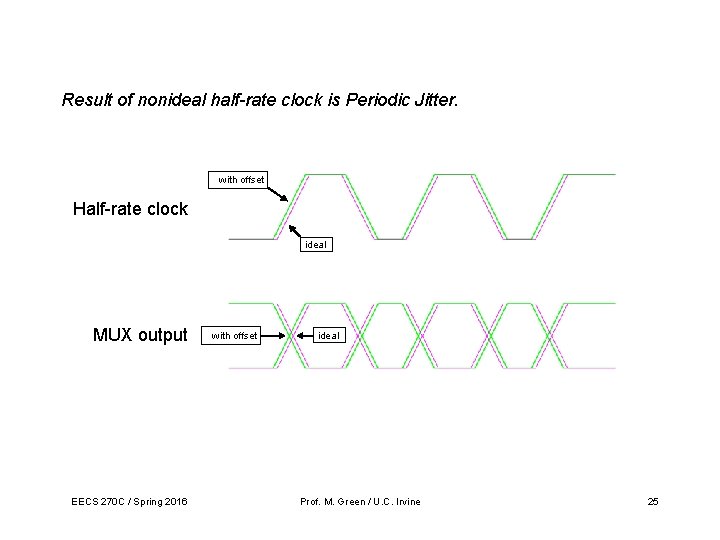

Result of nonideal half-rate clock is Periodic Jitter. with offset Half-rate clock ideal MUX output EECS 270 C / Spring 2016 with offset ideal Prof. M. Green / U. C. Irvine 25

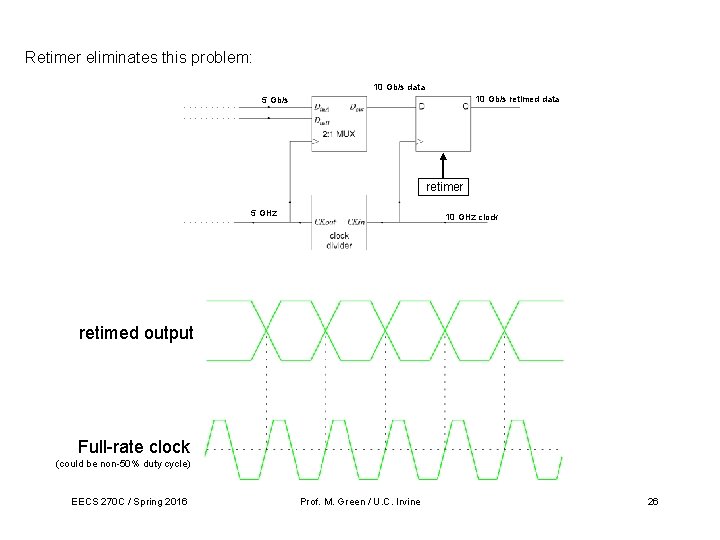

Retimer eliminates this problem: 10 Gb/s data 10 Gb/s retimed data 5 Gb/s retimer 5 GHz 10 GHz clock retimed output Full-rate clock (could be non-50% duty cycle) EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 26

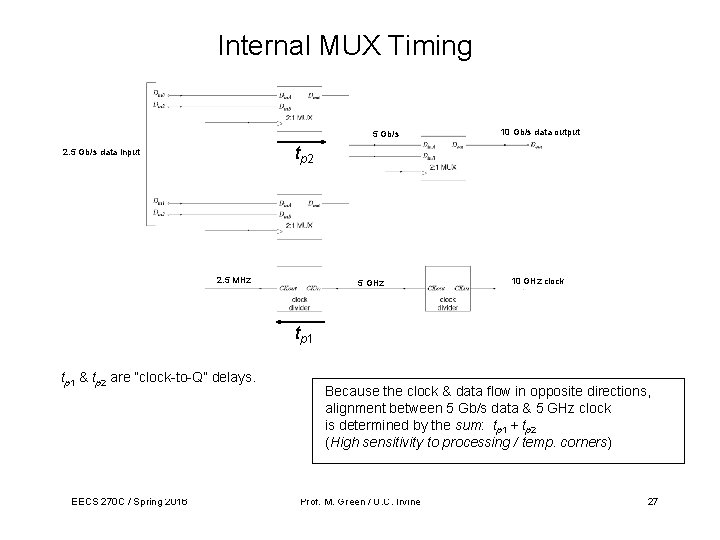

Internal MUX Timing 5 Gb/s 10 Gb/s data output tp 2 2. 5 Gb/s data input 2. 5 MHz 5 GHz 10 GHz clock tp 1 & tp 2 are “clock-to-Q” delays. EECS 270 C / Spring 2016 Because the clock & data flow in opposite directions, alignment between 5 Gb/s data & 5 GHz clock is determined by the sum: tp 1 + tp 2 (High sensitivity to processing / temp. corners) Prof. M. Green / U. C. Irvine 27

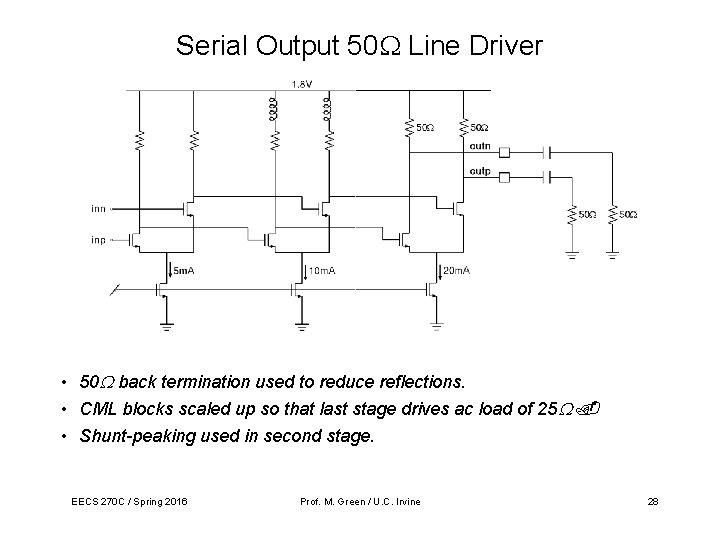

Serial Output 50 Line Driver • 50 back termination used to reduce reflections. • CML blocks scaled up so that last stage drives ac load of 25 • Shunt-peaking used in second stage. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 28

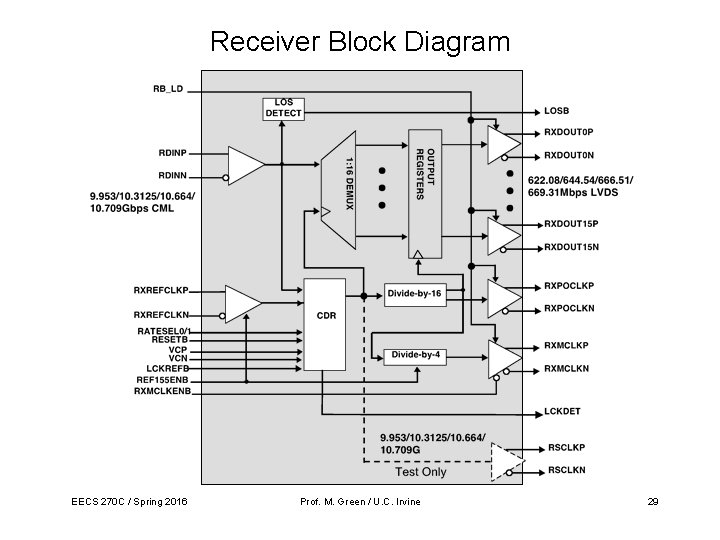

Receiver Block Diagram EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 29

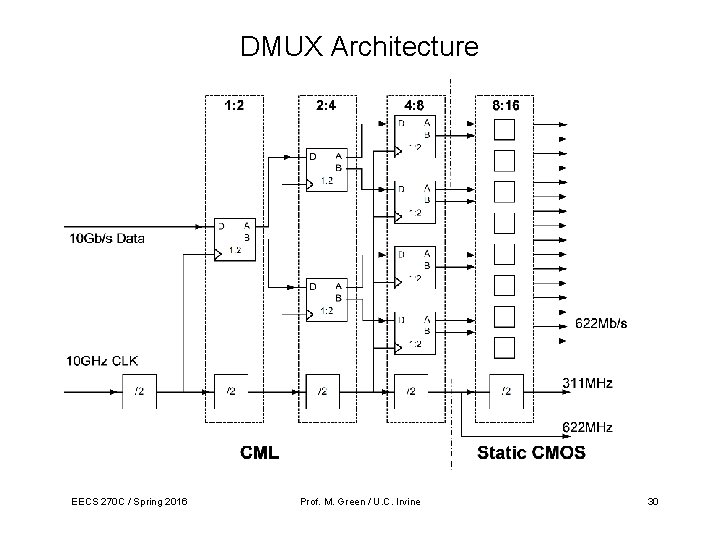

DMUX Architecture EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 30

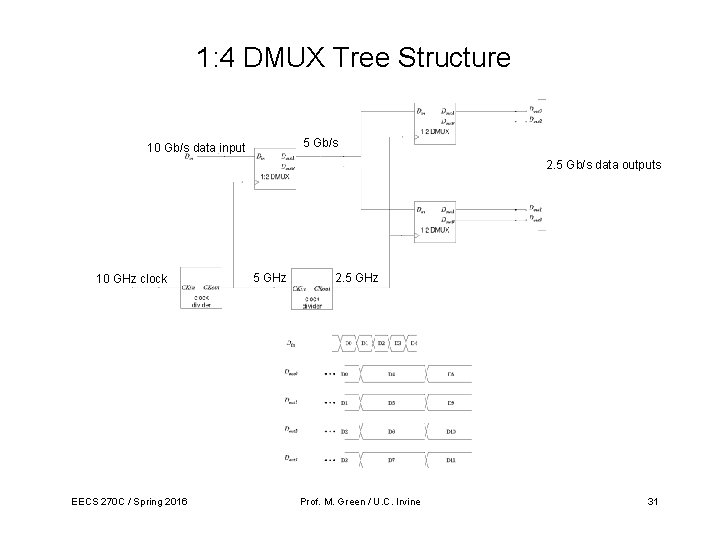

1: 4 DMUX Tree Structure 5 Gb/s 10 Gb/s data input 2. 5 Gb/s data outputs 10 GHz clock EECS 270 C / Spring 2016 5 GHz 2. 5 GHz Prof. M. Green / U. C. Irvine 31

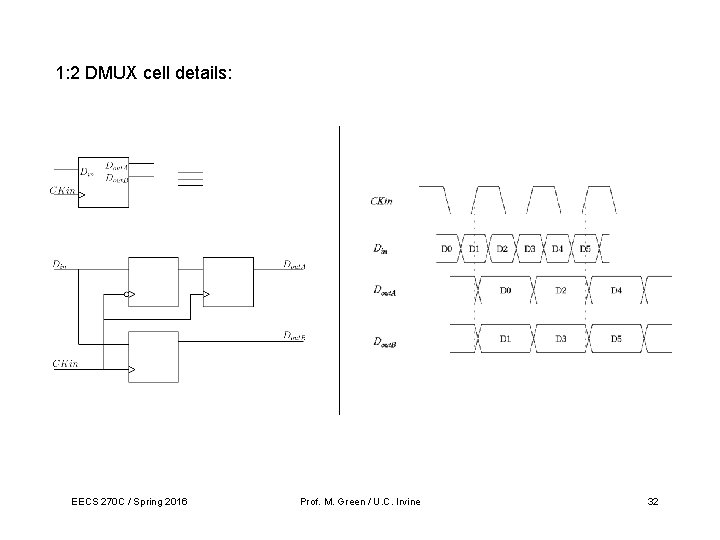

1: 2 DMUX cell details: EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 32

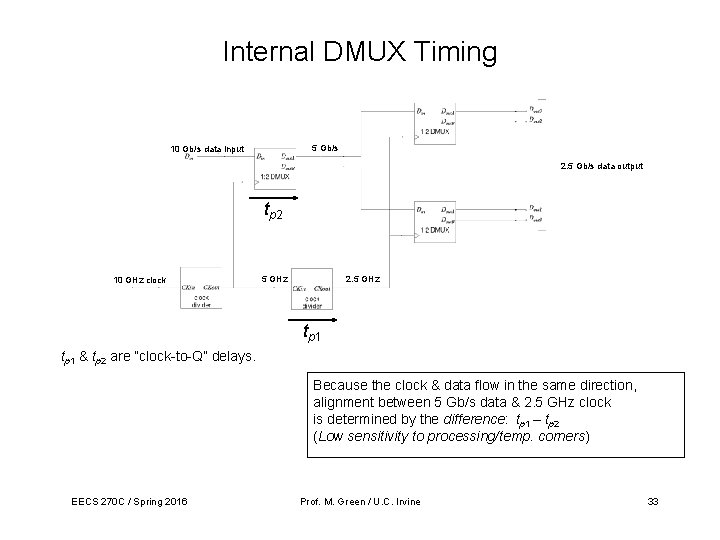

Internal DMUX Timing 5 Gb/s 10 Gb/s data input 2. 5 Gb/s data output tp 2 10 GHz clock 5 GHz 2. 5 GHz tp 1 & tp 2 are “clock-to-Q” delays. Because the clock & data flow in the same direction, alignment between 5 Gb/s data & 2. 5 GHz clock is determined by the difference: tp 1 – tp 2 (Low sensitivity to processing/temp. corners) EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 33

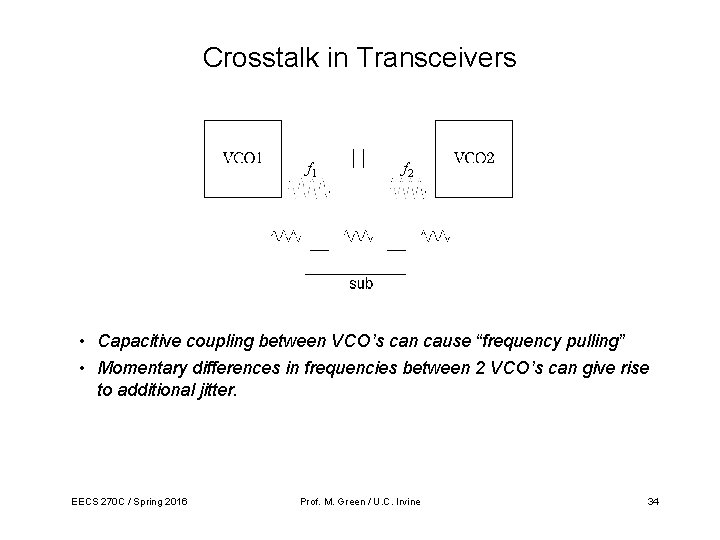

Crosstalk in Transceivers f 1 f 2 • Capacitive coupling between VCO’s can cause “frequency pulling” • Momentary differences in frequencies between 2 VCO’s can give rise to additional jitter. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 34

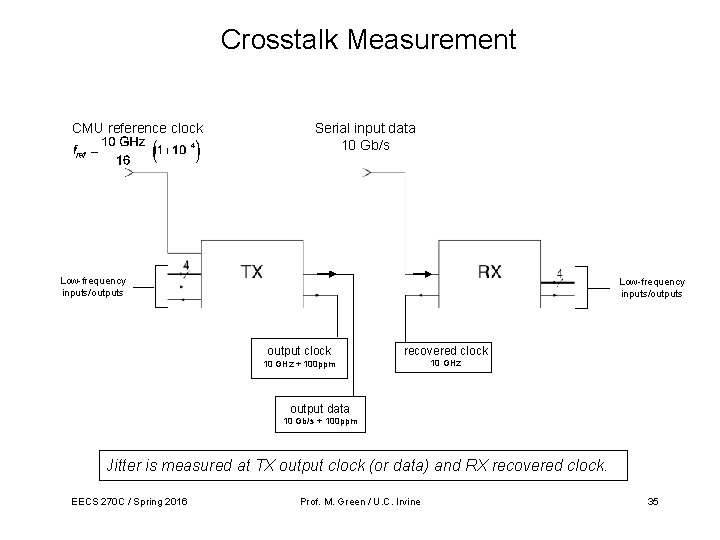

Crosstalk Measurement CMU reference clock Serial input data 10 Gb/s Low-frequency inputs/outputs output clock recovered clock 10 GHz + 100 ppm 10 GHz output data 10 Gb/s + 100 ppm Jitter is measured at TX output clock (or data) and RX recovered clock. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 35

Techniques for Reducing Transceiver Crosstalk • Sufficient physical separation between VCO’s • Separate supply connections to package for each block (e. g. , CMU, CDR, MUX, DMUX, FIFO, etc. ) • Ample guard rings to minimize substrate coupling Very difficult to simulate & predict! EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 36

SONET Jitter Specifications 1. Jitter Generation (transmitters) 2. Jitter Tolerance (receivers) 3. Jitter Transfer (repeaters) EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 37

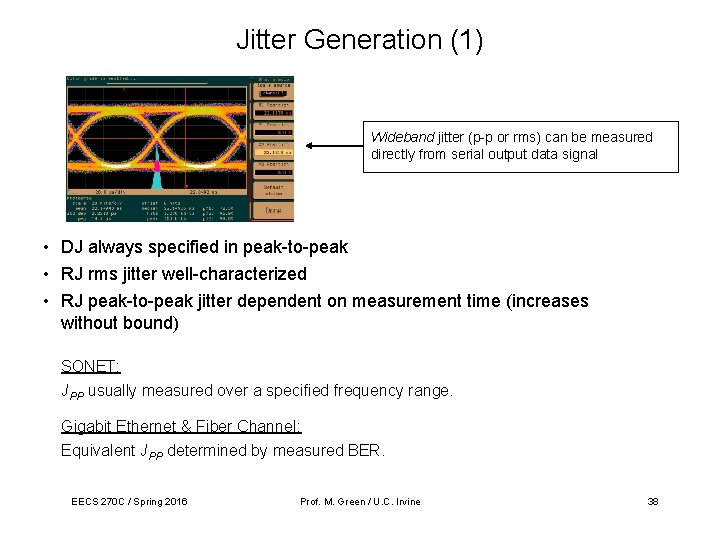

Jitter Generation (1) Wideband jitter (p-p or rms) can be measured directly from serial output data signal • DJ always specified in peak-to-peak • RJ rms jitter well-characterized • RJ peak-to-peak jitter dependent on measurement time (increases without bound) SONET: JPP usually measured over a specified frequency range. Gigabit Ethernet & Fiber Channel: Equivalent JPP determined by measured BER. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 38

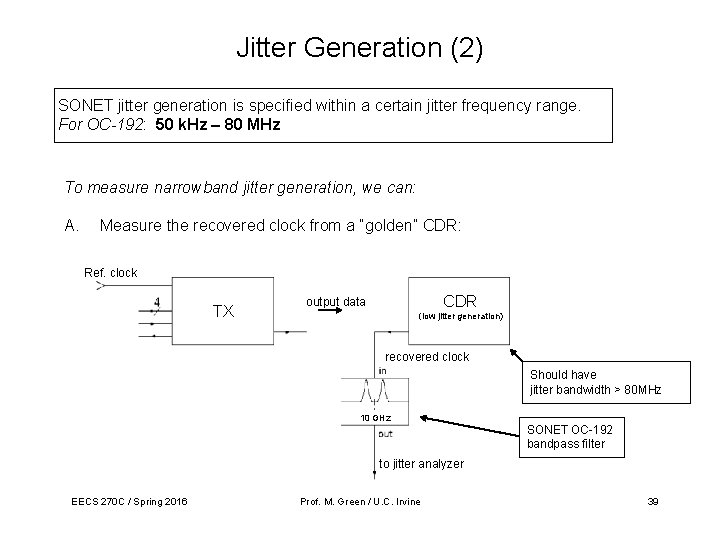

Jitter Generation (2) SONET jitter generation is specified within a certain jitter frequency range. For OC-192: 50 k. Hz – 80 MHz To measure narrowband jitter generation, we can: A. Measure the recovered clock from a “golden” CDR: Ref. clock TX CDR output data (low jitter generation) recovered clock Should have jitter bandwidth > 80 MHz 10 GHz SONET OC-192 bandpass filter to jitter analyzer EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 39

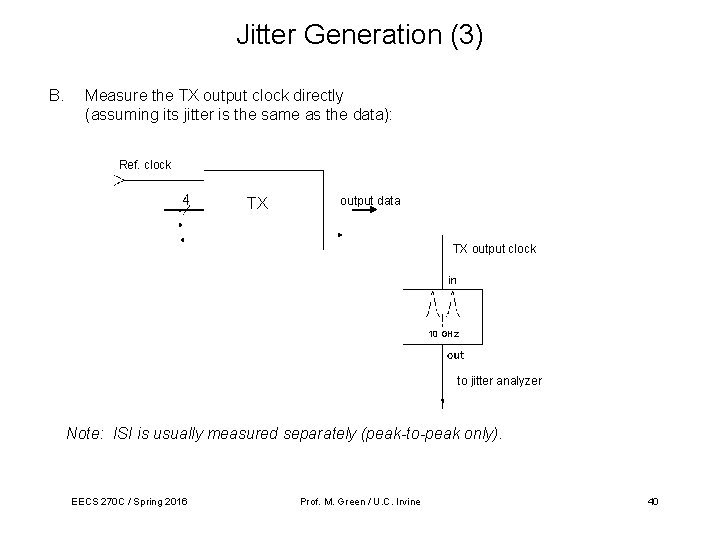

Jitter Generation (3) B. Measure the TX output clock directly (assuming its jitter is the same as the data): Ref. clock TX output data TX output clock 10 GHz to jitter analyzer Note: ISI is usually measured separately (peak-to-peak only). EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 40

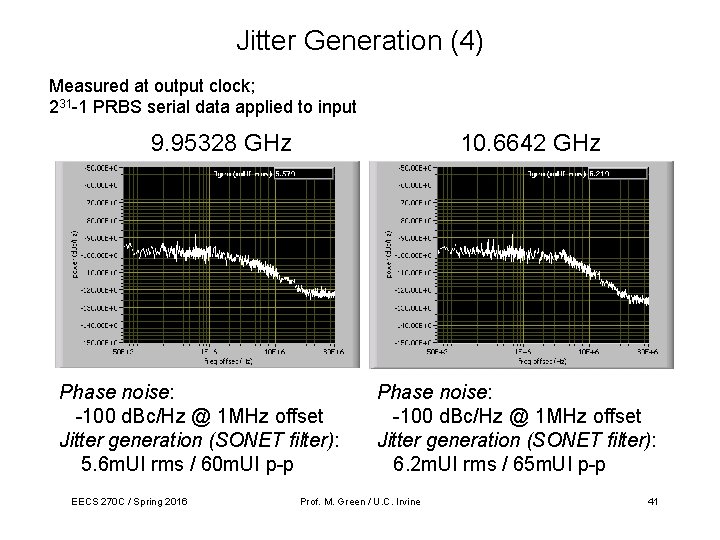

Jitter Generation (4) Measured at output clock; 231 -1 PRBS serial data applied to input 9. 95328 GHz 10. 6642 GHz Phase noise: -100 d. Bc/Hz @ 1 MHz offset Jitter generation (SONET filter): 5. 6 m. UI rms / 60 m. UI p-p EECS 270 C / Spring 2016 Phase noise: -100 d. Bc/Hz @ 1 MHz offset Jitter generation (SONET filter): 6. 2 m. UI rms / 65 m. UI p-p Prof. M. Green / U. C. Irvine 41

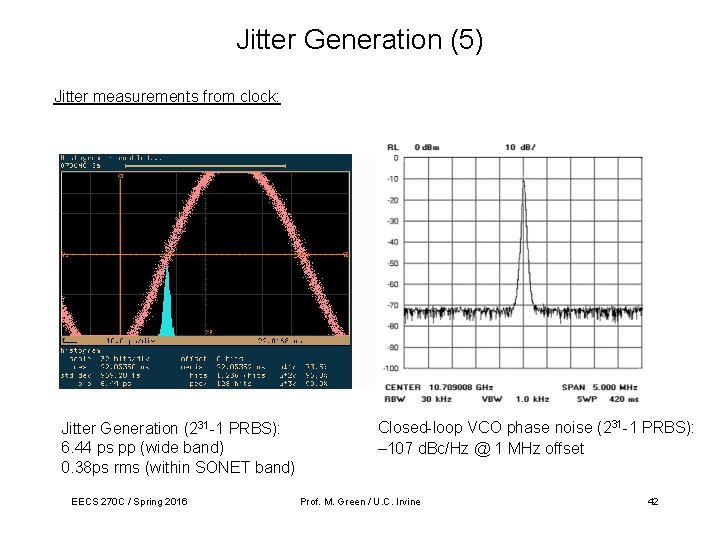

Jitter Generation (5) Jitter measurements from clock: Jitter Generation (231 -1 PRBS): 6. 44 ps pp (wide band) 0. 38 ps rms (within SONET band) EECS 270 C / Spring 2016 Closed-loop VCO phase noise (231 -1 PRBS): – 107 d. Bc/Hz @ 1 MHz offset Prof. M. Green / U. C. Irvine 42

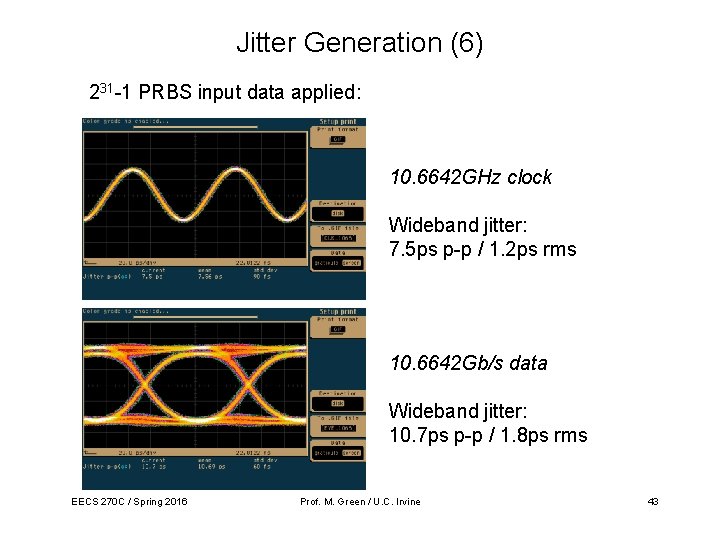

Jitter Generation (6) 231 -1 PRBS input data applied: 10. 6642 GHz clock Wideband jitter: 7. 5 ps p-p / 1. 2 ps rms 10. 6642 Gb/s data Wideband jitter: 10. 7 ps p-p / 1. 8 ps rms EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 43

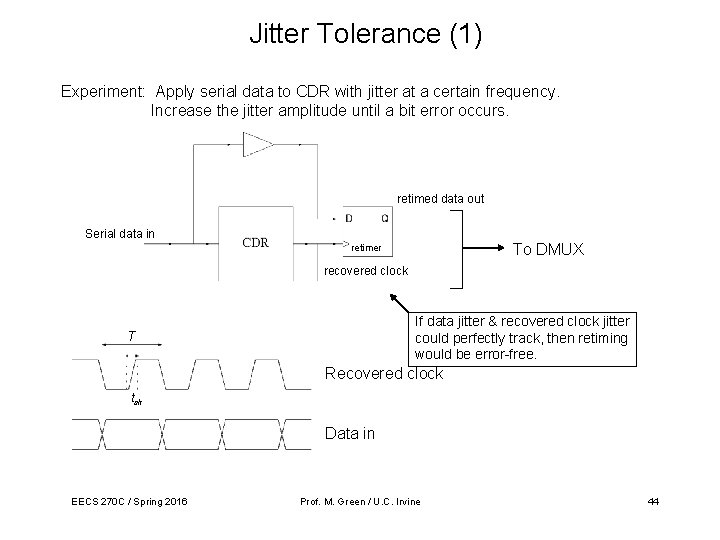

Jitter Tolerance (1) Experiment: Apply serial data to CDR with jitter at a certain frequency. Increase the jitter amplitude until a bit error occurs. retimed data out Serial data in To DMUX retimer recovered clock If data jitter & recovered clock jitter could perfectly track, then retiming would be error-free. T Recovered clock tsh Data in EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 44

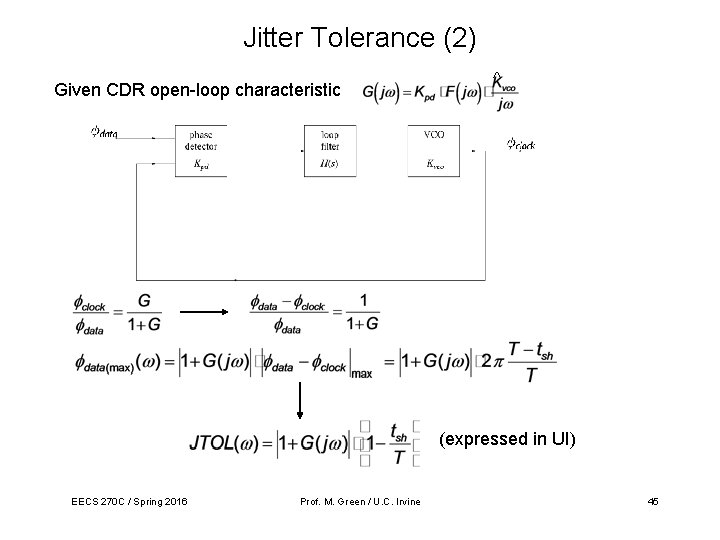

Jitter Tolerance (2) Given CDR open-loop characteristic ^ (expressed in UI) EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 45

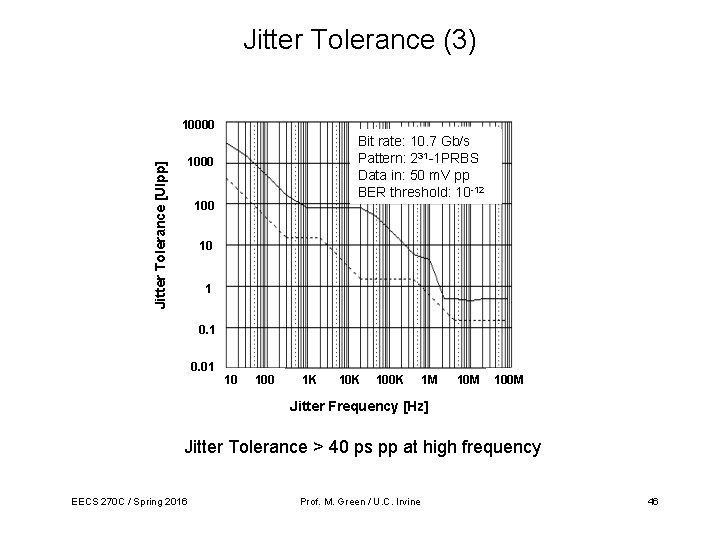

Jitter Tolerance (3) 10000 rate: 10. 7 Gb/s Bit rate: Bit 10. 7 Gb/s Pattern: 231 -1 PRBS 31 BER 10 -12 Pattern: 2 threshold: -1 PRBS Data in: 50 m. V pp BER threshold: 10 -12 Jitter Tolerance [UIpp] 1000 10 1 0. 01 10 100 1 K 100 K 1 M 100 M Jitter Frequency (Hz) [Hz] Jitter Frequency Jitter Tolerance > 40 ps pp at high frequency EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 46

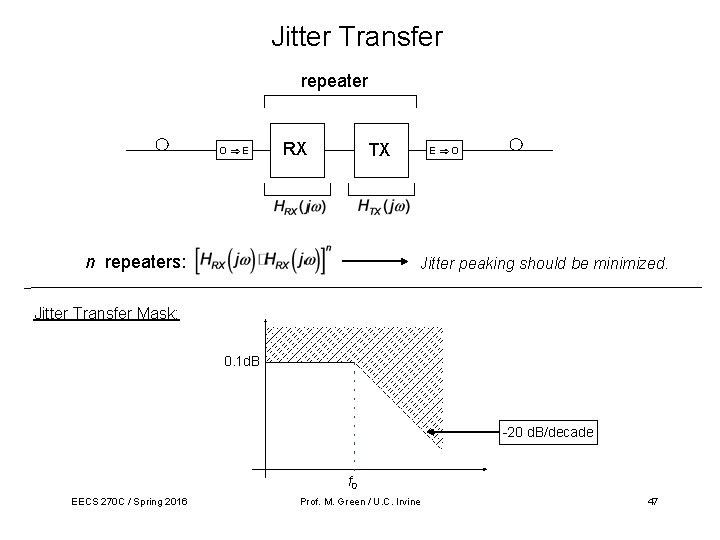

Jitter Transfer repeater O E RX TX n repeaters: E O Jitter peaking should be minimized. Jitter Transfer Mask: 0. 1 d. B -20 d. B/decade f 0 EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 47

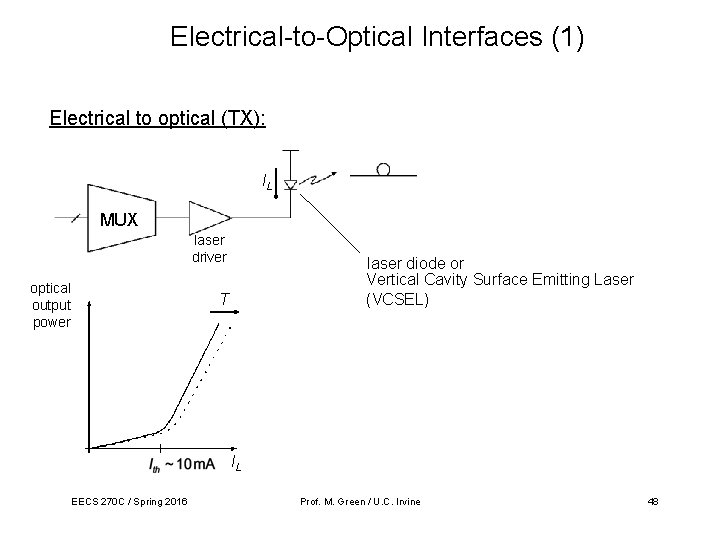

Electrical-to-Optical Interfaces (1) Electrical to optical (TX): IL MUX laser driver optical output power laser diode or Vertical Cavity Surface Emitting Laser (VCSEL) T IL EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 48

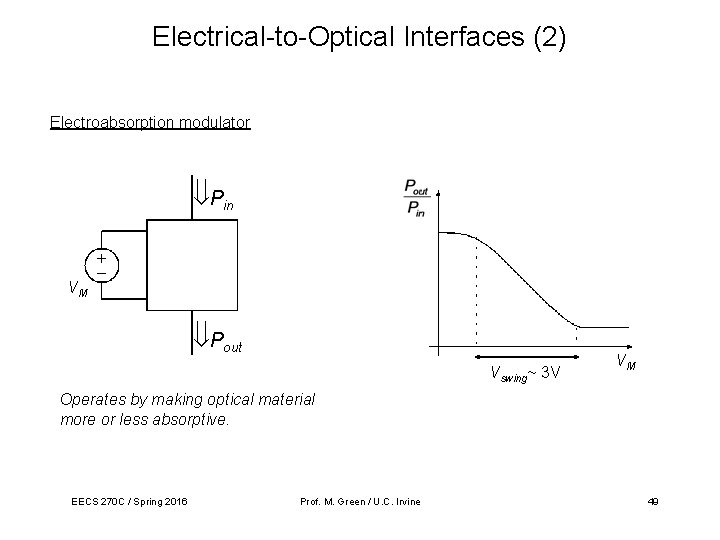

Electrical-to-Optical Interfaces (2) Electroabsorption modulator Pin VM Pout Vswing~ 3 V VM Operates by making optical material more or less absorptive. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 49

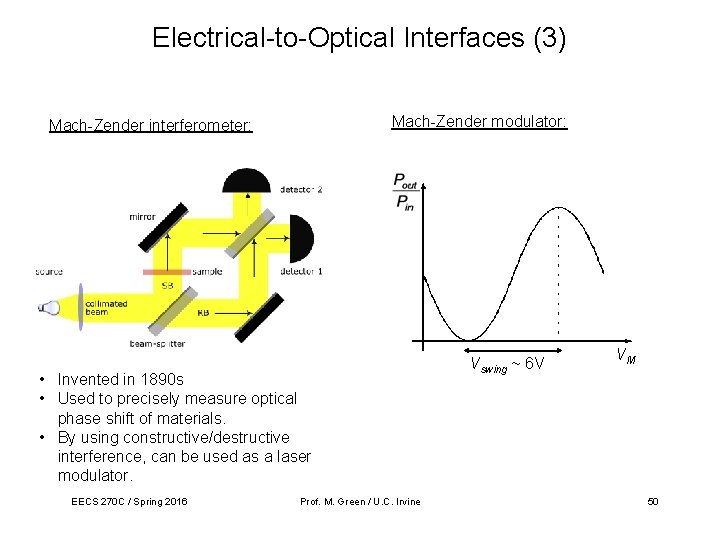

Electrical-to-Optical Interfaces (3) Mach-Zender modulator: Mach-Zender interferometer: • Invented in 1890 s • Used to precisely measure optical phase shift of materials. • By using constructive/destructive interference, can be used as a laser modulator. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine Vswing ~ 6 V VM 50

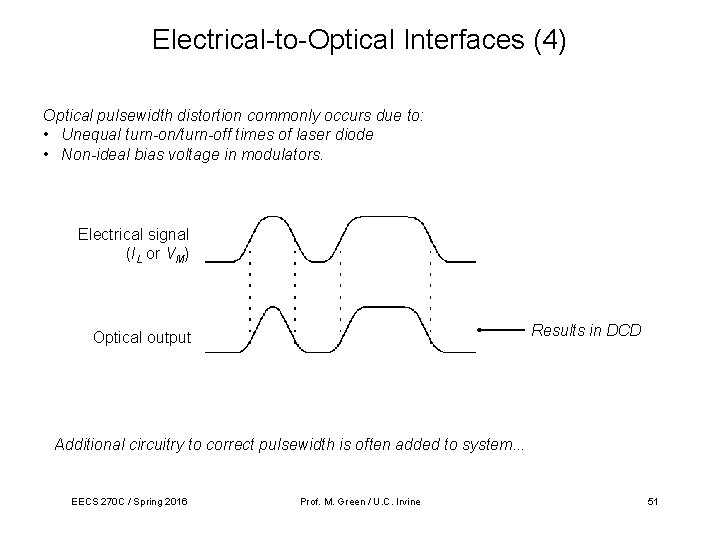

Electrical-to-Optical Interfaces (4) Optical pulsewidth distortion commonly occurs due to: • Unequal turn-on/turn-off times of laser diode • Non-ideal bias voltage in modulators. Electrical signal (IL or VM) Results in DCD Optical output Additional circuitry to correct pulsewidth is often added to system. . . EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 51

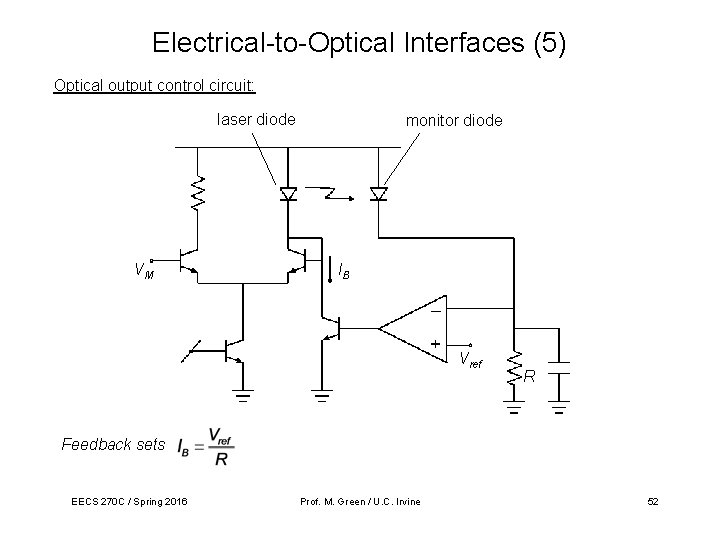

Electrical-to-Optical Interfaces (5) Optical output control circuit: laser diode VM monitor diode IB Vref R Feedback sets EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 52

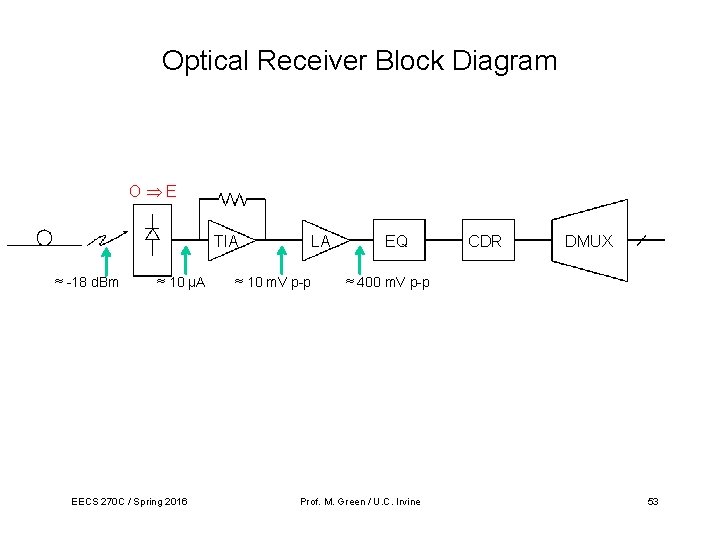

Optical Receiver Block Diagram O E TIA ≈ -18 d. Bm ≈ 10 µA EECS 270 C / Spring 2016 LA ≈ 10 m. V p-p EQ CDR DMUX ≈ 400 m. V p-p Prof. M. Green / U. C. Irvine 53

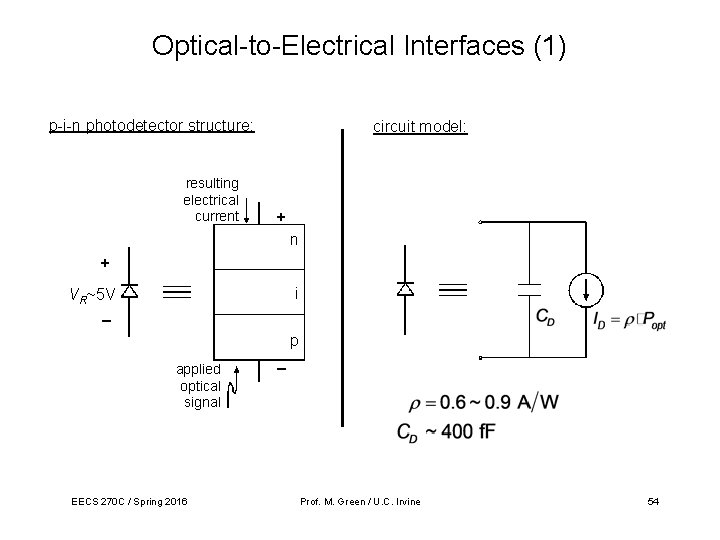

Optical-to-Electrical Interfaces (1) p-i-n photodetector structure: resulting electrical current circuit model: + n + i VR~5 V _ p applied optical signal EECS 270 C / Spring 2016 _ Prof. M. Green / U. C. Irvine 54

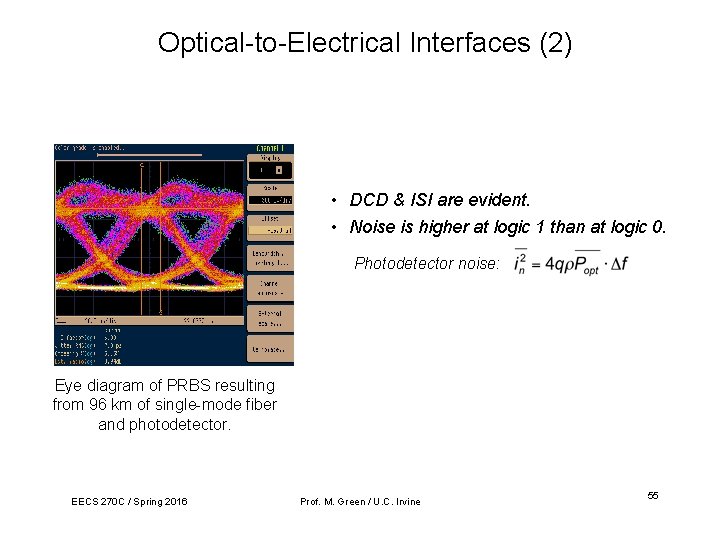

Optical-to-Electrical Interfaces (2) • DCD & ISI are evident. • Noise is higher at logic 1 than at logic 0. Photodetector noise: Eye diagram of PRBS resulting from 96 km of single-mode fiber and photodetector. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 55

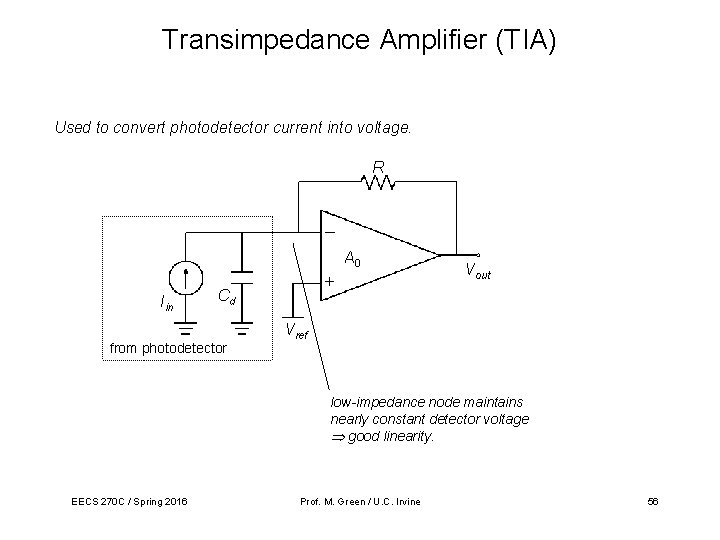

Transimpedance Amplifier (TIA) Used to convert photodetector current into voltage. R A 0 Iin Vout Cd from photodetector Vref low-impedance node maintains nearly constant detector voltage good linearity. EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 56

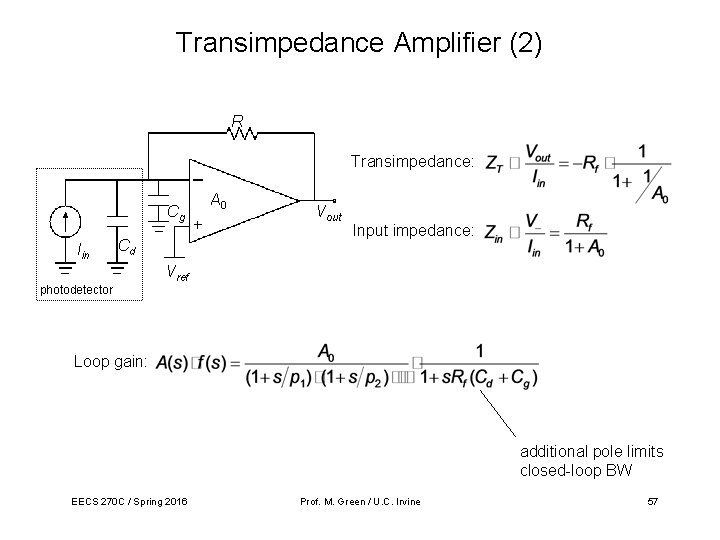

Transimpedance Amplifier (2) R Transimpedance: Cg Iin Cd photodetector A 0 Vout Input impedance: Vref Loop gain: additional pole limits closed-loop BW EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 57

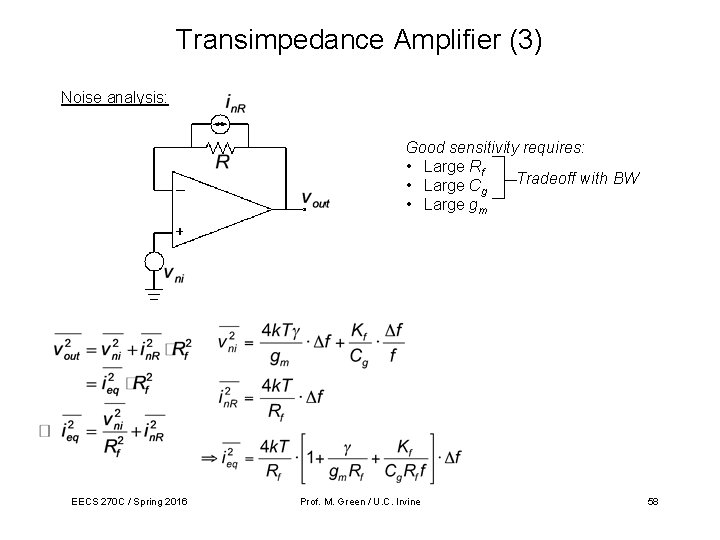

Transimpedance Amplifier (3) Noise analysis: Good sensitivity requires: • Large Rf Tradeoff with BW • Large Cg • Large gm EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 58

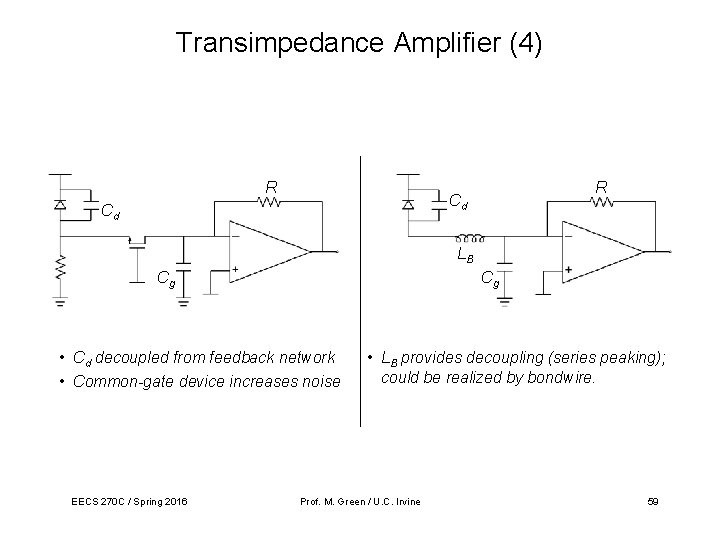

Transimpedance Amplifier (4) R R Cd Cd LB Cg Cg • Cd decoupled from feedback network • Common-gate device increases noise EECS 270 C / Spring 2016 • LB provides decoupling (series peaking); could be realized by bondwire. Prof. M. Green / U. C. Irvine 59

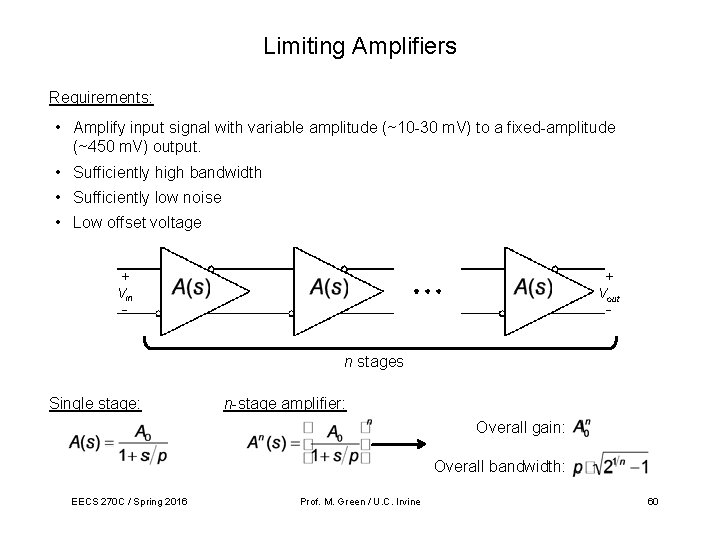

Limiting Amplifiers Requirements: • Amplify input signal with variable amplitude (~10 -30 m. V) to a fixed-amplitude (~450 m. V) output. • Sufficiently high bandwidth • Sufficiently low noise • Low offset voltage + Vin + Vout − − n stages Single stage: n-stage amplifier: Overall gain: Overall bandwidth: EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 60

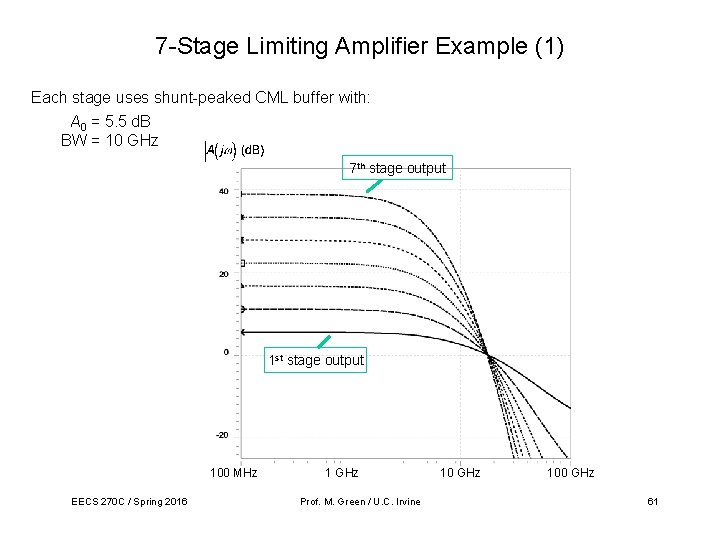

7 -Stage Limiting Amplifier Example (1) Each stage uses shunt-peaked CML buffer with: A 0 = 5. 5 d. B BW = 10 GHz 7 th stage output 1 st stage output 100 MHz EECS 270 C / Spring 2016 1 GHz Prof. M. Green / U. C. Irvine 10 GHz 100 GHz 61

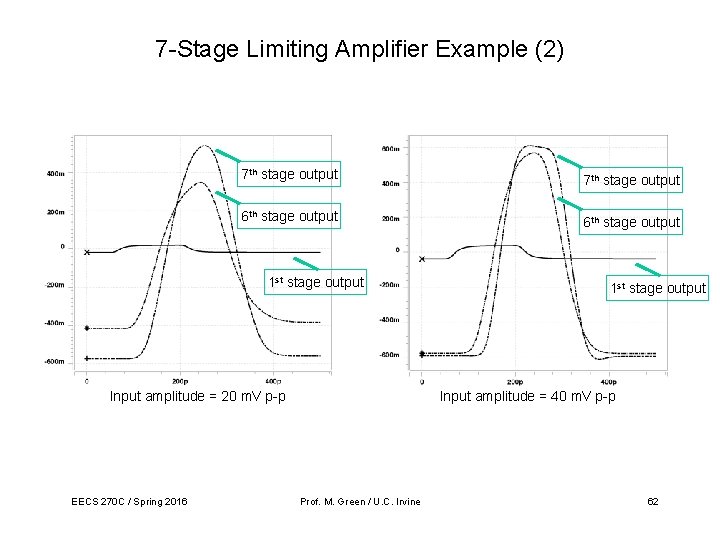

7 -Stage Limiting Amplifier Example (2) 7 th stage output 6 th stage output 1 st stage output Input amplitude = 20 m. V p-p EECS 270 C / Spring 2016 1 st stage output Input amplitude = 40 m. V p-p Prof. M. Green / U. C. Irvine 62

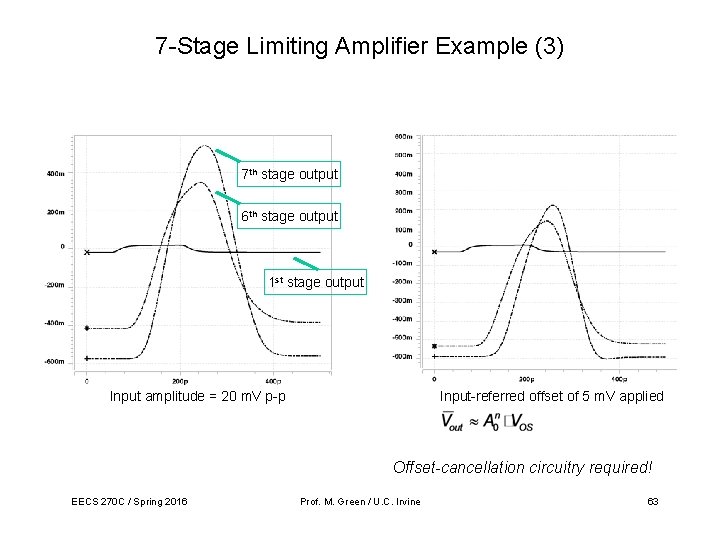

7 -Stage Limiting Amplifier Example (3) 7 th stage output 6 th stage output 1 st stage output Input amplitude = 20 m. V p-p Input-referred offset of 5 m. V applied Offset-cancellation circuitry required! EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 63

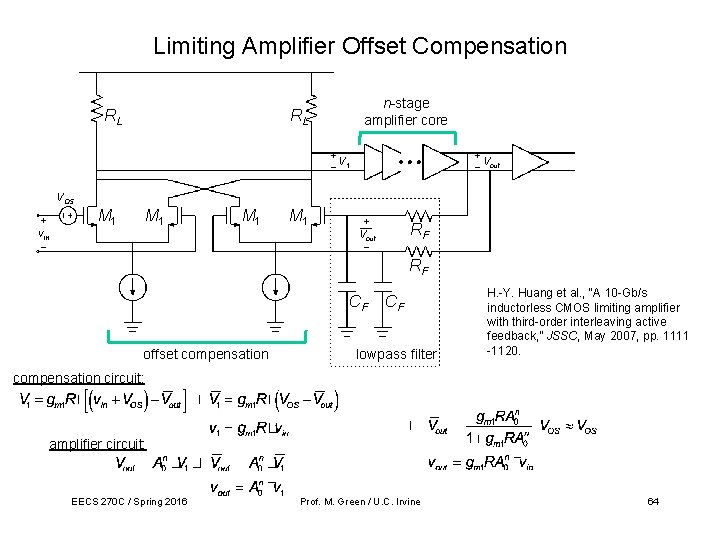

Limiting Amplifier Offset Compensation RL n-stage amplifier core RL + V − 1 + V − out VOS + vin − M 1 M 1 + Vout − RF RF CF offset compensation CF lowpass filter H. -Y. Huang et al. , “A 10 -Gb/s inductorless CMOS limiting amplifier with third-order interleaving active feedback, ” JSSC, May 2007, pp. 1111 -1120. compensation circuit: amplifier circuit: EECS 270 C / Spring 2016 Prof. M. Green / U. C. Irvine 64

- Slides: 64