NVMe Modern PC and CPU Architecture 1 Typical

- Slides: 13

NVMe & Modern PC and CPU Architecture 1

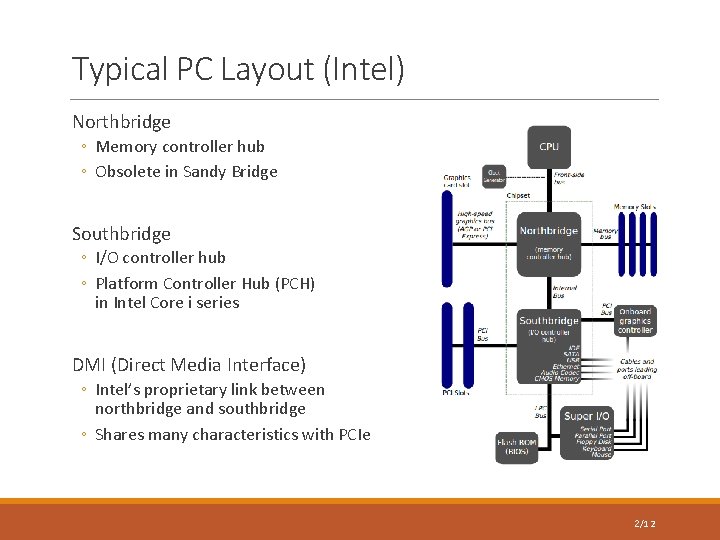

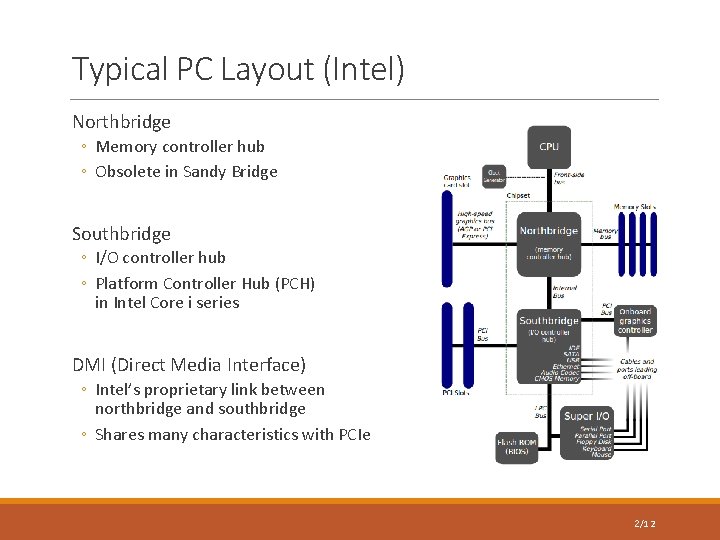

Typical PC Layout (Intel) Northbridge ◦ Memory controller hub ◦ Obsolete in Sandy Bridge Southbridge ◦ I/O controller hub ◦ Platform Controller Hub (PCH) in Intel Core i series DMI (Direct Media Interface) ◦ Intel’s proprietary link between northbridge and southbridge ◦ Shares many characteristics with PCIe 2/12

AHCI (Advanced Host Controller Interface) Adaptor-to-host side interface (HBA) ◦ AHCI supports ◦ Advanced features of SATA (adaptor-to-device side interface) ◦ System interconnect (host bus) PCI/PCIe ◦ Logical translation between two sides Features ◦ Queuing interface ◦ Power management 3/12

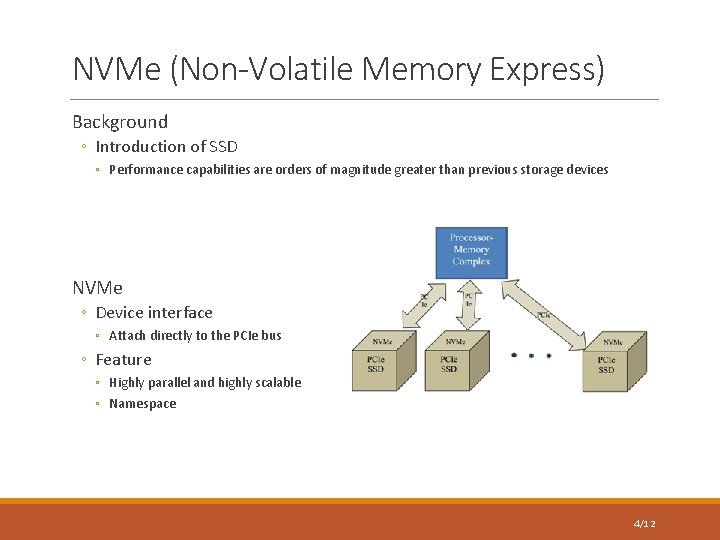

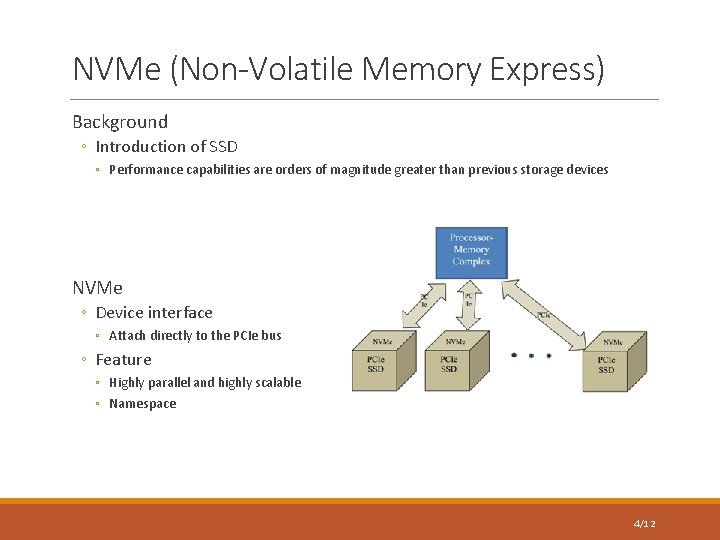

NVMe (Non-Volatile Memory Express) Background ◦ Introduction of SSD ◦ Performance capabilities are orders of magnitude greater than previous storage devices NVMe ◦ Device interface ◦ Attach directly to the PCIe bus ◦ Feature ◦ Highly parallel and highly scalable ◦ Namespace 4/12

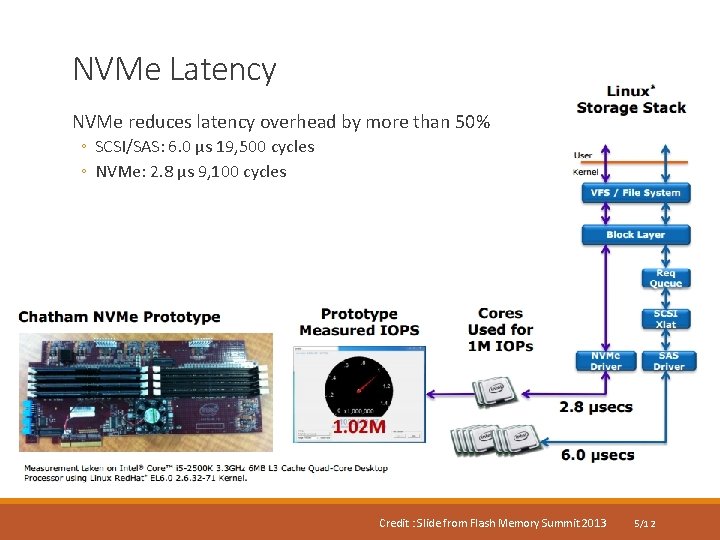

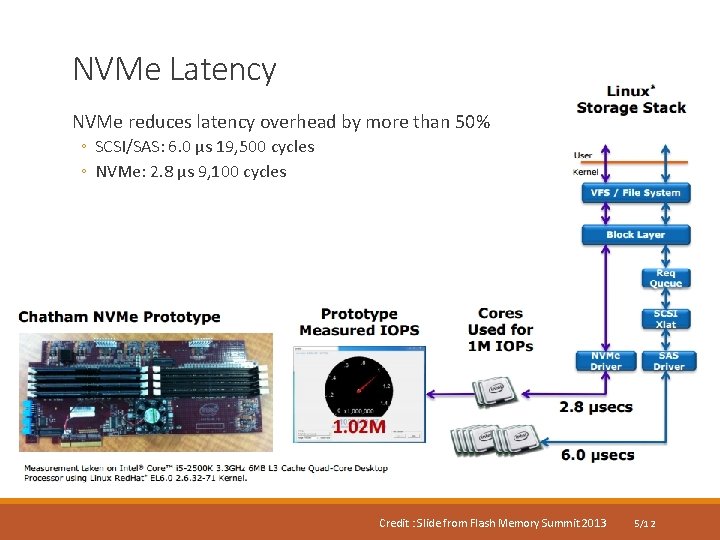

NVMe Latency NVMe reduces latency overhead by more than 50% ◦ SCSI/SAS: 6. 0 µs 19, 500 cycles ◦ NVMe: 2. 8 µs 9, 100 cycles Credit : Slide from Flash Memory Summit 2013 5/12

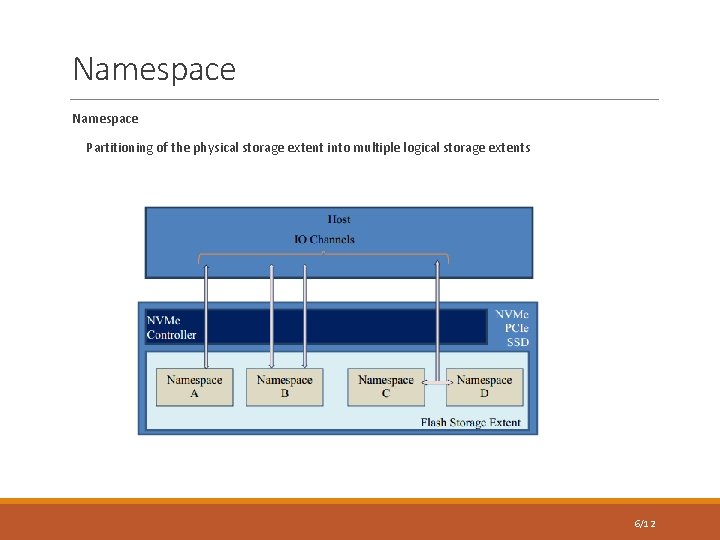

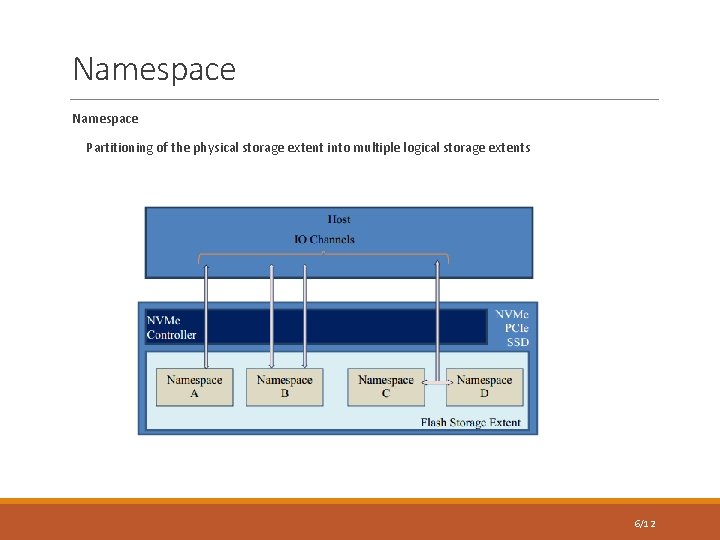

Namespace Partitioning of the physical storage extent into multiple logical storage extents 6/12

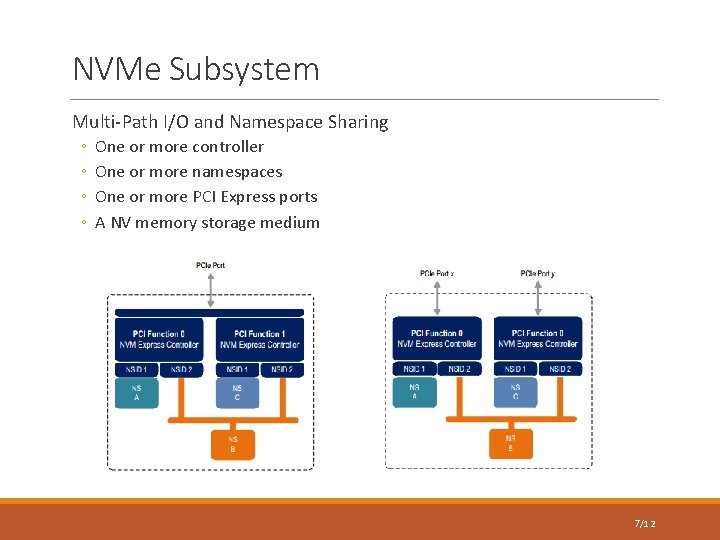

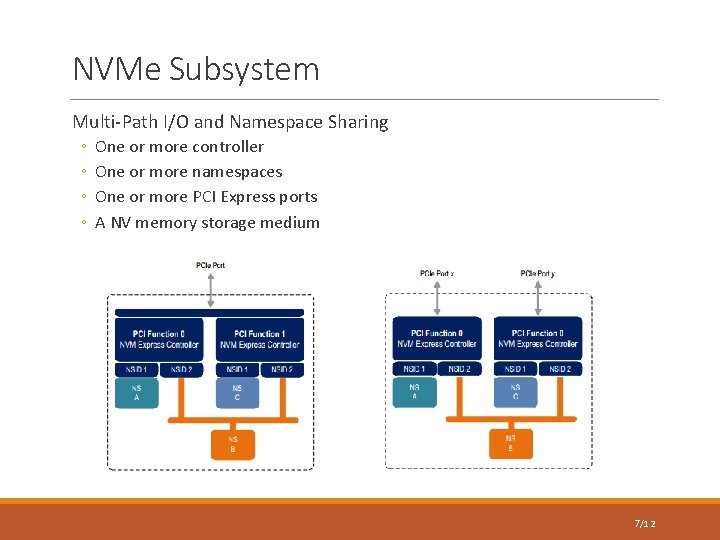

NVMe Subsystem Multi-Path I/O and Namespace Sharing ◦ ◦ One or more controller One or more namespaces One or more PCI Express ports A NV memory storage medium 7/12

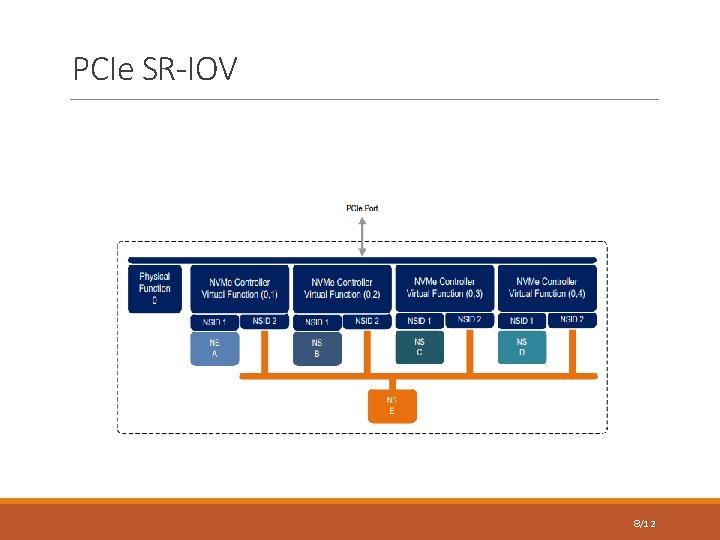

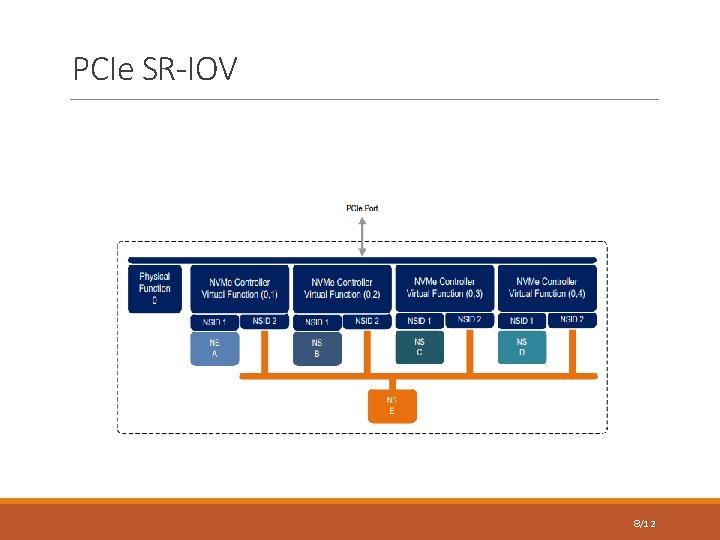

PCIe SR-IOV 8/12

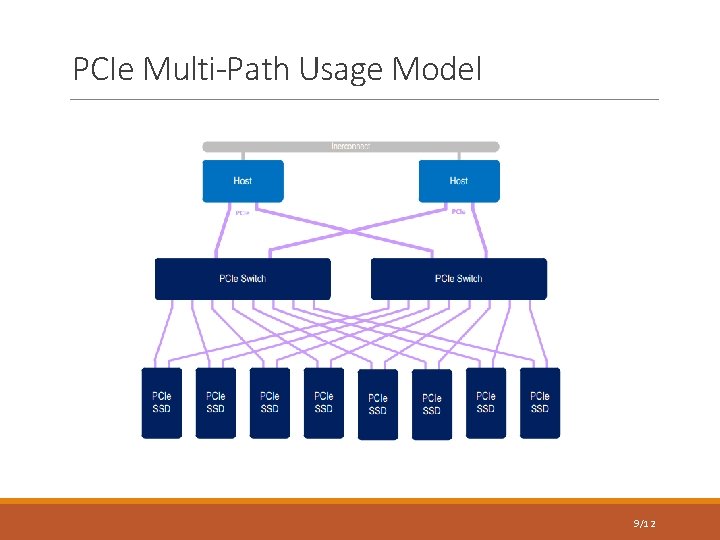

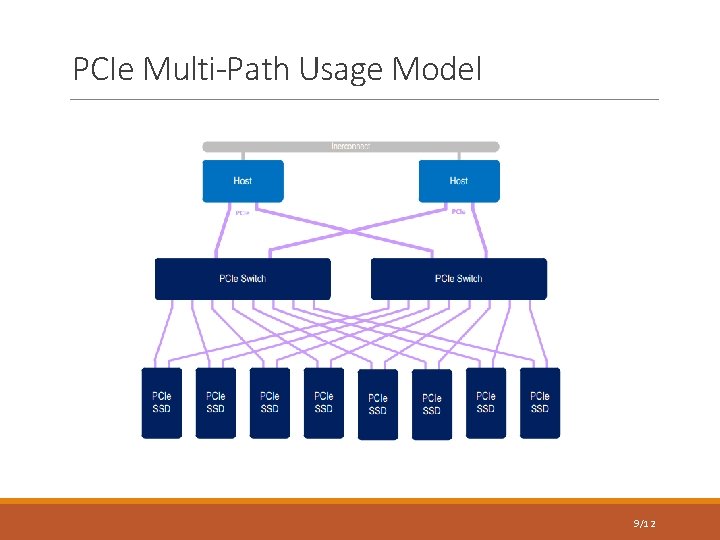

PCIe Multi-Path Usage Model 9/12

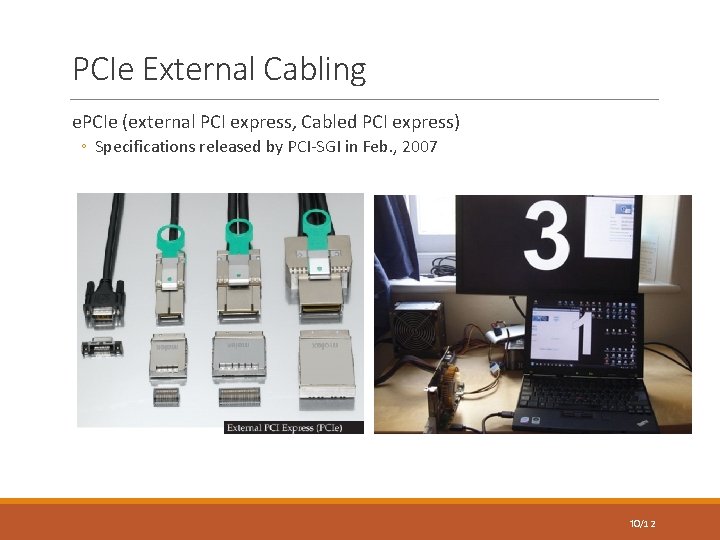

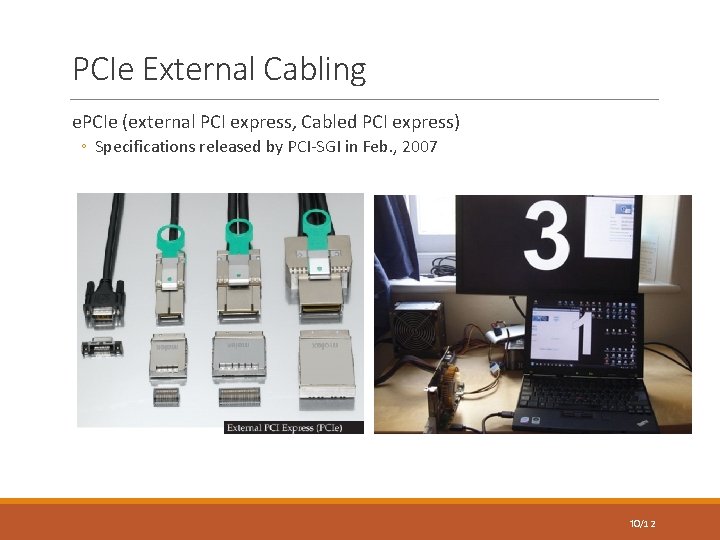

PCIe External Cabling e. PCIe (external PCI express, Cabled PCI express) ◦ Specifications released by PCI-SGI in Feb. , 2007 10/12

Intel Processor Architecture Core i series ◦ Nehalem ◦ FSB -> QPI ◦ Southbridge -> PCH (Lynnfield) ◦ Sandy Bridge ◦ Northbridge disappeared ◦ Ivy Bridge ◦ 22 nm die ◦ Haswell ◦ Transactional Synchronization Extensions (TSX) 11/12

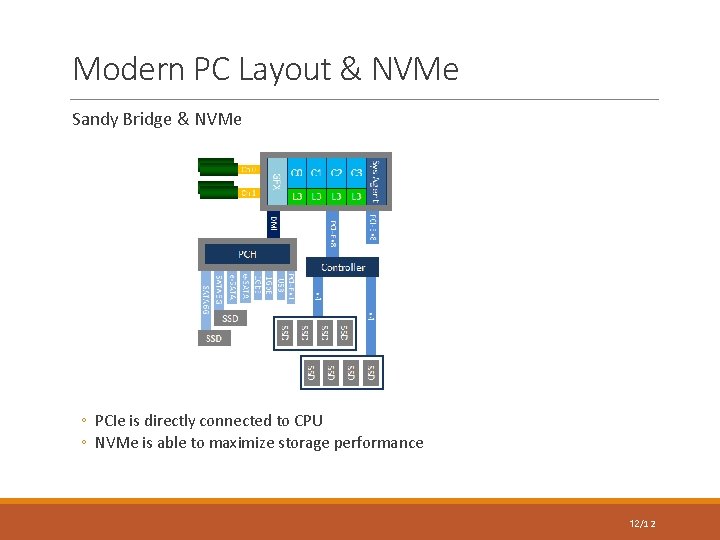

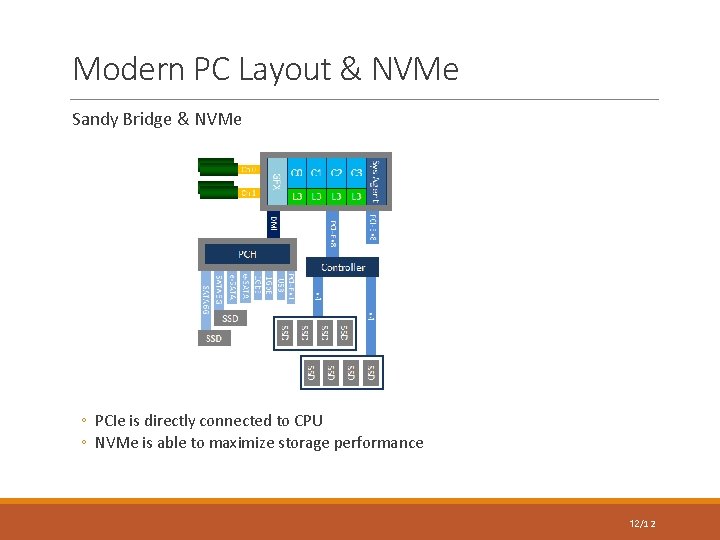

Modern PC Layout & NVMe Sandy Bridge & NVMe ◦ PCIe is directly connected to CPU ◦ NVMe is able to maximize storage performance 12/12

References A Comparison of NVMe and AHCI, 2012 NVM Express: Unlock Your Solid State Drives Potential, Flash Memory Summit 13/12