NTUplace A Partitioning Based Placement Algorithm for LargeScale

NTUplace: A Partitioning Based Placement Algorithm for Large-Scale Designs Tung-Chieh Chen 1, Tien-Chang Hsu 1, Zhe-Wei Jiang 1, and Yao-Wen Chang 1, 2 Graduate Institute of Electronics Engineering 1 Department of Electrical Engineering 2 National Taiwan University Taipei, Taiwan April 6, 2005 1

Outline ․Introduction ․Global placement ¾ ¾ ¾ HPWL modeling with min-cut Whitespace management Look-ahead partitioning ․Legalization ․Detailed placement ¾ Matching based detailed placement ․Results National Taiwan University 2

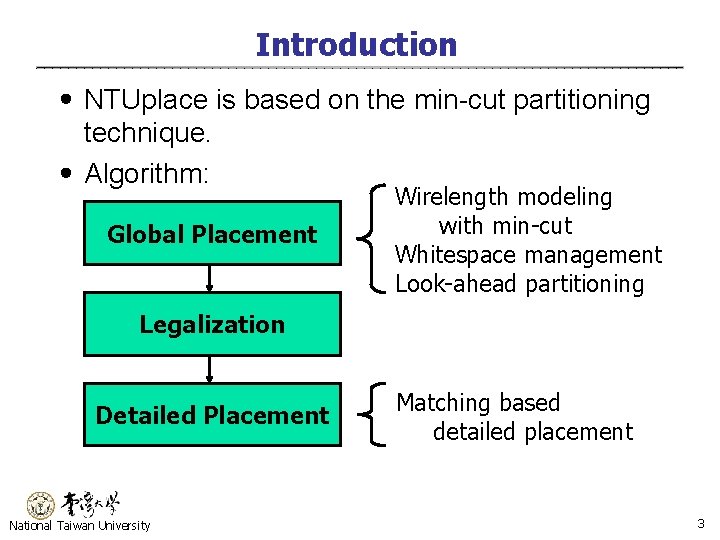

Introduction ․NTUplace is based on the min-cut partitioning technique. ․Algorithm: Global Placement Wirelength modeling with min-cut Whitespace management Look-ahead partitioning Legalization Detailed Placement National Taiwan University Matching based detailed placement 3

HPWL Modeling with Min-Cut ․The HPWL (half-perimeter wirelength) is exactly modeled with the min-cut objective. ¾ Finding the min-cut is equivalent to finding the minimum HPWL. ․The idea is similar to the Bounding Box aware Terminal Propagation (BBTP) in the The. To placer: ¾ Selvakkumaran and Karypis, Technical Report 04 -040, Univ. of Minnesota. Oct. 2004. ․They use 7 cases to discuss the HPWL modeling. ․We derive a unified method for the modeling. ․Our method can be applied to the diagonal-bin repartitioning. ¾ The. To might need to consider tens of cases. National Taiwan University 4

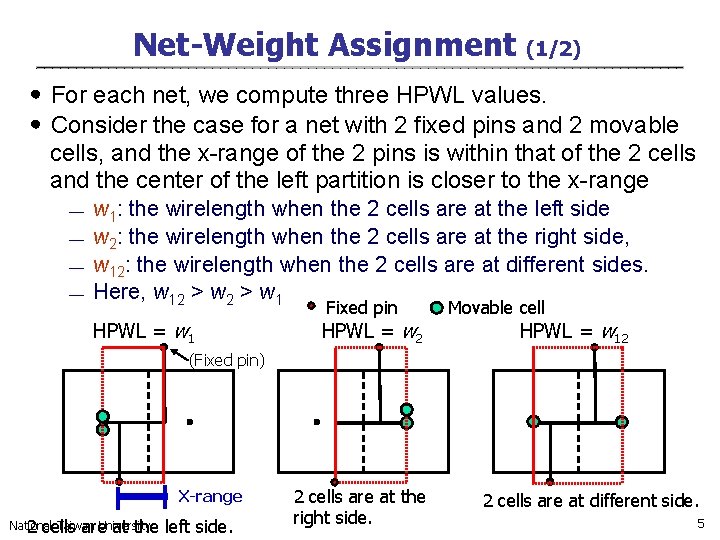

Net-Weight Assignment (1/2) ․For each net, we compute three HPWL values. ․Consider the case for a net with 2 fixed pins and 2 movable cells, and the x-range of the 2 pins is within that of the 2 cells and the center of the left partition is closer to the x-range ¾ ¾ w 1: the wirelength when the 2 cells are at the left side w 2: the wirelength when the 2 cells are at the right side, w 12: the wirelength when the 2 cells are at different sides. Here, w 12 > w 1 HPWL = w 1 Fixed pin HPWL = w 2 Movable cell HPWL = w 12 (Fixed pin) X-range National Taiwan 2 cells are. University at the left side. 2 cells are at the right side. 2 cells are at different side. 5

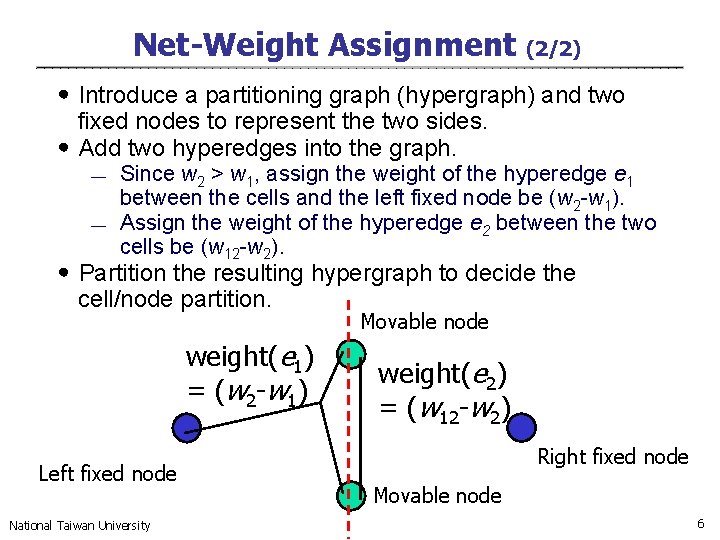

Net-Weight Assignment (2/2) ․Introduce a partitioning graph (hypergraph) and two fixed nodes to represent the two sides. ․Add two hyperedges into the graph. ¾ ¾ Since w 2 > w 1, assign the weight of the hyperedge e 1 between the cells and the left fixed node be (w 2 -w 1). Assign the weight of the hyperedge e 2 between the two cells be (w 12 -w 2). ․Partition the resulting hypergraph to decide the cell/node partition. weight(e 1) = ( w 2 - w 1 ) Left fixed node National Taiwan University Movable node weight(e 2) = (w 12 -w 2) Right fixed node Movable node 6

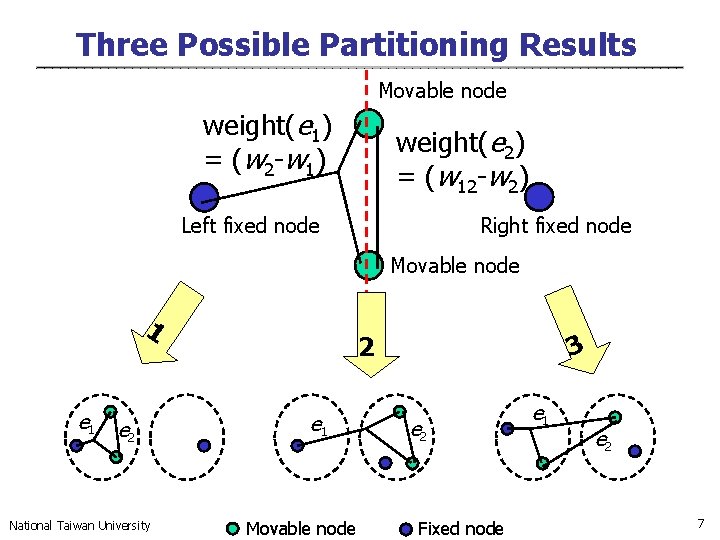

Three Possible Partitioning Results Movable node weight(e 1) = ( w 2 - w 1 ) weight(e 2) = (w 12 -w 2) Left fixed node Right fixed node Movable node 1 e 2 National Taiwan University 2 e 1 Movable node 3 e 2 Fixed node e 1 e 2 7

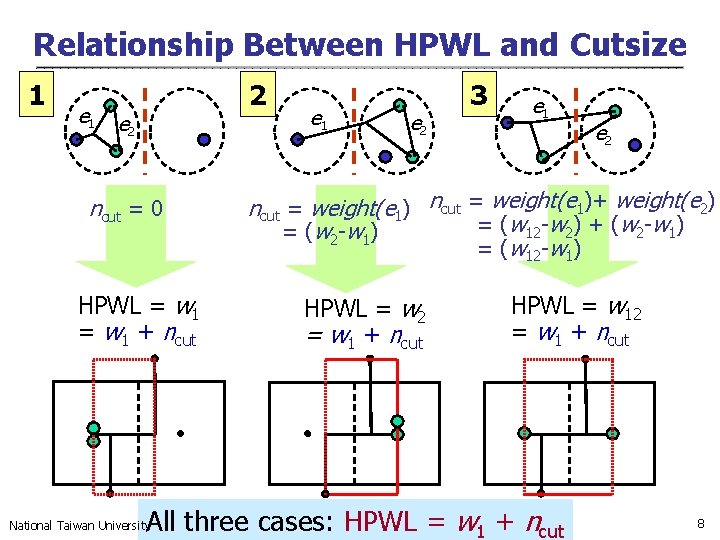

Relationship Between HPWL and Cutsize 1 2 e 2 ncut = 0 HPWL = w 1 + ncut e 1 e 2 3 e 1 ncut = weight(e 1)+ weight(e 2) = (w 12 -w 2) + (w 2 -w 1) = ( w 2 - w 1 ) = (w 12 -w 1) HPWL = w 2 = w 1 + ncut HPWL = w 12 = w 1 + ncut All three cases: HPWL = w 1 + ncut National Taiwan University e 2 8

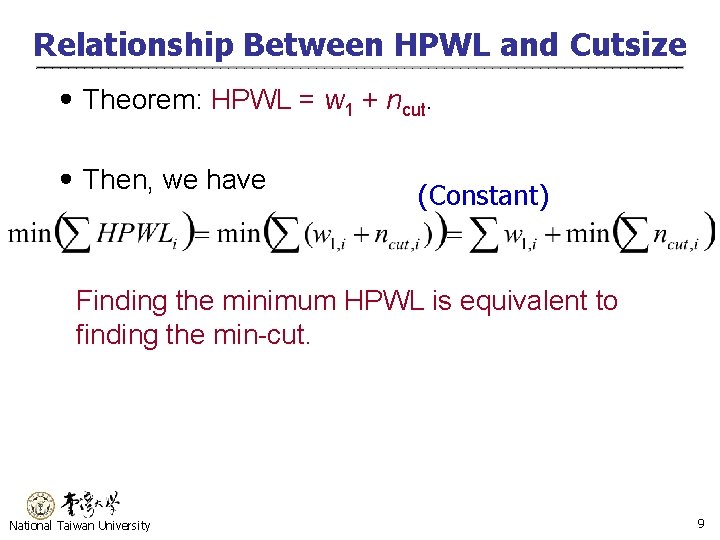

Relationship Between HPWL and Cutsize ․Theorem: HPWL = w 1 + ncut. ․Then, we have (Constant) Finding the minimum HPWL is equivalent to finding the min-cut. National Taiwan University 9

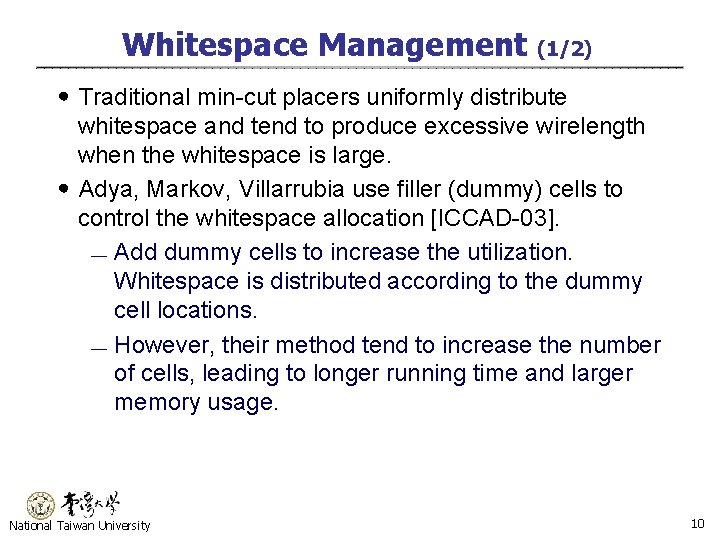

Whitespace Management (1/2) ․Traditional min-cut placers uniformly distribute whitespace and tend to produce excessive wirelength when the whitespace is large. ․Adya, Markov, Villarrubia use filler (dummy) cells to control the whitespace allocation [ICCAD-03]. ¾ Add dummy cells to increase the utilization. Whitespace is distributed according to the dummy cell locations. ¾ However, their method tend to increase the number of cells, leading to longer running time and larger memory usage. National Taiwan University 10

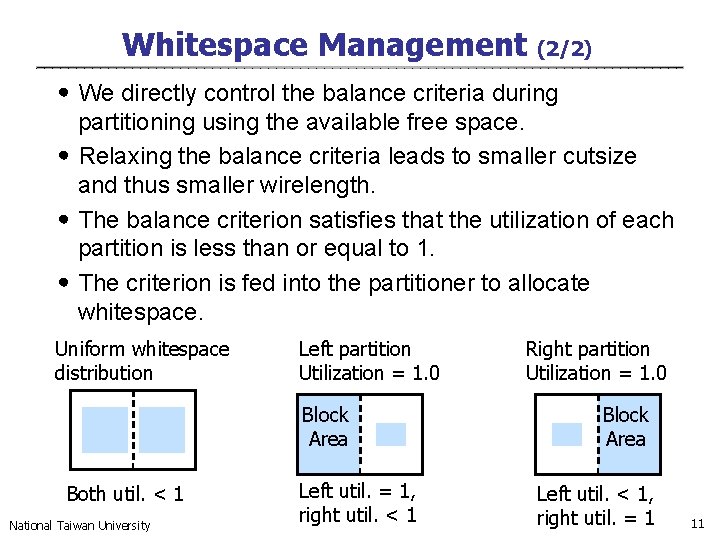

Whitespace Management (2/2) ․We directly control the balance criteria during partitioning using the available free space. ․Relaxing the balance criteria leads to smaller cutsize and thus smaller wirelength. ․The balance criterion satisfies that the utilization of each partition is less than or equal to 1. ․The criterion is fed into the partitioner to allocate whitespace. Uniform whitespace distribution Left partition Utilization = 1. 0 Block Area Both util. < 1 National Taiwan University Left util. = 1, right util. < 1 Right partition Utilization = 1. 0 Block Area Left util. < 1, right util. = 1 11

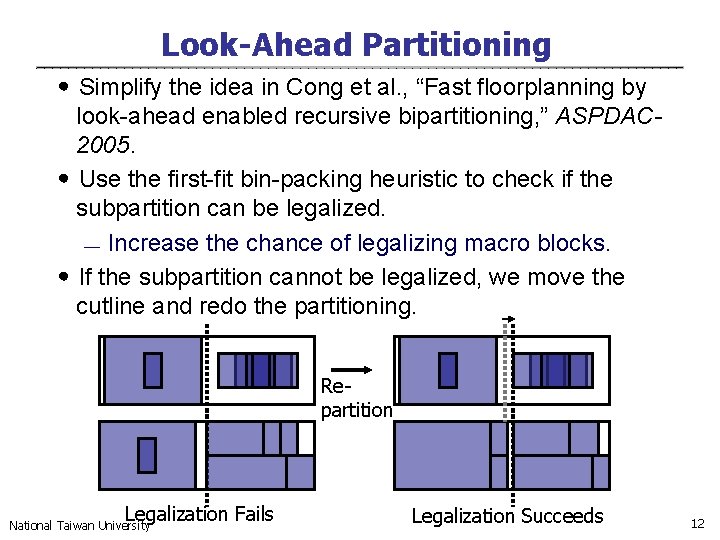

Look-Ahead Partitioning ․Simplify the idea in Cong et al. , “Fast floorplanning by look-ahead enabled recursive bipartitioning, ” ASPDAC 2005. ․Use the first-fit bin-packing heuristic to check if the subpartition can be legalized. ¾ Increase the chance of legalizing macro blocks. ․If the subpartition cannot be legalized, we move the cutline and redo the partitioning. Repartition Legalization Fails National Taiwan University Legalization Succeeds 12

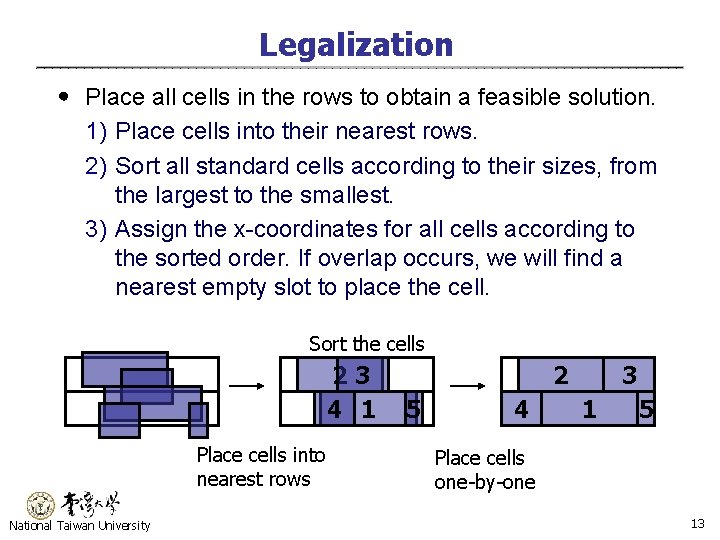

Legalization ․ Place all cells in the rows to obtain a feasible solution. 1) Place cells into their nearest rows. 2) Sort all standard cells according to their sizes, from the largest to the smallest. 3) Assign the x-coordinates for all cells according to the sorted order. If overlap occurs, we will find a nearest empty slot to place the cell. Sort the cells 23 4 1 Place cells into nearest rows National Taiwan University 2 5 4 3 1 5 Place cells one-by-one 13

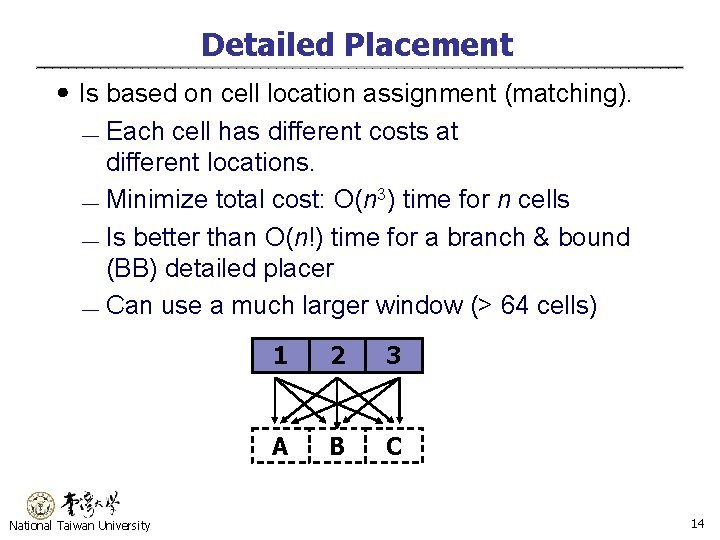

Detailed Placement ․Is based on cell location assignment (matching). Each cell has different costs at different locations. 3 ¾ Minimize total cost: O(n ) time for n cells ¾ Is better than O(n!) time for a branch & bound (BB) detailed placer ¾ Can use a much larger window (> 64 cells) ¾ National Taiwan University 1 2 3 A B C 14

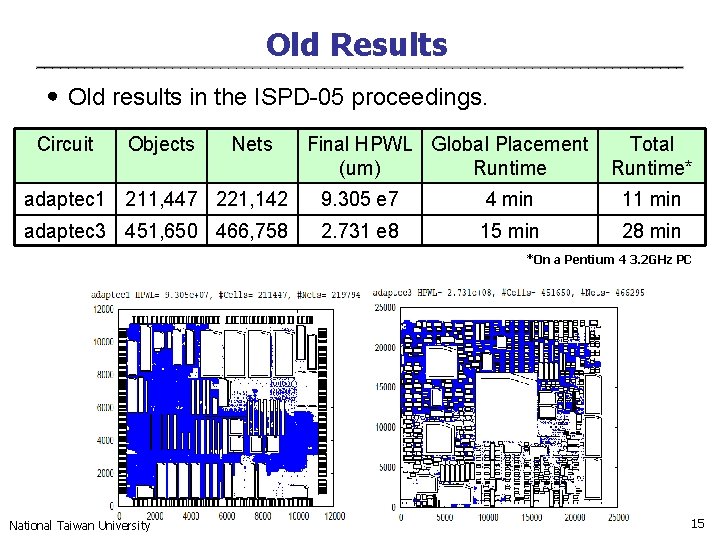

Old Results ․Old results in the ISPD-05 proceedings. Circuit Objects Nets Final HPWL Global Placement (um) Runtime Total Runtime* adaptec 1 211, 447 221, 142 9. 305 e 7 4 min 11 min adaptec 3 451, 650 466, 758 2. 731 e 8 15 min 28 min *On a Pentium 4 3. 2 GHz PC National Taiwan University 15

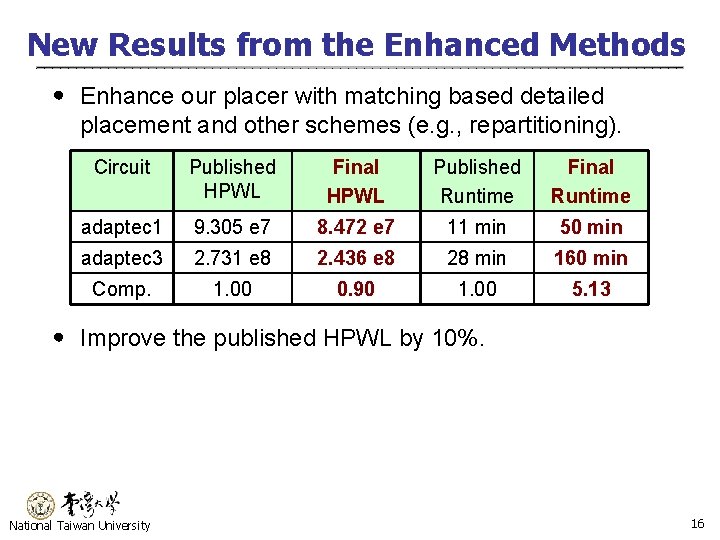

New Results from the Enhanced Methods ․ Enhance our placer with matching based detailed placement and other schemes (e. g. , repartitioning). Circuit Published HPWL Final HPWL Published Runtime Final Runtime adaptec 1 9. 305 e 7 8. 472 e 7 11 min 50 min adaptec 3 2. 731 e 8 2. 436 e 8 28 min 160 min Comp. 1. 00 0. 90 1. 00 5. 13 ․ Improve the published HPWL by 10%. National Taiwan University 16

Thank you for your attention! National Taiwan University 17

- Slides: 17