Nonlinear Neural Networks LAB CHAPTER 10 Introduction to

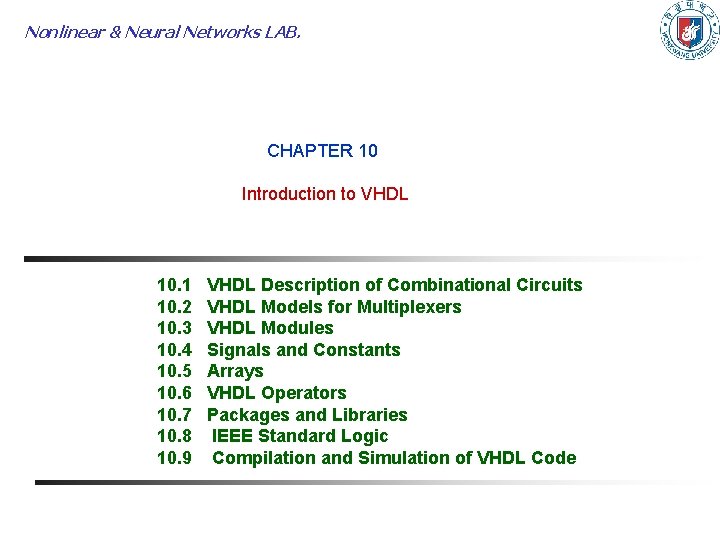

Nonlinear & Neural Networks LAB. CHAPTER 10 Introduction to VHDL 10. 1 10. 2 10. 3 10. 4 10. 5 10. 6 10. 7 10. 8 10. 9 VHDL Description of Combinational Circuits VHDL Models for Multiplexers VHDL Modules Signals and Constants Arrays VHDL Operators Packages and Libraries IEEE Standard Logic Compilation and Simulation of VHDL Code

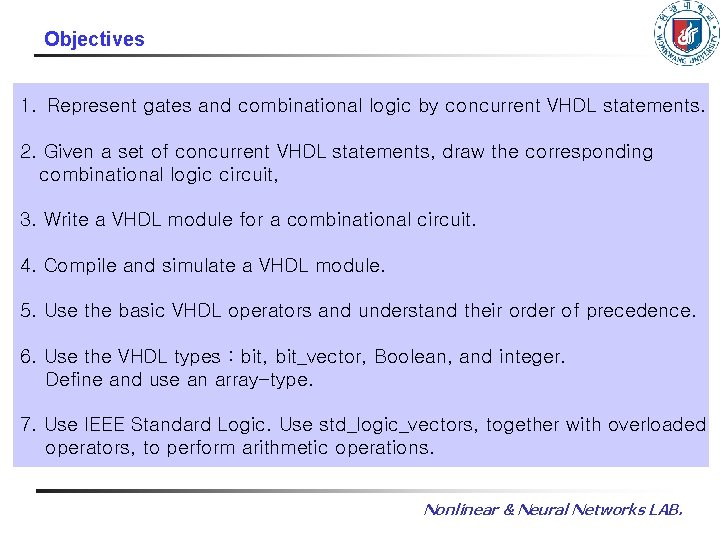

Objectives 1. Represent gates and combinational logic by concurrent VHDL statements. 2. Given a set of concurrent VHDL statements, draw the corresponding combinational logic circuit, 3. Write a VHDL module for a combinational circuit. 4. Compile and simulate a VHDL module. 5. Use the basic VHDL operators and understand their order of precedence. 6. Use the VHDL types : bit, bit_vector, Boolean, and integer. Define and use an array-type. 7. Use IEEE Standard Logic. Use std_logic_vectors, together with overloaded operators, to perform arithmetic operations. Nonlinear & Neural Networks LAB.

Introduction to VHDL Hardware Description Language(HDL) allows a digital system to be designed and debugged at a higher level before implementation VHDL, Verilog VHDL – VHSIC(Very High Speed IC) Hardware Description Language Behavior Level, Data Flow Level, Structural Level Nonlinear & Neural Networks LAB.

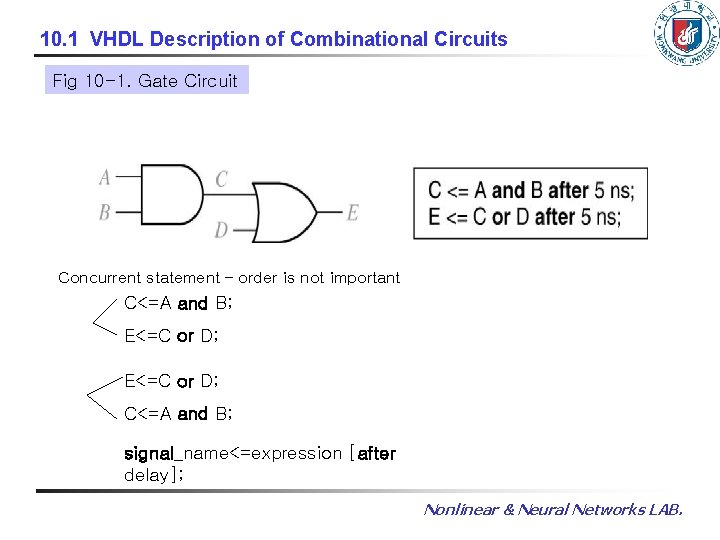

10. 1 VHDL Description of Combinational Circuits Fig 10 -1. Gate Circuit Concurrent statement – order is not important C<=A and B; E<=C or D; C<=A and B; signal_name<=expression [after delay]; Nonlinear & Neural Networks LAB.

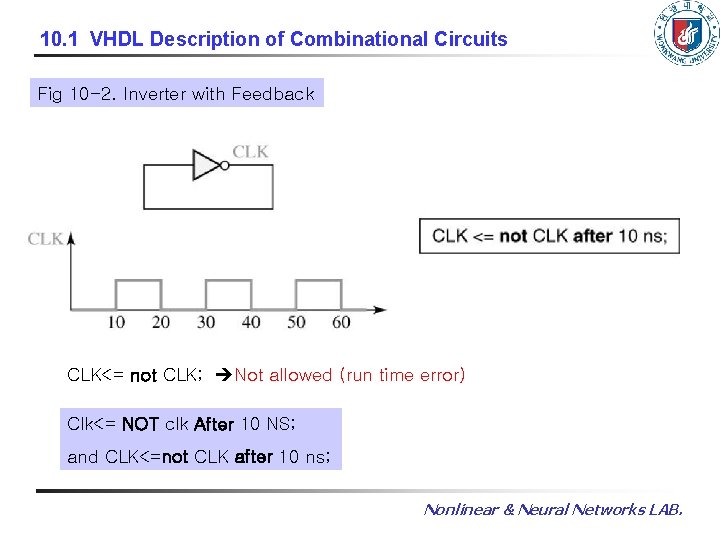

10. 1 VHDL Description of Combinational Circuits Fig 10 -2. Inverter with Feedback CLK<= not CLK; Not allowed (run time error) Clk<= NOT clk After 10 NS; and CLK<=not CLK after 10 ns; Nonlinear & Neural Networks LAB.

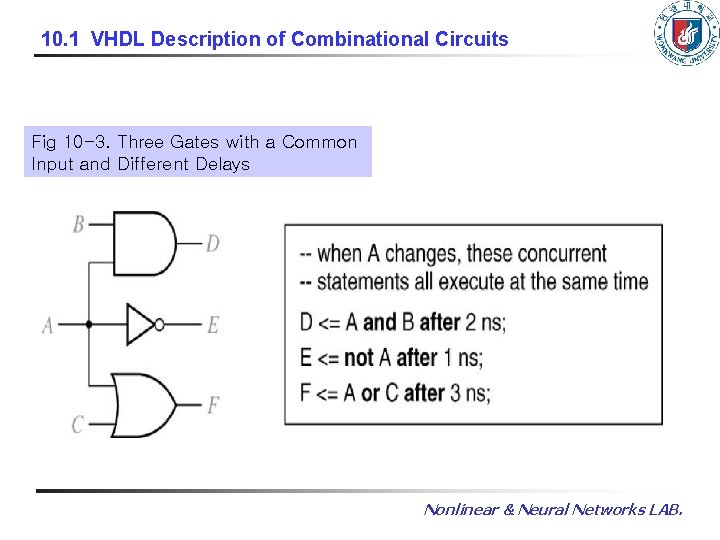

10. 1 VHDL Description of Combinational Circuits Fig 10 -3. Three Gates with a Common Input and Different Delays Nonlinear & Neural Networks LAB.

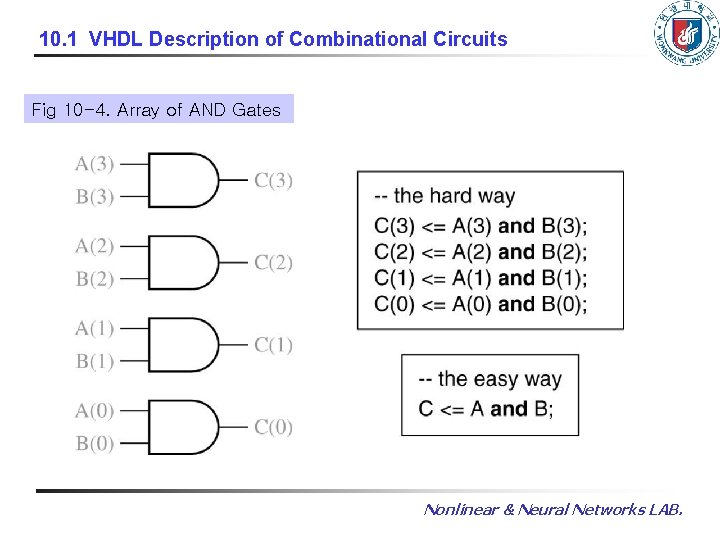

10. 1 VHDL Description of Combinational Circuits Fig 10 -4. Array of AND Gates Nonlinear & Neural Networks LAB.

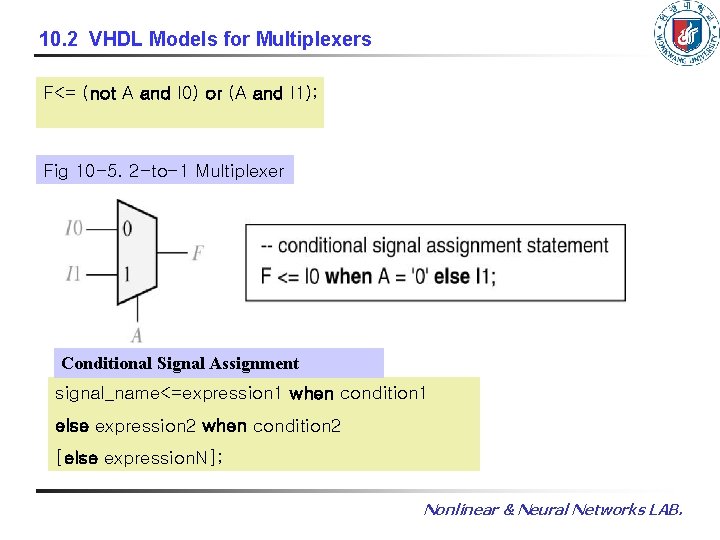

10. 2 VHDL Models for Multiplexers F<= (not A and I 0) or (A and I 1); Fig 10 -5. 2 -to-1 Multiplexer Conditional Signal Assignment signal_name<=expression 1 when condition 1 else expression 2 when condition 2 [else expression. N]; Nonlinear & Neural Networks LAB.

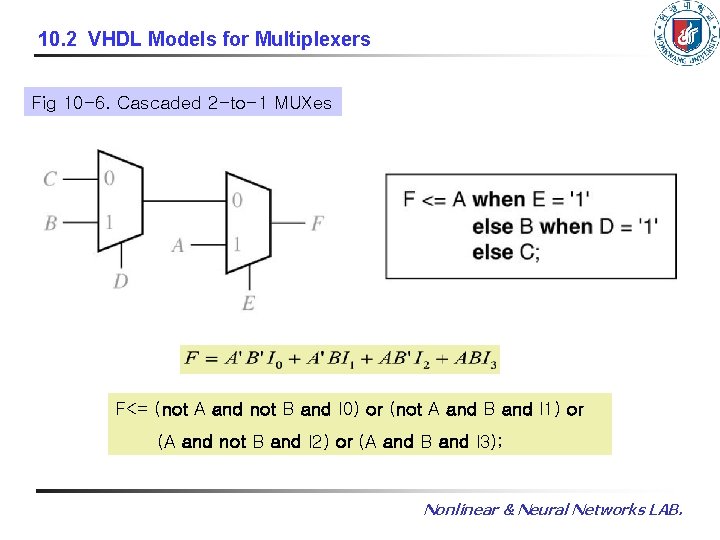

10. 2 VHDL Models for Multiplexers Fig 10 -6. Cascaded 2 -to-1 MUXes F<= (not A and not B and I 0) or (not A and B and l 1) or (A and not B and I 2) or (A and B and l 3); Nonlinear & Neural Networks LAB.

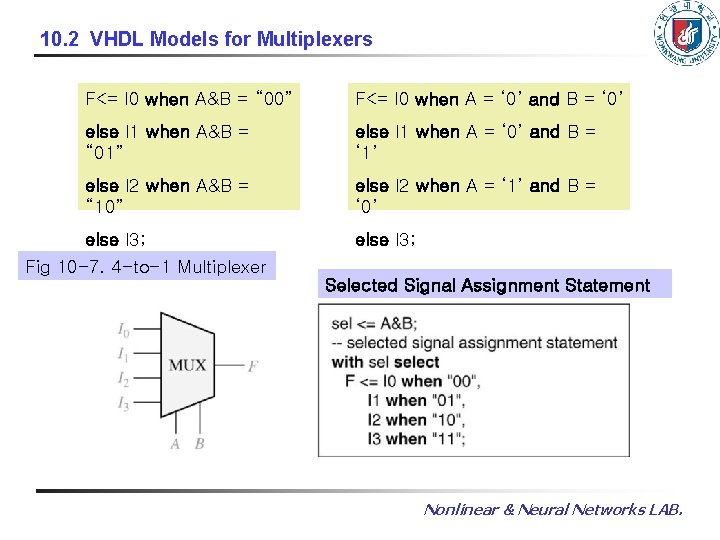

10. 2 VHDL Models for Multiplexers F<= l 0 when A&B = “ 00” F<= l 0 when A = ‘ 0’ and B = ‘ 0’ else l 1 when A&B = “ 01” else l 1 when A = ‘ 0’ and B = ‘ 1’ else l 2 when A&B = “ 10” else l 2 when A = ‘ 1’ and B = ‘ 0’ else l 3; Fig 10 -7. 4 -to-1 Multiplexer Selected Signal Assignment Statement Nonlinear & Neural Networks LAB.

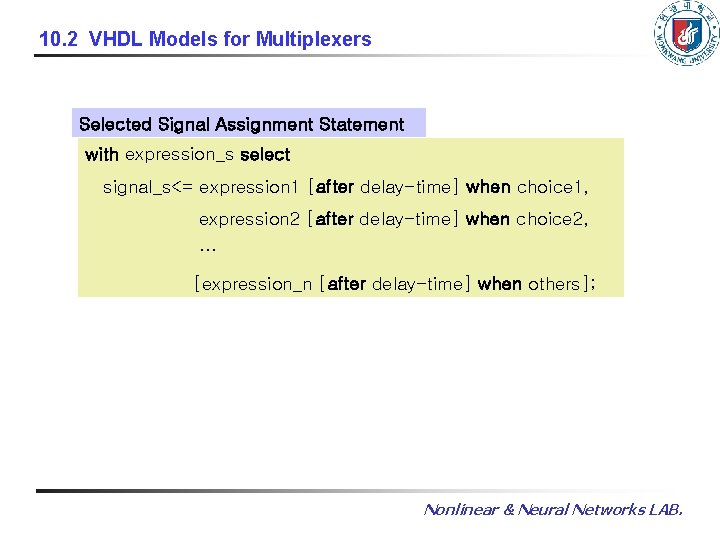

10. 2 VHDL Models for Multiplexers Selected Signal Assignment Statement with expression_s select signal_s<= expression 1 [after delay-time] when choice 1, expression 2 [after delay-time] when choice 2, … [expression_n [after delay-time] when others]; Nonlinear & Neural Networks LAB.

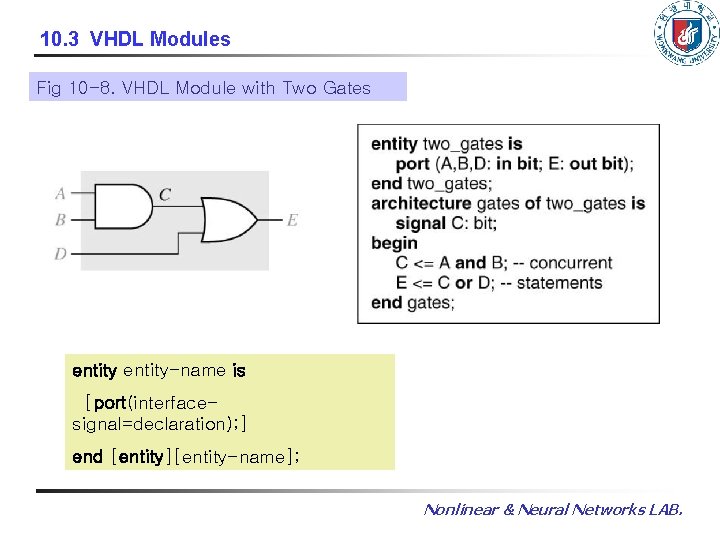

10. 3 VHDL Modules Fig 10 -8. VHDL Module with Two Gates entity-name is [port(interfacesignal=declaration); ] end [entity][entity-name]; Nonlinear & Neural Networks LAB.

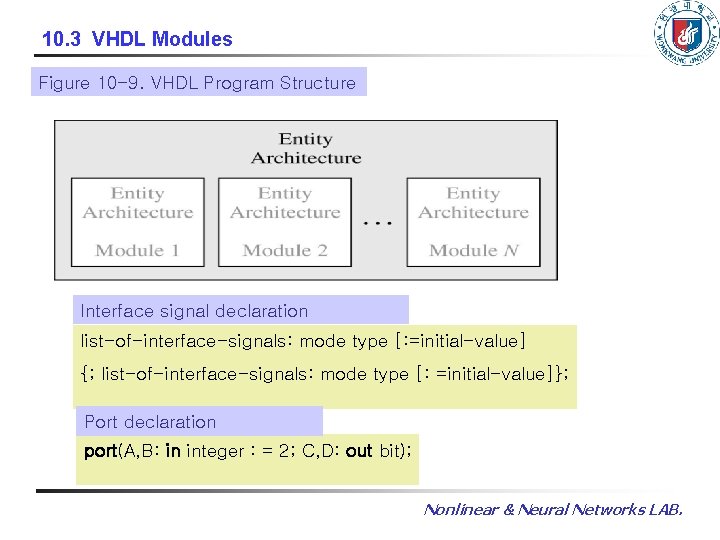

10. 3 VHDL Modules Figure 10 -9. VHDL Program Structure Interface signal declaration list-of-interface-signals: mode type [: =initial-value] {; list-of-interface-signals: mode type [: =initial-value]}; Port declaration port(A, B: in integer : = 2; C, D: out bit); Nonlinear & Neural Networks LAB.

![10. 3 VHDL Modules Architecture declaration architecture-name of entity-name is [declarations] begin architecture body 10. 3 VHDL Modules Architecture declaration architecture-name of entity-name is [declarations] begin architecture body](http://slidetodoc.com/presentation_image_h2/26a1733b7d2044adce25e5d03303a08d/image-14.jpg)

10. 3 VHDL Modules Architecture declaration architecture-name of entity-name is [declarations] begin architecture body end [architecture] [architecture-name]; Fig 10 -10. Entity Declaration for a Full Adder Module Nonlinear & Neural Networks LAB.

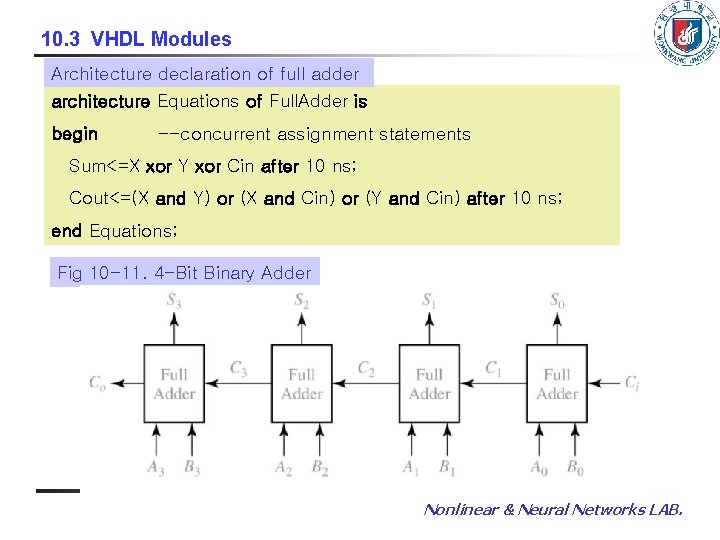

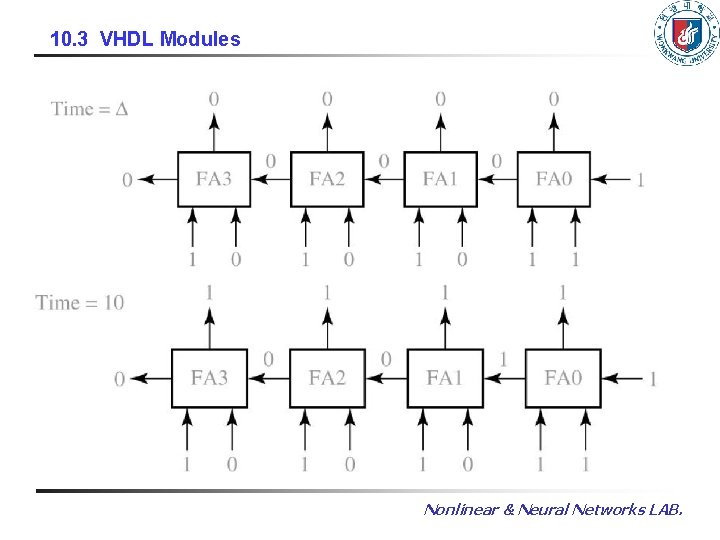

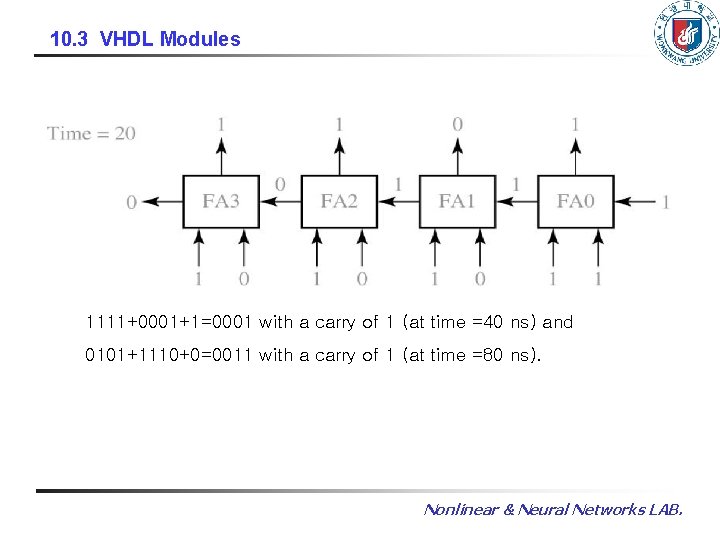

10. 3 VHDL Modules Architecture declaration of full adder architecture Equations of Full. Adder is begin --concurrent assignment statements Sum<=X xor Y xor Cin after 10 ns; Cout<=(X and Y) or (X and Cin) or (Y and Cin) after 10 ns; end Equations; Fig 10 -11. 4 -Bit Binary Adder Nonlinear & Neural Networks LAB.

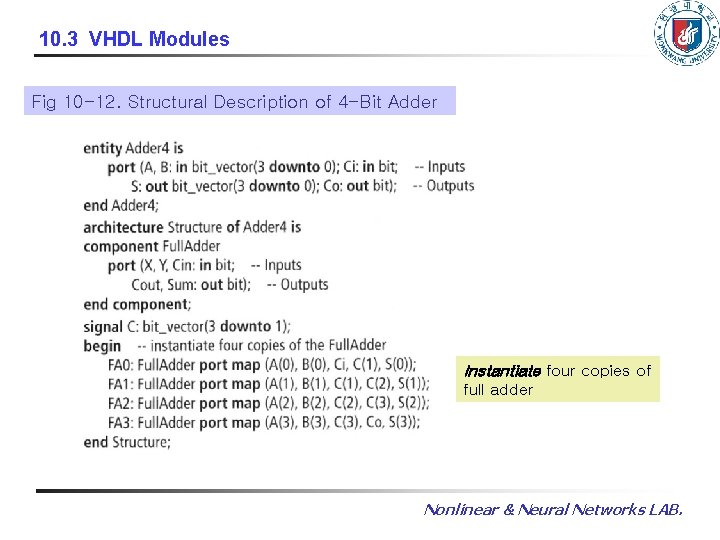

10. 3 VHDL Modules Fig 10 -12. Structural Description of 4 -Bit Adder Instantiate four copies of full adder Nonlinear & Neural Networks LAB.

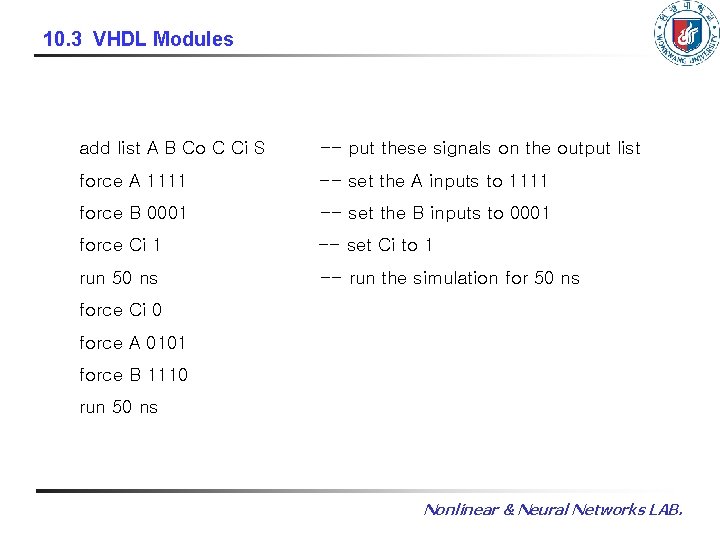

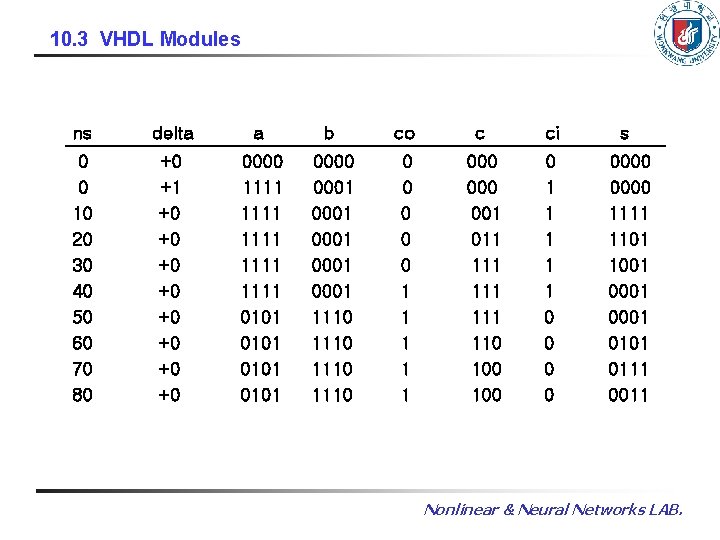

10. 3 VHDL Modules add list A B Co C Ci S -- put these signals on the output list force A 1111 -- set the A inputs to 1111 force B 0001 -- set the B inputs to 0001 force Ci 1 -- set Ci to 1 run 50 ns -- run the simulation for 50 ns force Ci 0 force A 0101 force B 1110 run 50 ns Nonlinear & Neural Networks LAB.

10. 3 VHDL Modules ns delta a b co c ci s 0 0 10 20 30 40 50 60 70 80 +0 +1 +0 +0 0000 1111 1111 0101 0000 0001 0001 1110 0 0 0 1 1 1 000 001 011 111 110 100 0 1 1 1 0 0 0000 1111 1101 1001 0001 0111 0011 Nonlinear & Neural Networks LAB.

10. 3 VHDL Modules Nonlinear & Neural Networks LAB.

10. 3 VHDL Modules 1111+0001+1=0001 with a carry of 1 (at time =40 ns) and 0101+1110+0=0011 with a carry of 1 (at time =80 ns). Nonlinear & Neural Networks LAB.

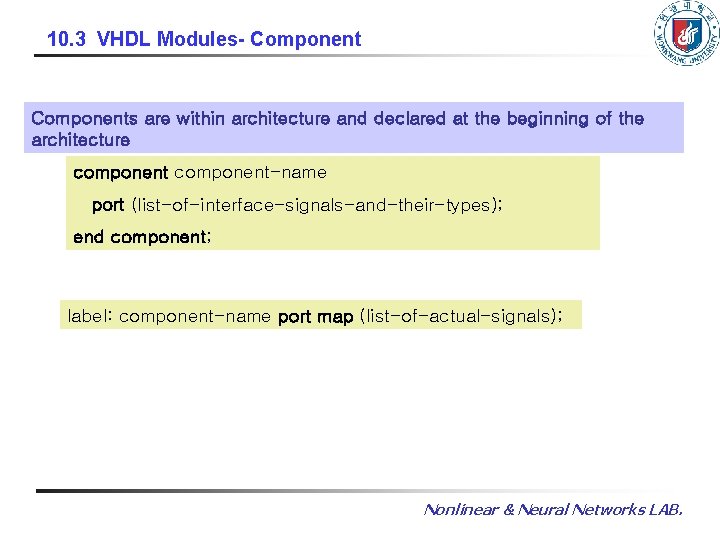

10. 3 VHDL Modules- Components are within architecture and declared at the beginning of the architecture component-name port (list-of-interface-signals-and-their-types); end component; label: component-name port map (list-of-actual-signals); Nonlinear & Neural Networks LAB.

![10. 4 Signals and Constants signal list_of_signal_names: type_name [constraint] [: = initial_value]; signal A, 10. 4 Signals and Constants signal list_of_signal_names: type_name [constraint] [: = initial_value]; signal A,](http://slidetodoc.com/presentation_image_h2/26a1733b7d2044adce25e5d03303a08d/image-22.jpg)

10. 4 Signals and Constants signal list_of_signal_names: type_name [constraint] [: = initial_value]; signal A, B, C: bit_vector(3 downto 0): = “ 1111”; signal E, F: integer range 0 to 15; constant_name: type_name [constraint] [: =constant_value]; constant limit : integer : = 17; constant delay 1 : time : = 5 ns; A<=B after delay 1; Nonlinear & Neural Networks LAB.

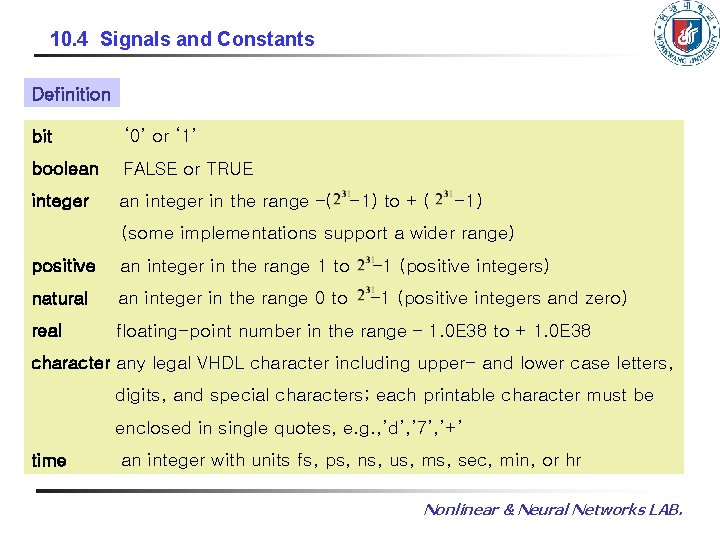

10. 4 Signals and Constants Definition bit ‘ 0’ or ‘ 1’ boolean FALSE or TRUE integer an integer in the range –( -1) to + ( -1) (some implementations support a wider range) positive an integer in the range 1 to – 1 (positive integers) natural an integer in the range 0 to – 1 (positive integers and zero) real floating-point number in the range – 1. 0 E 38 to + 1. 0 E 38 character any legal VHDL character including upper- and lower case letters, digits, and special characters; each printable character must be enclosed in single quotes, e. g. , ’d’, ’ 7’, ’+’ time an integer with units fs, ps, ns, us, ms, sec, min, or hr Nonlinear & Neural Networks LAB.

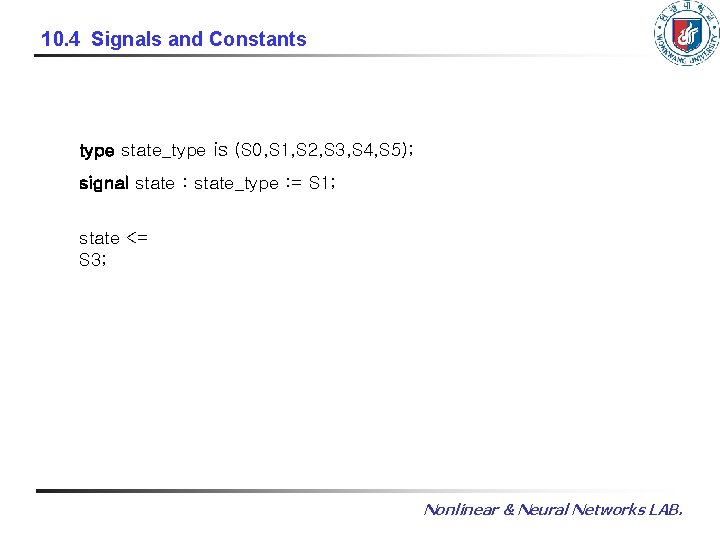

10. 4 Signals and Constants type state_type is (S 0, S 1, S 2, S 3, S 4, S 5); signal state : state_type : = S 1; state <= S 3; Nonlinear & Neural Networks LAB.

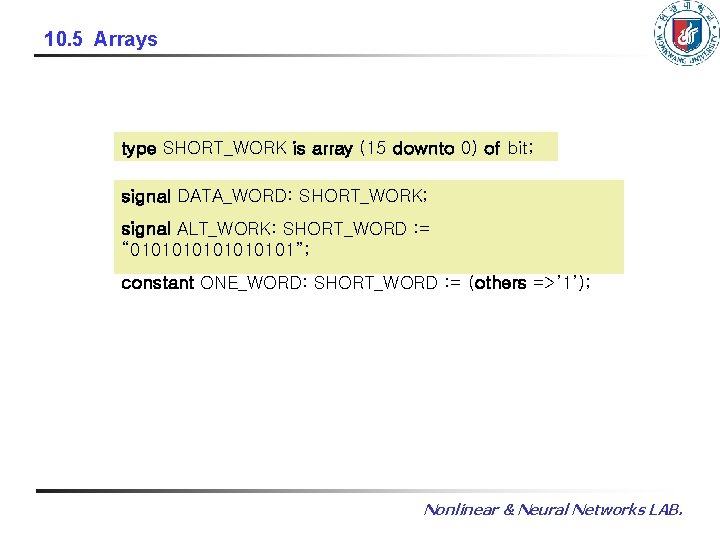

10. 5 Arrays type SHORT_WORK is array (15 downto 0) of bit; signal DATA_WORD: SHORT_WORK; signal ALT_WORK: SHORT_WORD : = “ 01010101”; constant ONE_WORD: SHORT_WORD : = (others =>’ 1’); Nonlinear & Neural Networks LAB.

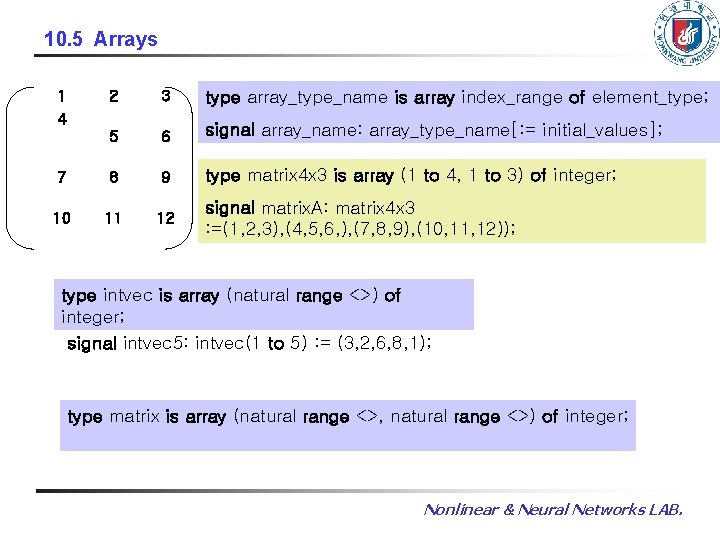

10. 5 Arrays 1 4 2 3 type array_type_name is array index_range of element_type; 5 6 signal array_name: array_type_name[: = initial_values]; 7 8 9 type matrix 4 x 3 is array (1 to 4, 1 to 3) of integer; 10 11 12 signal matrix. A: matrix 4 x 3 : =(1, 2, 3), (4, 5, 6, ), (7, 8, 9), (10, 11, 12)); type intvec is array (natural range <>) of integer; signal intvec 5: intvec(1 to 5) : = (3, 2, 6, 8, 1); type matrix is array (natural range <>, natural range <>) of integer; Nonlinear & Neural Networks LAB.

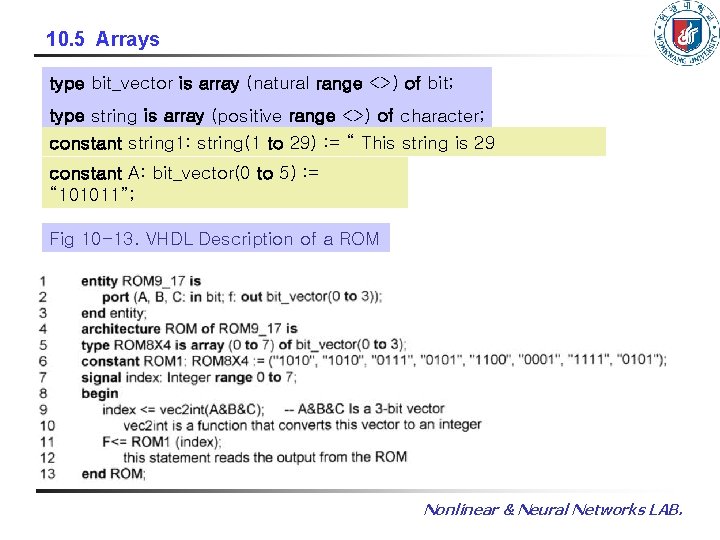

10. 5 Arrays type bit_vector is array (natural range <>) of bit; type string is array (positive range <>) of character; constant string 1: string(1 to 29) : = “ This string is 29 characters. ” constant A: bit_vector(0 to 5) : = “ 101011”; Fig 10 -13. VHDL Description of a ROM Nonlinear & Neural Networks LAB.

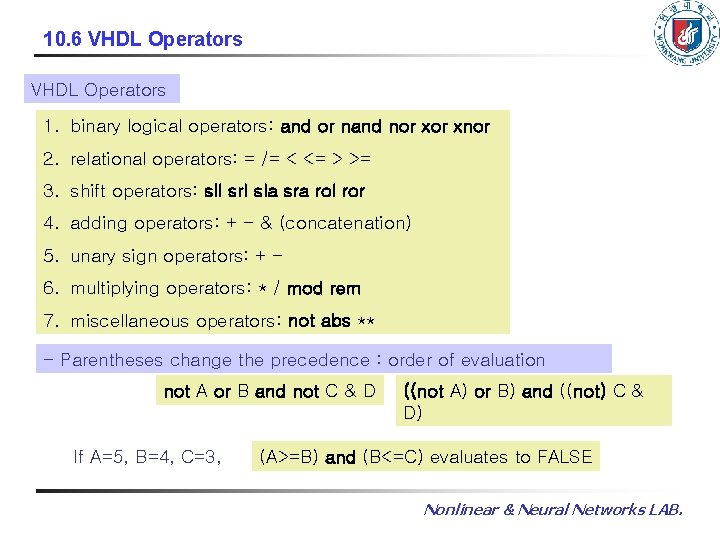

10. 6 VHDL Operators 1. binary logical operators: and or nand nor xnor 2. relational operators: = /= < <= > >= 3. shift operators: sll srl sla sra rol ror 4. adding operators: + - & (concatenation) 5. unary sign operators: + 6. multiplying operators: * / mod rem 7. miscellaneous operators: not abs ** - Parentheses change the precedence : order of evaluation not A or B and not C & D If A=5, B=4, C=3, ((not A) or B) and ((not) C & D) (A>=B) and (B<=C) evaluates to FALSE Nonlinear & Neural Networks LAB.

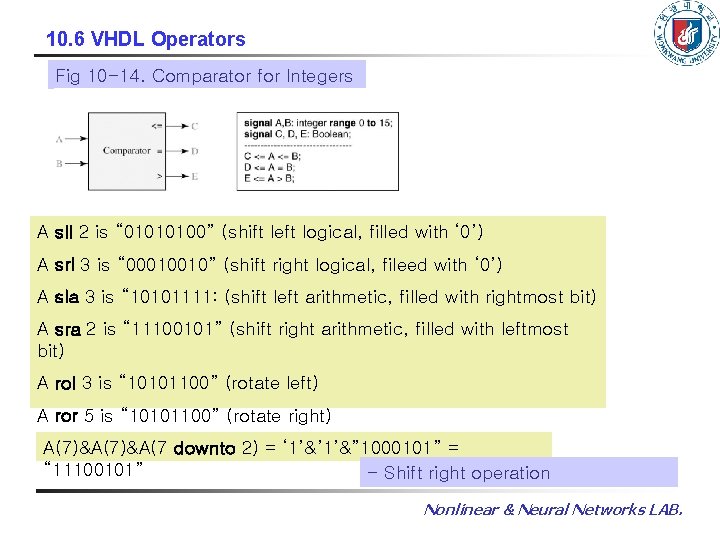

10. 6 VHDL Operators Fig 10 -14. Comparator for Integers A sll 2 is “ 01010100” (shift left logical, filled with ‘ 0’) A srl 3 is “ 00010010” (shift right logical, fileed with ‘ 0’) A sla 3 is “ 10101111: (shift left arithmetic, filled with rightmost bit) A sra 2 is “ 11100101” (shift right arithmetic, filled with leftmost bit) A rol 3 is “ 10101100” (rotate left) A ror 5 is “ 10101100” (rotate right) A(7)&A(7 downto 2) = ‘ 1’&’ 1’&” 1000101” = “ 11100101” - Shift right operation Nonlinear & Neural Networks LAB.

![10. 7 Packages and Libraries Package declaration package-name is package delarations end [package][package-name]; Optional 10. 7 Packages and Libraries Package declaration package-name is package delarations end [package][package-name]; Optional](http://slidetodoc.com/presentation_image_h2/26a1733b7d2044adce25e5d03303a08d/image-30.jpg)

10. 7 Packages and Libraries Package declaration package-name is package delarations end [package][package-name]; Optional package body package-name is package delarations end [package body][package-name]; Bit_package has a NOR 2 gate (inside CD-ROM attached) component Nor 2 port (A 1, A 2: in bit; Z: out bit); end component; --2 -input NOR gate entity Nor 2 is port (A 1, A 2: in bit; Z: out bit); end Nor 2; architecture concur of Nor 2 is begin Z<=not(A 1 or A 2) after 10 ns; end concur; Nonlinear & Neural Networks LAB.

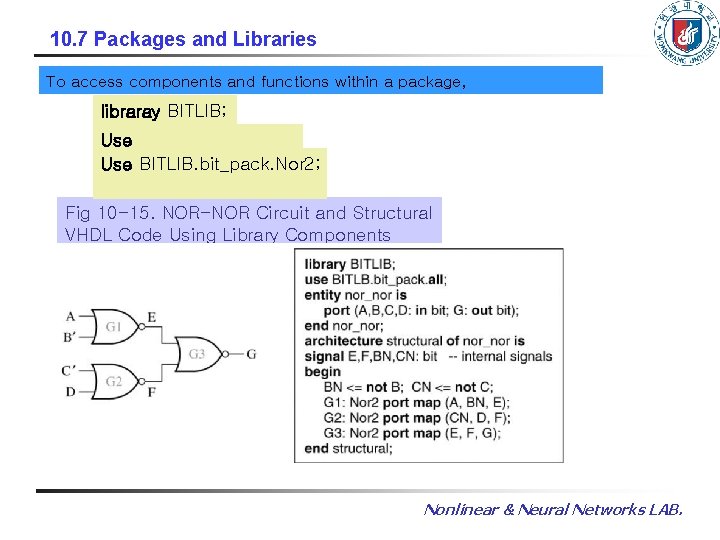

10. 7 Packages and Libraries To access components and functions within a package, libraray BITLIB; Use BITLIB. bit_pack. all; Use BITLIB. bit_pack. Nor 2; Fig 10 -15. NOR-NOR Circuit and Structural VHDL Code Using Library Components Nonlinear & Neural Networks LAB.

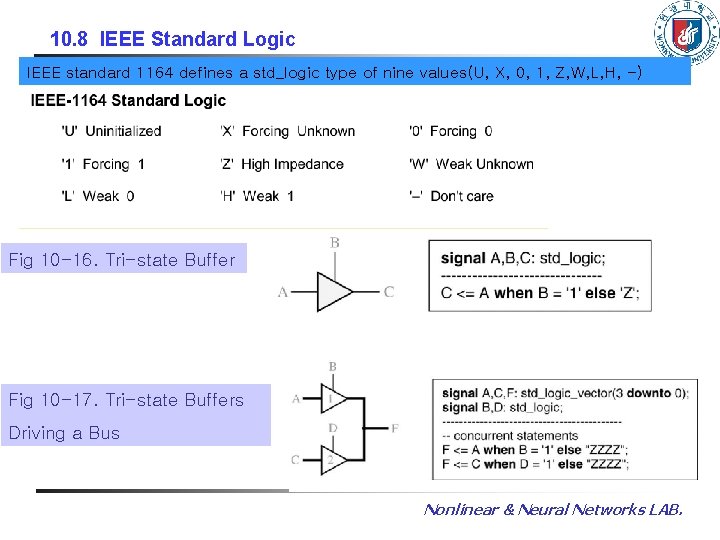

10. 8 IEEE Standard Logic IEEE standard 1164 defines a std_logic type of nine values(U, X, 0, 1, Z, W, L, H, -) Fig 10 -16. Tri-state Buffer Fig 10 -17. Tri-state Buffers Driving a Bus Nonlinear & Neural Networks LAB.

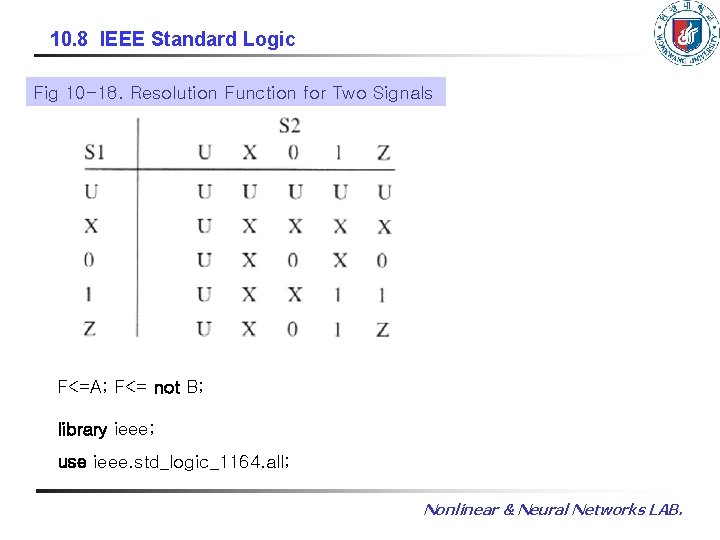

10. 8 IEEE Standard Logic Fig 10 -18. Resolution Function for Two Signals F<=A; F<= not B; library ieee; use ieee. std_logic_1164. all; Nonlinear & Neural Networks LAB.

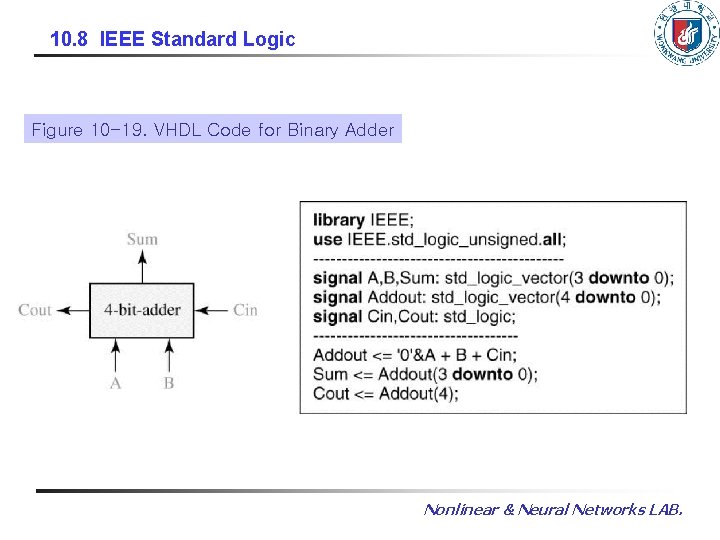

10. 8 IEEE Standard Logic Figure 10 -19. VHDL Code for Binary Adder Nonlinear & Neural Networks LAB.

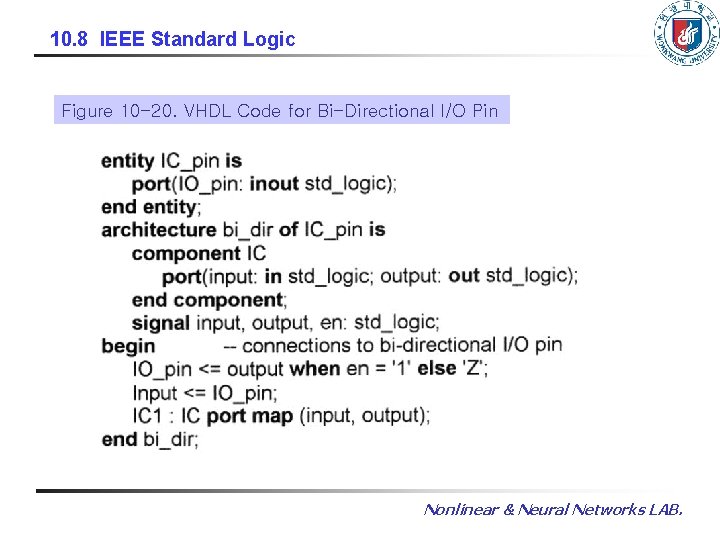

10. 8 IEEE Standard Logic Figure 10 -20. VHDL Code for Bi-Directional I/O Pin Nonlinear & Neural Networks LAB.

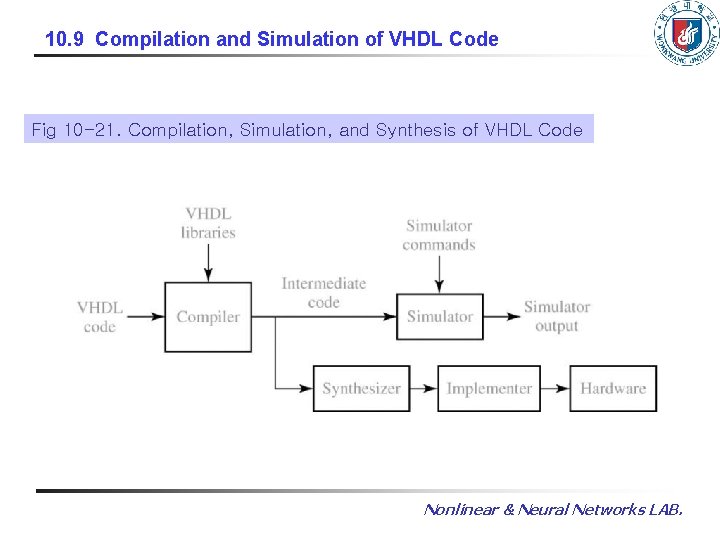

10. 9 Compilation and Simulation of VHDL Code Fig 10 -21. Compilation, Simulation, and Synthesis of VHDL Code Nonlinear & Neural Networks LAB.

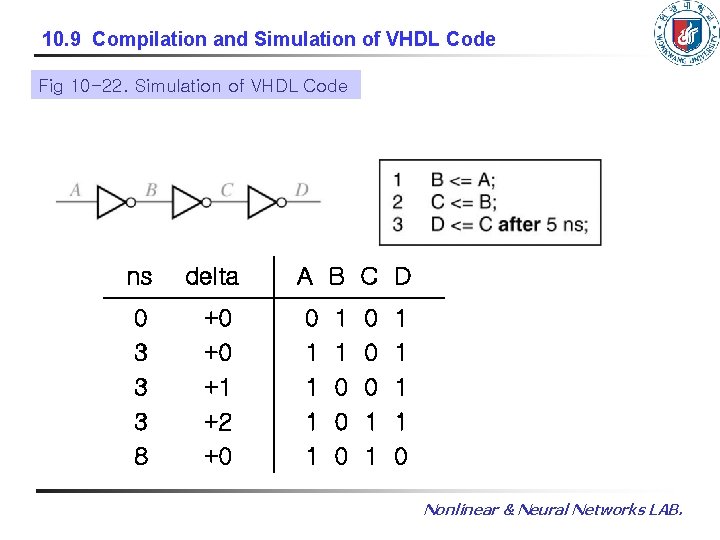

10. 9 Compilation and Simulation of VHDL Code Fig 10 -22. Simulation of VHDL Code ns delta 0 3 3 3 8 +0 +0 +1 +2 +0 A B C D 0 1 1 1 0 0 0 1 1 1 0 Nonlinear & Neural Networks LAB.

- Slides: 37