Noise and Power Tradeoffs in CMOS Front Ends

- Slides: 30

Noise and Power Tradeoffs in CMOS Front Ends Paul O’Connor VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006

Acknowledgements • • Gianluigi De Geronimo Veljko Radeka Angelo Dragone Jean-François Pratte VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 2

Outline • Fundamental limits • Constrained noise optimization – power – speed • Figure of merit – analog – digital • Architecture choices • Summary VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 3

What are the fundamental limits? • Charge of one electron ENC ≥ 1 electron rms? VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 4

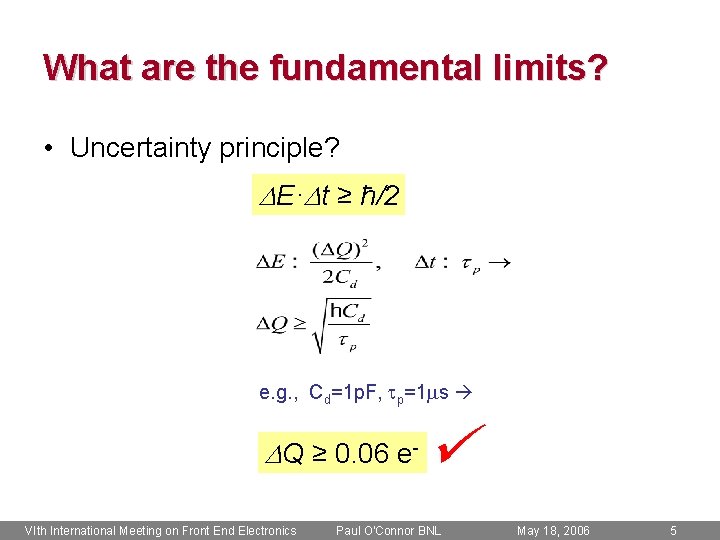

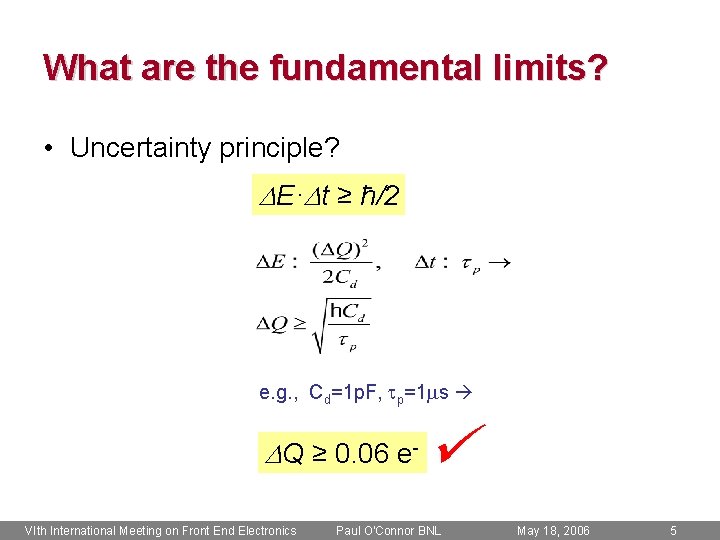

What are the fundamental limits? • Uncertainty principle? DE·Dt ≥ ħ/2 e. g. , Cd=1 p. F, tp=1 ms DQ ≥ 0. 06 e. VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 5

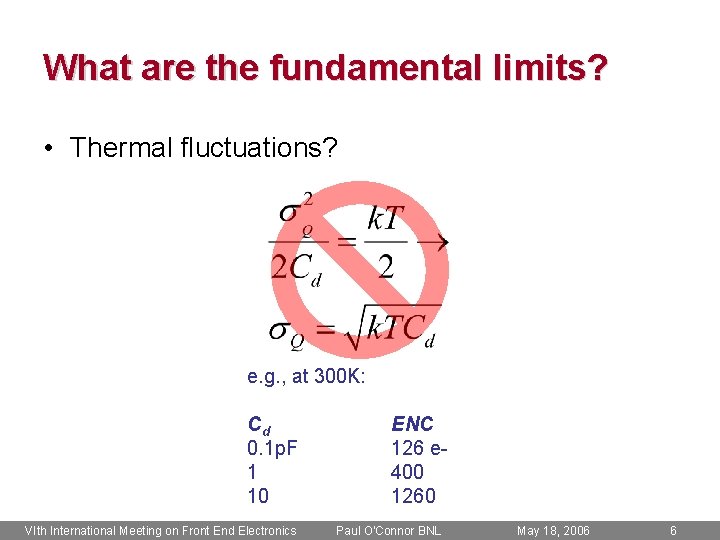

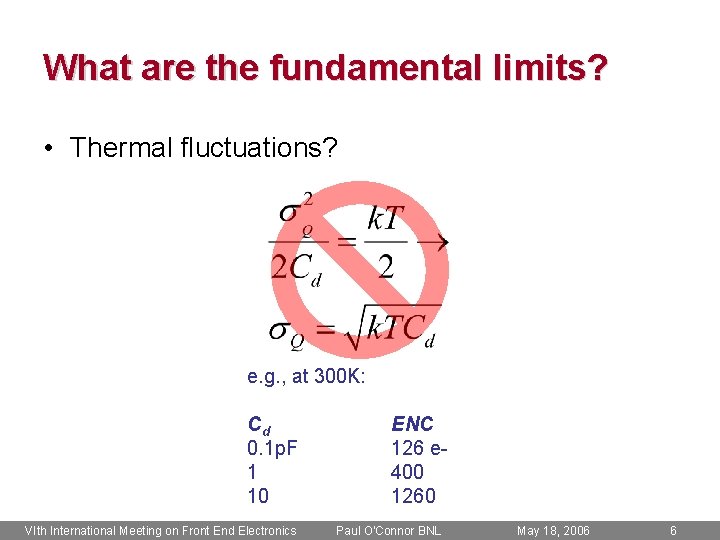

What are the fundamental limits? • Thermal fluctuations? e. g. , at 300 K: Cd 0. 1 p. F 1 10 VIth International Meeting on Front End Electronics ENC 126 e 400 1260 Paul O'Connor BNL May 18, 2006 6

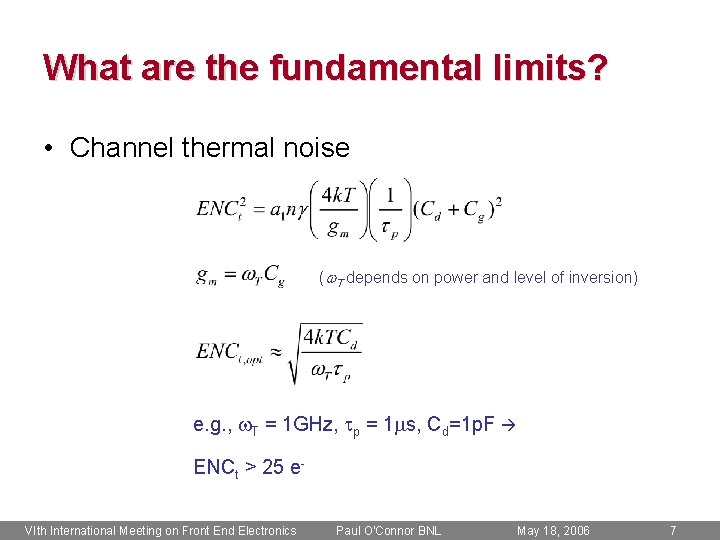

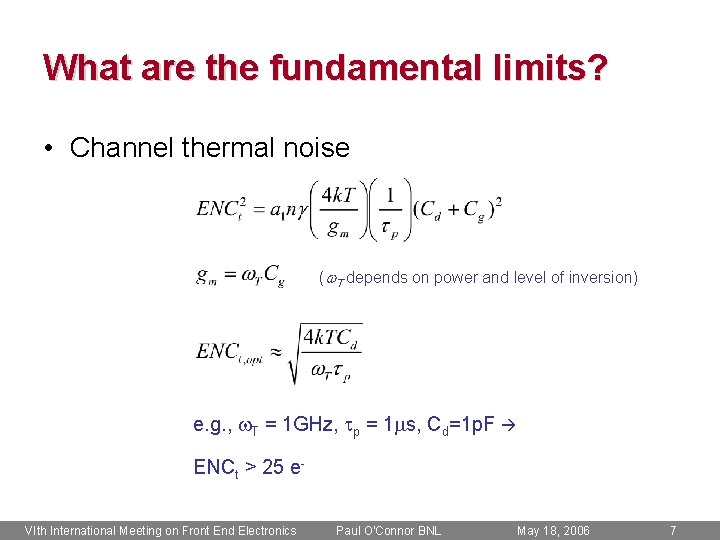

What are the fundamental limits? • Channel thermal noise (w. T depends on power and level of inversion) e. g. , w. T = 1 GHz, tp = 1 ms, Cd=1 p. F ENCt > 25 e. VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 7

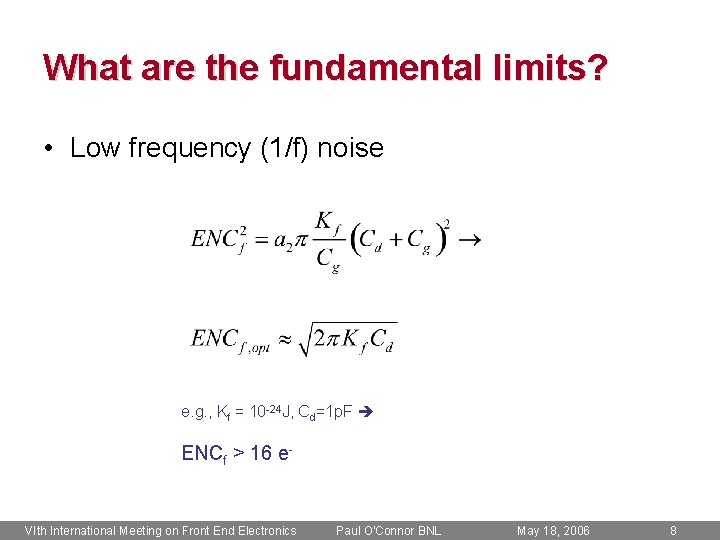

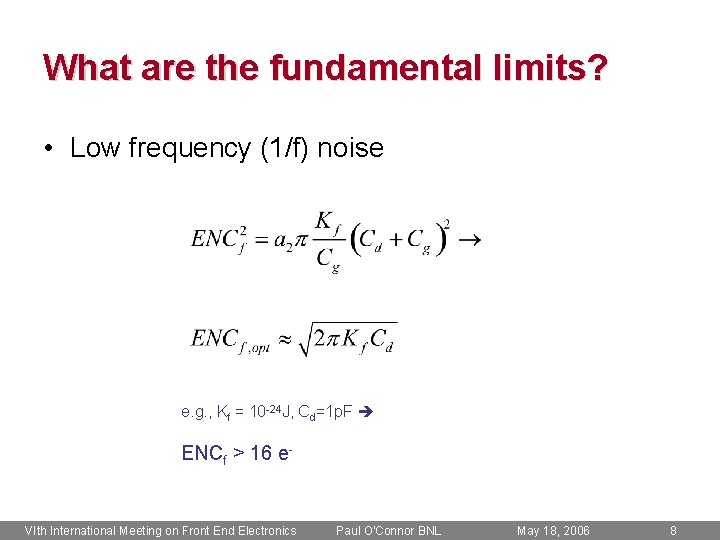

What are the fundamental limits? • Low frequency (1/f) noise e. g. , Kf = 10 -24 J, Cd=1 p. F ENCf > 16 e- VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 8

Most systems are power-constrained • • particle physics space security (portable) imaging VIth International Meeting on Front End Electronics services/cooling/material limited power sources power density/cooling Paul O'Connor BNL May 18, 2006 9

Shaping time is not always a free choice tp may be constrained by – – pileup timing precision ballistic deficit parallel noise (noise corner time constant √Rs. Rp. Cin 2) VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 10

How can power be reduced without sacrificing performance (SNR, pileup)? • design: – optimize M 1 and H(s) • technology: – scaling impact on noise and dynamic range • architecture: – multiplexing and digitizing strategy VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 11

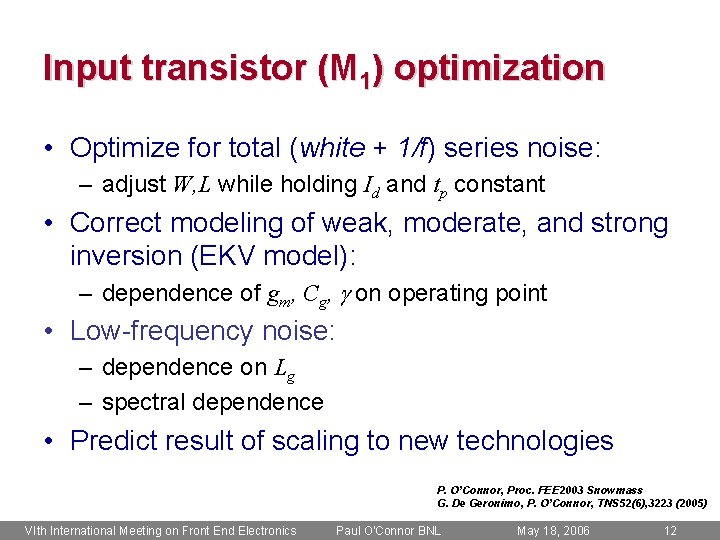

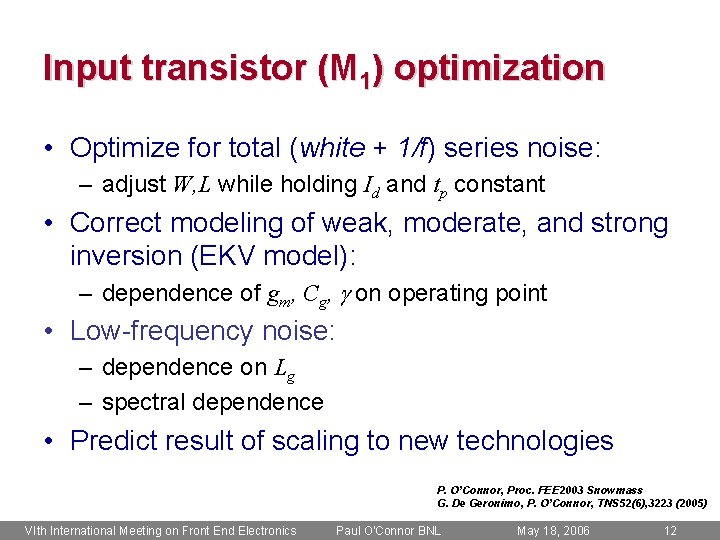

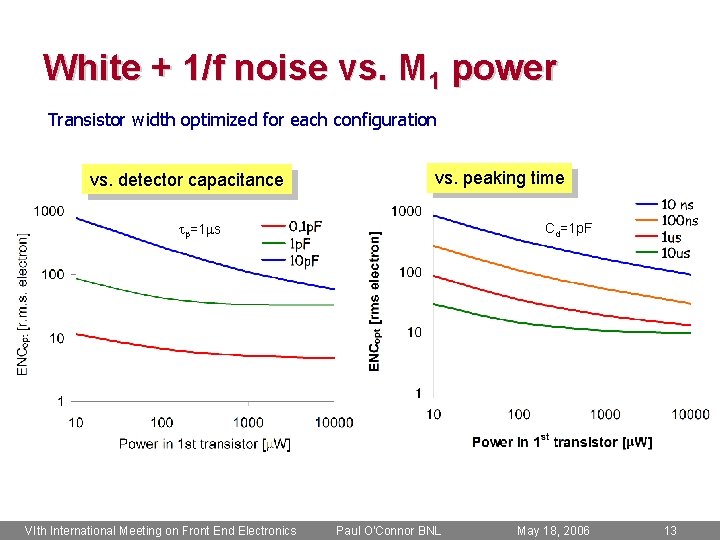

Input transistor (M 1) optimization • Optimize for total (white + 1/f) series noise: – adjust W, L while holding Id and tp constant • Correct modeling of weak, moderate, and strong inversion (EKV model): – dependence of gm, Cg, g on operating point • Low-frequency noise: – dependence on Lg – spectral dependence • Predict result of scaling to new technologies P. O’Connor, Proc. FEE 2003 Snowmass G. De Geronimo, P. O’Connor, TNS 52(6), 3223 (2005) VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 12

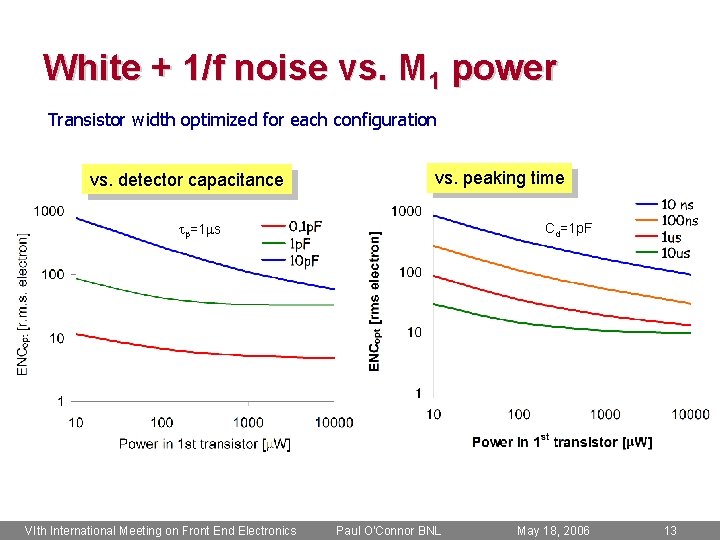

White + 1/f noise vs. M 1 power Transistor width optimized for each configuration vs. detector capacitance vs. peaking time tp=1 ms VIth International Meeting on Front End Electronics Cd=1 p. F Paul O'Connor BNL May 18, 2006 13

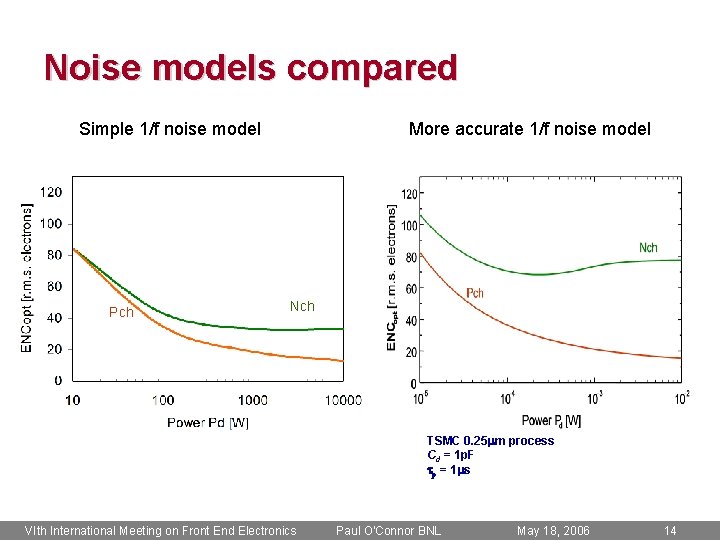

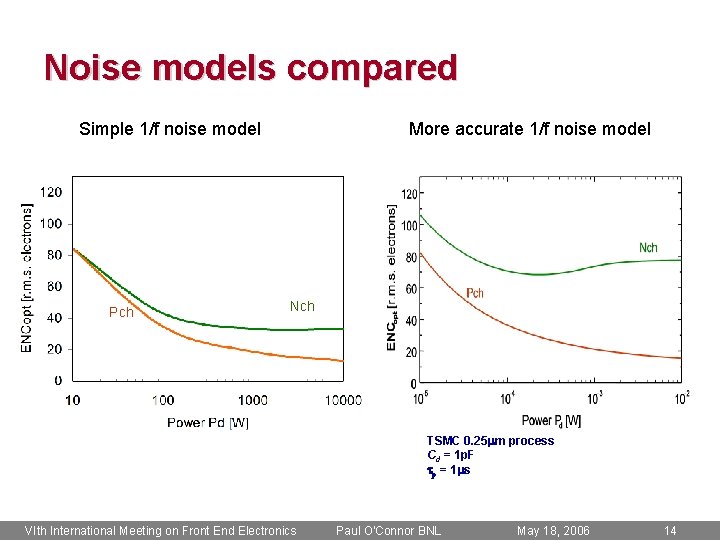

Noise models compared Simple 1/f noise model Pch More accurate 1/f noise model Nch TSMC 0. 25 mm process Cd = 1 p. F tp = 1 ms VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 14

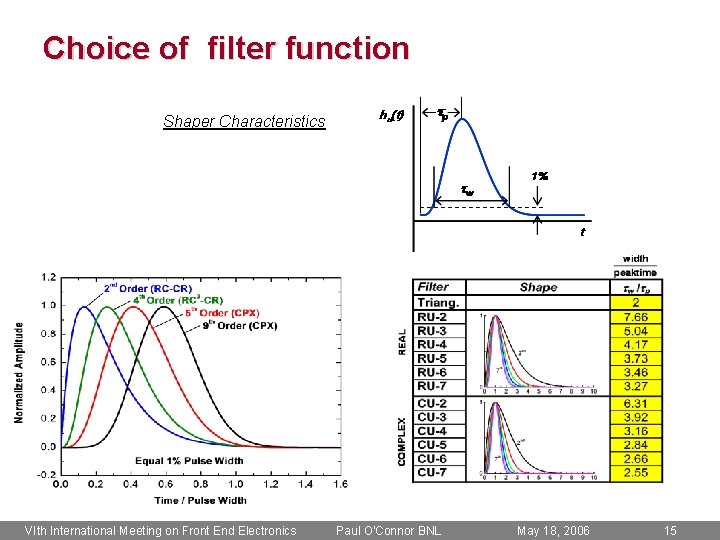

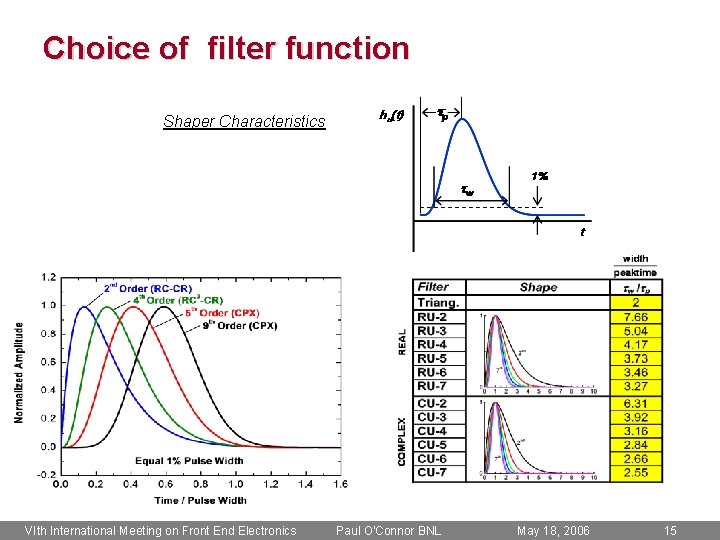

Choice of filter function Shaper Characteristics VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 15

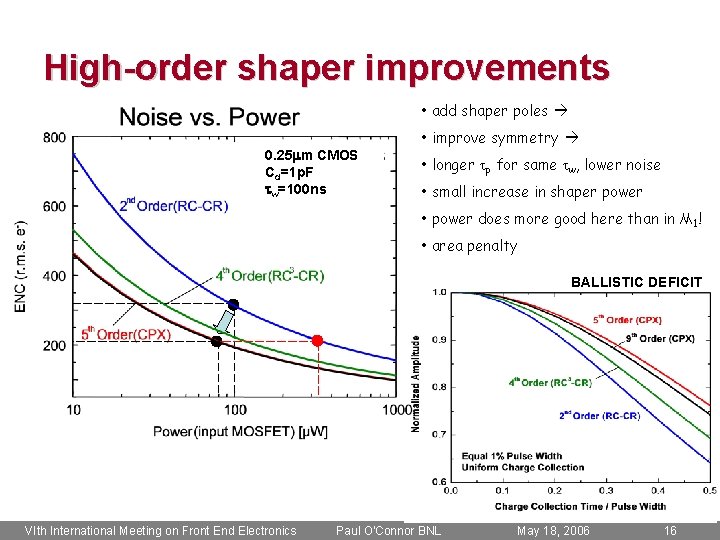

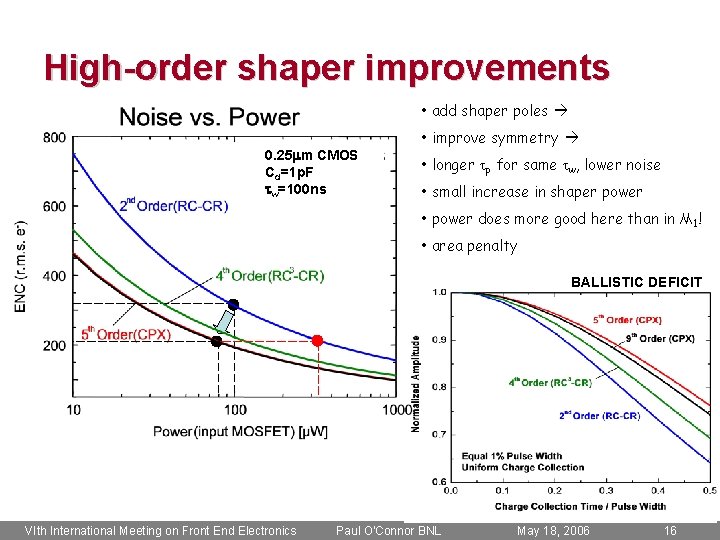

High-order shaper improvements • add shaper poles • improve symmetry 0. 25 mm CMOS Cd=1 p. F tw=100 ns • longer tp for same tw, lower noise • small increase in shaper power • power does more good here than in M 1! • area penalty BALLISTIC DEFICIT VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 16

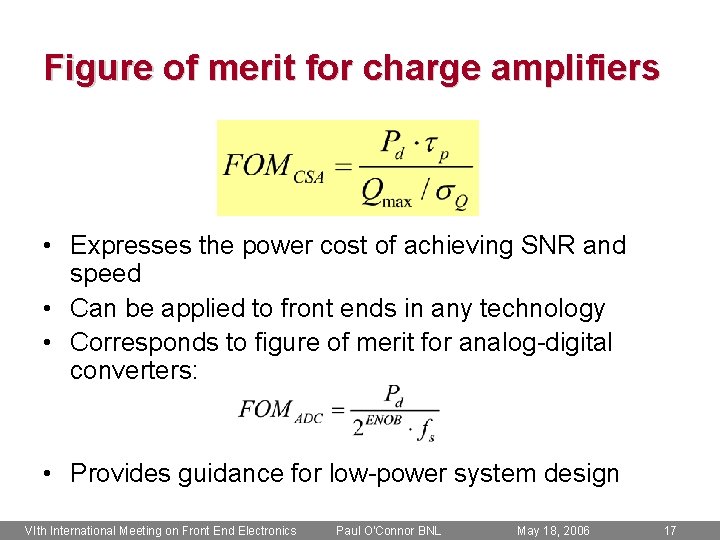

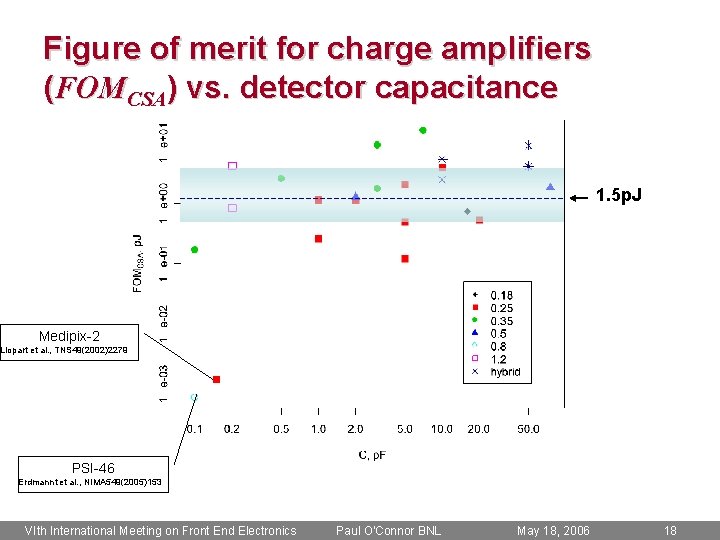

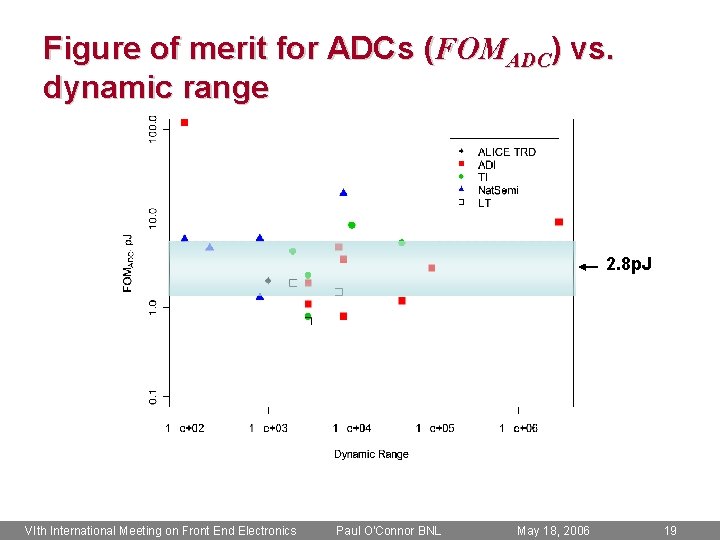

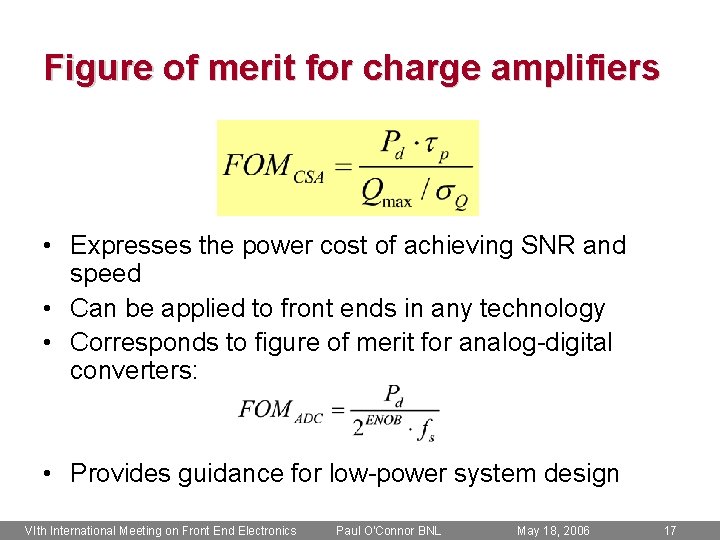

Figure of merit for charge amplifiers • Expresses the power cost of achieving SNR and speed • Can be applied to front ends in any technology • Corresponds to figure of merit for analog-digital converters: • Provides guidance for low-power system design VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 17

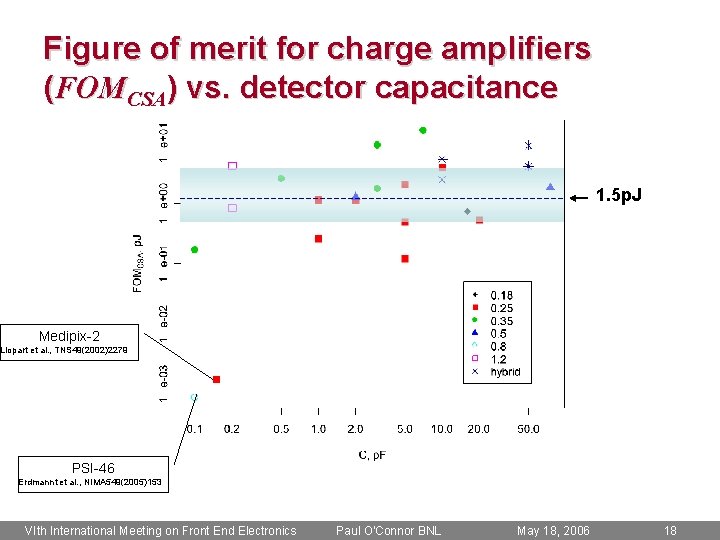

Figure of merit for charge amplifiers (FOMCSA) vs. detector capacitance 1. 5 p. J Medipix-2 Llopart et al. , TNS 49(2002)2279 PSI-46 Erdmannt et al. , NIMA 549(2005)153 VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 18

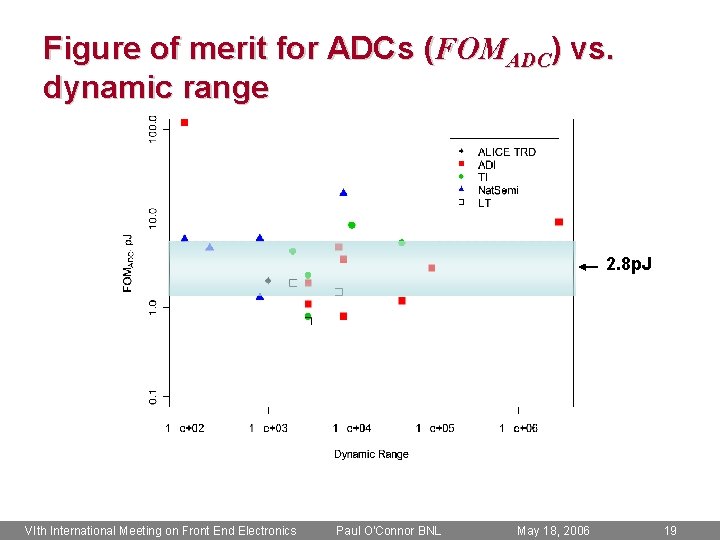

Figure of merit for ADCs (FOMADC) vs. dynamic range 2. 8 p. J VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 19

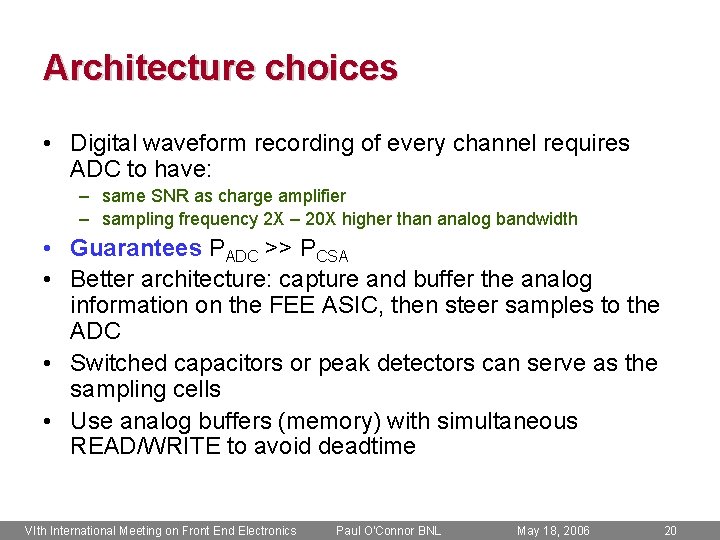

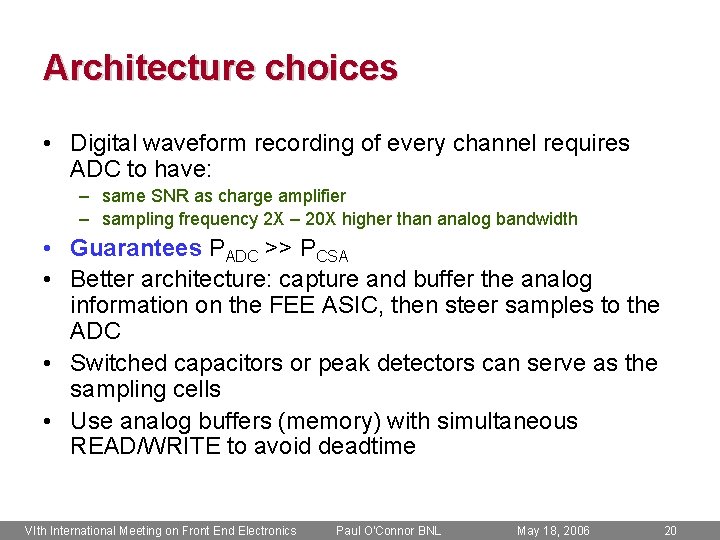

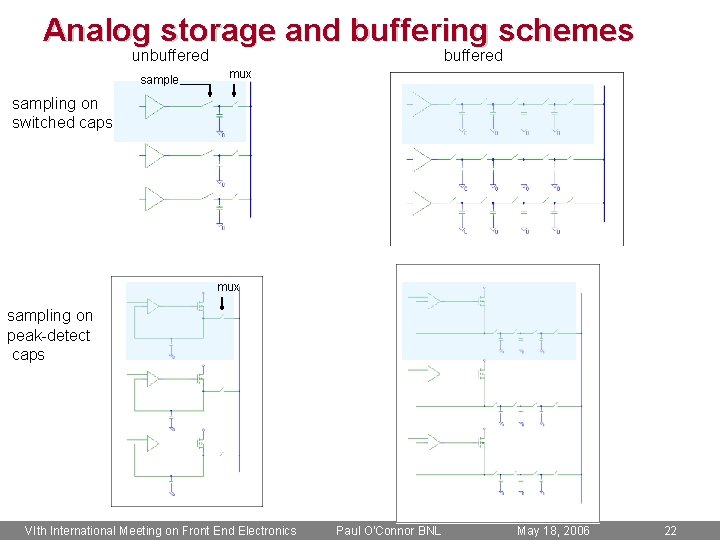

Architecture choices • Digital waveform recording of every channel requires ADC to have: – same SNR as charge amplifier – sampling frequency 2 X – 20 X higher than analog bandwidth • Guarantees PADC >> PCSA • Better architecture: capture and buffer the analog information on the FEE ASIC, then steer samples to the ADC • Switched capacitors or peak detectors can serve as the sampling cells • Use analog buffers (memory) with simultaneous READ/WRITE to avoid deadtime VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 20

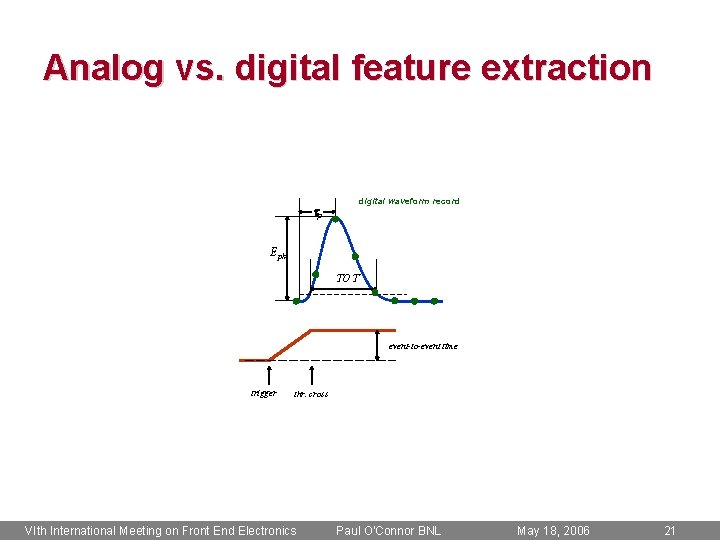

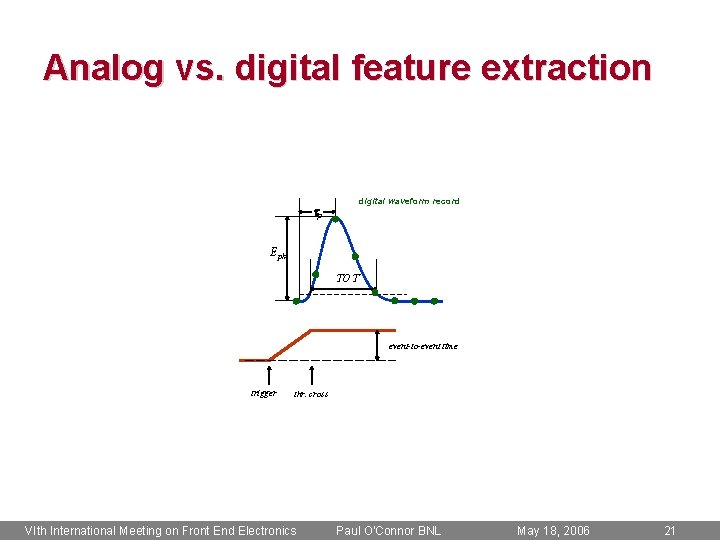

Analog vs. digital feature extraction digital waveform record tp Epk TOT event-to-event time trigger thr. cross VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 21

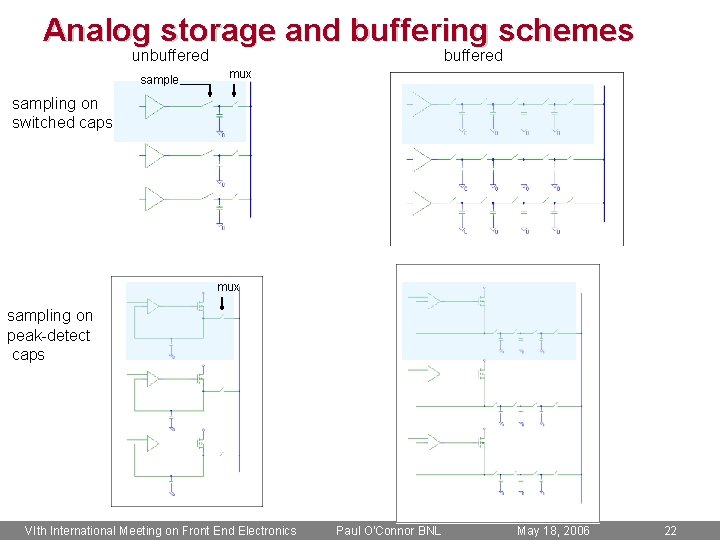

Analog storage and buffering schemes unbuffered sample buffered mux sampling on switched caps mux sampling on peak-detect caps VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 22

EXAMPLES VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 23

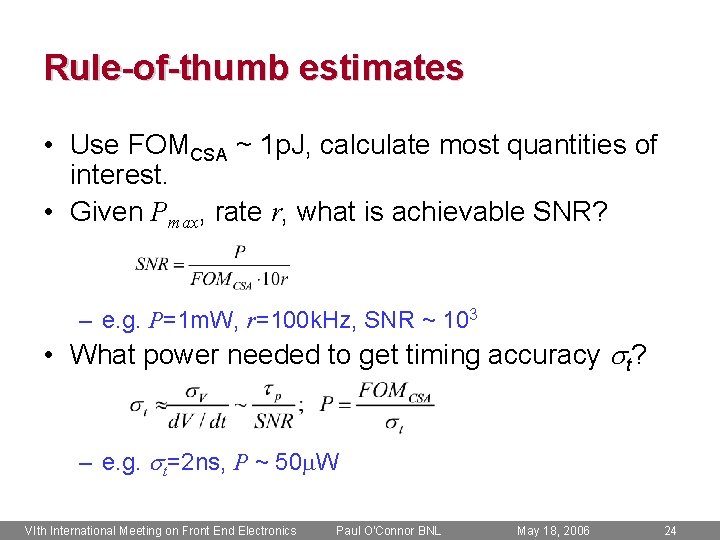

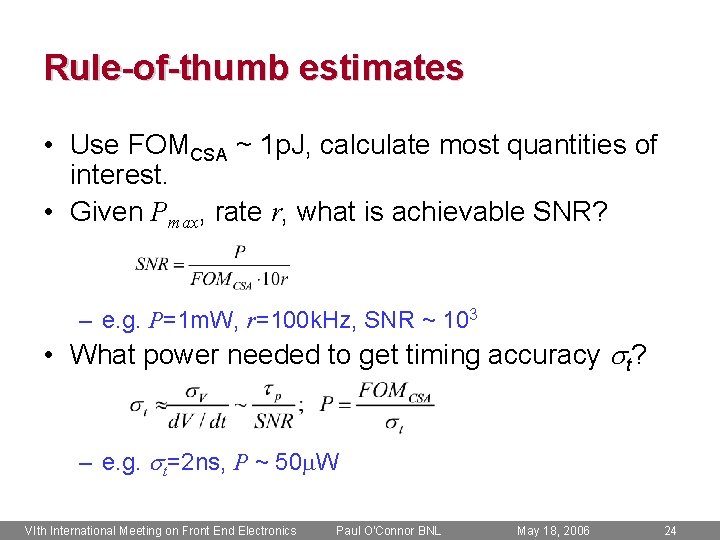

Rule-of-thumb estimates • Use FOMCSA ~ 1 p. J, calculate most quantities of interest. • Given Pmax, rate r, what is achievable SNR? – e. g. P=1 m. W, r=100 k. Hz, SNR ~ 103 • What power needed to get timing accuracy st? – e. g. st=2 ns, P ~ 50 m. W VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 24

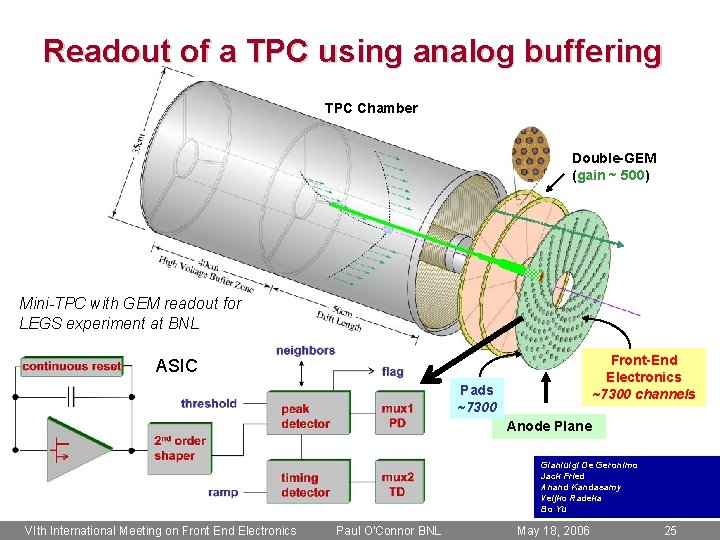

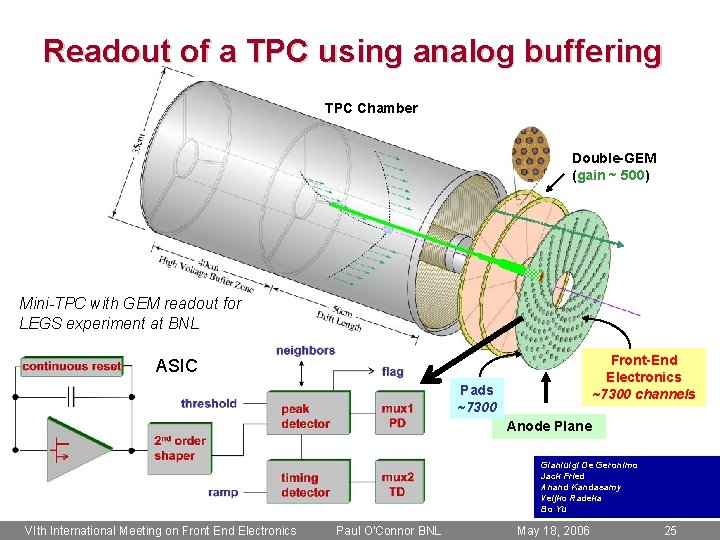

Readout of a TPC using analog buffering TPC Chamber Double-GEM (gain ~ 500) Mini-TPC with GEM readout for LEGS experiment at BNL Front-End Electronics ~7300 channels ASIC Pads ~7300 Anode Plane Gianluigi De Geronimo Jack Fried Anand Kandasamy Veljko Radeka Bo Yu VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 25

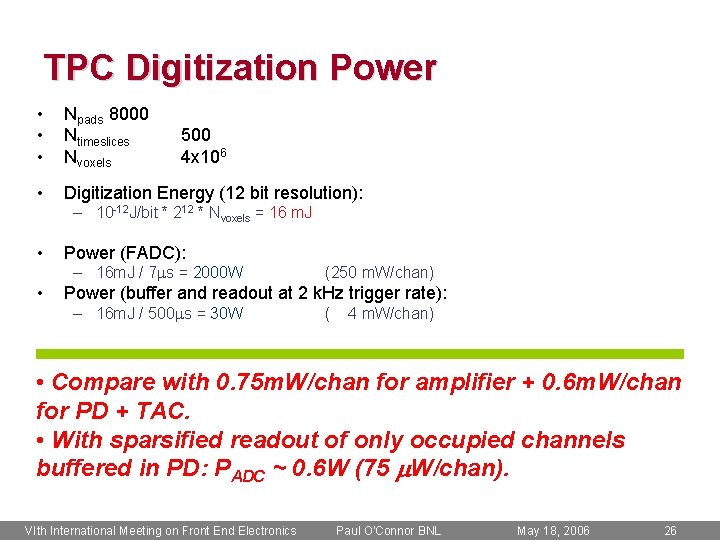

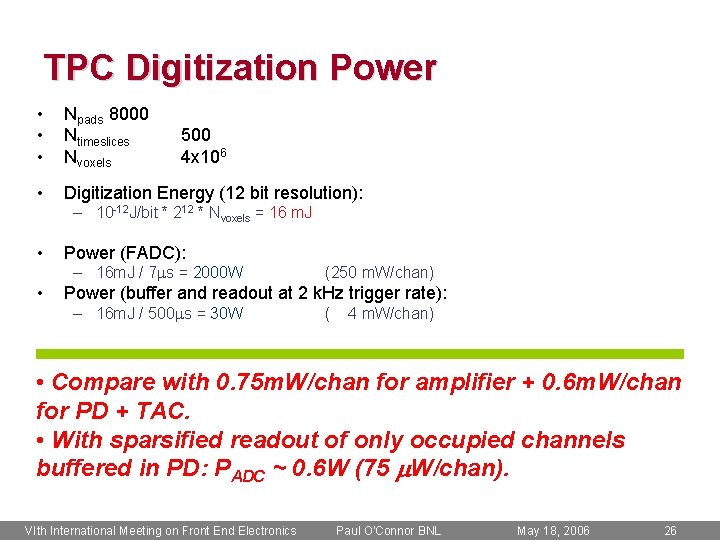

TPC Digitization Power • • • Npads 8000 Ntimeslices Nvoxels • Digitization Energy (12 bit resolution): 500 4 x 106 – 10 -12 J/bit * 212 * Nvoxels = 16 m. J • Power (FADC): – 16 m. J / 7 ms = 2000 W • (250 m. W/chan) Power (buffer and readout at 2 k. Hz trigger rate): – 16 m. J / 500 ms = 30 W ( 4 m. W/chan) • Compare with 0. 75 m. W/chan for amplifier + 0. 6 m. W/chan for PD + TAC. • With sparsified readout of only occupied channels buffered in PD: PADC ~ 0. 6 W (75 m. W/chan). VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 26

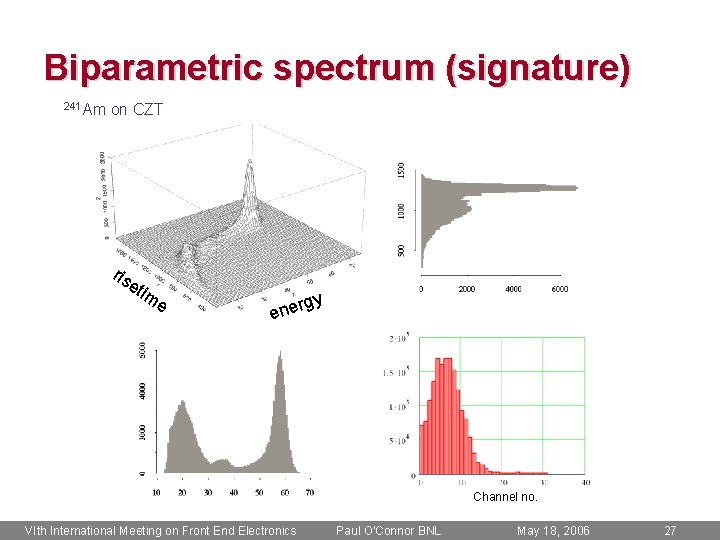

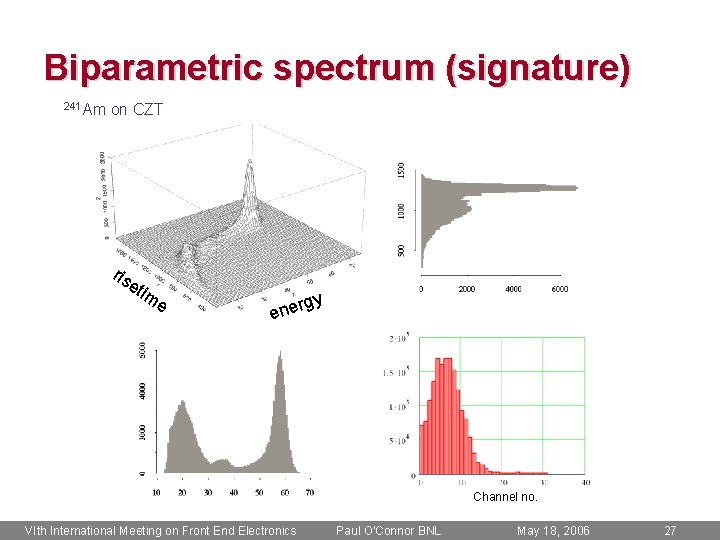

Biparametric spectrum (signature) 241 Am on CZT ris eti me ene rgy Channel no. VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 27

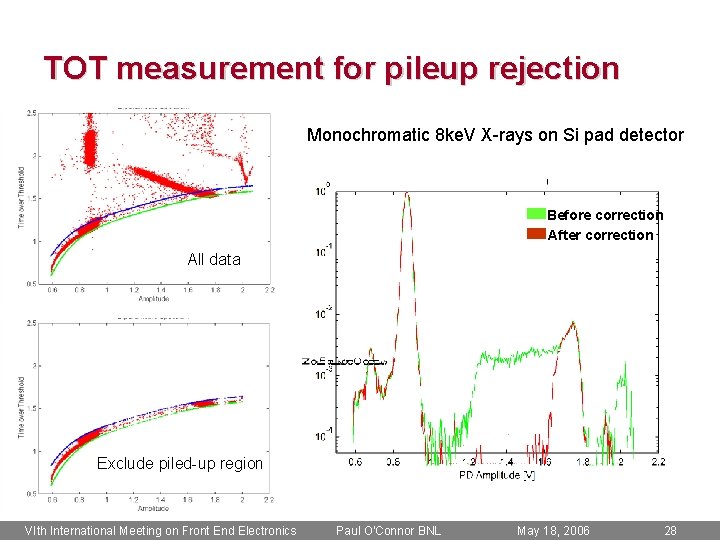

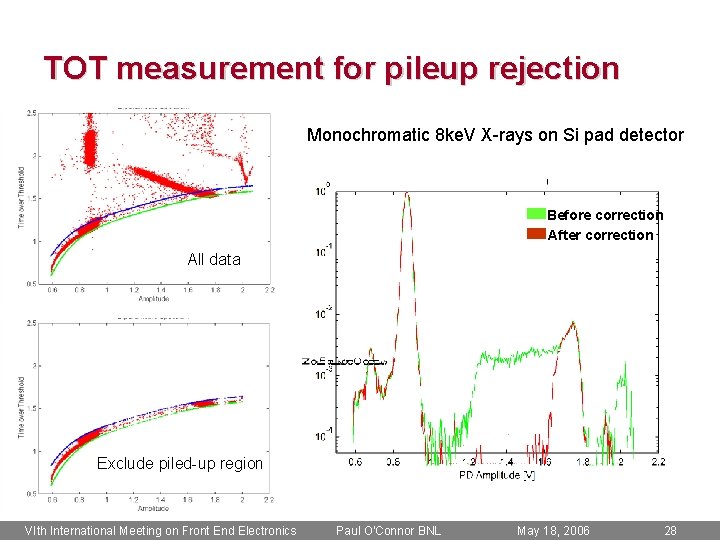

TOT measurement for pileup rejection Monochromatic 8 ke. V X-rays on Si pad detector Before correction After correction All data Exclude piled-up region VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 28

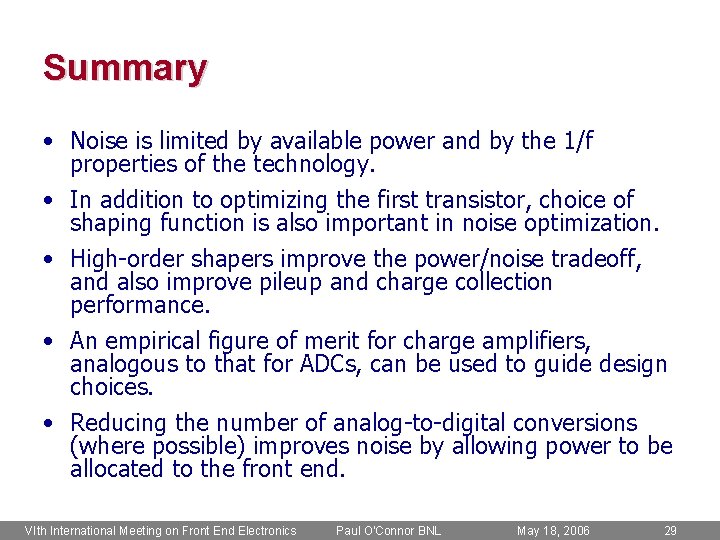

Summary • Noise is limited by available power and by the 1/f properties of the technology. • In addition to optimizing the first transistor, choice of shaping function is also important in noise optimization. • High-order shapers improve the power/noise tradeoff, and also improve pileup and charge collection performance. • An empirical figure of merit for charge amplifiers, analogous to that for ADCs, can be used to guide design choices. • Reducing the number of analog-to-digital conversions (where possible) improves noise by allowing power to be allocated to the front end. VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 29

VIth International Meeting on Front End Electronics Paul O'Connor BNL May 18, 2006 30