NEW PS TDC FORHEP AND OTHER APPLICATIONS 1

- Slides: 26

NEW PS TDC FORHEP AND OTHER APPLICATIONS 1 Jorgen Christiansen, Moritz Horstmann, Lukas Perktold (Now AMS), Jeffrey Prinzie (Leuven) CERN/PH-ESE

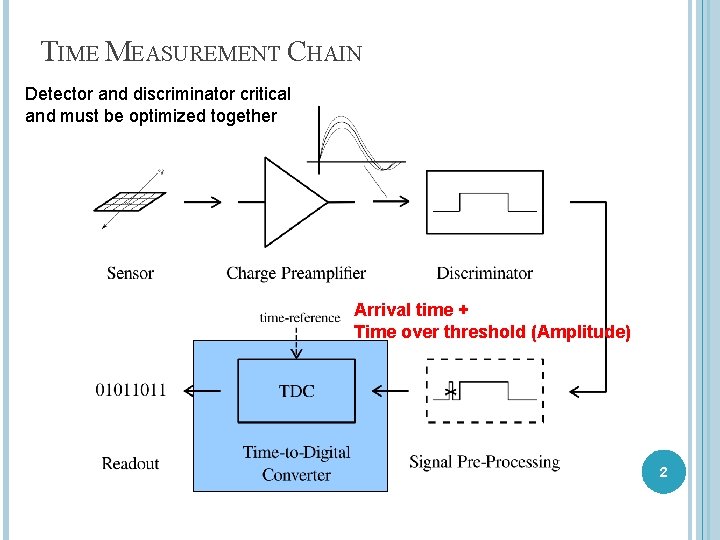

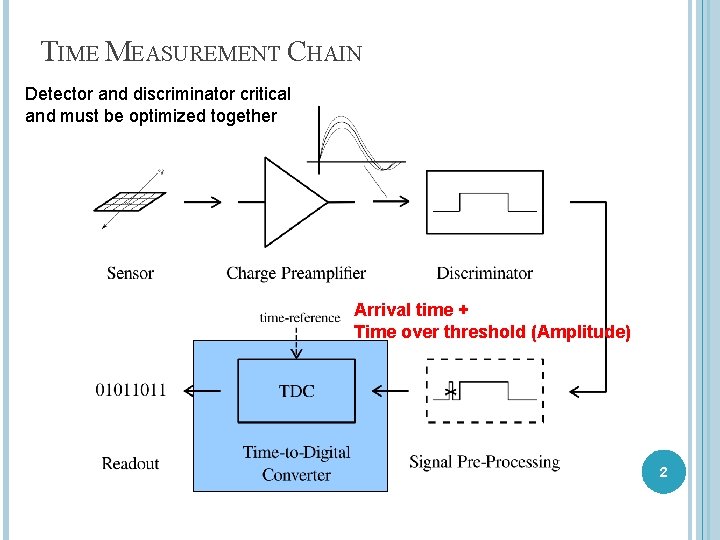

TIME MEASUREMENT CHAIN Detector and discriminator critical and must be optimized together Arrival time + Time over threshold (Amplitude) 2

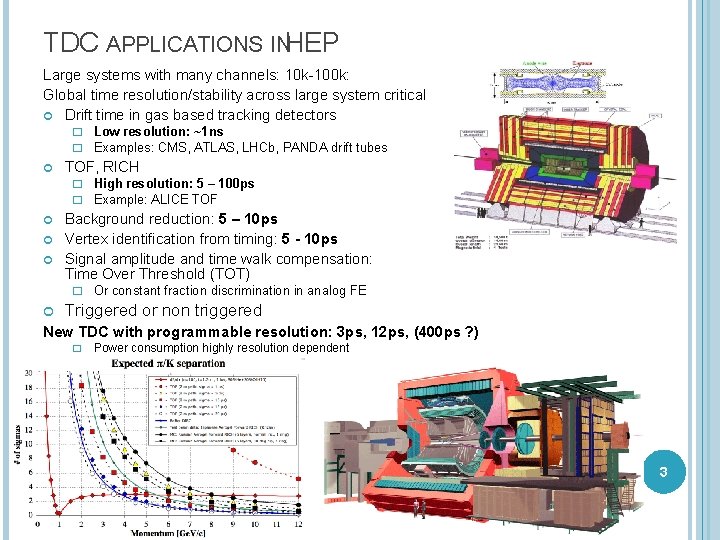

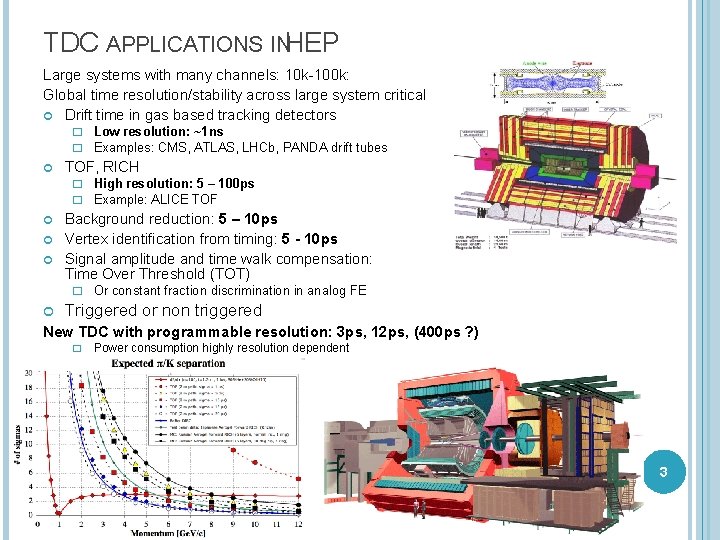

TDC APPLICATIONS INHEP Large systems with many channels: 10 k-100 k: Global time resolution/stability across large system critical Drift time in gas based tracking detectors � Low resolution: ~1 ns � Examples: CMS, ATLAS, LHCb, PANDA drift tubes TOF, RICH � High resolution: 5 – 100 ps � Example: ALICE TOF Background reduction: 5 – 10 ps Vertex identification from timing: 5 - 10 ps Signal amplitude and time walk compensation: Time Over Threshold (TOT) � Or constant fraction discrimination in analog FE Triggered or non triggered New TDC with programmable resolution: 3 ps, 12 ps, (400 ps ? ) � Power consumption highly resolution dependent 3

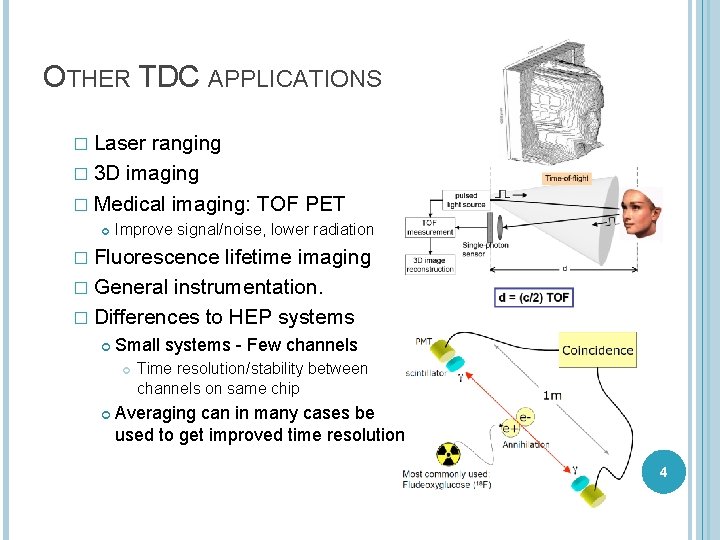

OTHER TDC APPLICATIONS � Laser ranging � 3 D imaging � Medical imaging: TOF PET Improve signal/noise, lower radiation � Fluorescence lifetime imaging � General instrumentation. � Differences to HEP systems Small systems - Few channels Time resolution/stability between channels on same chip Averaging can in many cases be used to get improved time resolution 4

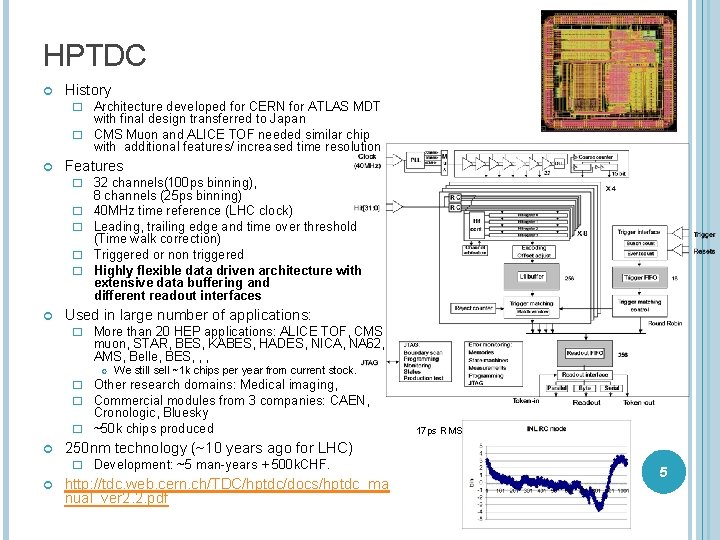

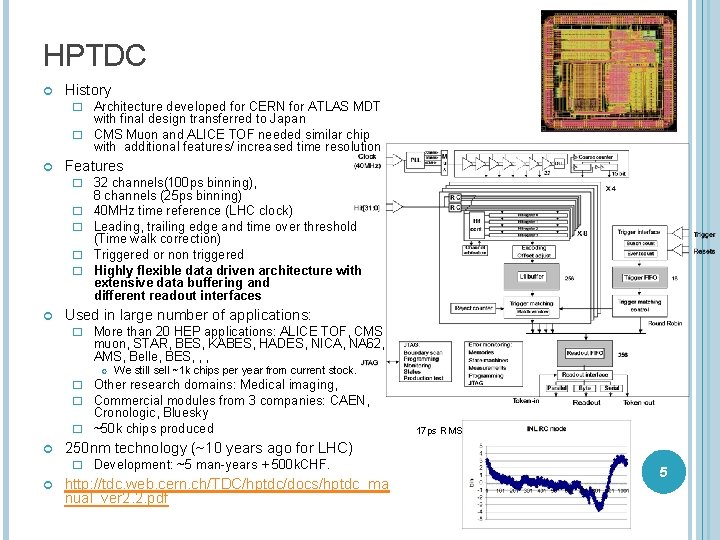

HPTDC History � Architecture developed for CERN for ATLAS MDT with final design transferred to Japan � CMS Muon and ALICE TOF needed similar chip with additional features/ increased time resolution Features � 32 channels(100 ps binning), � � 8 channels (25 ps binning) 40 MHz time reference (LHC clock) Leading, trailing edge and time over threshold (Time walk correction) Triggered or non triggered Highly flexible data driven architecture with extensive data buffering and different readout interfaces Used in large number of applications: � More than 20 HEP applications: ALICE TOF, CMS muon, STAR, BES, KABES, HADES, NICA, NA 62, AMS, Belle, BES, , , We still sell ~1 k chips per year from current stock. � Other research domains: Medical imaging, � Commercial modules from 3 companies: CAEN, Cronologic, Bluesky � ~50 k chips produced 250 nm technology (~10 years ago for LHC) � Development: ~5 man-years + 500 k. CHF. 17 ps RMS http: //tdc. web. cern. ch/TDC/hptdc/docs/hptdc_ma nual_ver 2. 2. pdf 5

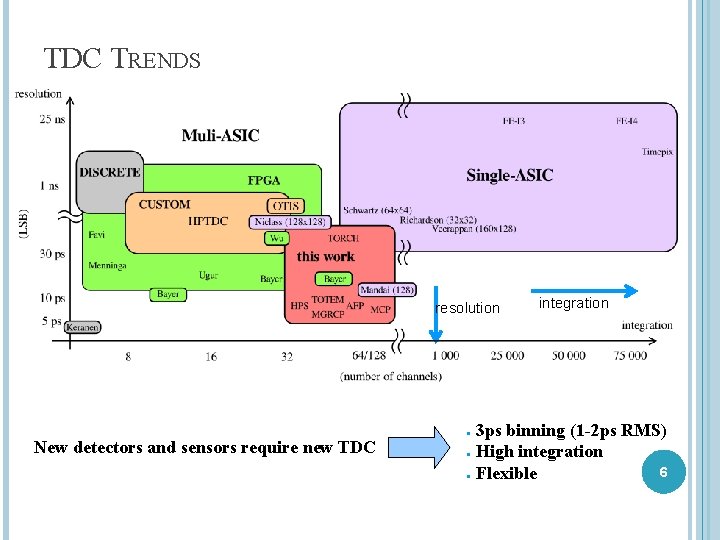

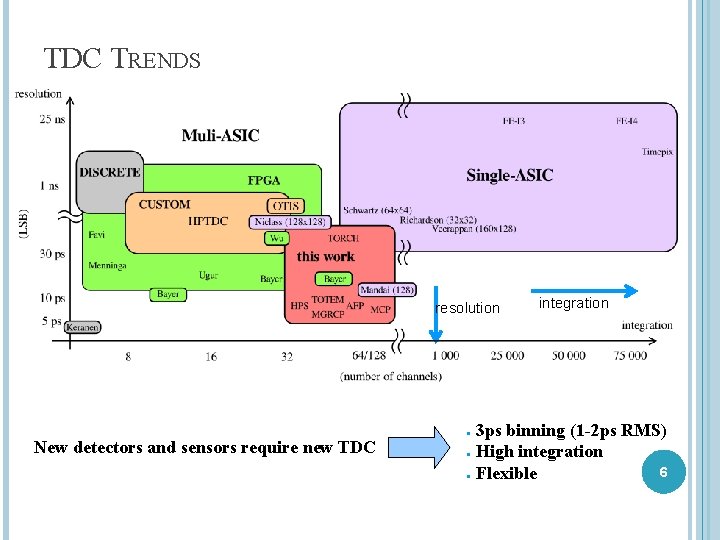

TDC TRENDS resolution New detectors and sensors require new TDC integration 3 ps binning (1 -2 ps RMS) ● High integration 6 ● Flexible ●

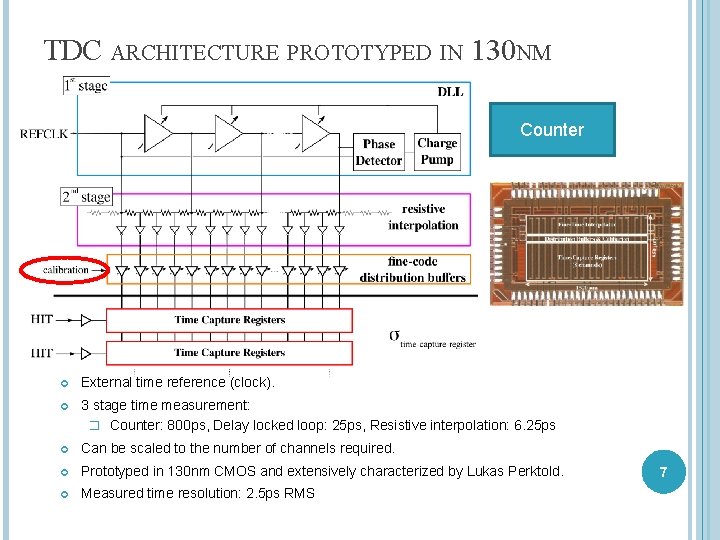

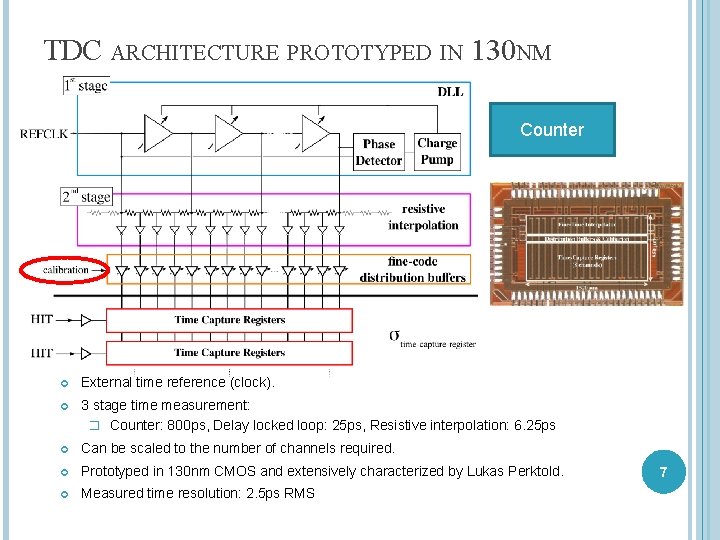

TDC ARCHITECTURE PROTOTYPED IN 130 NM Counter External time reference (clock). 3 stage time measurement: � Counter: 800 ps, Delay locked loop: 25 ps, Resistive interpolation: 6. 25 ps Can be scaled to the number of channels required. Prototyped in 130 nm CMOS and extensively characterized by Lukas Perktold. Measured time resolution: 2. 5 ps RMS 7

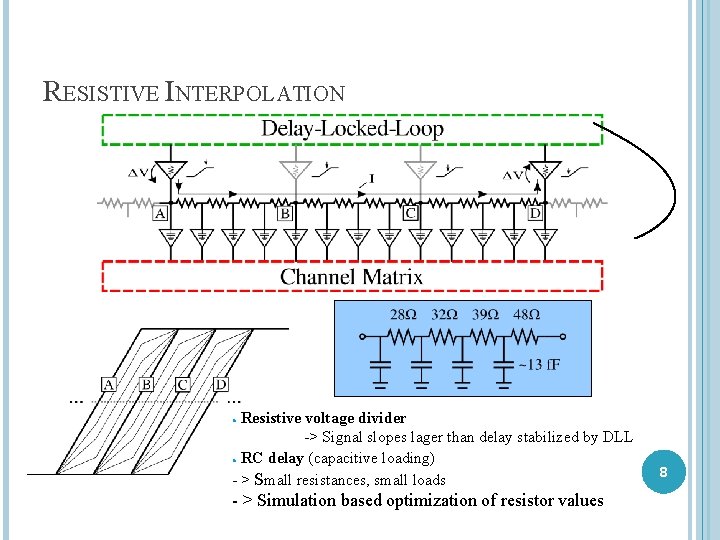

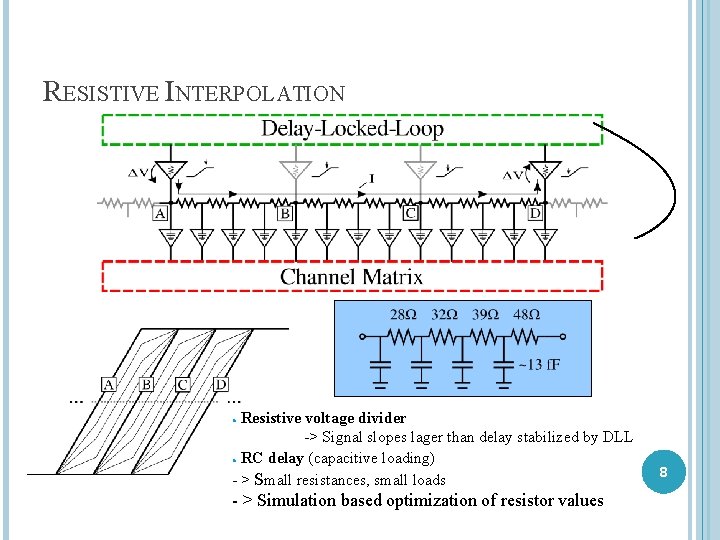

RESISTIVE INTERPOLATION Resistive voltage divider -> Signal slopes lager than delay stabilized by DLL ● RC delay (capacitive loading) - > Small resistances, small loads ● - > Simulation based optimization of resistor values 8

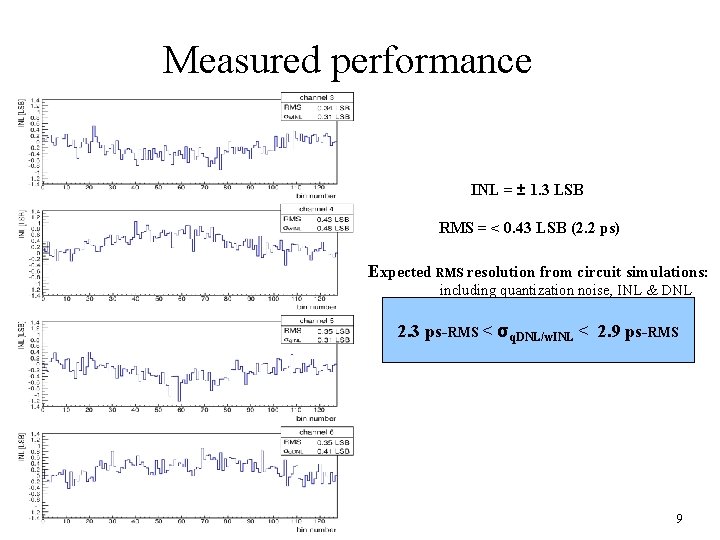

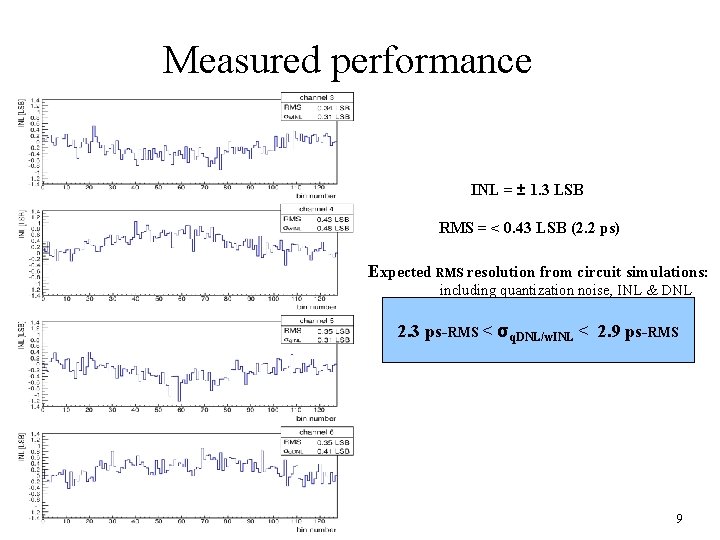

Measured performance INL = ± 1. 3 LSB RMS = < 0. 43 LSB (2. 2 ps) Expected RMS resolution from circuit simulations: including quantization noise, INL & DNL 2. 3 ps-RMS < σq. DNL/w. INL < 2. 9 ps-RMS 9

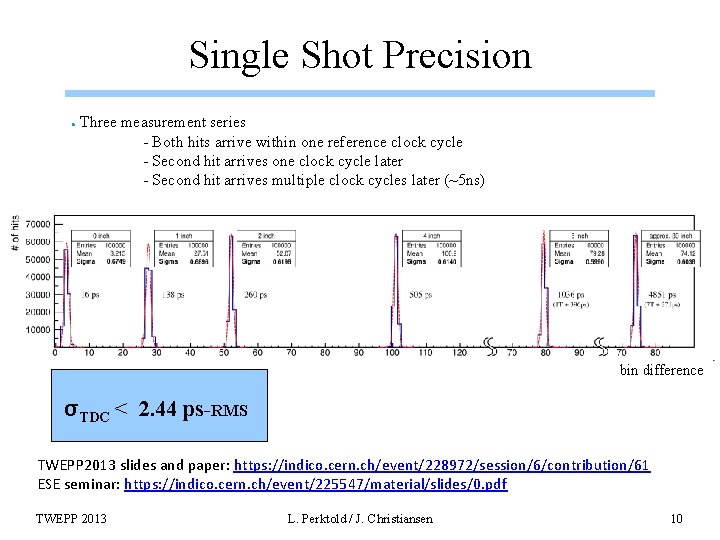

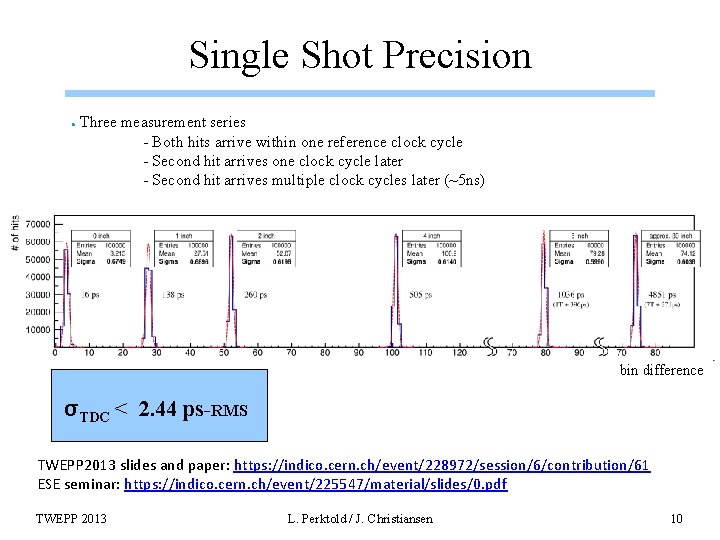

Single Shot Precision ● Three measurement series - Both hits arrive within one reference clock cycle - Second hit arrives one clock cycle later - Second hit arrives multiple clock cycles later (~5 ns) bin difference σTDC < 2. 44 ps-RMS TWEPP 2013 slides and paper: https: //indico. cern. ch/event/228972/session/6/contribution/61 ESE seminar: https: //indico. cern. ch/event/225547/material/slides/0. pdf TWEPP 2013 L. Perktold / J. Christiansen 10

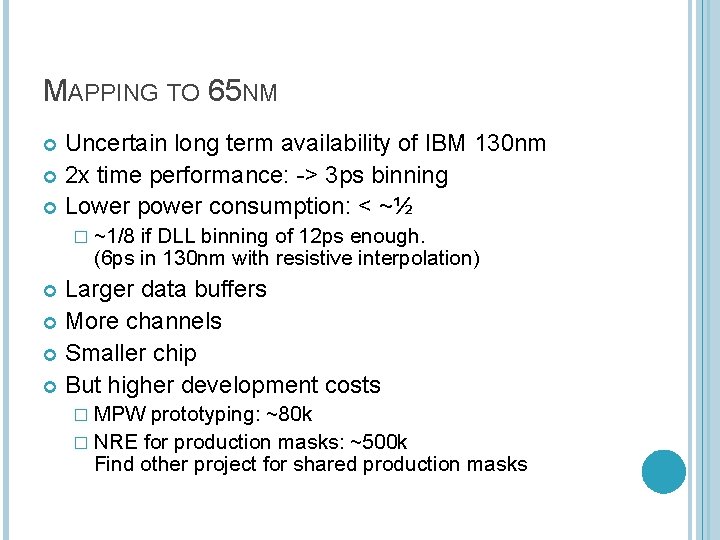

MAPPING TO 65 NM Uncertain long term availability of IBM 130 nm 2 x time performance: -> 3 ps binning Lower power consumption: < ~½ � ~1/8 if DLL binning of 12 ps enough. (6 ps in 130 nm with resistive interpolation) Larger data buffers More channels Smaller chip But higher development costs � MPW prototyping: ~80 k � NRE for production masks: ~500 k Find other project for shared production masks

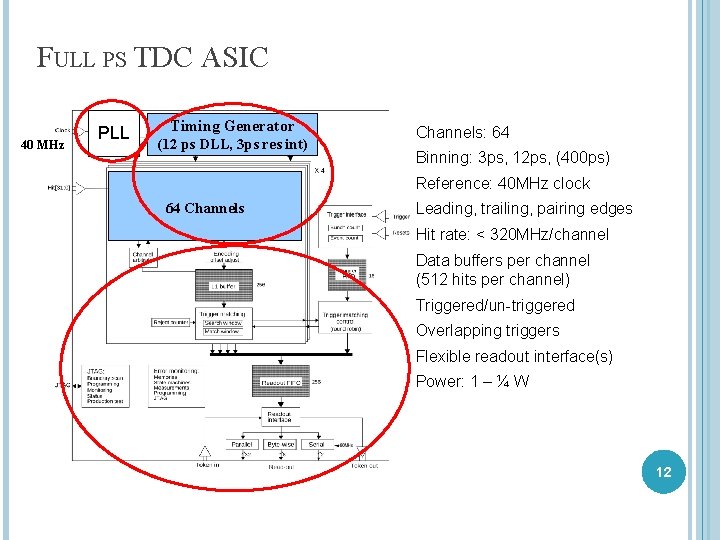

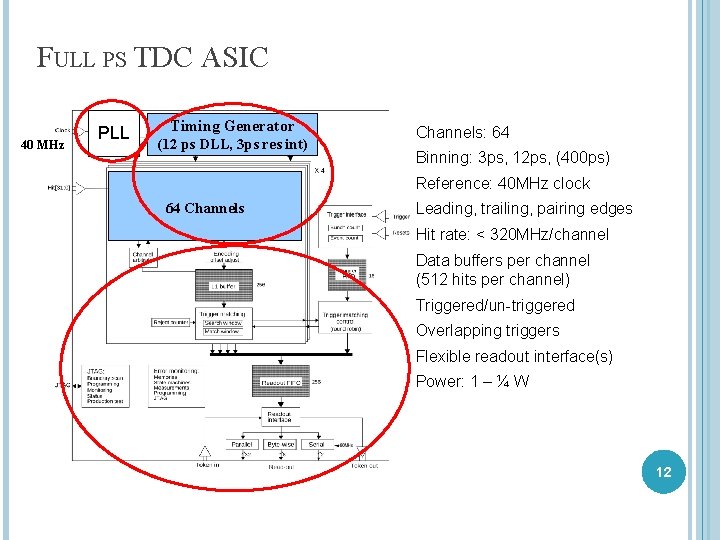

FULL PS TDC ASIC 40 MHz PLL Timing Generator (12 ps DLL, 3 ps res int) Channels: 64 Binning: 3 ps, 12 ps, (400 ps) Reference: 40 MHz clock 64 Channels Leading, trailing, pairing edges Hit rate: < 320 MHz/channel Data buffers per channel (512 hits per channel) Triggered/un-triggered Overlapping triggers Flexible readout interface(s) Power: 1 – ¼ W 12

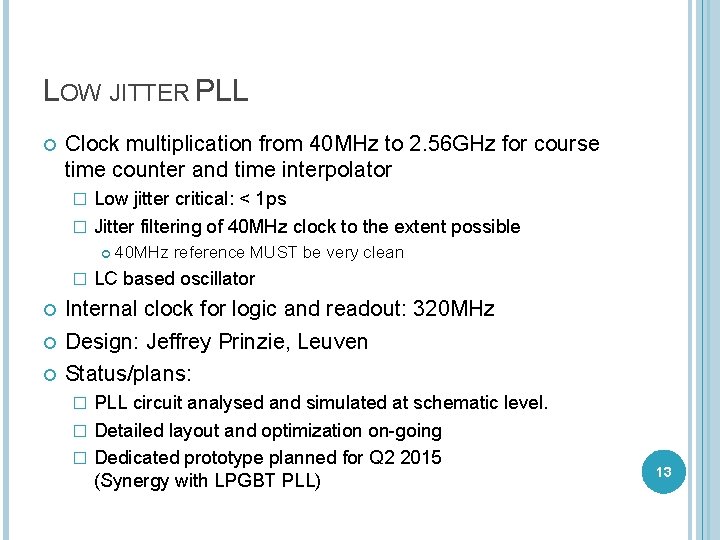

LOW JITTER PLL Clock multiplication from 40 MHz to 2. 56 GHz for course time counter and time interpolator Low jitter critical: < 1 ps � Jitter filtering of 40 MHz clock to the extent possible � � 40 MHz reference MUST be very clean LC based oscillator Internal clock for logic and readout: 320 MHz Design: Jeffrey Prinzie, Leuven Status/plans: PLL circuit analysed and simulated at schematic level. � Detailed layout and optimization on-going � Dedicated prototype planned for Q 2 2015 (Synergy with LPGBT PLL) � 13

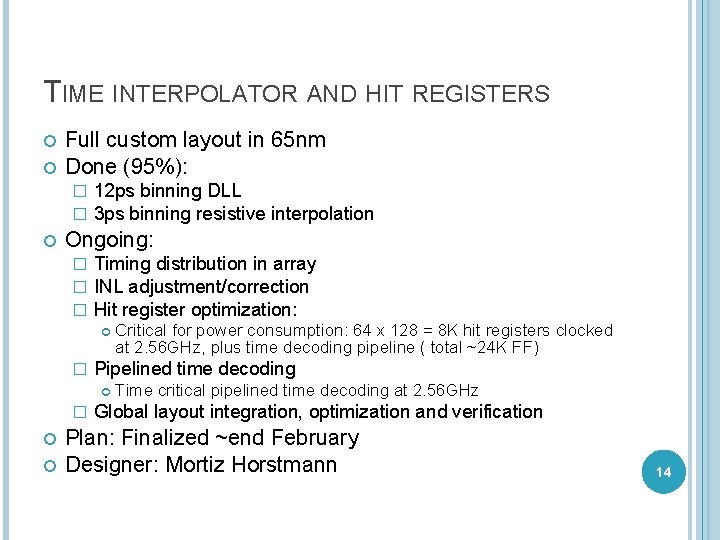

TIME INTERPOLATOR AND HIT REGISTERS Full custom layout in 65 nm Done (95%): � � 12 ps binning DLL 3 ps binning resistive interpolation Ongoing: � � � Timing distribution in array INL adjustment/correction Hit register optimization: � Pipelined time decoding � Critical for power consumption: 64 x 128 = 8 K hit registers clocked at 2. 56 GHz, plus time decoding pipeline ( total ~24 K FF) Time critical pipelined time decoding at 2. 56 GHz Global layout integration, optimization and verification Plan: Finalized ~end February Designer: Mortiz Horstmann 14

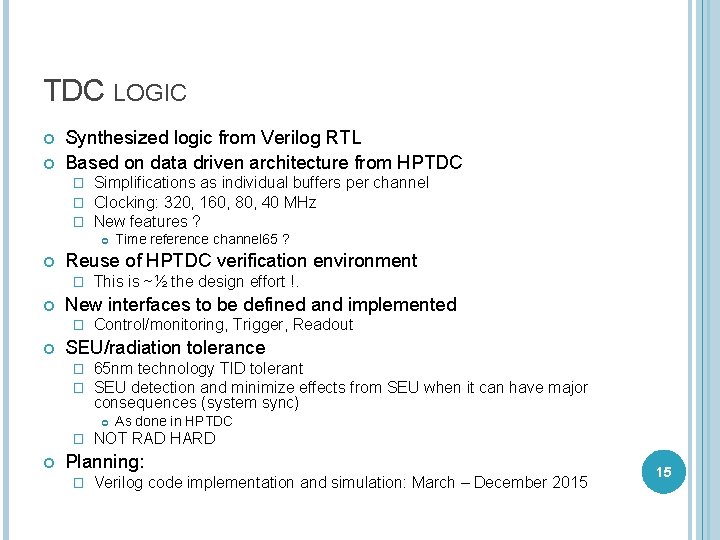

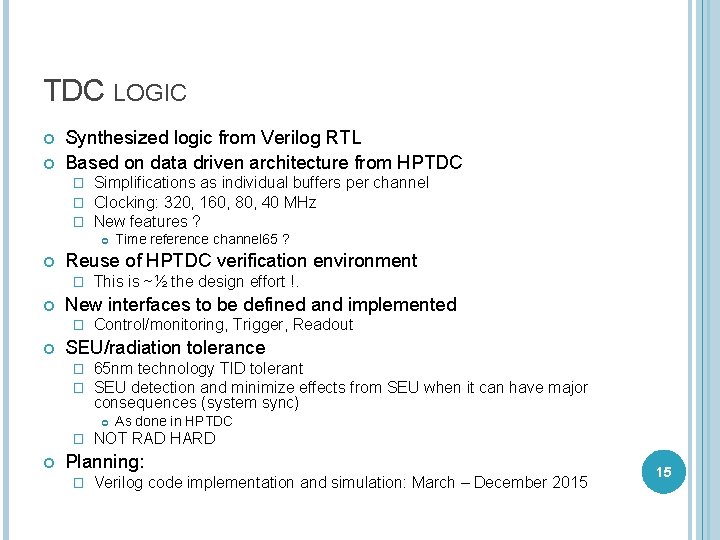

TDC LOGIC Synthesized logic from Verilog RTL Based on data driven architecture from HPTDC � � � Simplifications as individual buffers per channel Clocking: 320, 160, 80, 40 MHz New features ? Reuse of HPTDC verification environment � This is ~½ the design effort !. New interfaces to be defined and implemented � Control/monitoring, Trigger, Readout SEU/radiation tolerance � � 65 nm technology TID tolerant SEU detection and minimize effects from SEU when it can have major consequences (system sync) � Time reference channel 65 ? As done in HPTDC NOT RAD HARD Planning: � Verilog code implementation and simulation: March – December 2015 15

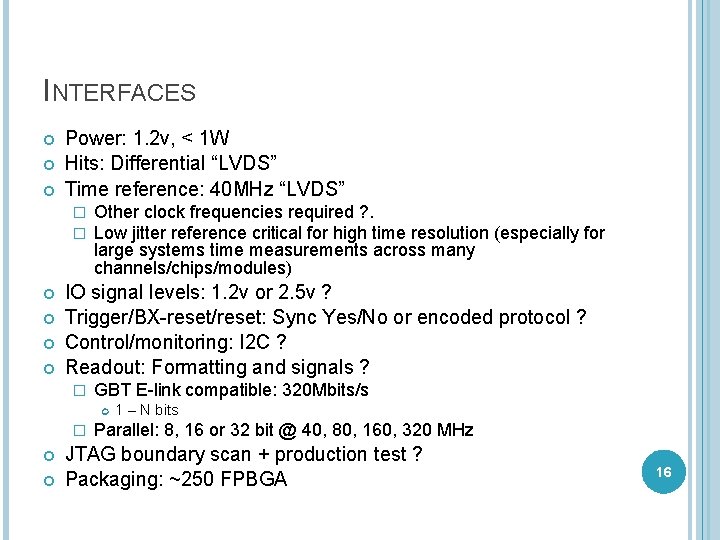

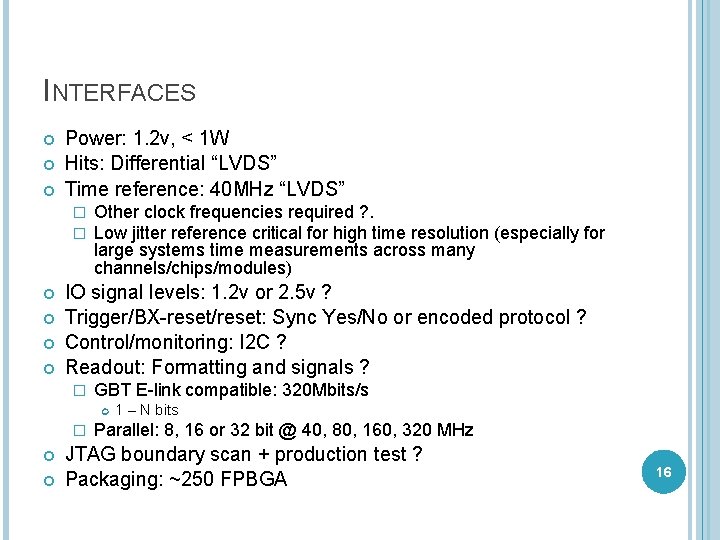

INTERFACES Power: 1. 2 v, < 1 W Hits: Differential “LVDS” Time reference: 40 MHz “LVDS” � � Other clock frequencies required ? . Low jitter reference critical for high time resolution (especially for large systems time measurements across many channels/chips/modules) IO signal levels: 1. 2 v or 2. 5 v ? Trigger/BX-reset/reset: Sync Yes/No or encoded protocol ? Control/monitoring: I 2 C ? Readout: Formatting and signals ? � GBT E-link compatible: 320 Mbits/s � 1 – N bits Parallel: 8, 16 or 32 bit @ 40, 80, 160, 320 MHz JTAG boundary scan + production test ? Packaging: ~250 FPBGA 16

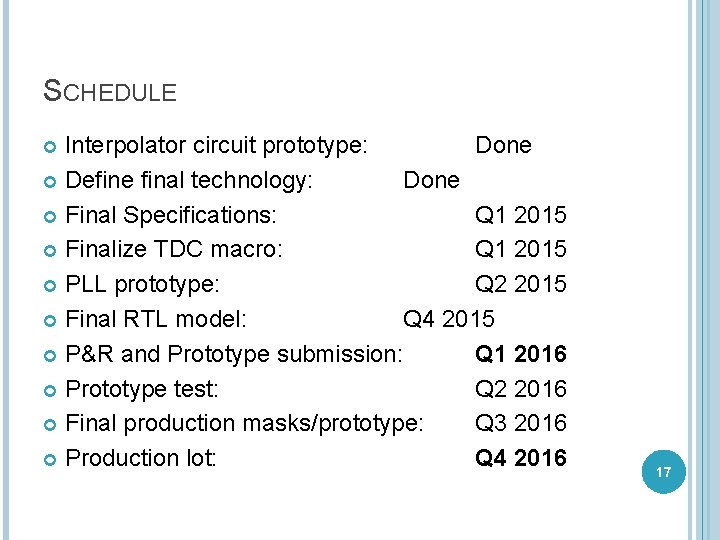

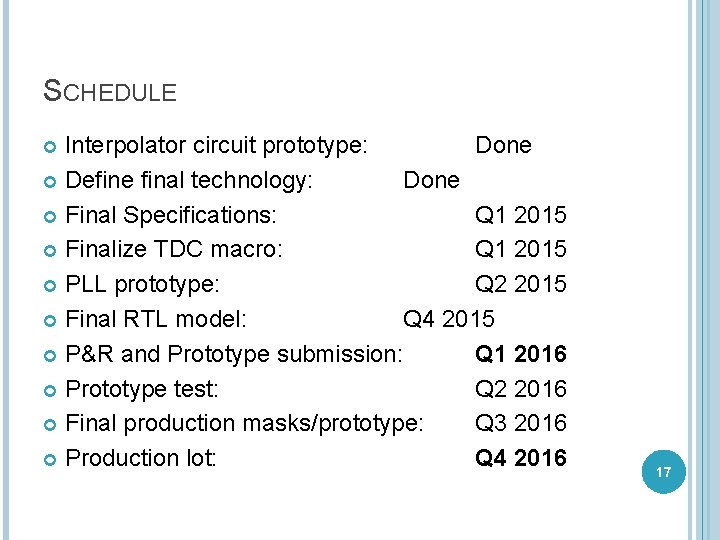

SCHEDULE Interpolator circuit prototype: Done Define final technology: Done Final Specifications: Q 1 2015 Finalize TDC macro: Q 1 2015 PLL prototype: Q 2 2015 Final RTL model: Q 4 2015 P&R and Prototype submission: Q 1 2016 Prototype test: Q 2 2016 Final production masks/prototype: Q 3 2016 Production lot: Q 4 2016 17

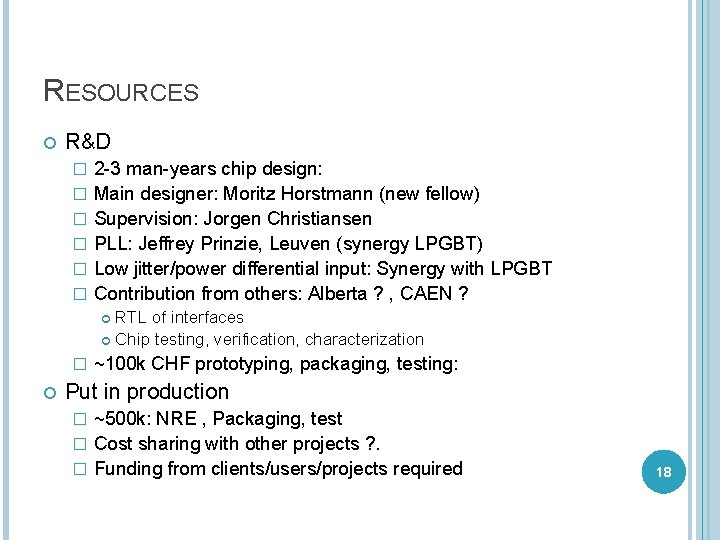

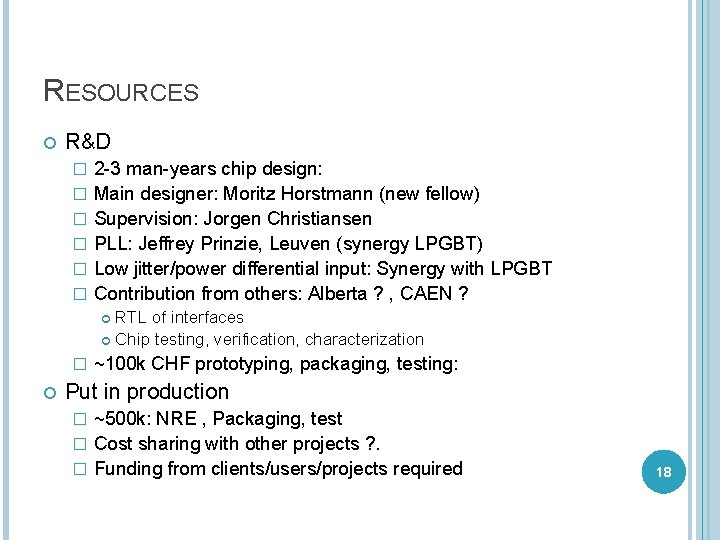

RESOURCES R&D � � � 2 -3 man-years chip design: Main designer: Moritz Horstmann (new fellow) Supervision: Jorgen Christiansen PLL: Jeffrey Prinzie, Leuven (synergy LPGBT) Low jitter/power differential input: Synergy with LPGBT Contribution from others: Alberta ? , CAEN ? RTL of interfaces Chip testing, verification, characterization � ~100 k CHF prototyping, packaging, testing: Put in production ~500 k: NRE , Packaging, test � Cost sharing with other projects ? . � Funding from clients/users/projects required � 18

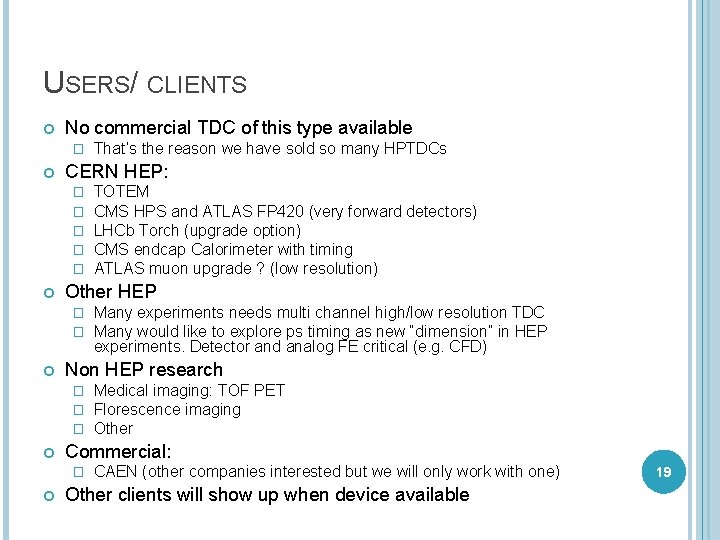

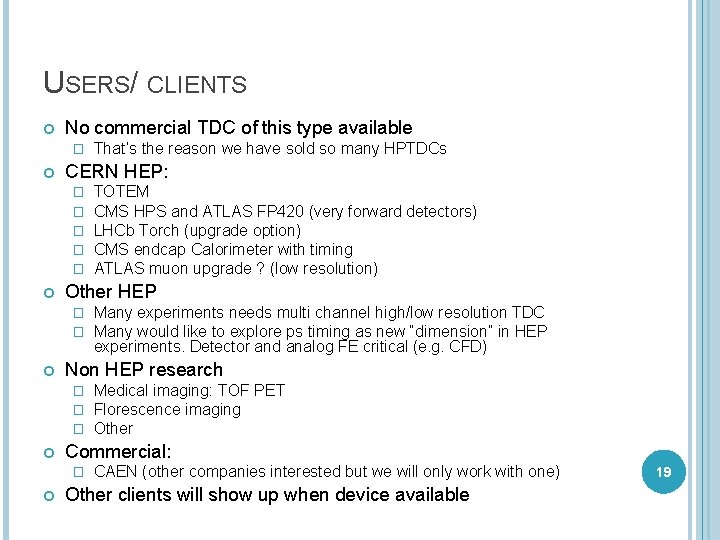

USERS/ CLIENTS No commercial TDC of this type available � CERN HEP: � � � Medical imaging: TOF PET Florescence imaging Other Commercial: � Many experiments needs multi channel high/low resolution TDC Many would like to explore ps timing as new “dimension” in HEP experiments. Detector and analog FE critical (e. g. CFD) Non HEP research � � � TOTEM CMS HPS and ATLAS FP 420 (very forward detectors) LHCb Torch (upgrade option) CMS endcap Calorimeter with timing ATLAS muon upgrade ? (low resolution) Other HEP � � That’s the reason we have sold so many HPTDCs CAEN (other companies interested but we will only work with one) Other clients will show up when device available 19

BACKUP SLIDES 20

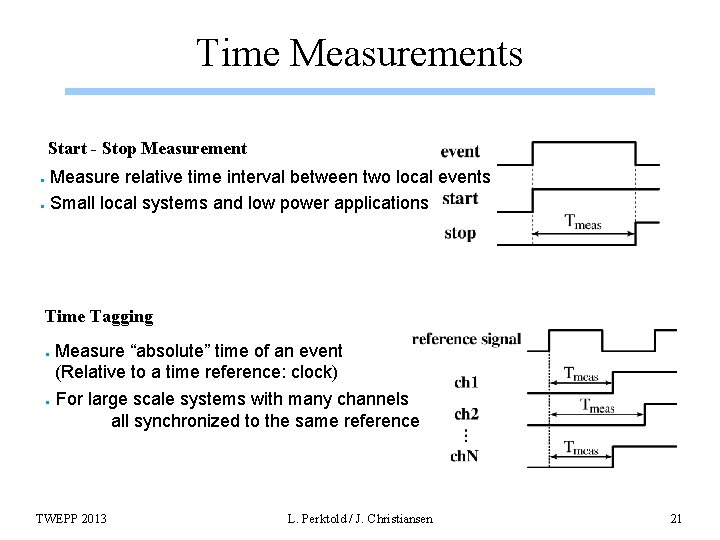

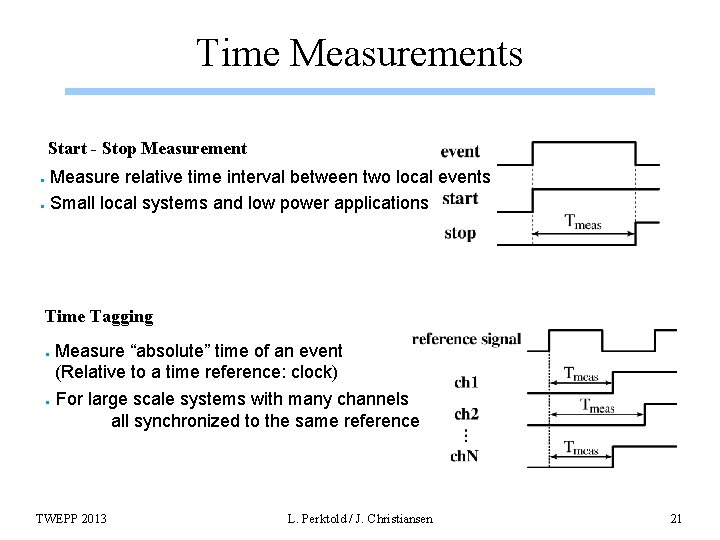

Time Measurements Start - Stop Measurement Measure relative time interval between two local events ● Small local systems and low power applications ● Time Tagging Measure “absolute” time of an event (Relative to a time reference: clock) ● For large scale systems with many channels all synchronized to the same reference ● TWEPP 2013 L. Perktold / J. Christiansen 21

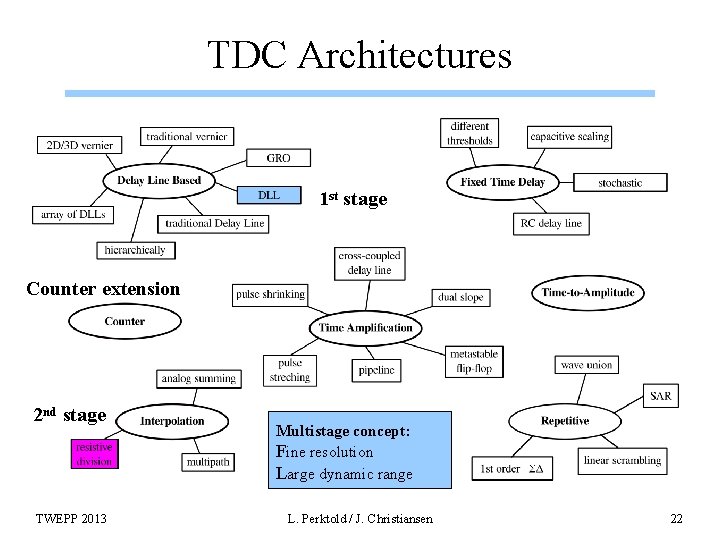

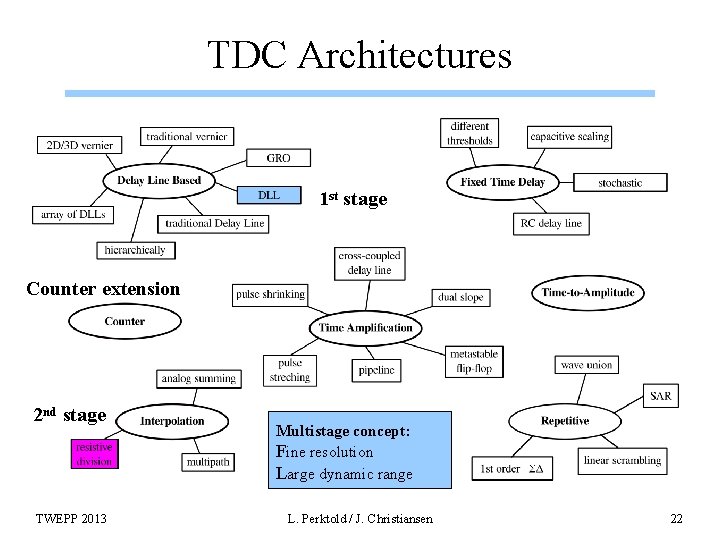

TDC Architectures 1 st stage Counter extension 2 nd stage TWEPP 2013 Multistage concept: Fine resolution Large dynamic range L. Perktold / J. Christiansen 22

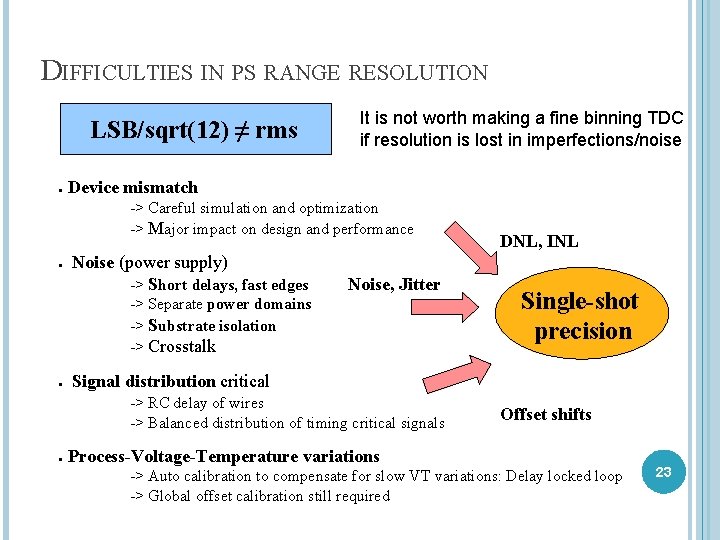

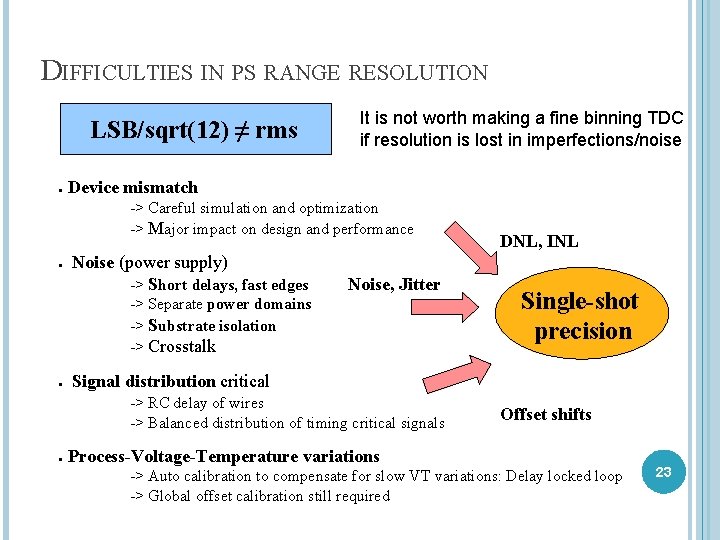

DIFFICULTIES IN PS RANGE RESOLUTION LSB/sqrt(12) ≠ rms ● It is not worth making a fine binning TDC if resolution is lost in imperfections/noise Device mismatch -> Careful simulation and optimization -> Major impact on design and performance ● Noise (power supply) -> Short delays, fast edges Noise, Jitter -> Separate power domains -> Substrate isolation -> Crosstalk ● Single-shot precision Signal distribution critical -> RC delay of wires -> Balanced distribution of timing critical signals ● DNL, INL Offset shifts Process-Voltage-Temperature variations -> Auto calibration to compensate for slow VT variations: Delay locked loop -> Global offset calibration still required 23

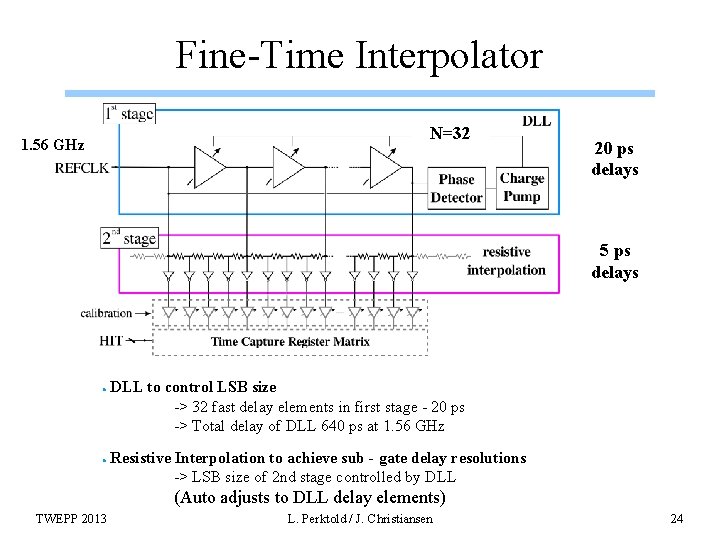

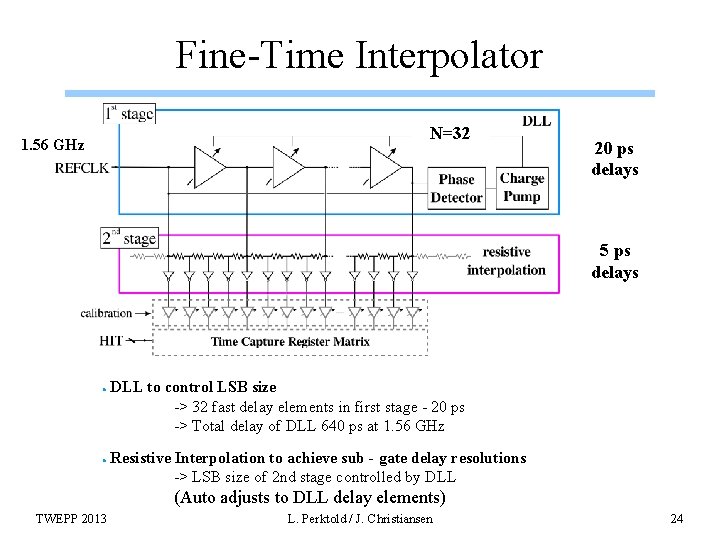

Fine-Time Interpolator N=32 1. 56 GHz 20 ps delays 5 ps delays ● ● DLL to control LSB size -> 32 fast delay elements in first stage - 20 ps -> Total delay of DLL 640 ps at 1. 56 GHz Resistive Interpolation to achieve sub - gate delay resolutions -> LSB size of 2 nd stage controlled by DLL (Auto adjusts to DLL delay elements) TWEPP 2013 L. Perktold / J. Christiansen 24

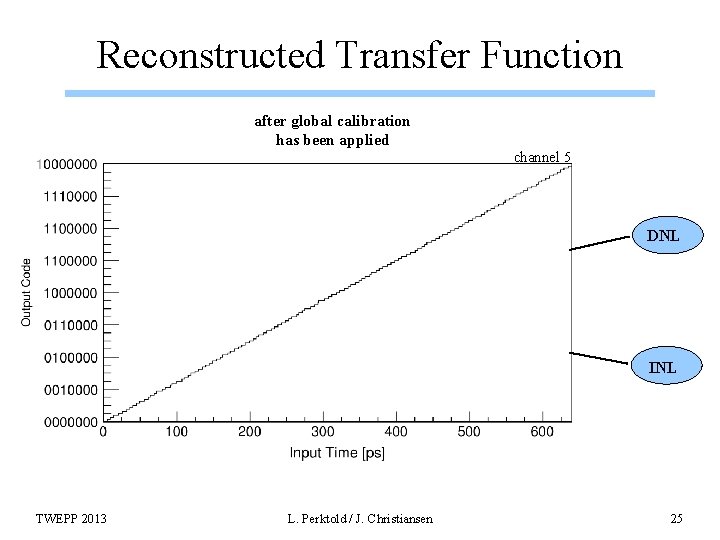

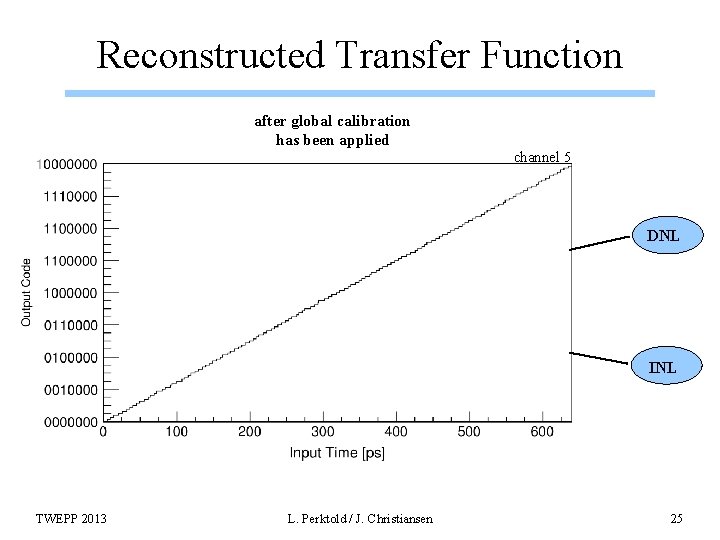

Reconstructed Transfer Function after global calibration has been applied channel 5 DNL INL TWEPP 2013 L. Perktold / J. Christiansen 25

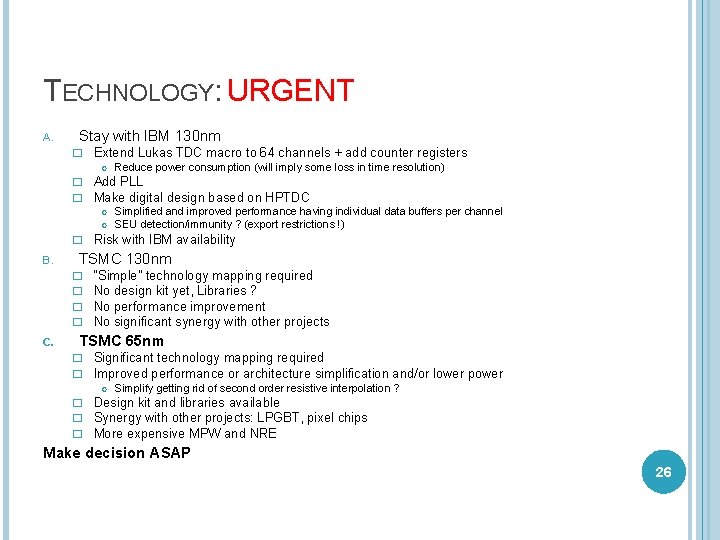

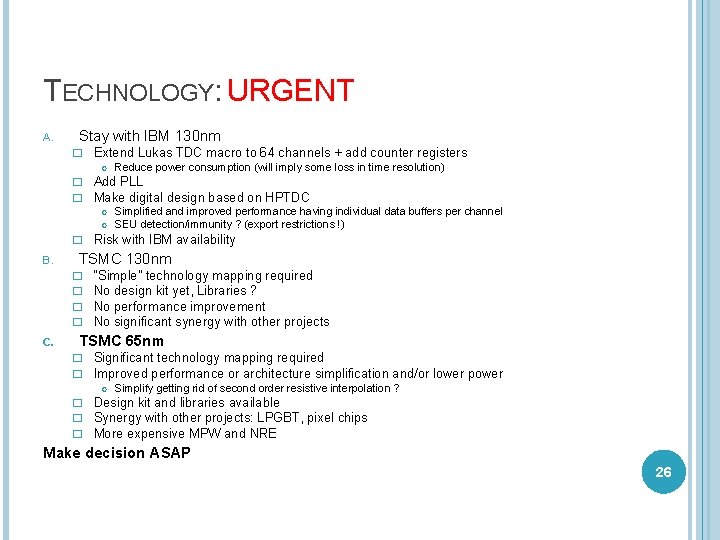

TECHNOLOGY: URGENT A. Stay with IBM 130 nm � Extend Lukas TDC macro to 64 channels + add counter registers Reduce power consumption (will imply some loss in time resolution) � Add PLL � Make digital design based on HPTDC Simplified and improved performance having individual data buffers per channel SEU detection/immunity ? (export restrictions !) � Risk with IBM availability B. TSMC 130 nm � � C. “Simple” technology mapping required No design kit yet, Libraries ? No performance improvement No significant synergy with other projects TSMC 65 nm � Significant technology mapping required � Improved performance or architecture simplification and/or lower power Simplify getting rid of second order resistive interpolation ? � Design kit and libraries available � Synergy with other projects: LPGBT, pixel chips � More expensive MPW and NRE Make decision ASAP 26