NetworkonChip An Overview SystemonChip Group CSEIMM DTU SystemonChip

- Slides: 24

Network-on-Chip An Overview System-on-Chip Group, CSE-IMM, DTU © System-on-Chip Group, CSE-IMM, DTU

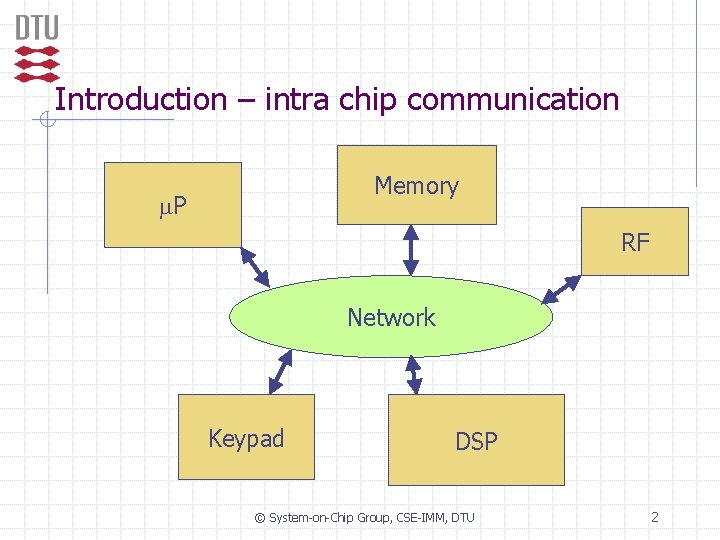

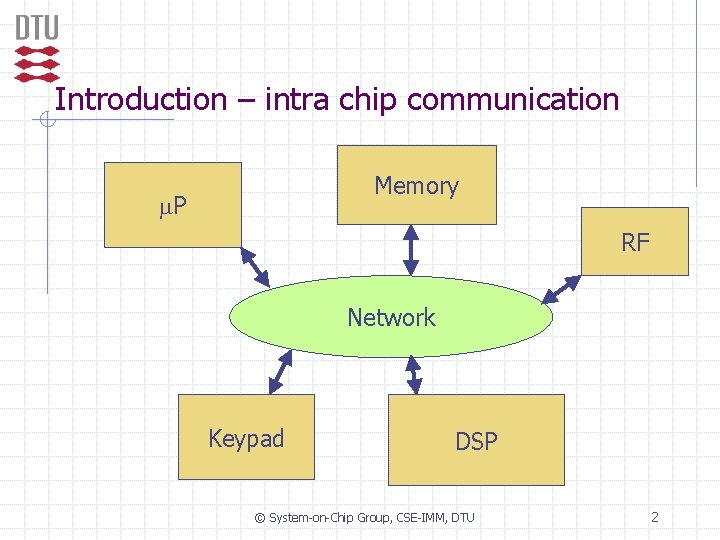

Introduction – intra chip communication Memory m. P RF Network Keypad DSP © System-on-Chip Group, CSE-IMM, DTU 2

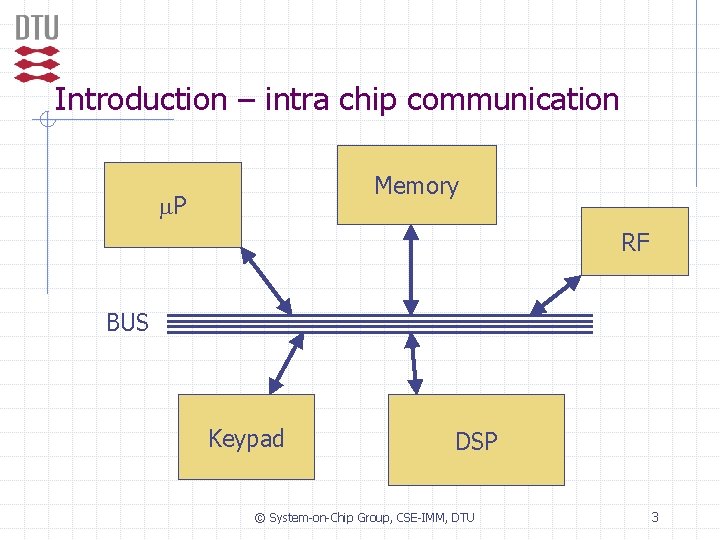

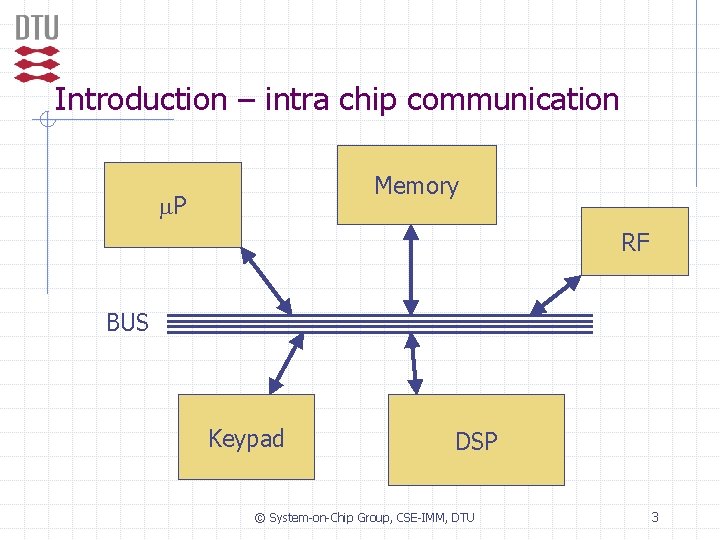

Introduction – intra chip communication Memory m. P RF BUS Keypad DSP © System-on-Chip Group, CSE-IMM, DTU 3

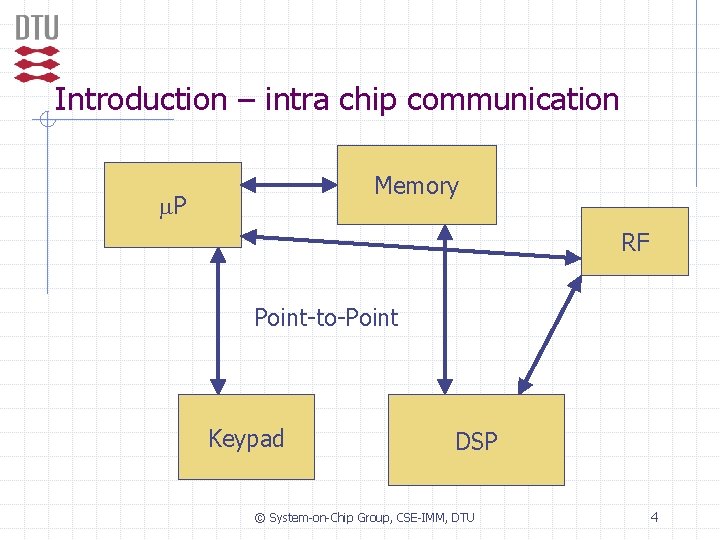

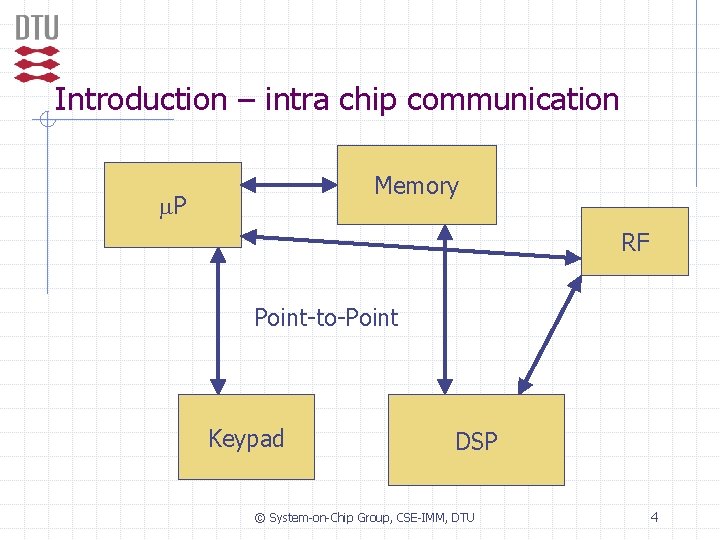

Introduction – intra chip communication Memory m. P RF Point-to-Point Keypad DSP © System-on-Chip Group, CSE-IMM, DTU 4

Overview • • Important Paradigms Network Abstraction Performance Evaluation Research Opportunities © System-on-Chip Group, CSE-IMM, DTU 5

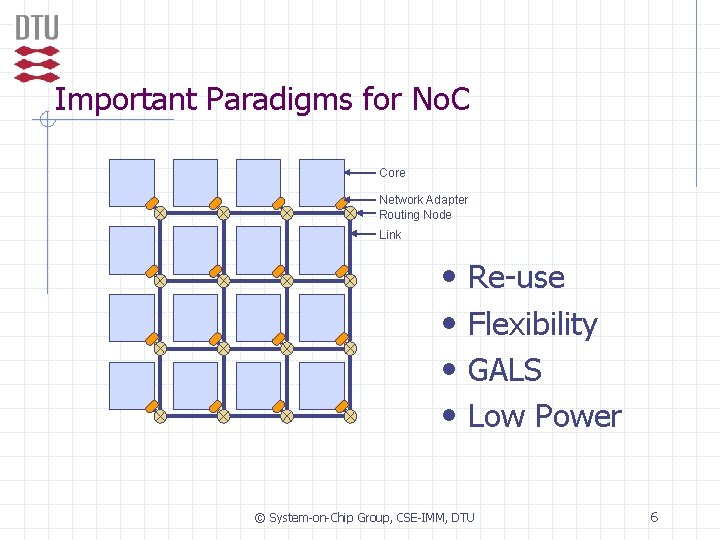

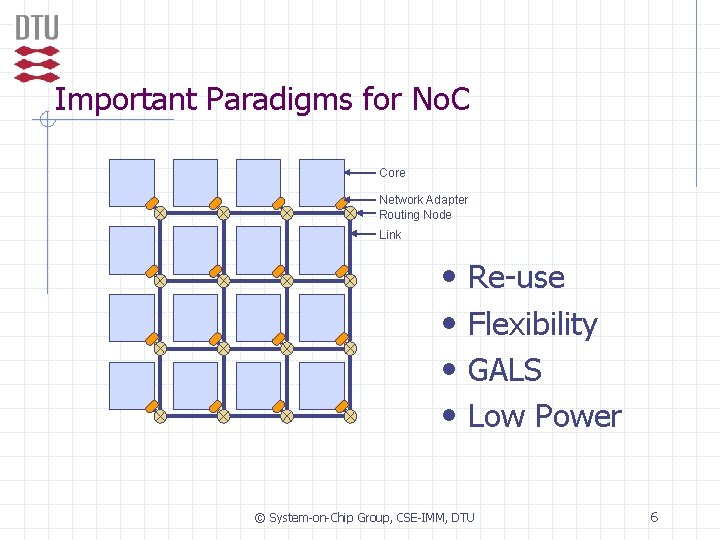

Important Paradigms for No. C Core Network Adapter Routing Node Link • • Re-use Flexibility GALS Low Power © System-on-Chip Group, CSE-IMM, DTU 6

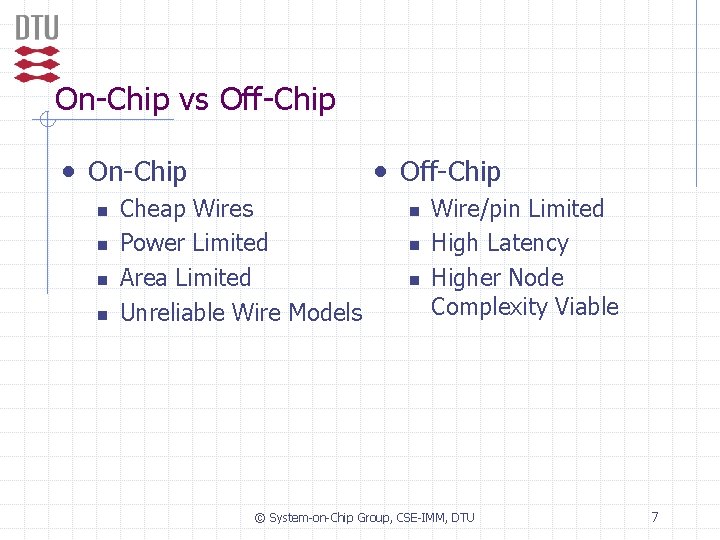

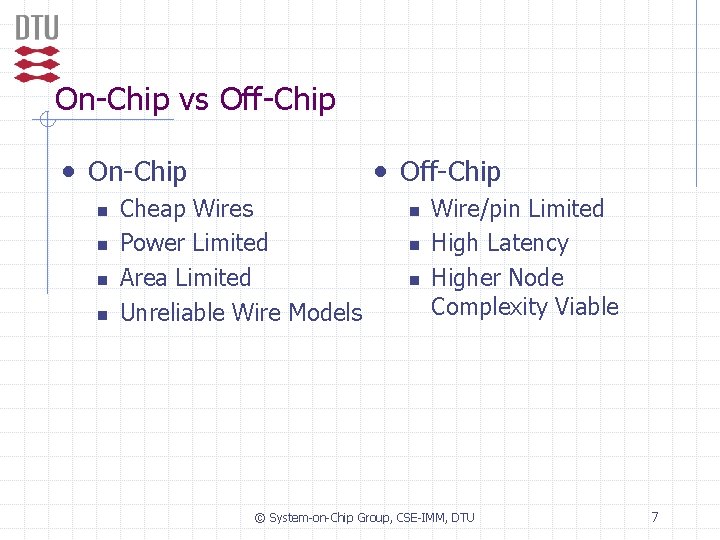

On-Chip vs Off-Chip • On-Chip n n • Off-Chip Cheap Wires Power Limited Area Limited Unreliable Wire Models n n n Wire/pin Limited High Latency Higher Node Complexity Viable © System-on-Chip Group, CSE-IMM, DTU 7

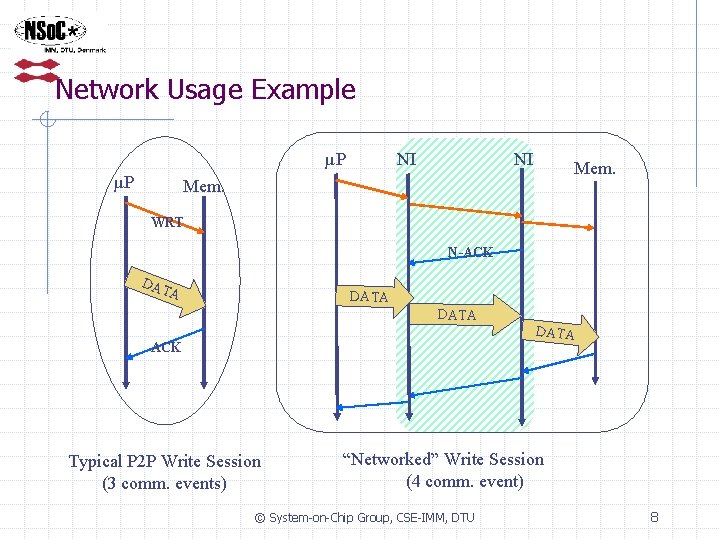

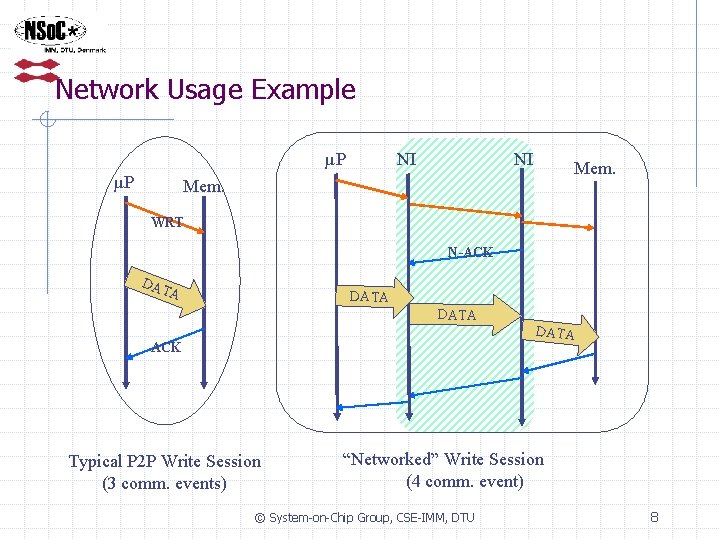

Network Usage Example µP µP NI NI Mem. WRT N-ACK DA TA DATA ACK Typical P 2 P Write Session (3 comm. events) “Networked” Write Session (4 comm. event) © System-on-Chip Group, CSE-IMM, DTU 8

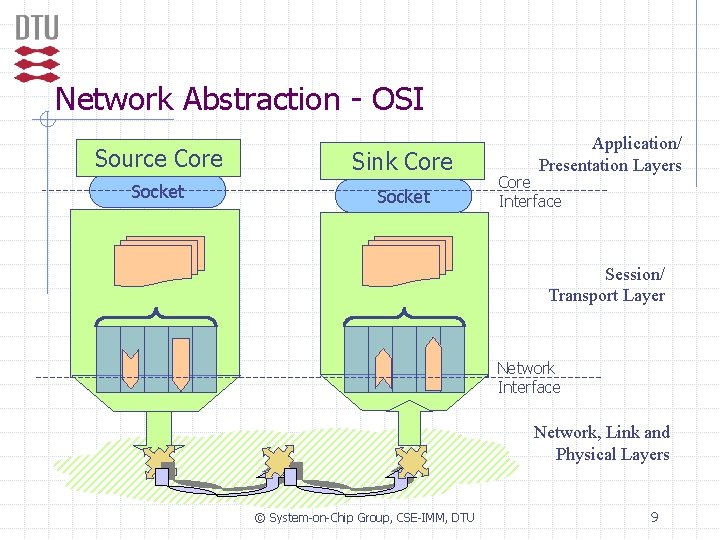

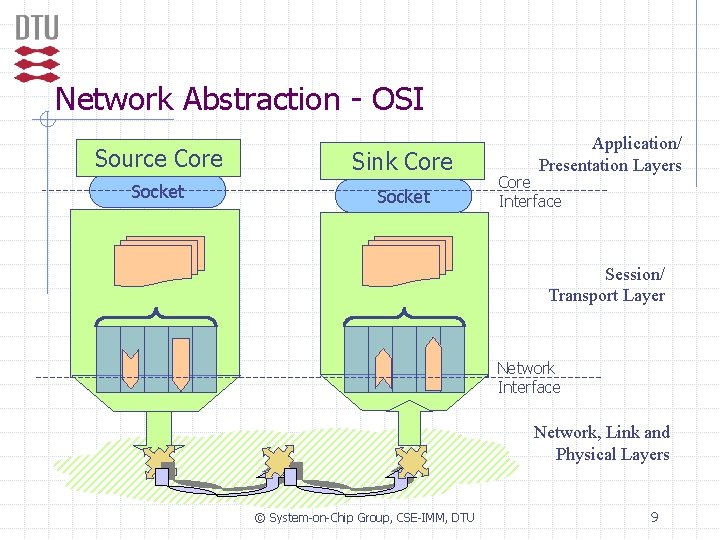

Network Abstraction - OSI Source Core Sink Core Socket Application/ Presentation Layers Core Interface Session/ Transport Layer Network Interface Network, Link and Physical Layers © System-on-Chip Group, CSE-IMM, DTU 9

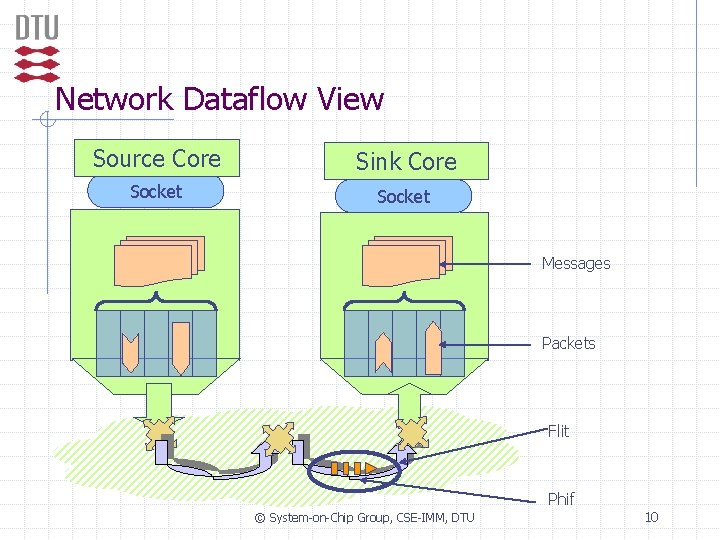

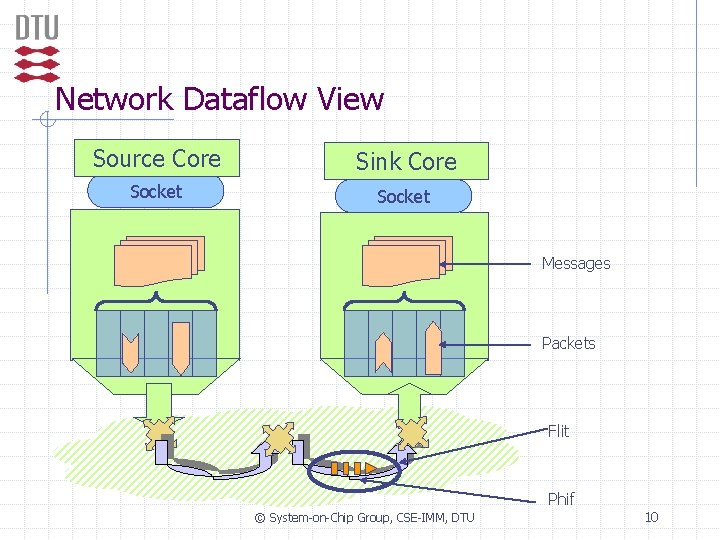

Network Dataflow View Source Core Sink Core Socket Messages Packets Flit Phif © System-on-Chip Group, CSE-IMM, DTU 10

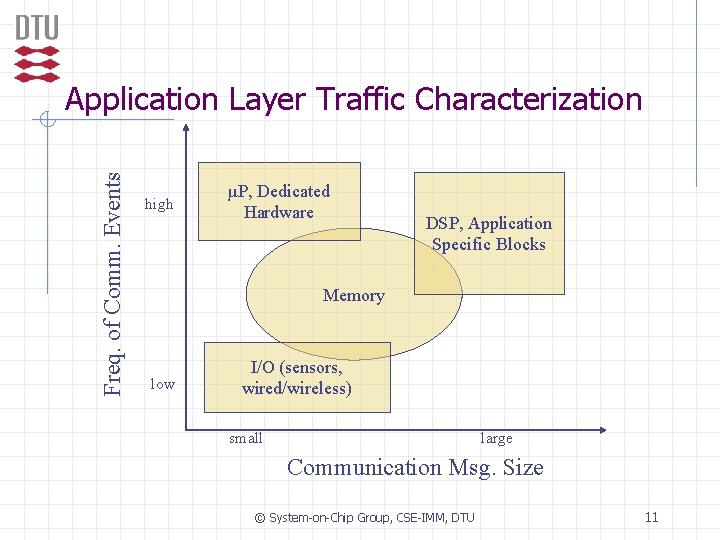

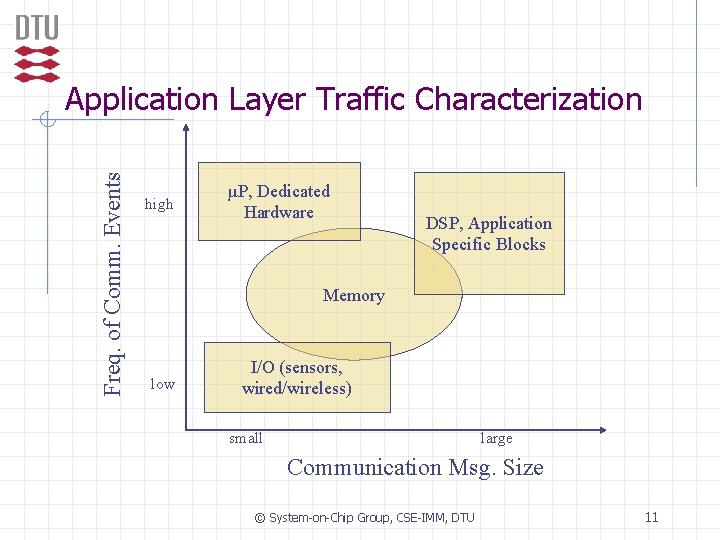

Freq. of Comm. Events Application Layer Traffic Characterization high µP, Dedicated Hardware DSP, Application Specific Blocks Memory low I/O (sensors, wired/wireless) small large Communication Msg. Size © System-on-Chip Group, CSE-IMM, DTU 11

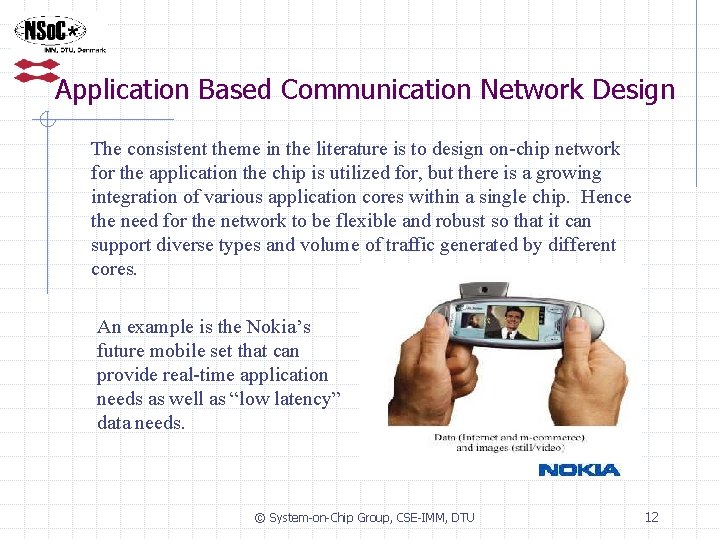

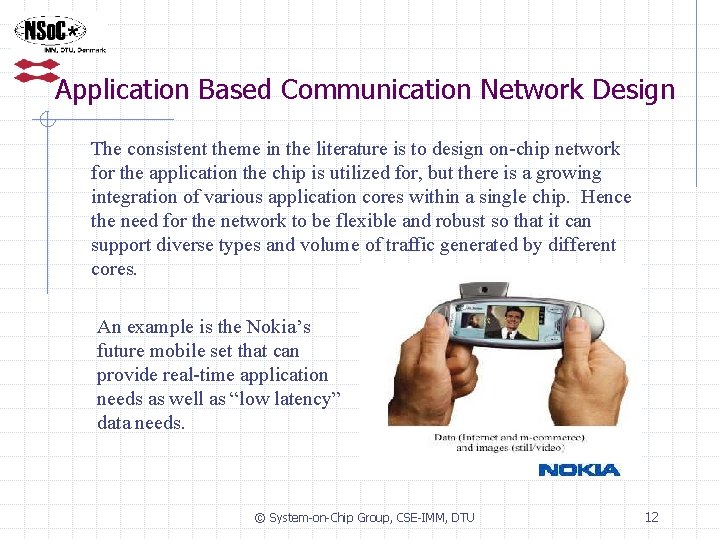

Application Based Communication Network Design The consistent theme in the literature is to design on-chip network for the application the chip is utilized for, but there is a growing integration of various application cores within a single chip. Hence the need for the network to be flexible and robust so that it can support diverse types and volume of traffic generated by different cores. An example is the Nokia’s future mobile set that can provide real-time application needs as well as “low latency” data needs. © System-on-Chip Group, CSE-IMM, DTU 12

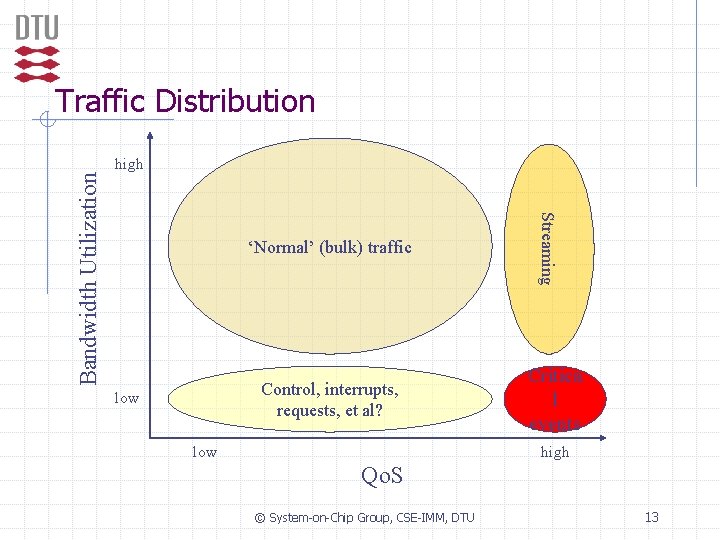

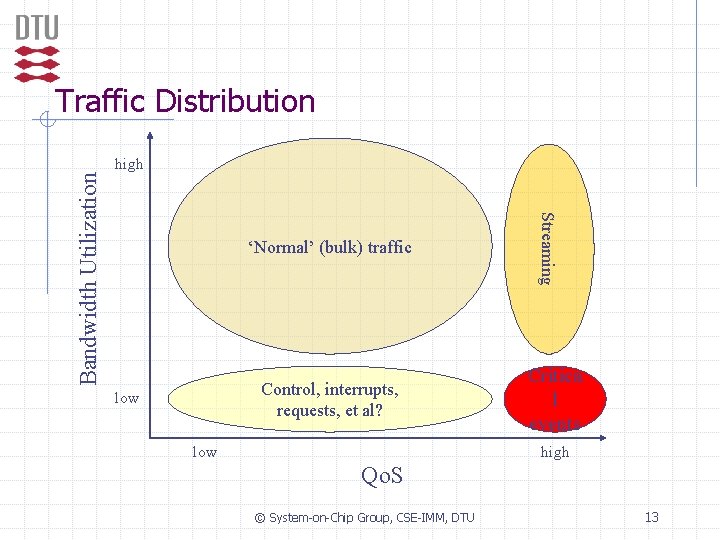

high ‘Normal’ (bulk) traffic Control, interrupts, requests, et al? low Streaming Bandwidth Utilization Traffic Distribution Critica l events high Qo. S © System-on-Chip Group, CSE-IMM, DTU 13

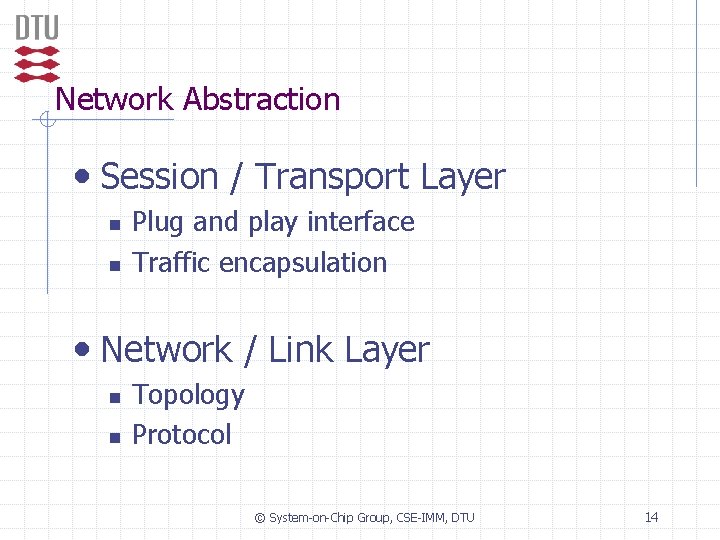

Network Abstraction • Session / Transport Layer n n Plug and play interface Traffic encapsulation • Network / Link Layer n n Topology Protocol © System-on-Chip Group, CSE-IMM, DTU 14

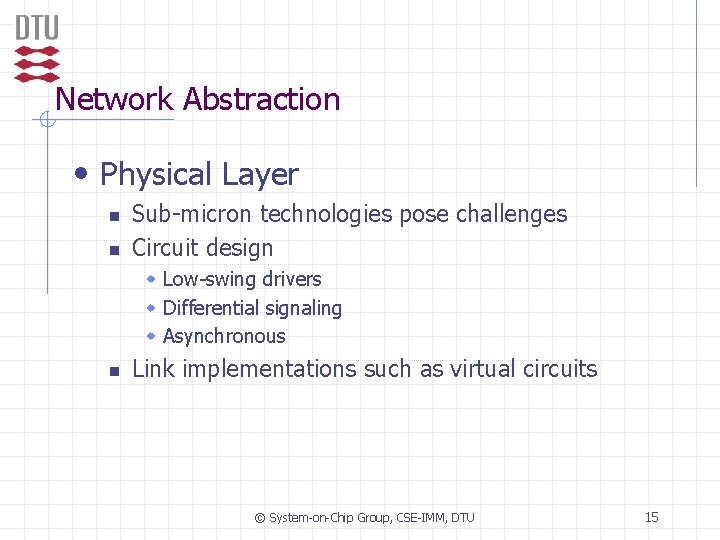

Network Abstraction • Physical Layer n n Sub-micron technologies pose challenges Circuit design w Low-swing drivers w Differential signaling w Asynchronous n Link implementations such as virtual circuits © System-on-Chip Group, CSE-IMM, DTU 15

Networks-on-Chip Many combinations! How to judge trade-offs? ! © System-on-Chip Group, CSE-IMM, DTU 16

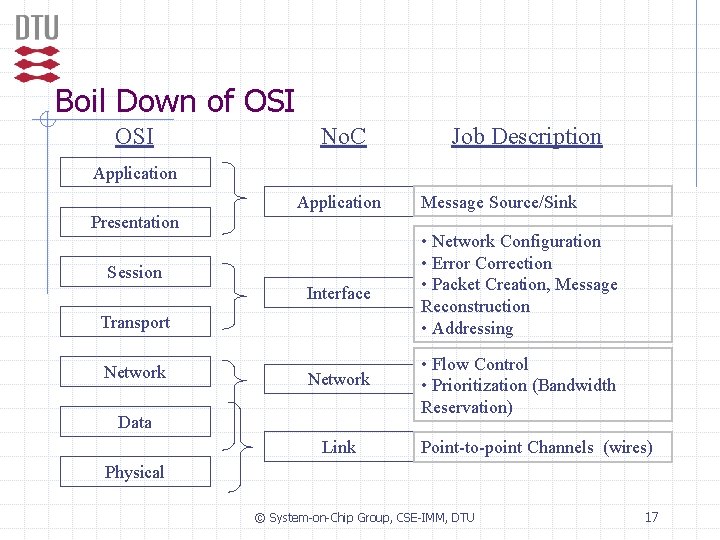

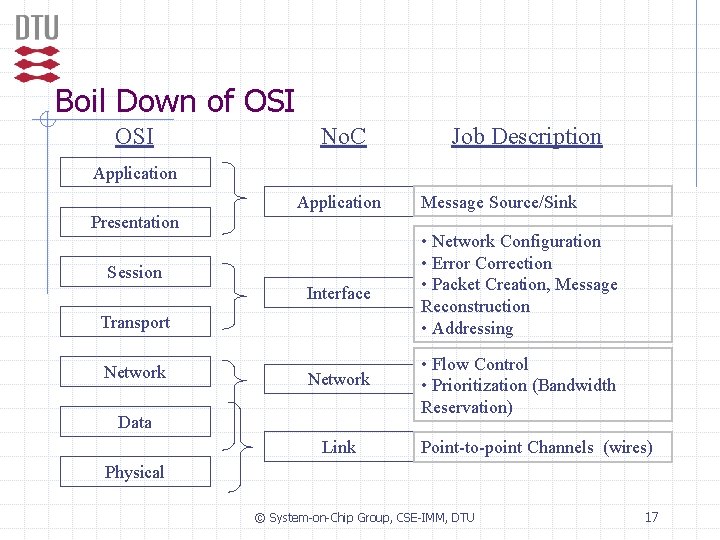

Boil Down of OSI No. C Job Description Application Presentation Interface • Network Configuration • Error Correction • Packet Creation, Message Reconstruction • Addressing Network • Flow Control • Prioritization (Bandwidth Reservation) Session Transport Network Message Source/Sink Data Link Point-to-point Channels (wires) Physical © System-on-Chip Group, CSE-IMM, DTU 17

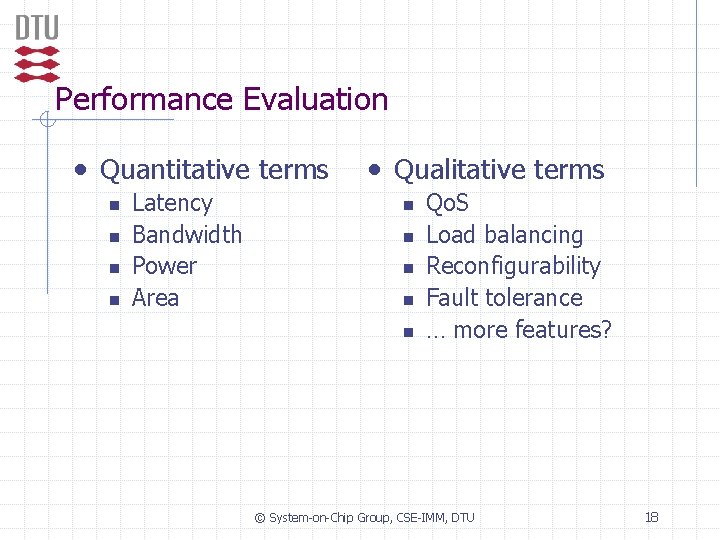

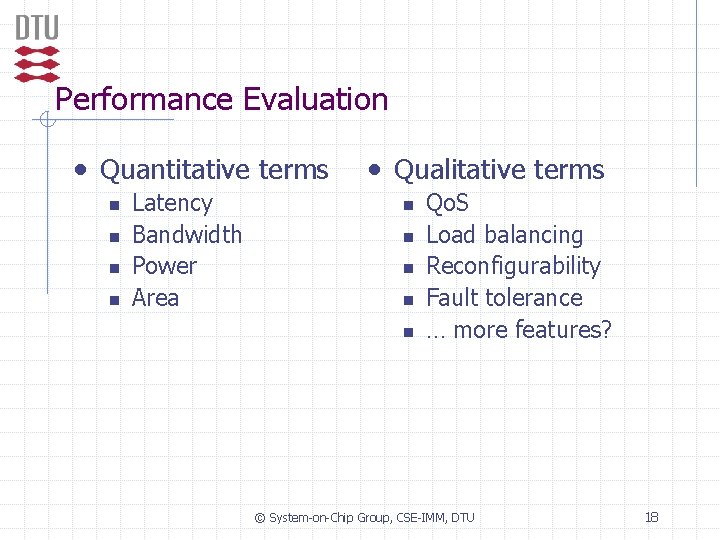

Performance Evaluation • Quantitative terms n n Latency Bandwidth Power Area • Qualitative terms n n n Qo. S Load balancing Reconfigurability Fault tolerance … more features? © System-on-Chip Group, CSE-IMM, DTU 18

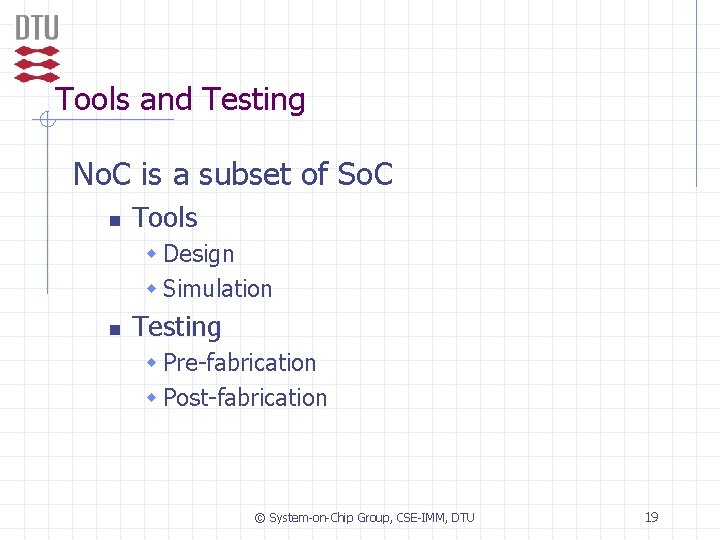

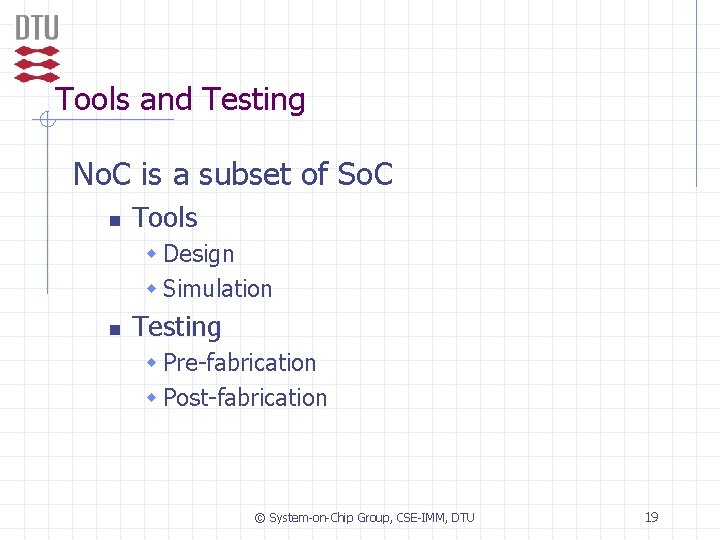

Tools and Testing No. C is a subset of So. C n Tools w Design w Simulation n Testing w Pre-fabrication w Post-fabrication © System-on-Chip Group, CSE-IMM, DTU 19

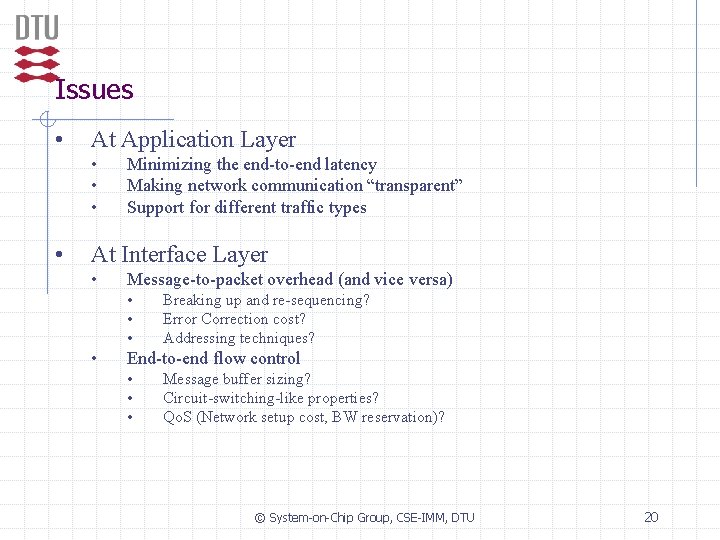

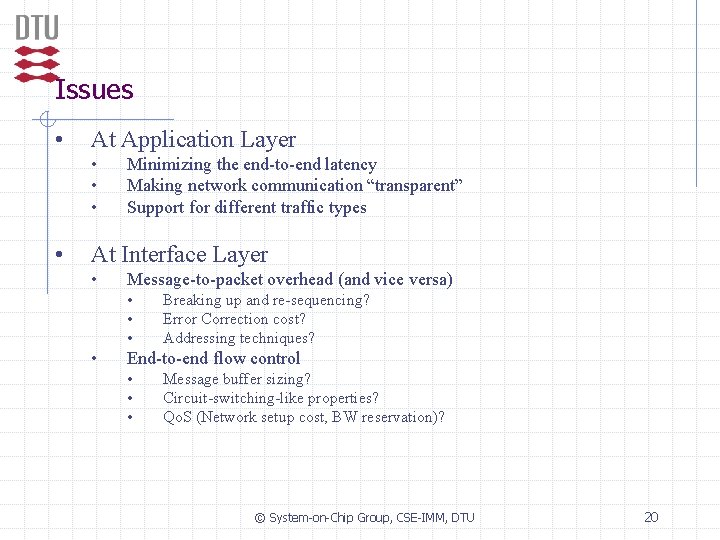

Issues • At Application Layer • • Minimizing the end-to-end latency Making network communication “transparent” Support for different traffic types At Interface Layer • Message-to-packet overhead (and vice versa) • • Breaking up and re-sequencing? Error Correction cost? Addressing techniques? End-to-end flow control • • • Message buffer sizing? Circuit-switching-like properties? Qo. S (Network setup cost, BW reservation)? © System-on-Chip Group, CSE-IMM, DTU 20

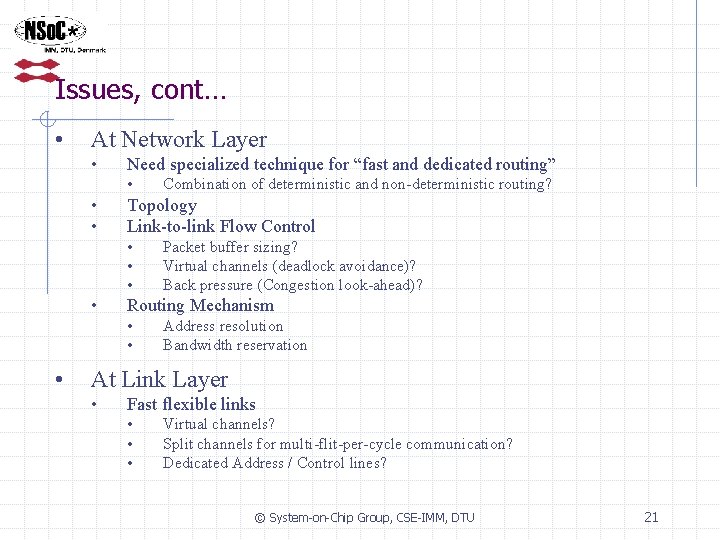

Issues, cont… • At Network Layer • Need specialized technique for “fast and dedicated routing” • • • Topology Link-to-link Flow Control • • Packet buffer sizing? Virtual channels (deadlock avoidance)? Back pressure (Congestion look-ahead)? Routing Mechanism • • • Combination of deterministic and non-deterministic routing? Address resolution Bandwidth reservation At Link Layer • Fast flexible links • • • Virtual channels? Split channels for multi-flit-per-cycle communication? Dedicated Address / Control lines? © System-on-Chip Group, CSE-IMM, DTU 21

Overhead Considerations • • • Routing Protocol Congestion control Error-correction Network setup/tear-down Synchronization © System-on-Chip Group, CSE-IMM, DTU 22

Research Opportunities • • • Traffic + Application Topology + Protocol Reconfigurability Area + Power Issues Interfaces (GALS) Sub-micron Technology Exploitation © System-on-Chip Group, CSE-IMM, DTU 23

References • • • BJERREGAARD, T. and MAHADEVAN, S. 2004. “No. C Survey Manuscript”, Submitted. HO, R. , MAI, K. W. , AND HOROWITZ, M. A. 2001. The future of wires. Proceedings of the IEEE. ITRS. 2001. International technology roadmap for semiconductors (ITRS) 2001. Tech. rep. , International Technology Roadmap for Semiconductors. JANTSCH, A. AND TENHUNEN, H. 2003. Networks on Chip. Kluwer Academic Publishers. LEE, K. 1998. On-chip interconnects - gigahertz and beyond. Solid State Technology. OCPIP. The importance of sockets in soc design. White paper downloadable from http: //www. ocpip. org. BENINI, L. AND MICHELI, G. D. 2002. Networks on chips: A new soc paradigm. IEEE Computer. DALLY, W. J. AND TOWLES, B. 2001. Route packets, not wires: On-chip interconnection networks. In Proceedings of the 38 th Design Automation Conference. DIELISSEN, J. , RADULESCU, A. , GOOSSENS, K. , AND RIJPKEMA, E. 2003. Concepts and implementation of the phillips network-on-chip. In Proceedings of the IP based SOC IPSOC’ 03. GOOSSENS, K. , MEERBERGEN, J. V. , PEETERS, A. , AND WIELAGE, P. 2002. Networks on silicon: Combining best-effort and guaranteed services. In Proceedings of the 2002 Design, Automation and Test in Europe Conference (DATE’ 02). IEEE. © System-on-Chip Group, CSE-IMM, DTU 24