Network Processor and Applications Prof Laxmi Bhuyan bhuyancs

Network Processor and Applications Prof. Laxmi Bhuyan bhuyan@cs. ucr. edu 4/22/2003 Network Processor & Its Applications 1

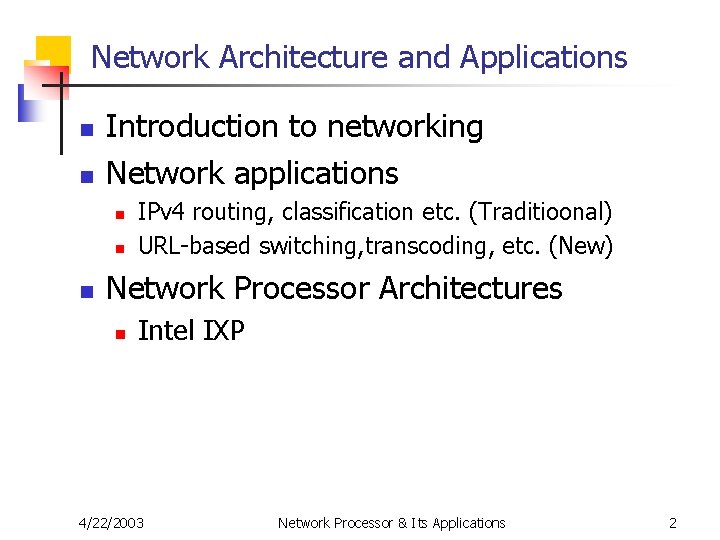

Network Architecture and Applications n n Introduction to networking Network applications n n n IPv 4 routing, classification etc. (Traditioonal) URL-based switching, transcoding, etc. (New) Network Processor Architectures n Intel IXP 4/22/2003 Network Processor & Its Applications 2

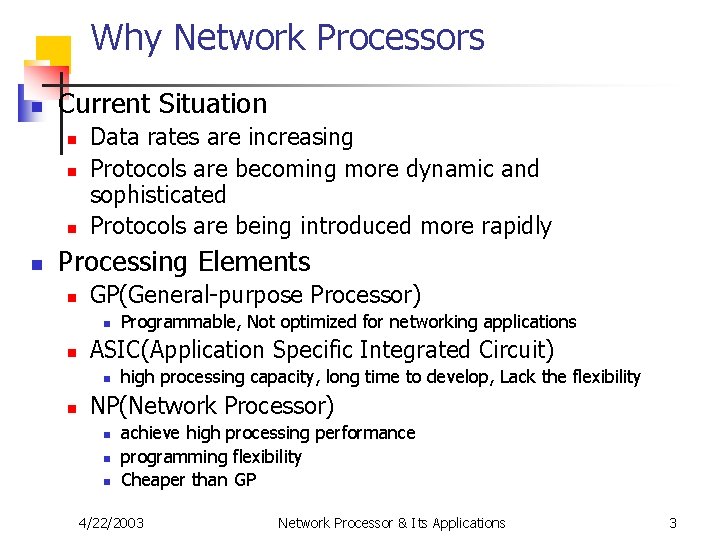

Why Network Processors n Current Situation n n Data rates are increasing Protocols are becoming more dynamic and sophisticated Protocols are being introduced more rapidly Processing Elements n GP(General-purpose Processor) n n ASIC(Application Specific Integrated Circuit) n n Programmable, Not optimized for networking applications high processing capacity, long time to develop, Lack the flexibility NP(Network Processor) n n n achieve high processing performance programming flexibility Cheaper than GP 4/22/2003 Network Processor & Its Applications 3

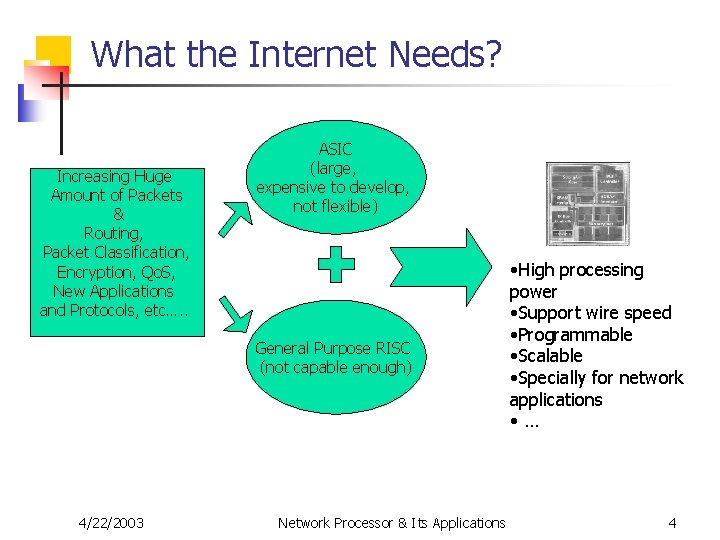

What the Internet Needs? Increasing Huge Amount of Packets & Routing, Packet Classification, Encryption, Qo. S, New Applications and Protocols, etc…. . ASIC (large, expensive to develop, not flexible) General Purpose RISC (not capable enough) 4/22/2003 Network Processor & Its Applications • High processing power • Support wire speed • Programmable • Scalable • Specially for network applications • … 4

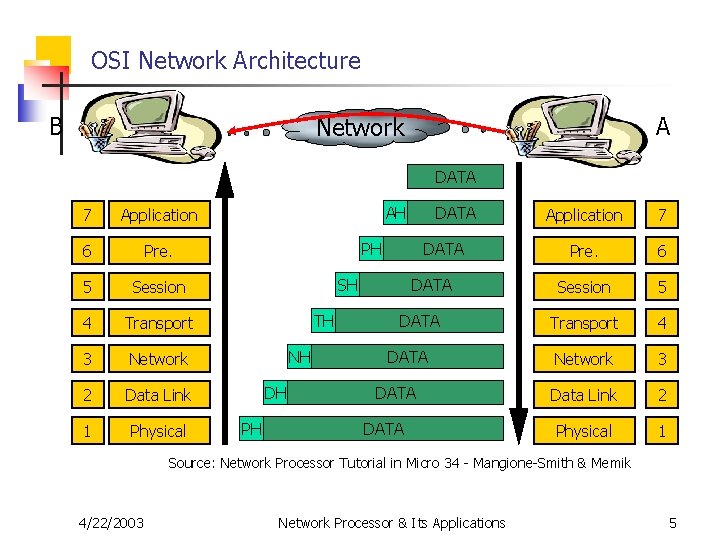

OSI Network Architecture B A Network DATA 7 Application 6 Pre. 5 Session 4 Transport 3 Network 2 Data Link 1 Physical AH DATA PH DATA SH TH NH DH PH DATA DATA Application 7 Pre. 6 Session 5 Transport 4 Network 3 Data Link 2 Physical 1 Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 5

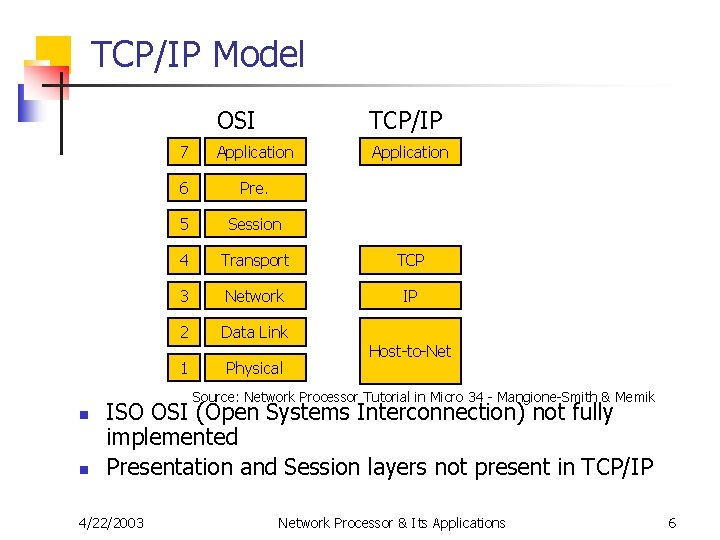

TCP/IP Model OSI TCP/IP 7 Application 6 Pre. 5 Session 4 Transport TCP 3 Network IP 2 Data Link 1 Physical Host-to-Net Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik n n ISO OSI (Open Systems Interconnection) not fully implemented Presentation and Session layers not present in TCP/IP 4/22/2003 Network Processor & Its Applications 6

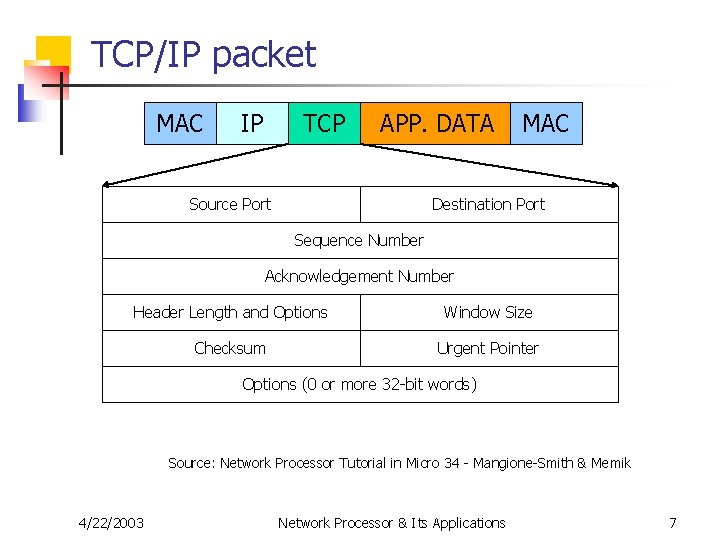

TCP/IP packet MAC IP TCP APP. DATA Source Port MAC Destination Port Sequence Number Acknowledgement Number Header Length and Options Window Size Checksum Urgent Pointer Options (0 or more 32 -bit words) Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 7

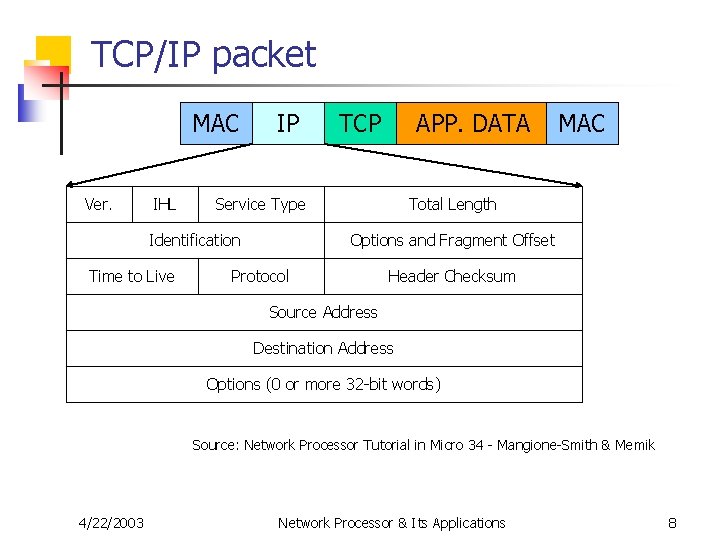

TCP/IP packet MAC Ver. IHL IP APP. DATA Service Type Identification Time to Live TCP MAC Total Length Options and Fragment Offset Protocol Header Checksum Source Address Destination Address Options (0 or more 32 -bit words) Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 8

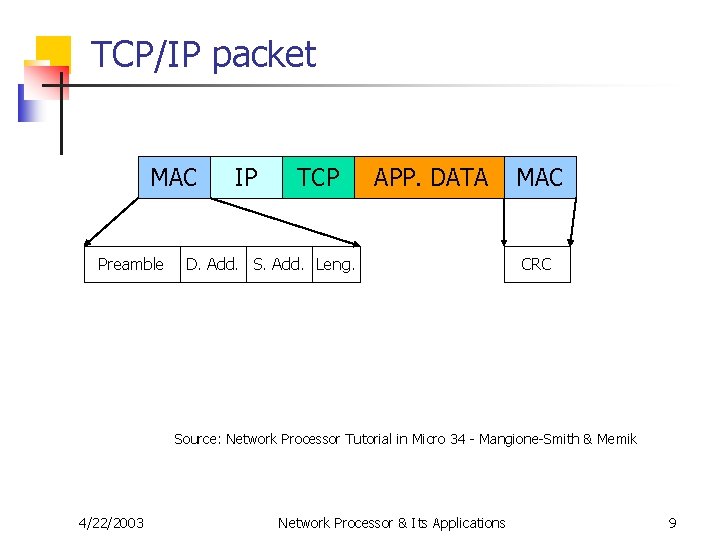

TCP/IP packet MAC Preamble IP TCP APP. DATA D. Add. S. Add. Leng. MAC CRC Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 9

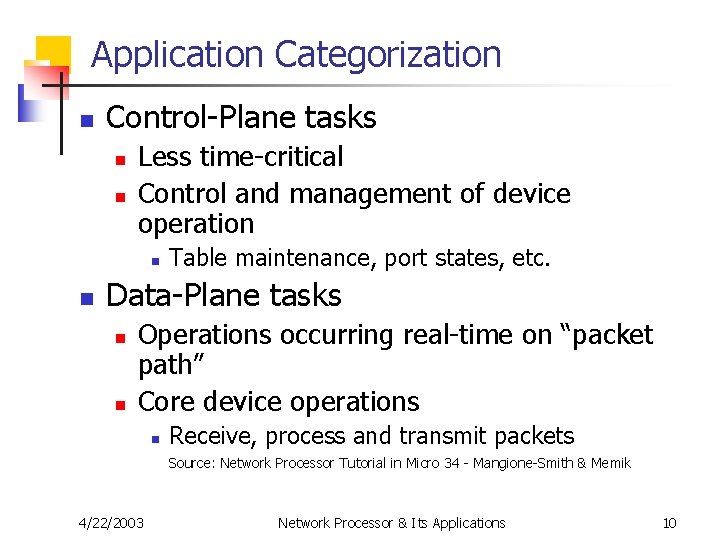

Application Categorization n Control-Plane tasks n n Less time-critical Control and management of device operation n n Table maintenance, port states, etc. Data-Plane tasks n n Operations occurring real-time on “packet path” Core device operations n Receive, process and transmit packets Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 10

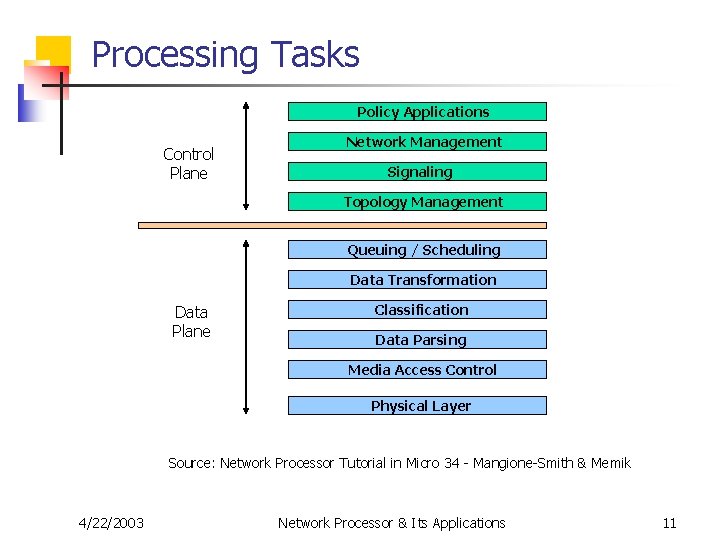

Processing Tasks Policy Applications Control Plane Network Management Signaling Topology Management Queuing / Scheduling Data Transformation Data Plane Classification Data Parsing Media Access Control Physical Layer Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 11

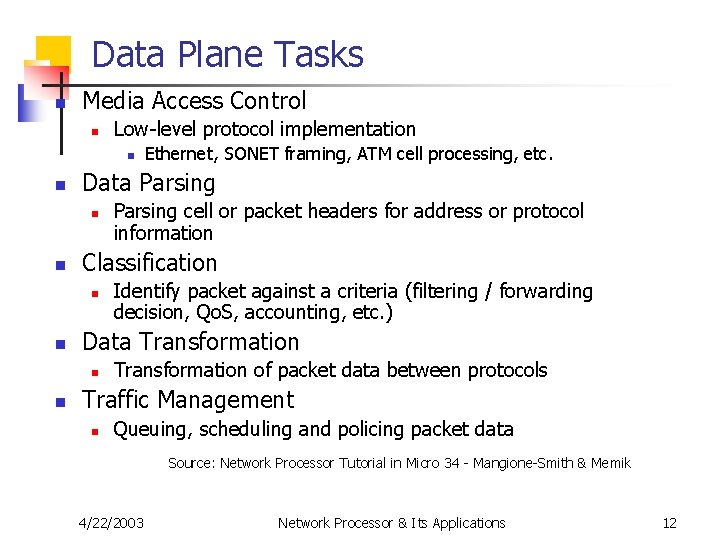

Data Plane Tasks n Media Access Control n Low-level protocol implementation n n Data Parsing n n Identify packet against a criteria (filtering / forwarding decision, Qo. S, accounting, etc. ) Data Transformation n n Parsing cell or packet headers for address or protocol information Classification n n Ethernet, SONET framing, ATM cell processing, etc. Transformation of packet data between protocols Traffic Management n Queuing, scheduling and policing packet data Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 12

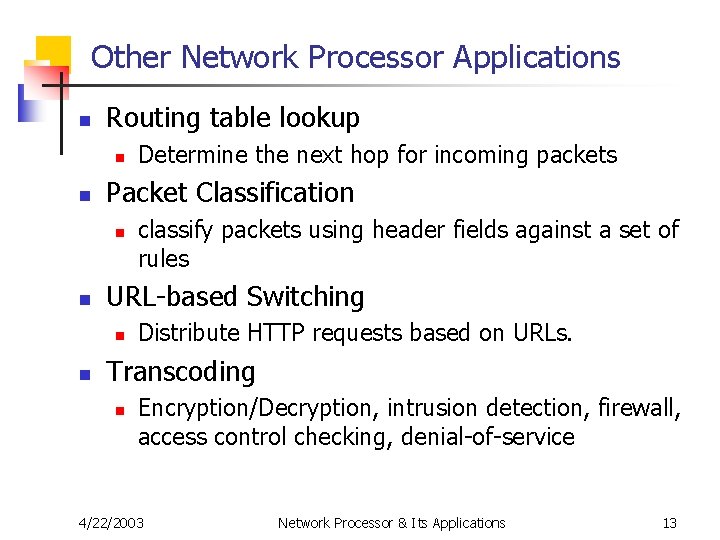

Other Network Processor Applications n Routing table lookup n n Packet Classification n n classify packets using header fields against a set of rules URL-based Switching n n Determine the next hop for incoming packets Distribute HTTP requests based on URLs. Transcoding n Encryption/Decryption, intrusion detection, firewall, access control checking, denial-of-service 4/22/2003 Network Processor & Its Applications 13

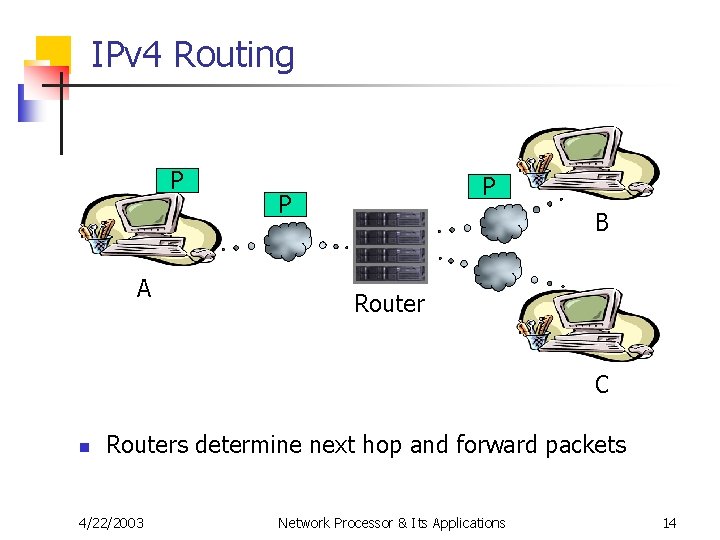

IPv 4 Routing P A P P B Router C n Routers determine next hop and forward packets 4/22/2003 Network Processor & Its Applications 14

Packet Classification n Routers are required to distinguish packets for n n n n Packets are classified by rules n n Flow identification Fair sharing of bandwidth Qo. S Security Accounting, billing etc Src IP, Dest IP, src port #, dest port # etc Classification Algorithm Metrics n n n Search speed Storage cost Scalability Updates Etc. 4/22/2003 Network Processor & Its Applications 15

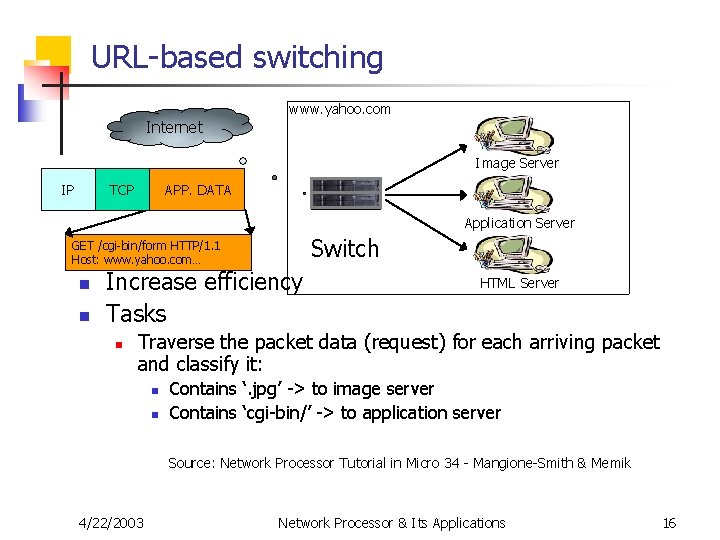

URL-based switching www. yahoo. com Internet Image Server IP TCP APP. DATA Application Server GET /cgi-bin/form HTTP/1. 1 Host: www. yahoo. com… n n Switch Increase efficiency Tasks n HTML Server Traverse the packet data (request) for each arriving packet and classify it: n n Contains ‘. jpg’ -> to image server Contains ‘cgi-bin/’ -> to application server Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 16

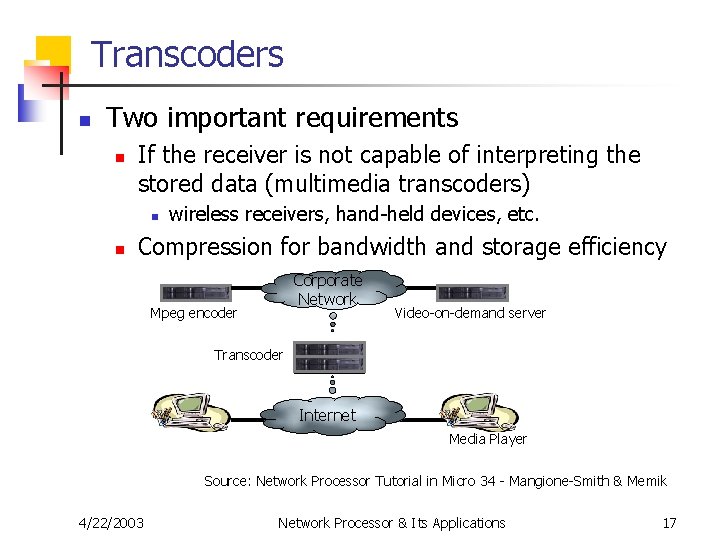

Transcoders n Two important requirements n If the receiver is not capable of interpreting the stored data (multimedia transcoders) n n wireless receivers, hand-held devices, etc. Compression for bandwidth and storage efficiency Corporate Network Mpeg encoder Video-on-demand server Transcoder Internet Media Player Source: Network Processor Tutorial in Micro 34 - Mangione-Smith & Memik 4/22/2003 Network Processor & Its Applications 17

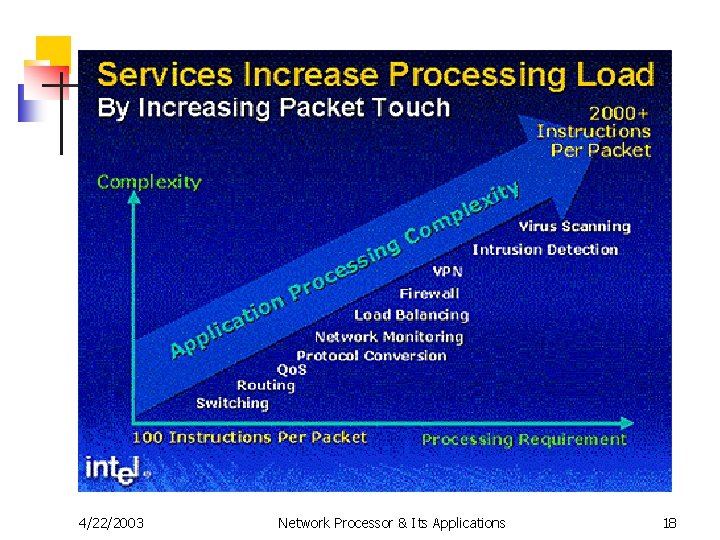

4/22/2003 Network Processor & Its Applications 18

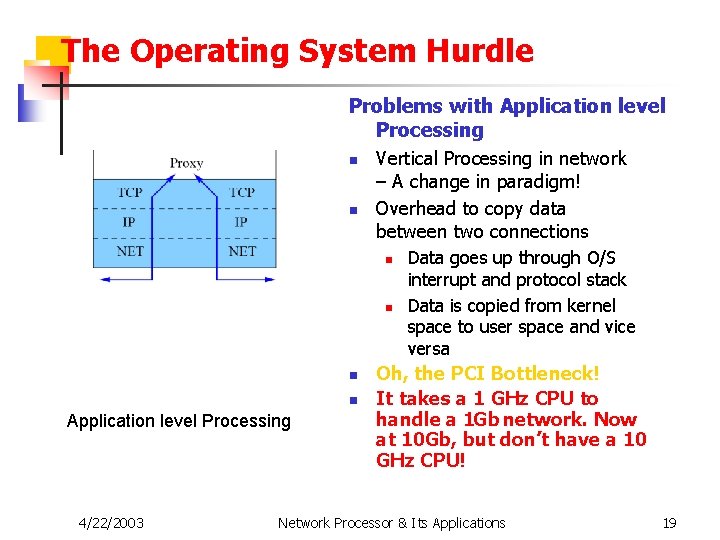

The Operating System Hurdle Problems with Application level Processing n n Vertical Processing in network – A change in paradigm! Overhead to copy data between two connections n n Application level Processing 4/22/2003 Data goes up through O/S interrupt and protocol stack Data is copied from kernel space to user space and vice versa Oh, the PCI Bottleneck! It takes a 1 GHz CPU to handle a 1 Gb network. Now at 10 Gb, but don’t have a 10 GHz CPU! Network Processor & Its Applications 19

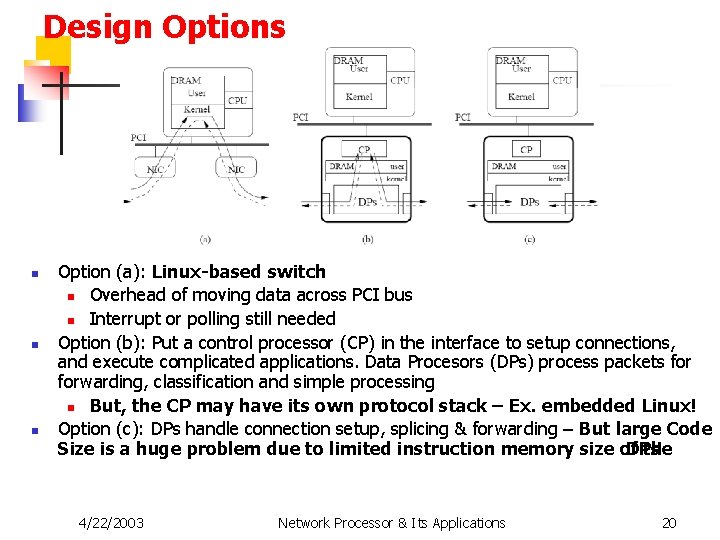

Design Options n n n Option (a): Linux-based switch n Overhead of moving data across PCI bus n Interrupt or polling still needed Option (b): Put a control processor (CP) in the interface to setup connections, and execute complicated applications. Data Procesors (DPs) process packets forwarding, classification and simple processing n But, the CP may have its own protocol stack – Ex. embedded Linux! Option (c): DPs handle connection setup, splicing & forwarding – But large Code Size is a huge problem due to limited instruction memory size of DPs! the 4/22/2003 Network Processor & Its Applications 20

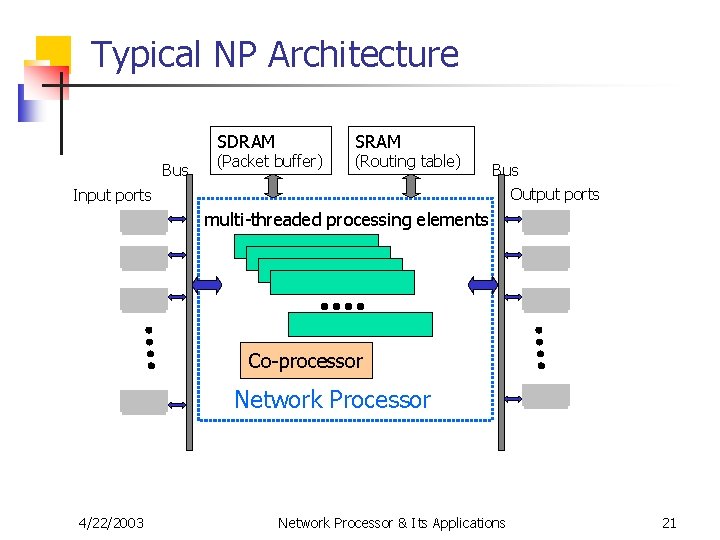

Typical NP Architecture SDRAM Bus (Packet buffer) SRAM (Routing table) Input ports Bus Output ports multi-threaded processing elements Co-processor Network Processor 4/22/2003 Network Processor & Its Applications 21

Organizing Processor Resources n Design decisions: n n High-level organization ISA and micro architecture Memory and I/O integration Today’s commercial NPs: n n n 4/22/2003 Chip multiprocessors Most are multithreaded Exploit little ILP (Cisco does) No cache Micro-programmed Network Processor & Its Applications 22

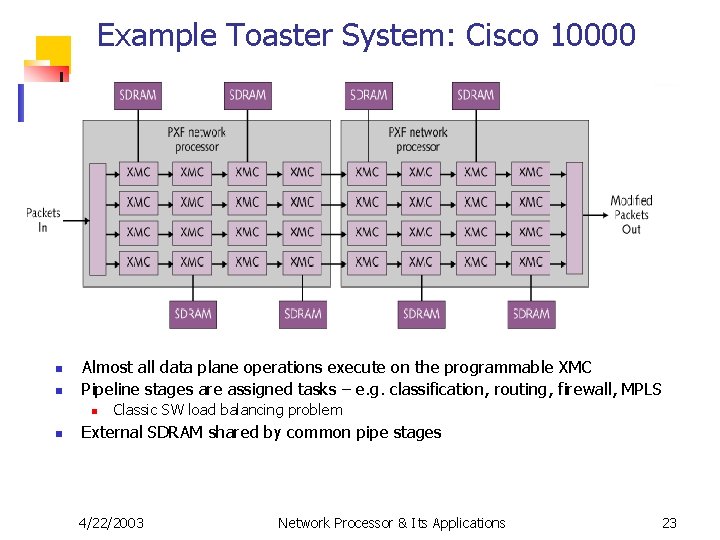

Example Toaster System: Cisco 10000 n n Almost all data plane operations execute on the programmable XMC Pipeline stages are assigned tasks – e. g. classification, routing, firewall, MPLS n n Classic SW load balancing problem External SDRAM shared by common pipe stages 4/22/2003 Network Processor & Its Applications 23

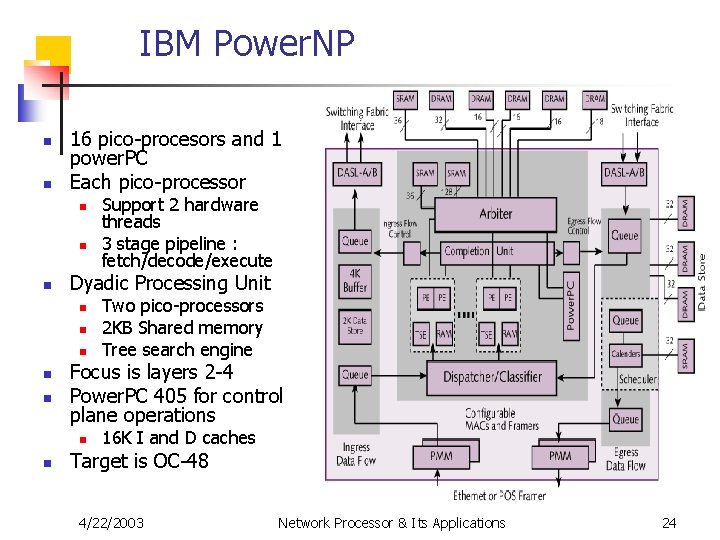

IBM Power. NP n n 16 pico-procesors and 1 power. PC Each pico-processor n n n Dyadic Processing Unit n n n Two pico-processors 2 KB Shared memory Tree search engine Focus is layers 2 -4 Power. PC 405 for control plane operations n n Support 2 hardware threads 3 stage pipeline : fetch/decode/execute 16 K I and D caches Target is OC-48 4/22/2003 Network Processor & Its Applications 24

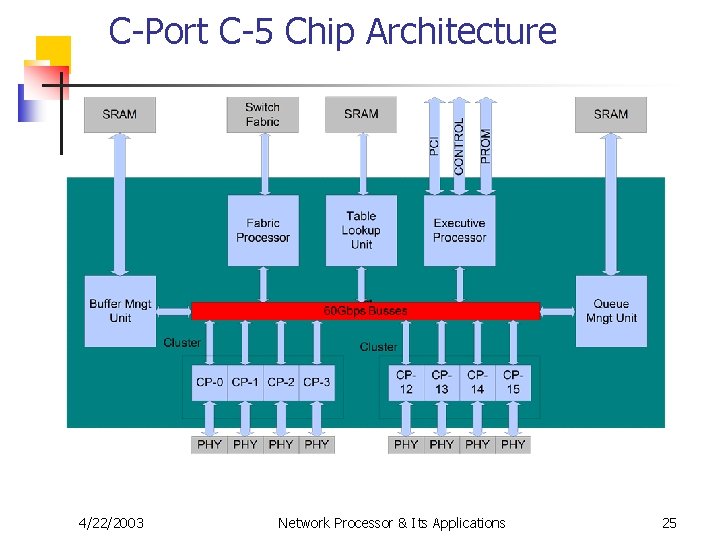

C-Port C-5 Chip Architecture 4/22/2003 Network Processor & Its Applications 25

Some Challenges n Intelligent Design n Given a selection of programs, a target network link speed, the ‘best’ design for the processor n n Least area Least power Most performance Write efficient multithreaded programs n NPs have n Heterogeneous computer resources Non-uniform memory Multiple interacting threads of execution Real-time constraints n How to use special instructions and hardware assists n n Make use of resources n n n Multithreaded programs n n 4/22/2003 Compilers Hand-coded Manage access to shared state Synchronization between threads Network Processor & Its Applications 26

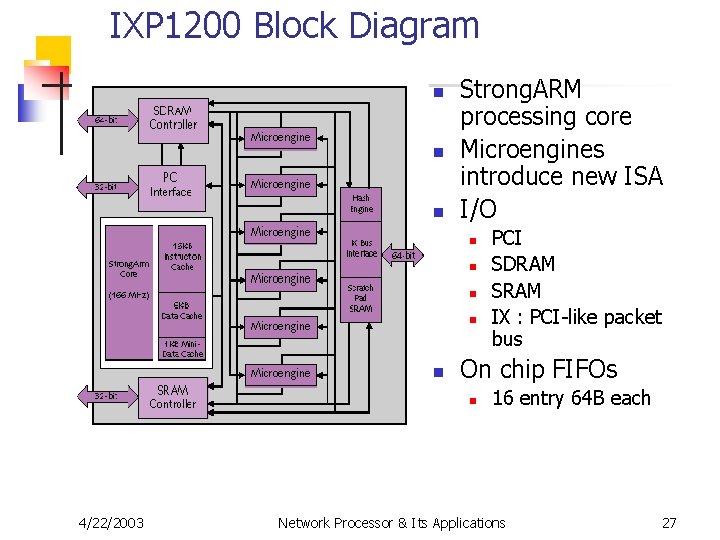

IXP 1200 Block Diagram n n n Strong. ARM processing core Microengines introduce new ISA I/O n n n On chip FIFOs n 4/22/2003 PCI SDRAM SRAM IX : PCI-like packet bus 16 entry 64 B each Network Processor & Its Applications 27

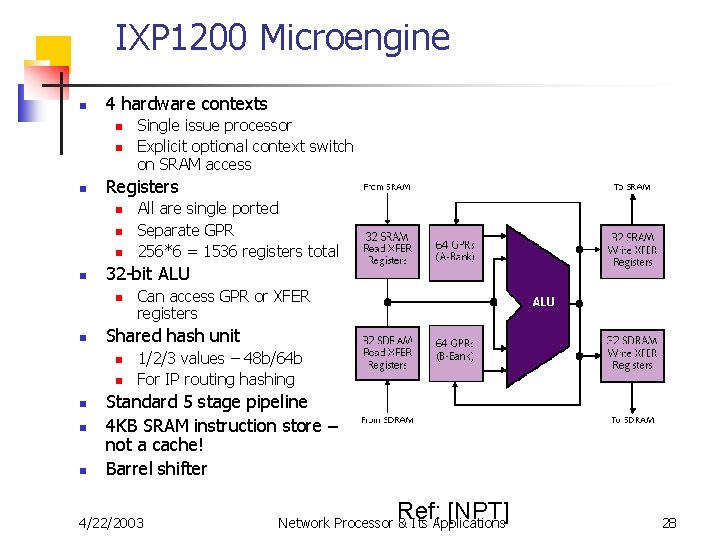

IXP 1200 Microengine n 4 hardware contexts n n n Registers n n n n Can access GPR or XFER registers Shared hash unit n n All are single ported Separate GPR 256*6 = 1536 registers total 32 -bit ALU n n Single issue processor Explicit optional context switch on SRAM access 1/2/3 values – 48 b/64 b For IP routing hashing Standard 5 stage pipeline 4 KB SRAM instruction store – not a cache! Barrel shifter 4/22/2003 Ref: [NPT] Network Processor & Its Applications 28

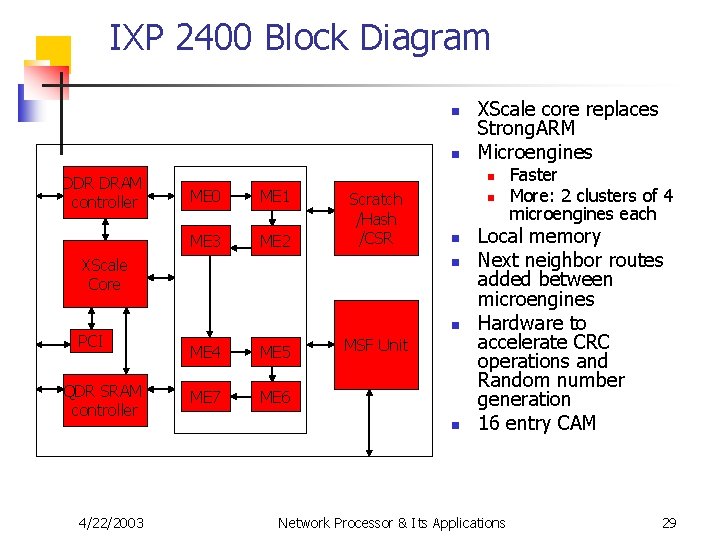

IXP 2400 Block Diagram n n DDR DRAM controller n ME 0 ME 1 ME 3 ME 2 Scratch /Hash /CSR XScale Core PCI QDR SRAM controller 4/22/2003 XScale core replaces Strong. ARM Microengines n n ME 4 ME 5 ME 7 ME 6 MSF Unit n Faster More: 2 clusters of 4 microengines each Local memory Next neighbor routes added between microengines Hardware to accelerate CRC operations and Random number generation 16 entry CAM Network Processor & Its Applications 29

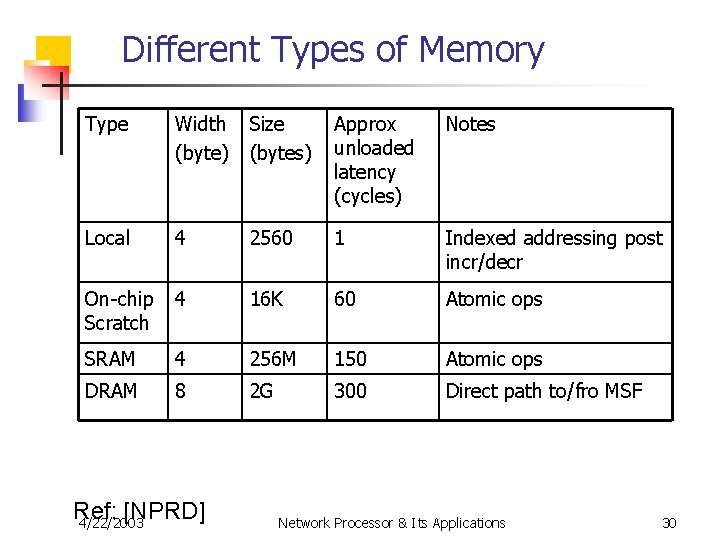

Different Types of Memory Type Width (byte) Size (bytes) Approx unloaded latency (cycles) Notes Local 4 2560 1 Indexed addressing post incr/decr On-chip Scratch 4 16 K 60 Atomic ops SRAM 4 256 M 150 Atomic ops DRAM 8 2 G 300 Direct path to/fro MSF Ref: [NPRD] 4/22/2003 Network Processor & Its Applications 30

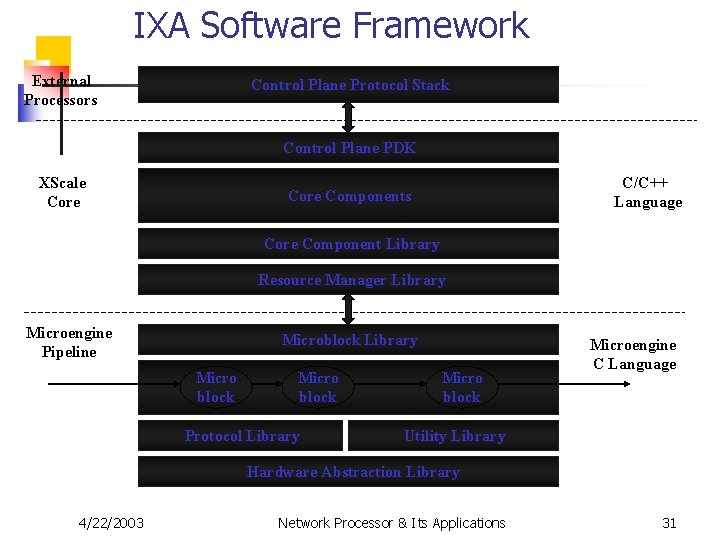

IXA Software Framework External Processors Control Plane Protocol Stack Control Plane PDK XScale Core C/C++ Language Core Components Core Component Library Resource Manager Library Microengine Pipeline Microblock Library Micro block Protocol Library Micro block Microengine C Language Utility Library Hardware Abstraction Library 4/22/2003 Network Processor & Its Applications 31

Summary n n n NP is developing very fast and is a hot research area Multithreaded NP Architectures provide tremendous packet processing capability NP can be applied in various network layers and applications n n n Traditional apps – forwarding, classification Advanced apps – transcoding, URL-based switching, security etc. New apps 4/22/2003 Network Processor & Its Applications 32

- Slides: 32