NETW 1010 IOT Design An Embedded System Overview

NETW 1010 IOT Design: An Embedded System Overview Buses Dr. Eng. Amr T. Abdel-Hamid Fall 2016

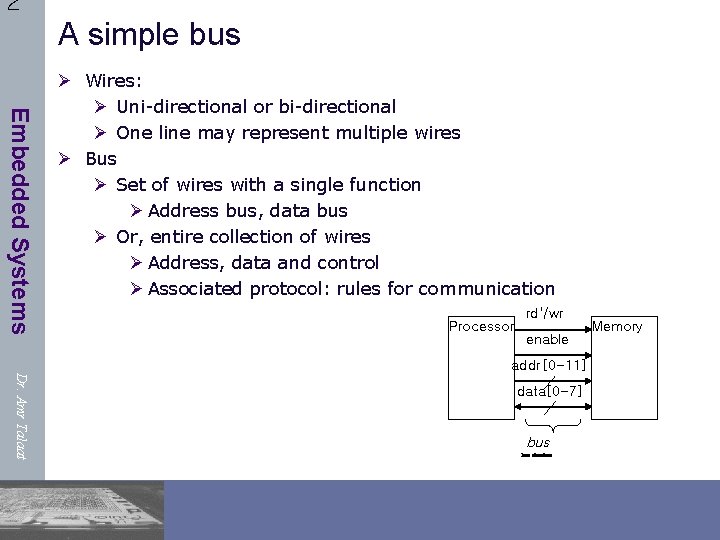

2 A simple bus Embedded Systems Ø Wires: Ø Uni-directional or bi-directional Ø One line may represent multiple wires Ø Bus Ø Set of wires with a single function Ø Address bus, data bus Ø Or, entire collection of wires Ø Address, data and control Ø Associated protocol: rules for communication Processor rd'/wr enable addr[0 -11] Dr. Amr Talaat data[0 -7] bus structure Memory

![3 Ports Embedded Systems port Processor rd'/wr enable Memory addr[0 -11] data[0 -7] Ø 3 Ports Embedded Systems port Processor rd'/wr enable Memory addr[0 -11] data[0 -7] Ø](http://slidetodoc.com/presentation_image_h2/f8aae0a3ae273791f6109681574dd210/image-3.jpg)

3 Ports Embedded Systems port Processor rd'/wr enable Memory addr[0 -11] data[0 -7] Ø Conducting device on periphery bus Ø Connects bus to processor or memory Ø Often referred to as a pin Dr. Amr Talaat Ø Actual pins on periphery of IC package that plug into socket on printedcircuit board Ø Sometimes metallic balls instead of pins Ø Today, metal “pads” connecting processors and memories within single IC Ø Single wire or set of wires with single function Ø E. g. , 12 -wire address port

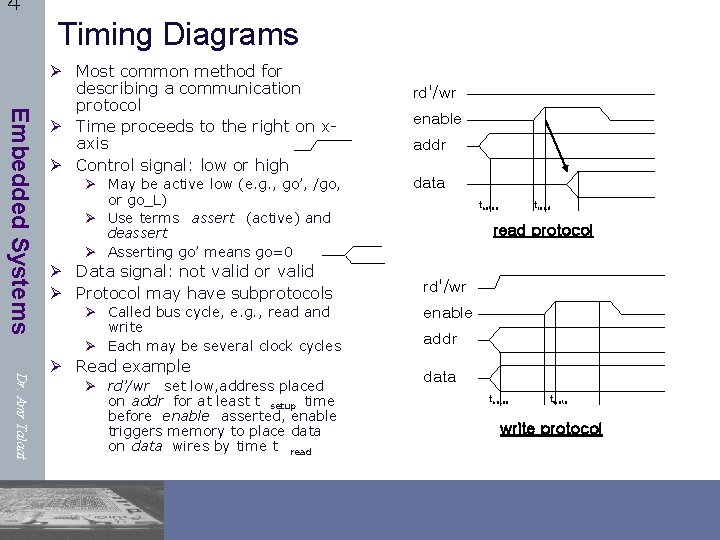

4 Timing Diagrams Embedded Systems Ø Most common method for describing a communication protocol Ø Time proceeds to the right on xaxis Ø Control signal: low or high Ø May be active low (e. g. , go’, /go, or go_L) Ø Use terms assert (active) and deassert Ø Asserting go’ means go=0 Ø Data signal: not valid or valid Ø Protocol may have subprotocols Ø Called bus cycle, e. g. , read and write Ø Each may be several clock cycles Dr. Amr Talaat Ø Read example Ø rd’/wr set low, address placed on addr for at least t setup time before enable asserted, enable triggers memory to place data on data wires by time t read rd'/wr enable addr data tsetup tread protocol rd'/wr enable addr data tsetup twrite protocol

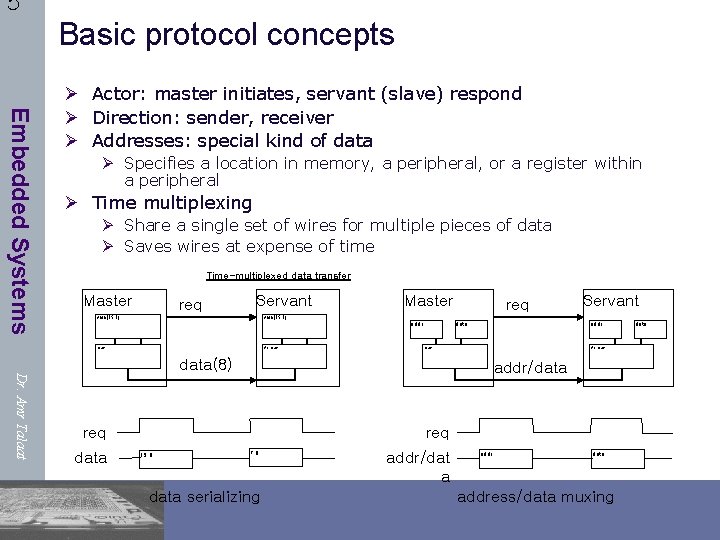

5 Basic protocol concepts Embedded Systems Ø Actor: master initiates, servant (slave) respond Ø Direction: sender, receiver Ø Addresses: special kind of data Ø Specifies a location in memory, a peripheral, or a register within a peripheral Ø Time multiplexing Ø Share a single set of wires for multiple pieces of data Ø Saves wires at expense of time Time-multiplexed data transfer Master req Servant data(15: 0) Master req addr mux demux data(8) Dr. Amr Talaat addr/data req data Servant data(15: 0) req 15: 8 7: 0 data serializing addr/dat a addr data address/data muxing data

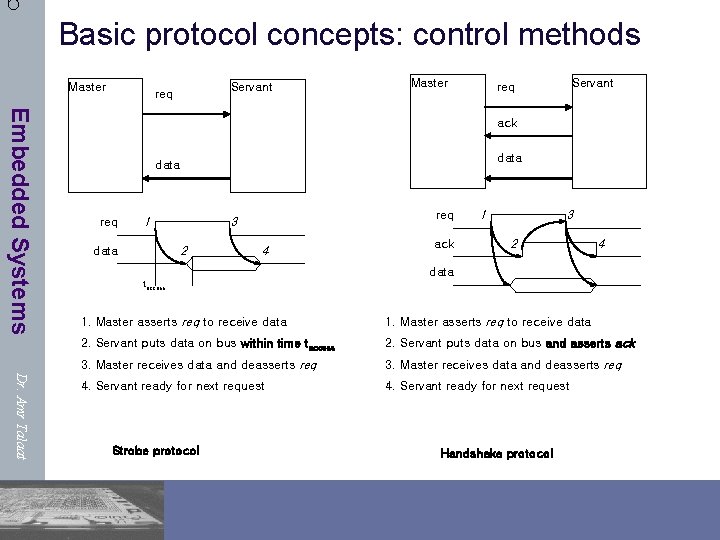

6 Basic protocol concepts: control methods Master Servant req Embedded Systems ack data req 1 2 data req 3 4 ack 1 3 2 4 data taccess Dr. Amr Talaat 1. Master asserts req to receive data 2. Servant puts data on bus within time taccess 2. Servant puts data on bus and asserts ack 3. Master receives data and deasserts req 4. Servant ready for next request Strobe protocol Handshake protocol

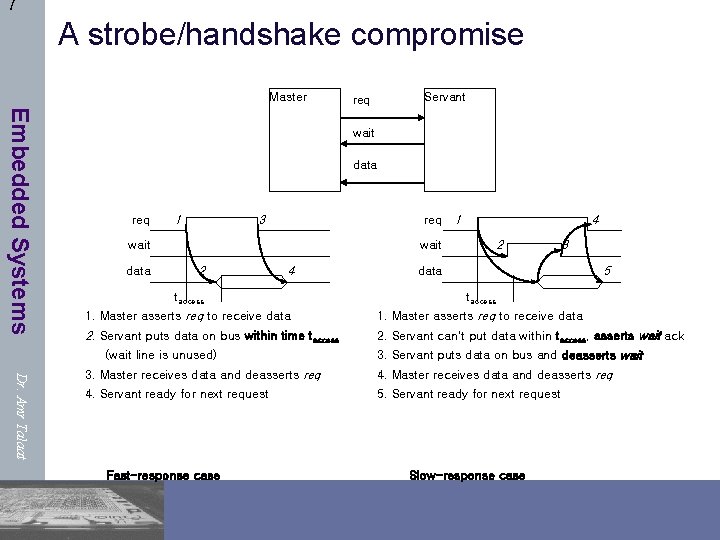

7 A strobe/handshake compromise Master Servant req Embedded Systems wait data req 1 3 req 1 wait data wait 2 4 4 2 3 5 data taccess 1. Master asserts req to receive data 2. Servant puts data on bus within time taccess 2. Servant can't put data within taccess, asserts wait ack (wait line is unused) 3. Servant puts data on bus and deasserts wait Dr. Amr Talaat 3. Master receives data and deasserts req 4. Servant ready for next request 5. Servant ready for next request Fast-response case Slow-response case

8 Parallel communication Embedded Systems Ø Multiple data, control, and possibly power wires Ø One bit per wire Ø High data throughput with short distances Ø Typically used when connecting devices on same IC or same circuit board Ø Bus must be kept short Dr. Amr Talaat Ø long parallel wires result in high capacitance values which requires more time to charge/discharge Ø Data misalignment between wires increases as length increases Ø Higher cost, bulky

9 Serial communication Embedded Systems Ø Single data wire, possibly also control and power wires Ø Words transmitted one bit at a time Ø Higher data throughput with long distances Ø Less average capacitance, so more bits per unit of time Ø Cheaper, less bulky Ø More complex interfacing logic and communication protocol Dr. Amr Talaat Ø Sender needs to decompose word into bits Ø Receiver needs to recompose bits into word Ø Control signals often sent on same wire as data increasing protocol complexity

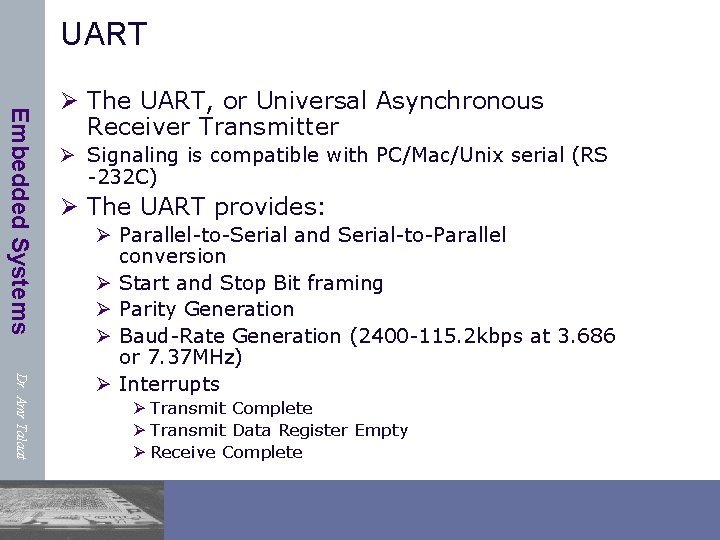

UART Embedded Systems Ø The UART, or Universal Asynchronous Receiver Transmitter Ø Signaling is compatible with PC/Mac/Unix serial (RS -232 C) Ø The UART provides: Dr. Amr Talaat Ø Parallel-to-Serial and Serial-to-Parallel conversion Ø Start and Stop Bit framing Ø Parity Generation Ø Baud-Rate Generation (2400 -115. 2 kbps at 3. 686 or 7. 37 MHz) Ø Interrupts Ø Transmit Complete Ø Transmit Data Register Empty Ø Receive Complete

1 1 BASICS OF SERIAL COMMUNICATION Embedded Systems Bit rate: -Number of bits sent every second (BPS) Baud rate: -Number of symbols sent every second, where every symbol can represent more than one bit. Ex. high-speed modems which use phase shifts to make every data transition period represent more than one bit. Dr. Amr Talaat -So, we can consider bit rate and baud rate the same thing.

1 2 TRANSMISSION REQUIREMENT Embedded Systems Before transmission begins, transmitter and receiver must agree on : - Baud rate (75, 150, 300, 600, etc) - 1, 1. 5 or 2 stop bits - 5, 6, 7 or 8 data bits Dr. Amr Talaat - even, odd or no parity

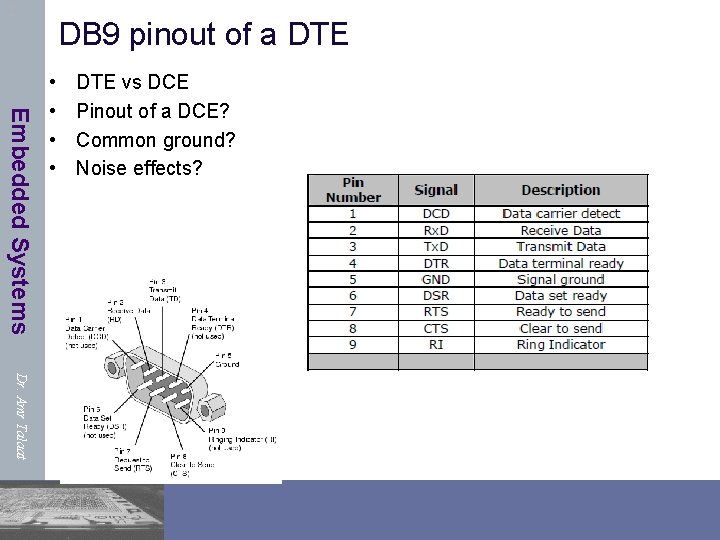

3 DB 9 pinout of a DTE Embedded Systems • • DTE vs DCE Pinout of a DCE? Common ground? Noise effects? Dr. Amr Talaat

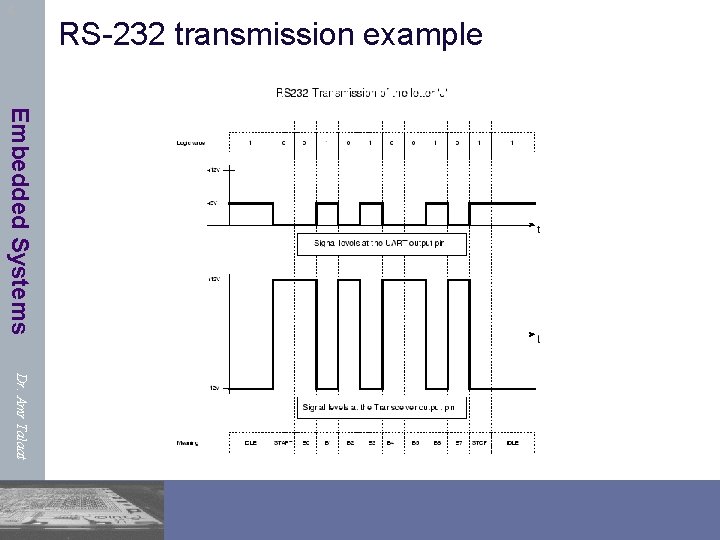

RS-232 transmission example 4 Embedded Systems Dr. Amr Talaat

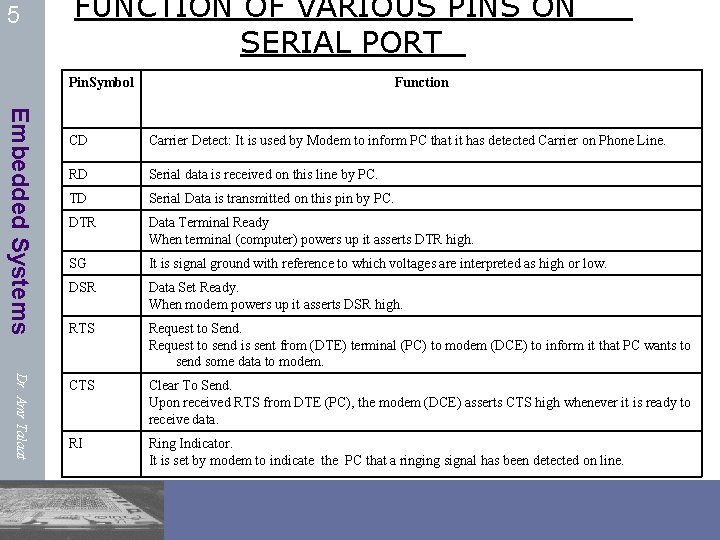

5 FUNCTION OF VARIOUS PINS ON SERIAL PORT Pin. Symbol Function Embedded Systems Dr. Amr Talaat CD Carrier Detect: It is used by Modem to inform PC that it has detected Carrier on Phone Line. RD Serial data is received on this line by PC. TD Serial Data is transmitted on this pin by PC. DTR Data Terminal Ready When terminal (computer) powers up it asserts DTR high. SG It is signal ground with reference to which voltages are interpreted as high or low. DSR Data Set Ready. When modem powers up it asserts DSR high. RTS Request to Send. Request to send is sent from (DTE) terminal (PC) to modem (DCE) to inform it that PC wants to send some data to modem. CTS Clear To Send. Upon received RTS from DTE (PC), the modem (DCE) asserts CTS high whenever it is ready to receive data. RI Ring Indicator. It is set by modem to indicate the PC that a ringing signal has been detected on line.

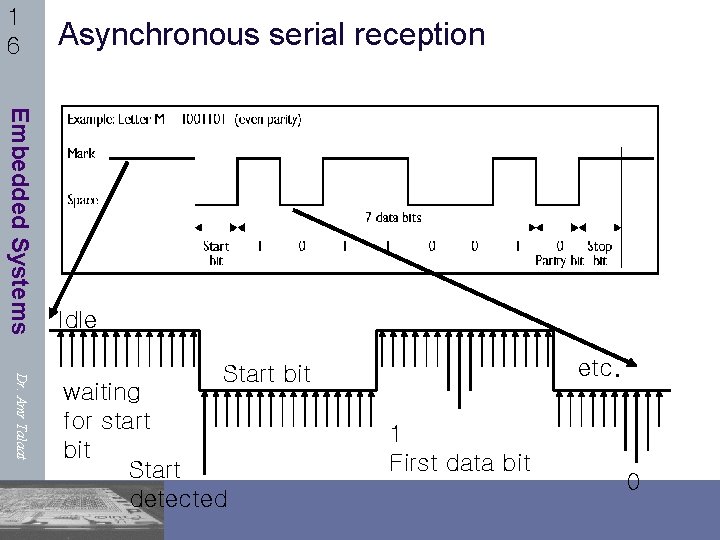

1 6 Asynchronous serial reception Embedded Systems Idle Dr. Amr Talaat etc. Start bit waiting for start bit Start detected 1 First data bit 0

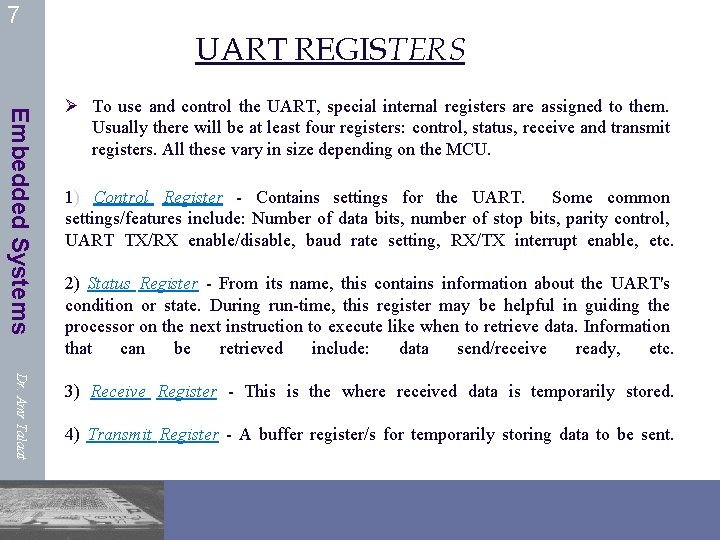

7 UART REGISTERS Embedded Systems Ø To use and control the UART, special internal registers are assigned to them. Usually there will be at least four registers: control, status, receive and transmit registers. All these vary in size depending on the MCU. 1) Control Register - Contains settings for the UART. Some common settings/features include: Number of data bits, number of stop bits, parity control, UART TX/RX enable/disable, baud rate setting, RX/TX interrupt enable, etc. 2) Status Register - From its name, this contains information about the UART's condition or state. During run-time, this register may be helpful in guiding the processor on the next instruction to execute like when to retrieve data. Information that can be retrieved include: data send/receive ready, etc. Dr. Amr Talaat 3) Receive Register - This is the where received data is temporarily stored. 4) Transmit Register - A buffer register/s for temporarily storing data to be sent.

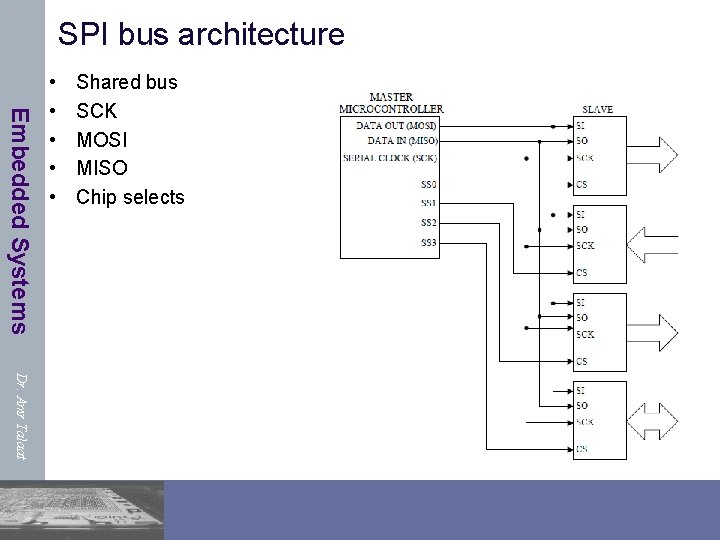

8 SPI bus architecture Embedded Systems • • • Shared bus SCK MOSI MISO Chip selects Dr. Amr Talaat

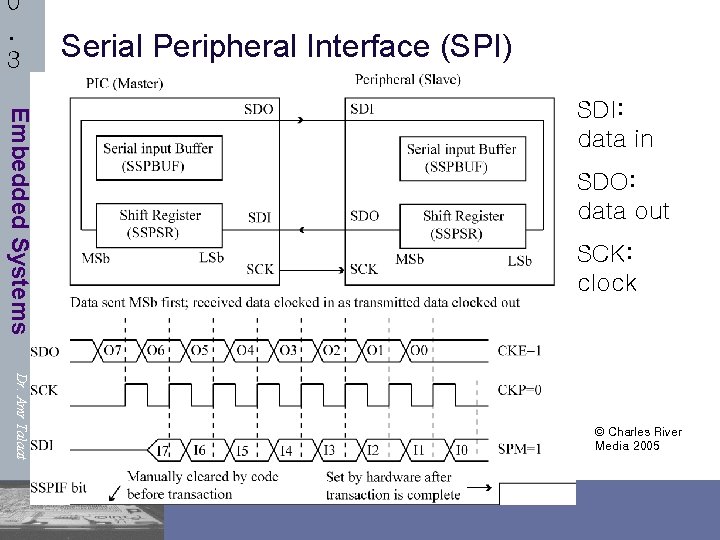

0. 3 Serial Peripheral Interface (SPI) Embedded Systems SDI: data in SDO: data out SCK: clock Dr. Amr Talaat © Charles River Media 2005

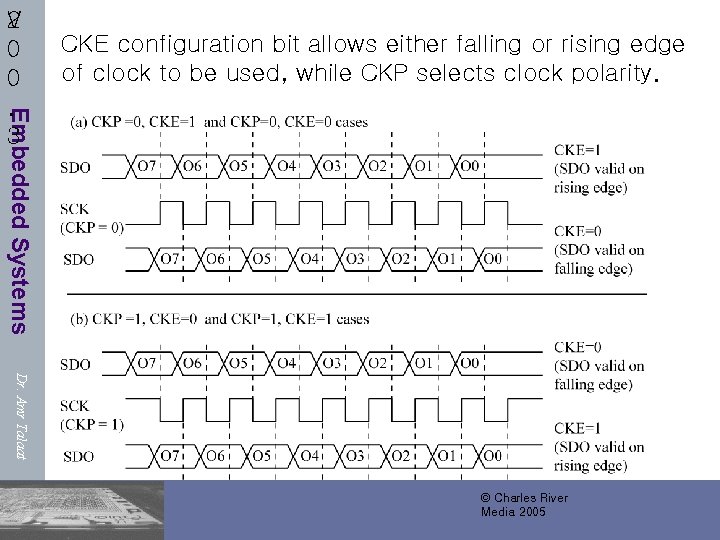

CKE configuration bit allows either falling or rising edge of clock to be used, while CKP selects clock polarity. Embedded Systems 2 V 0 0. 3 Dr. Amr Talaat © Charles River Media 2005

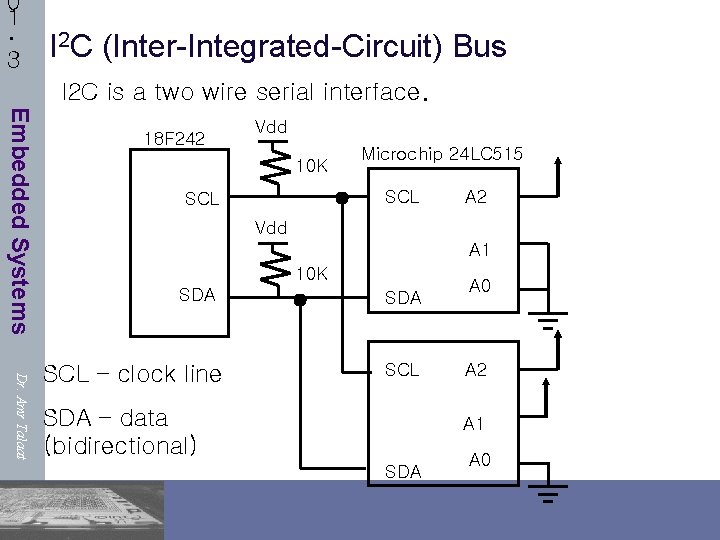

0 1. 3 I 2 C (Inter-Integrated-Circuit) Bus I 2 C is a two wire serial interface. Embedded Systems 18 F 242 Vdd 10 K Microchip 24 LC 515 SCL A 2 Vdd A 1 10 K SDA Dr. Amr Talaat SCL – clock line SDA SCL SDA – data (bidirectional) A 0 A 2 A 1 SDA A 0

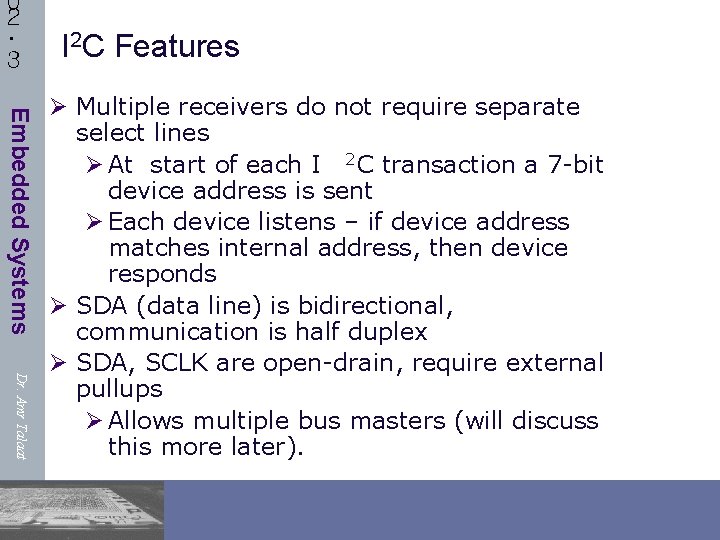

0 2. 3 I 2 C Features Embedded Systems Dr. Amr Talaat Ø Multiple receivers do not require separate select lines Ø At start of each I 2 C transaction a 7 -bit device address is sent Ø Each device listens – if device address matches internal address, then device responds Ø SDA (data line) is bidirectional, communication is half duplex Ø SDA, SCLK are open-drain, require external pullups Ø Allows multiple bus masters (will discuss this more later).

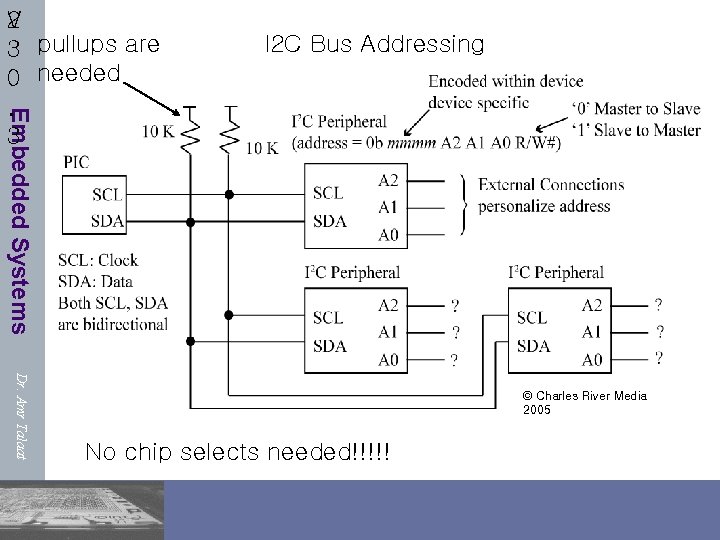

I 2 C Bus Addressing Embedded Systems 2 V 3 pullups are 0 needed. 3 Dr. Amr Talaat © Charles River Media 2005 No chip selects needed!!!!!

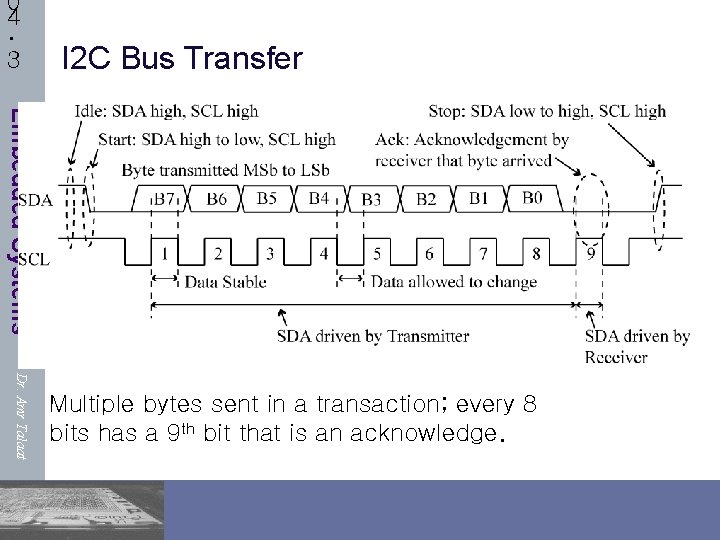

0 4. 3 I 2 C Bus Transfer Embedded Systems Dr. Amr Talaat Multiple bytes sent in a transaction; every 8 bits has a 9 th bit that is an acknowledge.

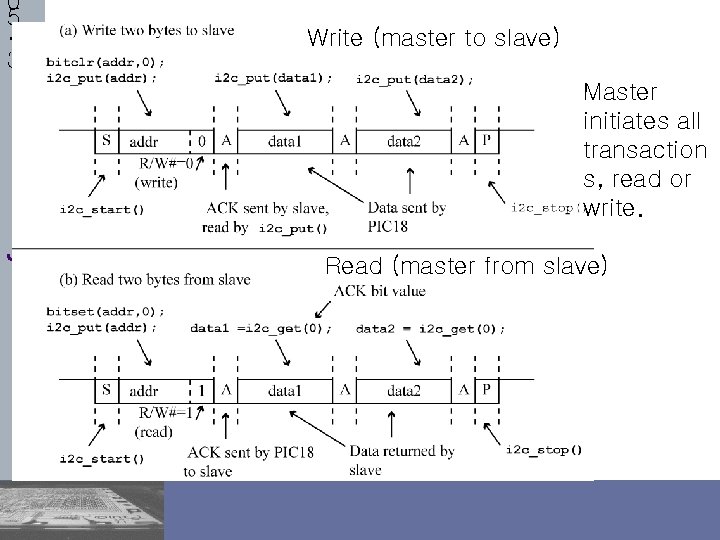

0 5. 3 Write (master to slave) Embedded Systems Master initiates all transaction s, read or write. Read (master from slave) Dr. Amr Talaat

- Slides: 25