NetOS Initialization Sequence Initialization Routine Roles ROM Image

- Slides: 20

Net+OS Initialization Sequence Initialization Routine Roles ROM Image Compression/Decompression

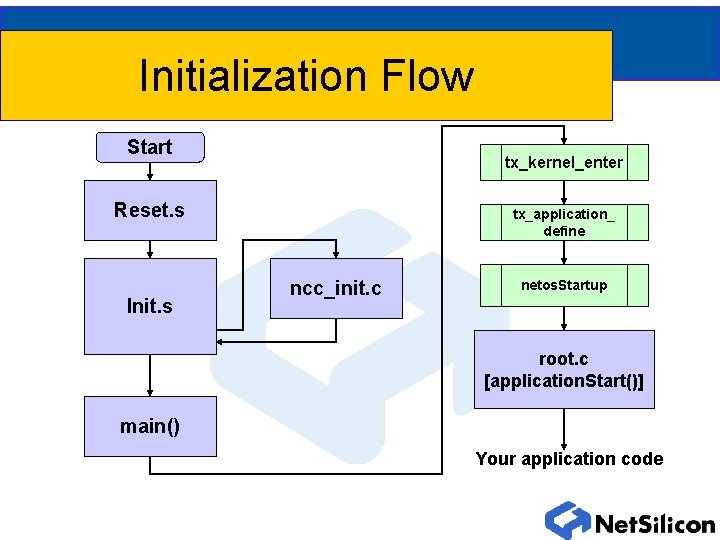

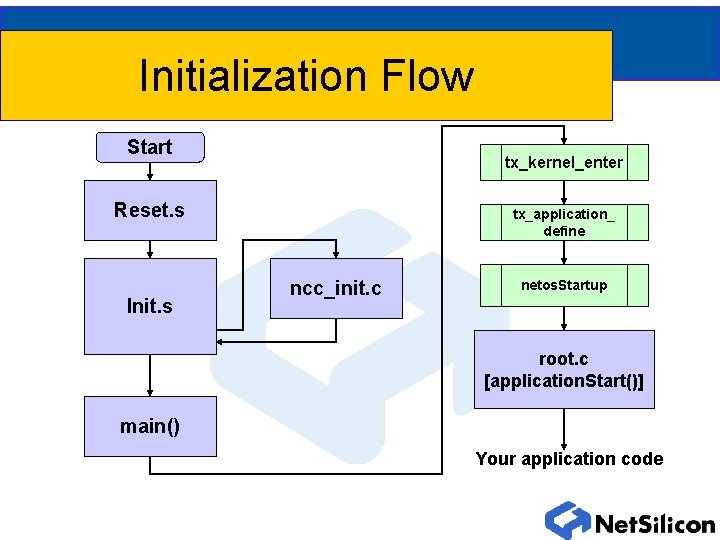

Initialization Flow Start tx_kernel_enter Reset. s Init. s tx_application_ define ncc_init. c netos. Startup root. c [application. Start()] main() Your application code

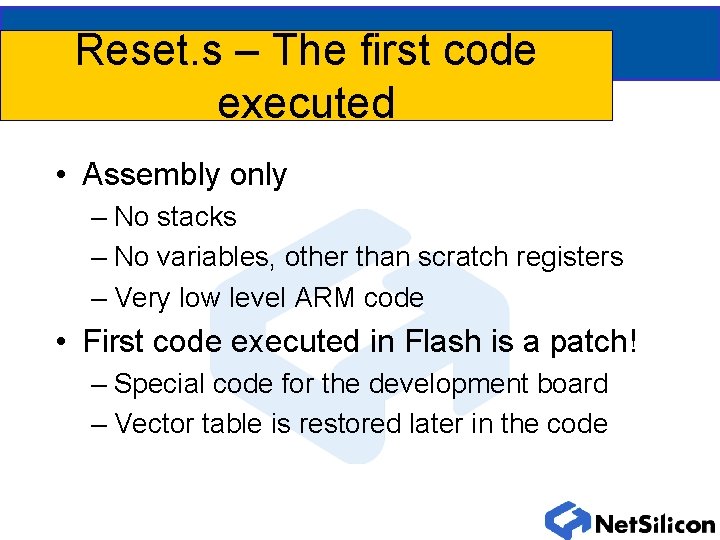

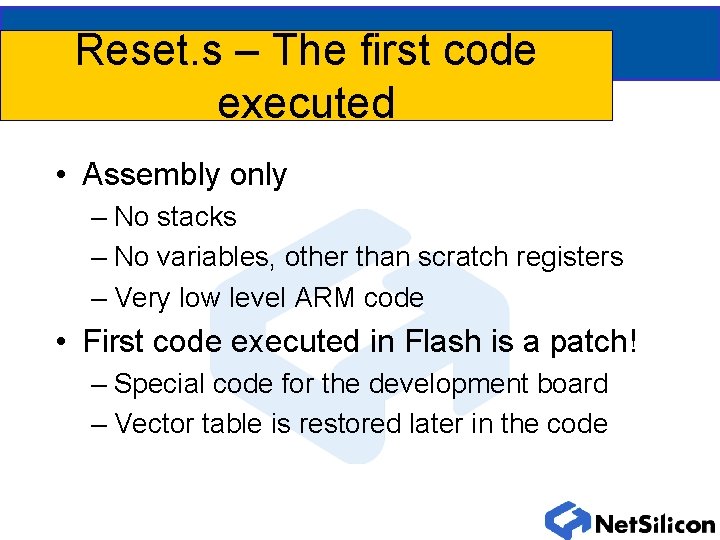

Reset. s – The first code executed • Assembly only – No stacks – No variables, other than scratch registers – Very low level ARM code • First code executed in Flash is a patch! – Special code for the development board – Vector table is restored later in the code

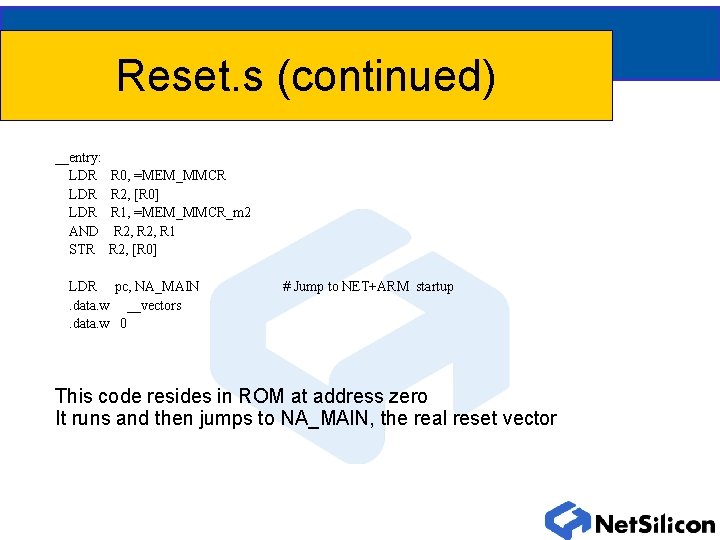

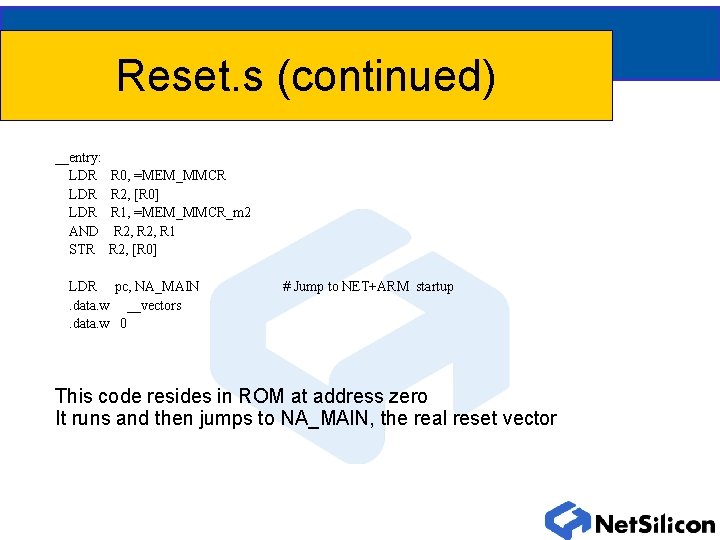

Reset. s (continued) __entry: LDR LDR AND STR R 0, =MEM_MMCR R 2, [R 0] R 1, =MEM_MMCR_m 2 R 2, R 1 R 2, [R 0] LDR pc, NA_MAIN. data. w __vectors. data. w 0 # Jump to NET+ARM startup This code resides in ROM at address zero It runs and then jumps to NA_MAIN, the real reset vector

Init. s The real initialization code • Start at Reset_Handler_Rom – Jump to Reset_Handler if debugger is detected • CS 0 valid bit is ‘off’ (set to zero) • REFCNT has been set in MMCR (for DRAM) • ROM already mapped to higher address – If no debugger, then remap ROM & RAM • ROM mapped to 0 x 0200 0000 • RAM mapped to 0 x 0

Init. s (continued) • A Software reset is performed – Only resets EFE, DMA, GEN, SER modules • Except BSPEED, BCLKD, & PORT A, B, C • Then configure Chip Select Zero – Set base address register – Set option register – Values are OR-ed in to preserve bits already set

Init. s (continued) • Then auto-configure CS 1 for RAM – Same debugger check is made (again) – SDRAM is assumed and checked – Eventually get to cs 1_configured • Much of this auto-detect logic can be removed • Set up an 8 K temporary stack at location 8 K – Now we can call our first C routine – Branch with Link so we can return

Ncc_init. c • First C routine – Still linear main() style C (pre Thread. X) • One line at a time, no multi-tasking • First Step, Configure the GEN module – Set System Configuration Register (SCR) • Set BSPEED to full speed • Turn on Bus Monitor Timer • Enable access to NET+ARM internal registers when in USER mode – OR in these settings to preserve earlier settings

Ncc_init. c (continued) • Disable Interrupts – (*NCC_GEN). i_er. reg = 0; • Use the Interrupt Enable Register Mask • Set PLLCNT in PLL Config Register – (*NCC_GEN). pllcr. bits. pllcnt = 6; • This value is critical to generate Fsysclk & Fxtal regardless of crystal or oscillator clock input • Note that SW does not care about PLL, only about Fsysclk and Fxtal

Ncc_init. c (continued) • Initialize the PORT A, B, and C registers – Sets up Serial ports, DMA handshake special signals, and GPIO pins for LEDs on dev board – Port C config leaves the Green LED ‘on’ • LED assertions are negative ( 0 == ‘on’) • Configure Chip Select 1 for RAM – Being careful to check for a debugger before overwriting settings

Ncc_init. c (continued) • Configure Chip Select 3 for NVRAM – Dev Board has 8 K parallel EE on CS 3 • *Very* useful for configuration parameters et. al. • Warning, if APP_USE_NVRAM is not set in appconf. h, then CS 3 is shut off! – This may cause trouble when integrating new prototype hardware

Ncc_init. c (continued) • CS 4 is disabled (unused on dev board) – This may cause trouble when integrating new prototype hardware • Any memory registers are volatile as long as the USER bit is set in the SCR – You can reconfigure CS 4 later in the code! • Final Step – a complete RAM test is done – This is what takes 40 seconds to finish bootup • Then return right where we left off in init. s

Back to init. s • RAM (and other chip selects) are done • Setup real running stacks for each operating mode of the ARM 7 – ABT, IRQ, FIQ, UND, SVC, USER – Continue running in SYS mode • Now use real stacks and jump to romstart

Romstart. c • Step one – copy the vector table from ROM to RAM • Step Two – copy initialized data from ROM to RAM (. data segment) • Step Three – copy uninitialized data from ROM to RAM and set it to zero (. BSS segment)

Romstart. c (cont. ) • Initialize IRQ tables • Reset MII (if used) • Perform POST tests (if called out in appconf. h) • Re-initialize the IRQ tables – Primarily to restore any changes made during POST tests • Return to init. s

Back to init. s (again) • Load Stack pointer and PC for Thread. X launch and GO LDR sp, STACK LDR pc, START • START is beginning of GHS initialization • GHS routine returns after it initializes and calls main() from bsproot. c

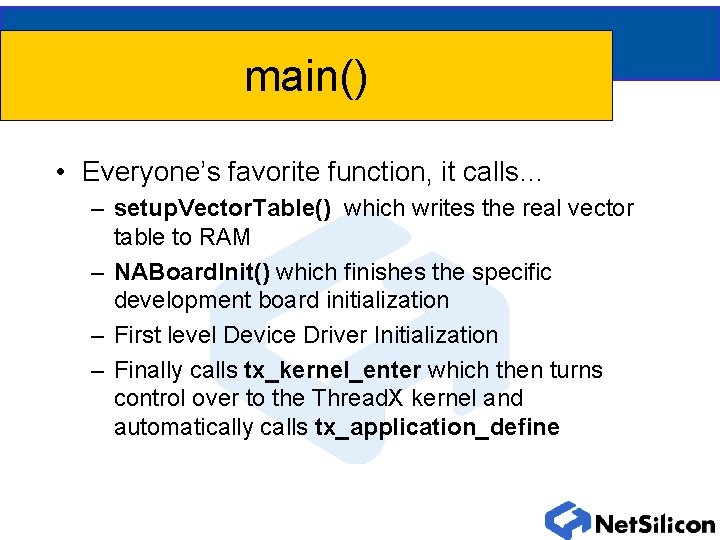

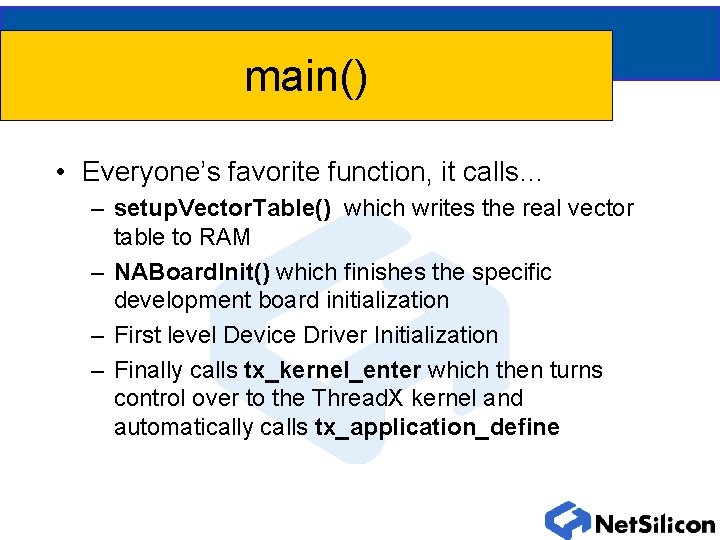

main() • Everyone’s favorite function, it calls… – setup. Vector. Table() which writes the real vector table to RAM – NABoard. Init() which finishes the specific development board initialization – First level Device Driver Initialization – Finally calls tx_kernel_enter which then turns control over to the Thread. X kernel and automatically calls tx_application_define

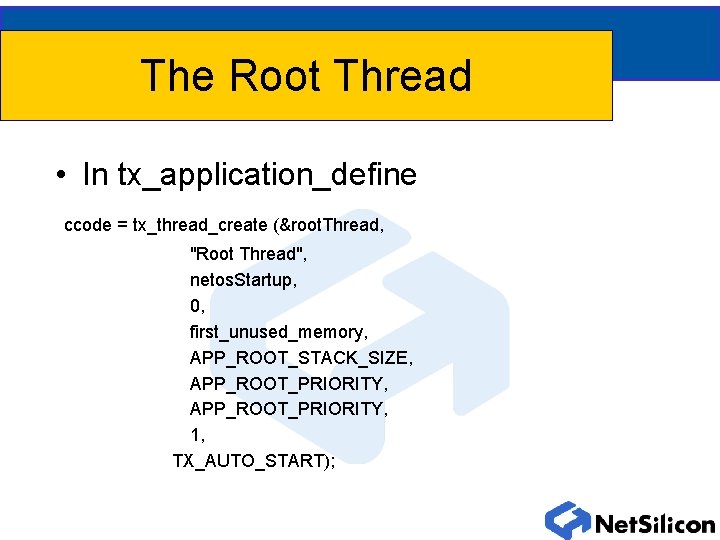

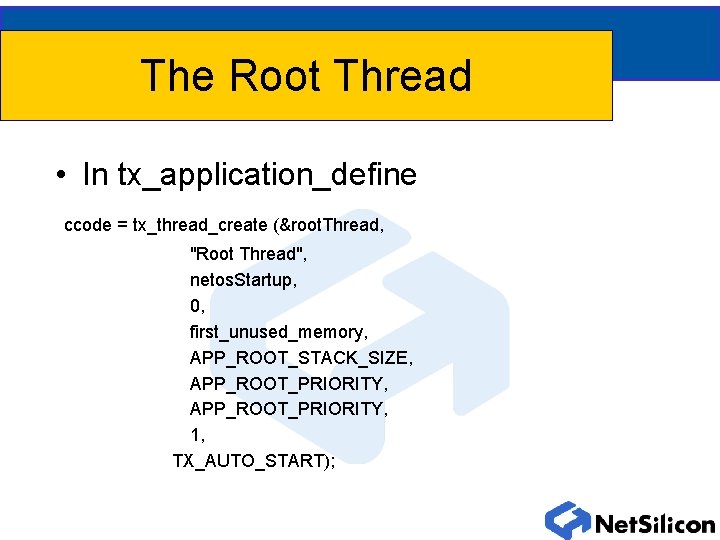

The Root Thread • In tx_application_define ccode = tx_thread_create (&root. Thread, "Root Thread", netos. Startup, 0, first_unused_memory, APP_ROOT_STACK_SIZE, APP_ROOT_PRIORITY, 1, TX_AUTO_START);

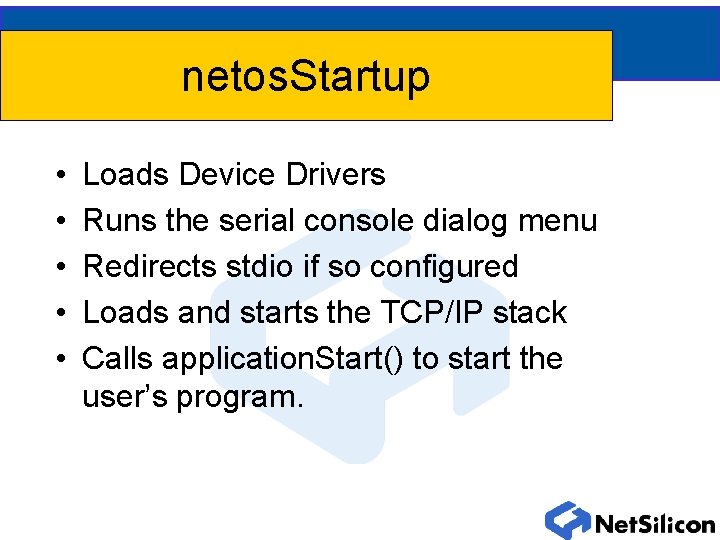

netos. Startup • • • Loads Device Drivers Runs the serial console dialog menu Redirects stdio if so configured Loads and starts the TCP/IP stack Calls application. Start() to start the user’s program.

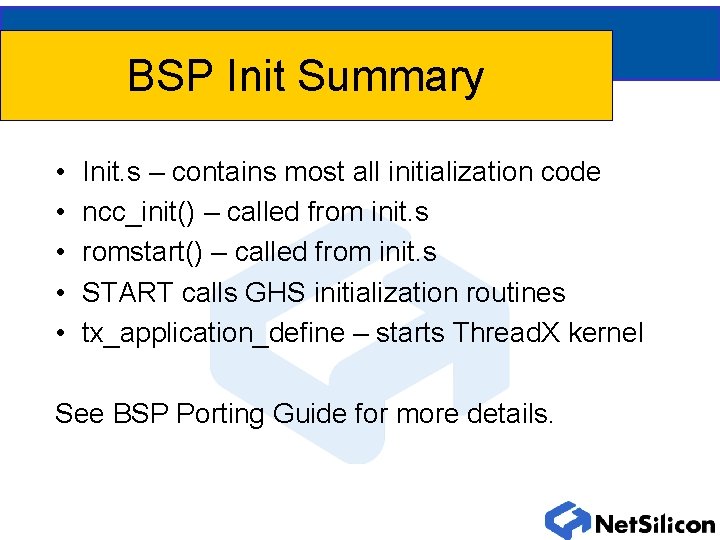

BSP Init Summary • • • Init. s – contains most all initialization code ncc_init() – called from init. s romstart() – called from init. s START calls GHS initialization routines tx_application_define – starts Thread. X kernel See BSP Porting Guide for more details.