NETOS 6 1 Training BSP NETOS 6 1

NET+OS 6. 1 Training

BSP

NET+OS 6. 1 BSP • • • Initialization Memory map New features Debugging Porting Issues

Overall view of the BSP • Identify and process Reset types: – – – hardware reset, power-up reset, software restart, wakeup reset from sleep mode • Perform Memory test. • Load LED and Simple Serial driver for debugging before the kernel and other device drivers are loaded. • Set C library startup from Green. Hills and GNU. • Load the device drivers; Ethernet, DMA, PCI, I 2 C, USB, LCD).

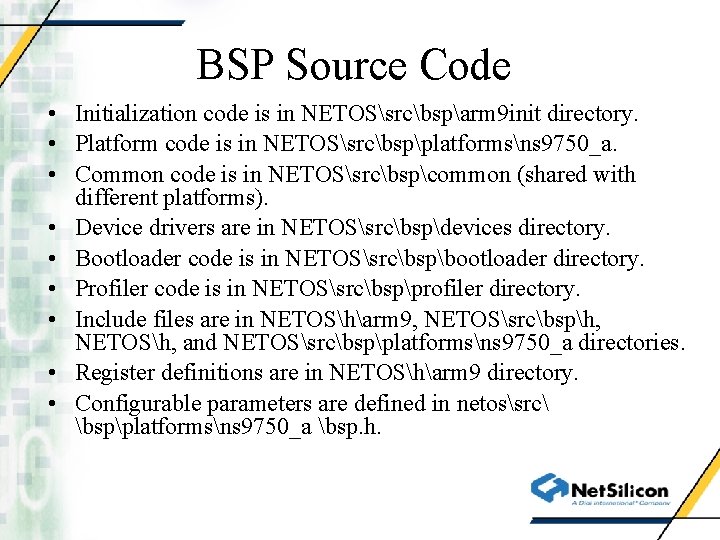

BSP Source Code • Initialization code is in NETOSsrcbsparm 9 init directory. • Platform code is in NETOSsrcbspplatformsns 9750_a. • Common code is in NETOSsrcbspcommon (shared with different platforms). • Device drivers are in NETOSsrcbspdevices directory. • Bootloader code is in NETOSsrcbspbootloader directory. • Profiler code is in NETOSsrcbspprofiler directory. • Include files are in NETOSharm 9, NETOSsrcbsph, NETOSh, and NETOSsrcbspplatformsns 9750_a directories. • Register definitions are in NETOSharm 9 directory. • Configurable parameters are defined in netossrc bspplatformsns 9750_a bsp. h.

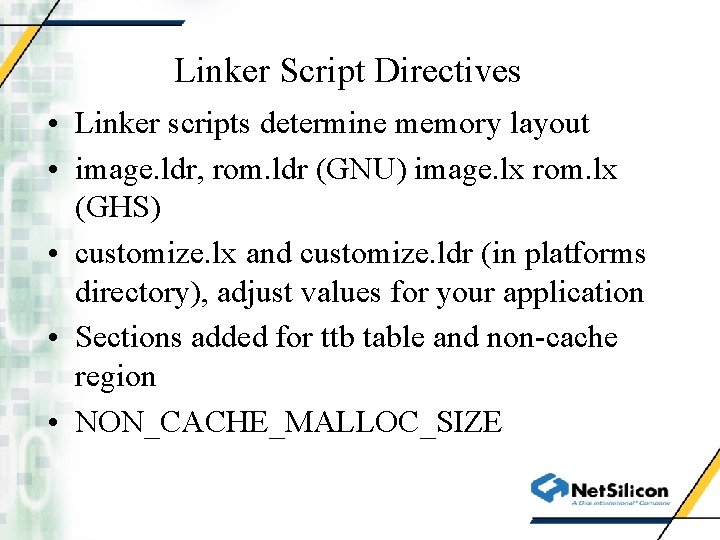

Linker Script Directives • Linker scripts determine memory layout • image. ldr, rom. ldr (GNU) image. lx rom. lx (GHS) • customize. lx and customize. ldr (in platforms directory), adjust values for your application • Sections added for ttb table and non-cache region • NON_CACHE_MALLOC_SIZE

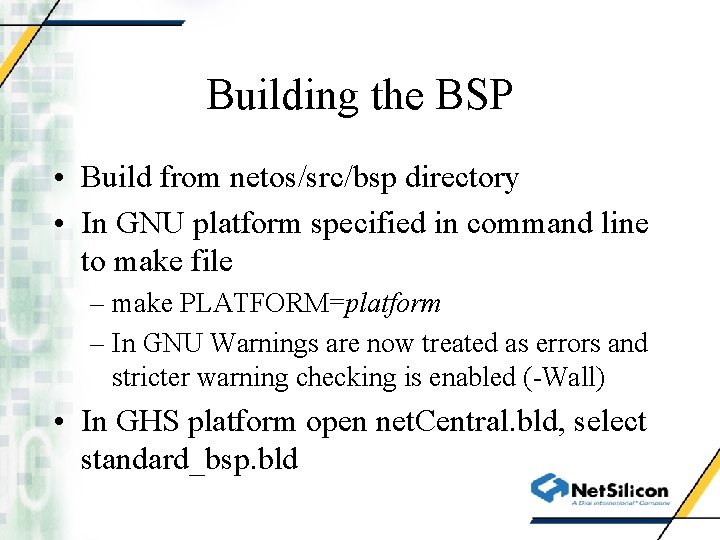

Building the BSP • Build from netos/src/bsp directory • In GNU platform specified in command line to make file – make PLATFORM=platform – In GNU Warnings are now treated as errors and stricter warning checking is enabled (-Wall) • In GHS platform open net. Central. bld, select standard_bsp. bld

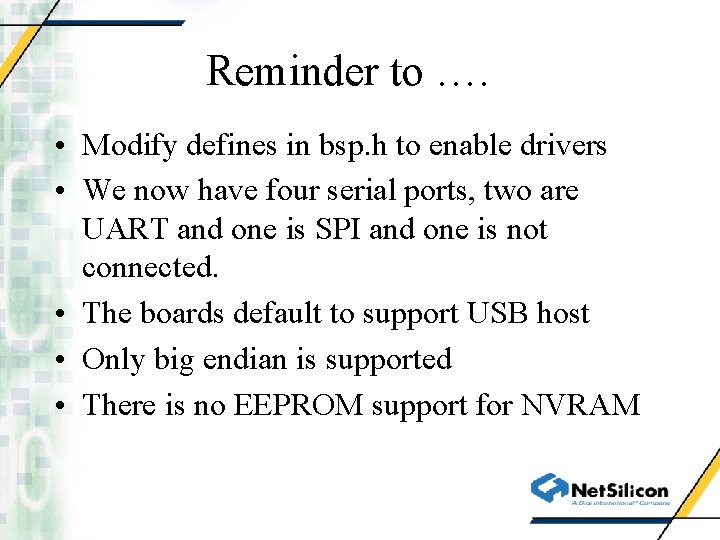

Reminder to …. • Modify defines in bsp. h to enable drivers • We now have four serial ports, two are UART and one is SPI and one is not connected. • The boards default to support USB host • Only big endian is supported • There is no EEPROM support for NVRAM

Initialization and Start up • • • Hardware initialization Software initialization Memory map Device driver initialization Exception and interrupt handler setup Interfacing with higher level modules: RTOS, TCP/IP, ACE, and Application Code

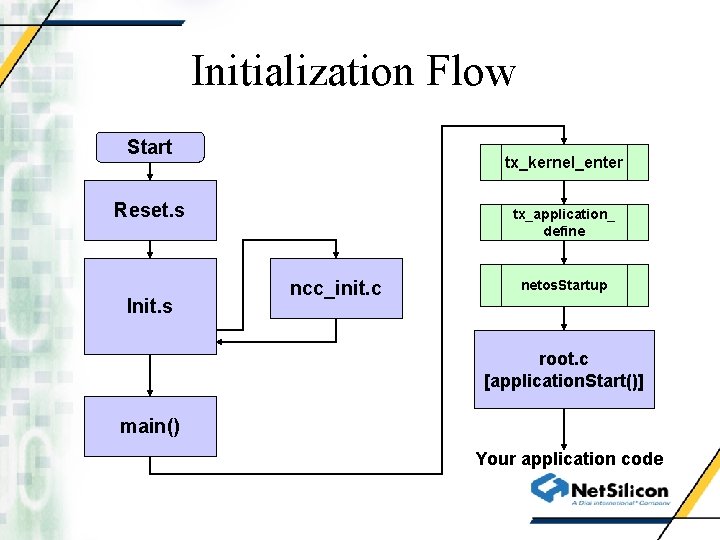

Initialization Flow Start tx_kernel_enter Reset. s Init. s tx_application_ define ncc_init. c netos. Startup root. c [application. Start()] main() Your application code

Hardware Initialization • Reset_Handler: First routine to be executed • Identify and process reset types (hardware reset, power-up reset, software restart, and wakeup reset from sleep mode). • Initializes SDRAM on CS 4 using the values from settings. s (RAS/CAS) • USB configuration and Bbus rest • Calls ncc. Init using a small stack on CS 4 • Jumps to C library Reset_Handler. doc

Initialization: ncc. Init • Check to see if we are in the debugger or if a software restart occurred. • Call setup. Simple. Serial • Call customize. Setup. GPIO • Call customize. Read. Power. On. Buttons • Call customize. Memory. Test • Programs chip selects (Base and Mask)

Initialization: (cont) • ncc. Init: Check to see if the application will fit into RAM (linker directives) ncc_init. doc

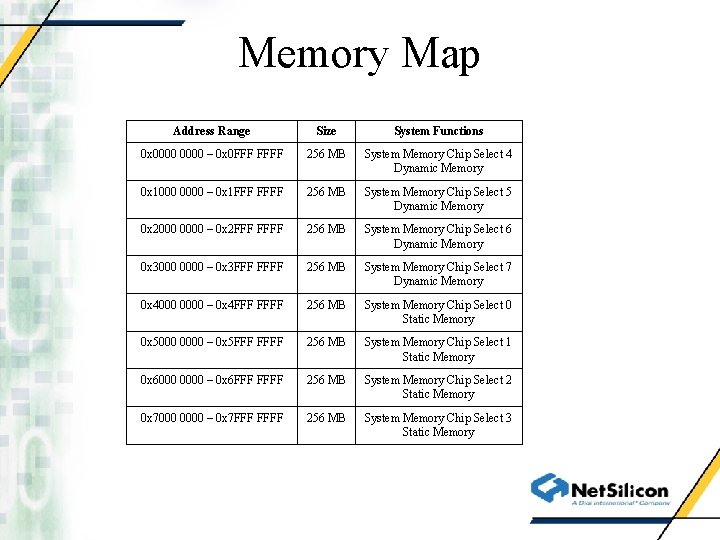

Memory Map Address Range Size System Functions 0 x 0000 – 0 x 0 FFF FFFF 256 MB System Memory Chip Select 4 Dynamic Memory 0 x 1000 0000 – 0 x 1 FFF FFFF 256 MB System Memory Chip Select 5 Dynamic Memory 0 x 2000 0000 – 0 x 2 FFF FFFF 256 MB System Memory Chip Select 6 Dynamic Memory 0 x 3000 0000 – 0 x 3 FFF FFFF 256 MB System Memory Chip Select 7 Dynamic Memory 0 x 4000 0000 – 0 x 4 FFF FFFF 256 MB System Memory Chip Select 0 Static Memory 0 x 5000 0000 – 0 x 5 FFF FFFF 256 MB System Memory Chip Select 1 Static Memory 0 x 6000 0000 – 0 x 6 FFF FFFF 256 MB System Memory Chip Select 2 Static Memory 0 x 7000 0000 – 0 x 7 FFF FFFF 256 MB System Memory Chip Select 3 Static Memory

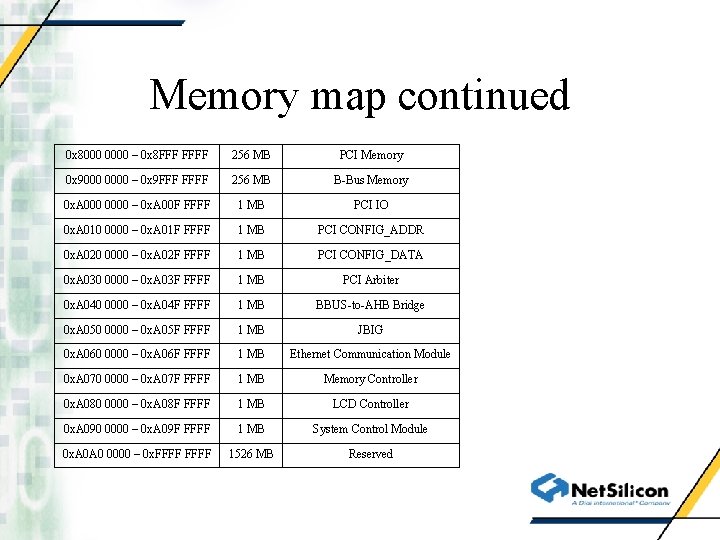

Memory map continued 0 x 8000 0000 – 0 x 8 FFF FFFF 256 MB PCI Memory 0 x 9000 0000 – 0 x 9 FFF FFFF 256 MB B-Bus Memory 0 x. A 0000 – 0 x. A 00 F FFFF 1 MB PCI IO 0 x. A 010 0000 – 0 x. A 01 F FFFF 1 MB PCI CONFIG_ADDR 0 x. A 020 0000 – 0 x. A 02 F FFFF 1 MB PCI CONFIG_DATA 0 x. A 030 0000 – 0 x. A 03 F FFFF 1 MB PCI Arbiter 0 x. A 040 0000 – 0 x. A 04 F FFFF 1 MB BBUS-to-AHB Bridge 0 x. A 050 0000 – 0 x. A 05 F FFFF 1 MB JBIG 0 x. A 060 0000 – 0 x. A 06 F FFFF 1 MB Ethernet Communication Module 0 x. A 070 0000 – 0 x. A 07 F FFFF 1 MB Memory Controller 0 x. A 080 0000 – 0 x. A 08 F FFFF 1 MB LCD Controller 0 x. A 090 0000 – 0 x. A 09 F FFFF 1 MB System Control Module 0 x. A 0 A 0 0000 – 0 x. FFFF 1526 MB Reserved

SDRAM Memory settings • Settings. s contains the memory controller register settings for SDRAM. (not in debugger) • If you use different memory parts you must modify this file (PC 133). • RAS and CAS Delay Registers • Dynamic memory configuration registers

SRAM (flash) • Table defined in bsp. c defines the register settings for SRAM parts • SRAM memory configuration registers, specifies 16 bit or 32 -bit. • Static memory Read Delay registers

Initialization : Main() • • • execute POST Setup. Vector Table Enable MMU (data cache) DDI First Level Initialization Start thread. X main. doc

Initialization: Loading RTOS • Set up FIQ and IRQ stack. • Create threadx (system) timer thread (stack size 1024, priority is 0). • Call BSP routine to set up system timer clock and timer 2 and to create root thread (stack size and priority are configurable in appconf. h file) and start it. • Start RTOS scheduler. threadx_init. doc

Root Thread: netos. Startup() • Load device drivers • Read parameters from NVRAM and configure dialog. • Call netosstart. TCP() to initialize and start TCP/IP stack and ACE. • Set up real time source and install time zone. • Start up application. root_thread. doc

- Slides: 20