National Taiwan University Chap 8 Datapath Units Multiplier

- Slides: 25

National Taiwan University Chap. 8 Datapath Units: Multiplier Design Prof. An-Yeu Wu Undergraduate VLSI Design Course Updated: June 12, 2002

National Taiwan University Several Implementations of Multipliers • • Array Multiplier 2’s Complement Array Multiplier Serial Multiplier CSD Code String-encoding Multiplier Modified Booth-encoded Multiplier Implementation (Chap. 8. 2. 7. 2) A. Y. Wu 2

National Taiwan University 6 -by-6 Multiplication A. Y. Wu 3

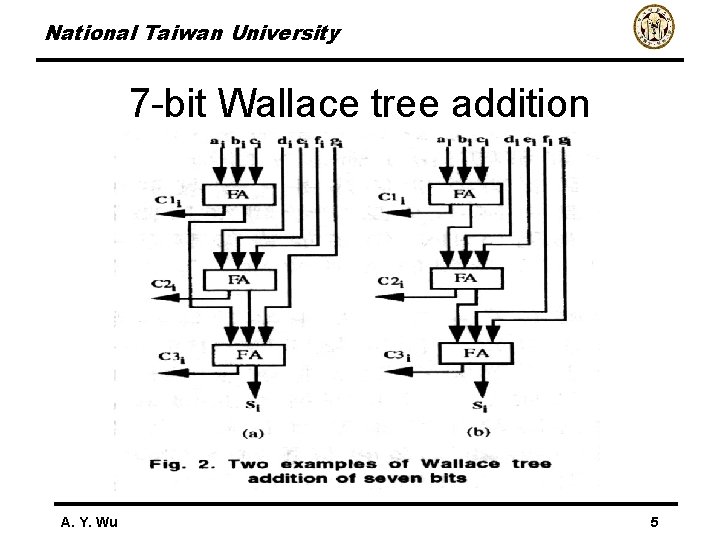

National Taiwan University Wallace-Tree Multiplication A. Y. Wu • FA is a “one’s counter”: Take A, B, and C inputs and encodes them on SUM and CARRY outputs. • A 1 -bit full adder (FA) provides a 3: 2 compression in the number of bits. • A+B+C=2 C+S 4

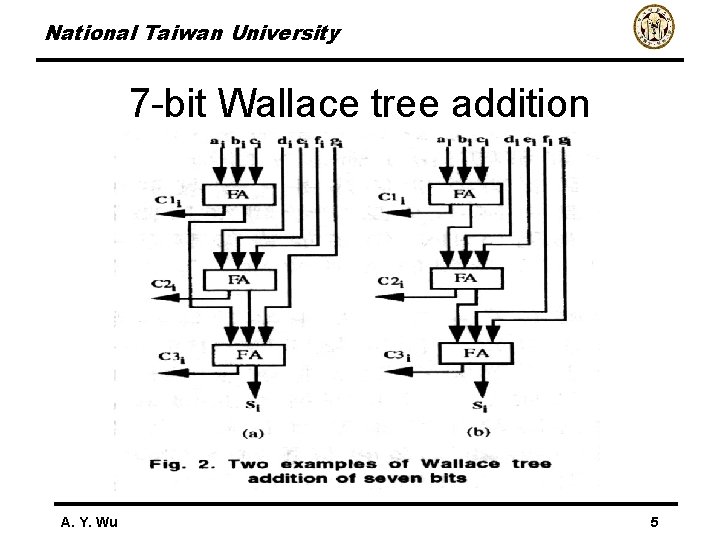

National Taiwan University 7 -bit Wallace tree addition A. Y. Wu 5

National Taiwan University Ex: 6× 6 Wallace Multiplier A. Y. Wu 6

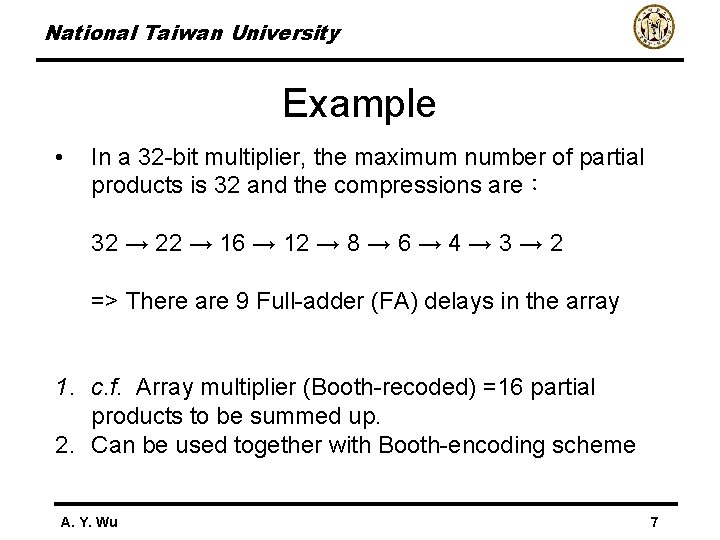

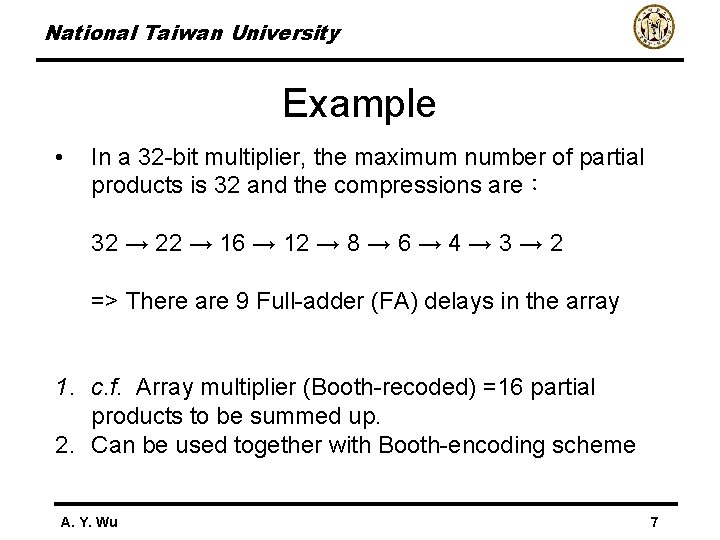

National Taiwan University Example • In a 32 -bit multiplier, the maximum number of partial products is 32 and the compressions are: 32 → 22 → 16 → 12 → 8 → 6 → 4 → 3 → 2 => There are 9 Full-adder (FA) delays in the array 1. c. f. Array multiplier (Booth-recoded) =16 partial products to be summed up. 2. Can be used together with Booth-encoding scheme A. Y. Wu 7

National Taiwan University Wallace Tree Multiplier • Mx. N Booth-encoded multiplier (IEEE JSSC, vol. 1, no. 2, June 1993) A. Y. Wu 8

National Taiwan University A typical delay distribution of the output of Wallace tree section A. Y. Wu 9

National Taiwan University Extension • • 32 -bits Wallace-tree multiplier has 9 FA delays in the array Questions: 1. For a 64 -bit multiplier, what is the minimum adder delay? 2. Is there any way to reduce the delay by other compression scheme? A. Y. Wu 10

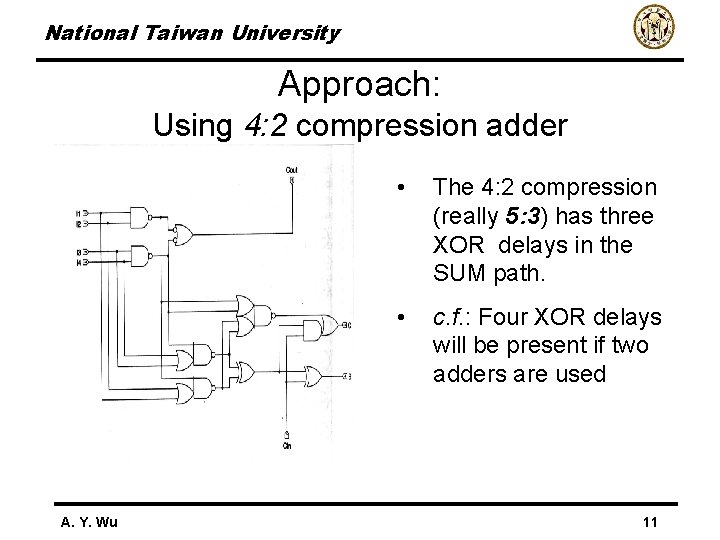

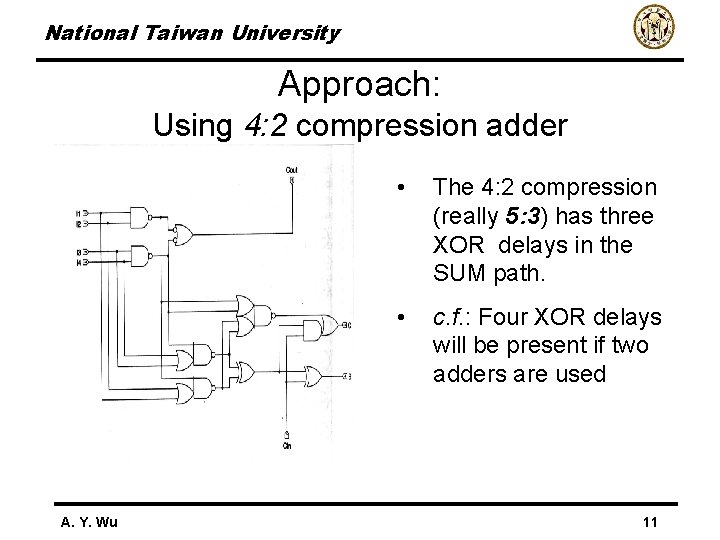

National Taiwan University Approach: Using 4: 2 compression adder A. Y. Wu • The 4: 2 compression (really 5: 3) has three XOR delays in the SUM path. • c. f. : Four XOR delays will be present if two adders are used 11

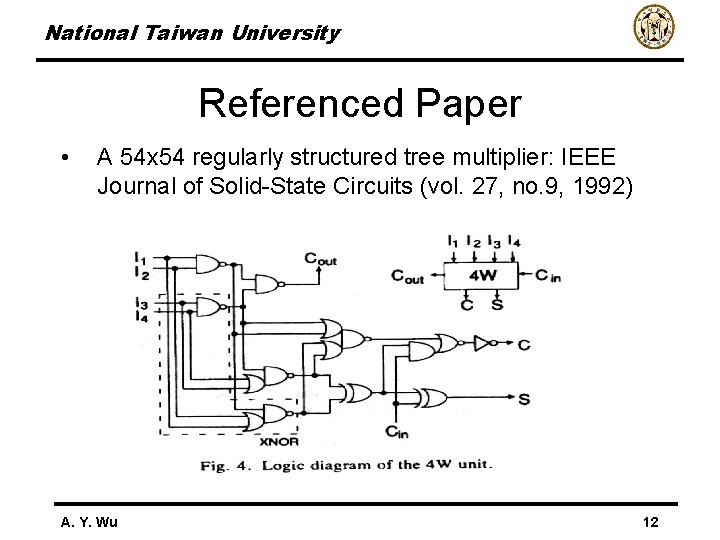

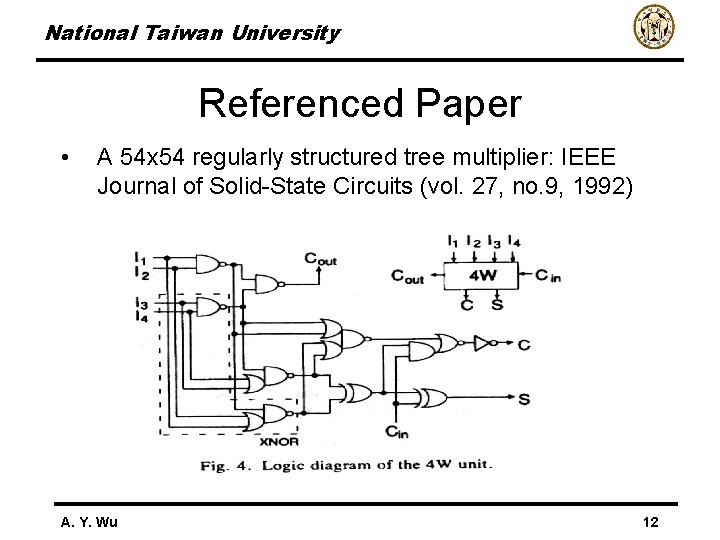

National Taiwan University Referenced Paper • A 54 x 54 regularly structured tree multiplier: IEEE Journal of Solid-State Circuits (vol. 27, no. 9, 1992) A. Y. Wu 12

National Taiwan University Chap. 8. 2. 7. 2: Implementation of Booth-encoded Multiplier A. Y. Wu 13

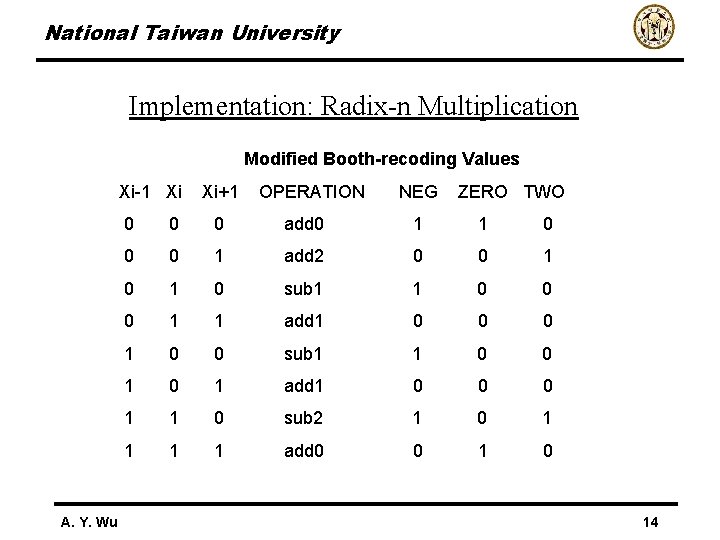

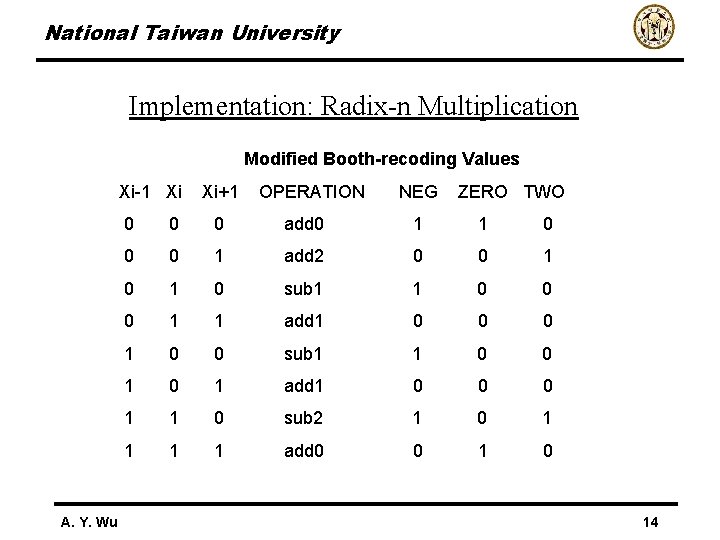

National Taiwan University Implementation: Radix-n Multiplication Modified Booth-recoding Values Xi-1 Xi A. Y. Wu Xi+1 OPERATION NEG ZERO TWO 0 0 0 add 0 1 1 0 0 0 1 add 2 0 0 1 0 sub 1 1 0 0 0 1 1 add 1 0 0 0 1 0 0 sub 1 1 0 0 1 add 1 0 0 0 1 1 0 sub 2 1 0 1 1 add 0 0 14

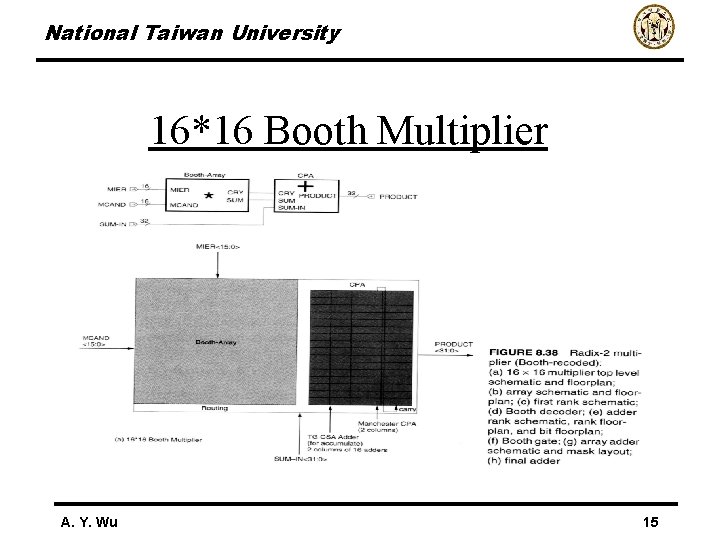

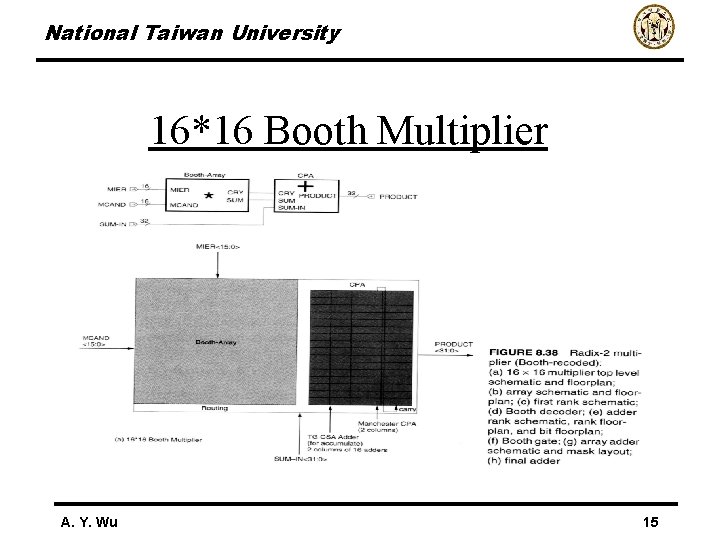

National Taiwan University 16*16 Booth Multiplier A. Y. Wu 15

National Taiwan University Array schematic A. Y. Wu 16

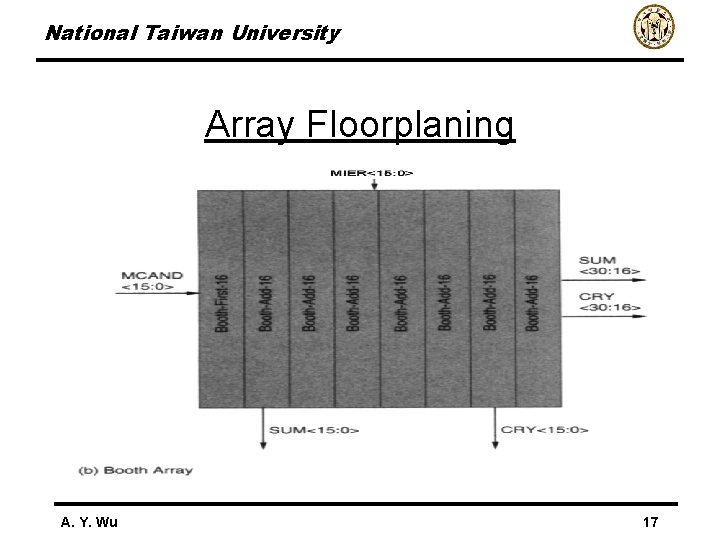

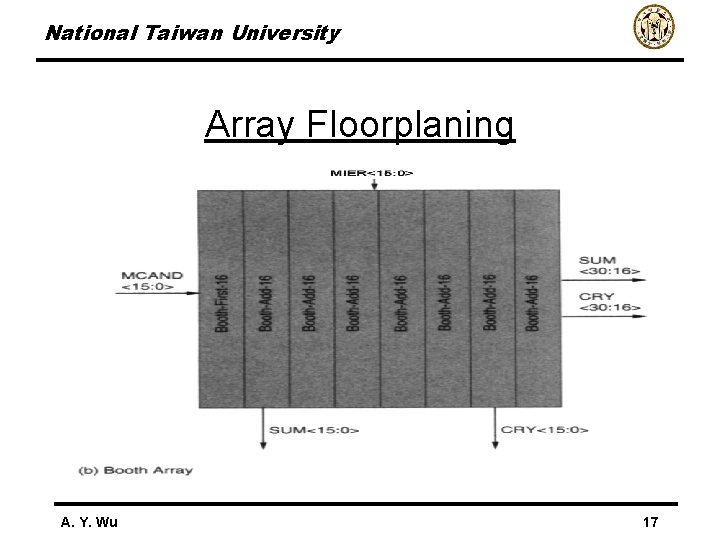

National Taiwan University Array Floorplaning A. Y. Wu 17

National Taiwan University First Rank Schematic A. Y. Wu 18

National Taiwan University Booth decoding Schematic A. Y. Wu 19

National Taiwan University Booth-Add-16 rank floorplan A. Y. Wu 20

National Taiwan University Adder rank schematic A. Y. Wu 21

National Taiwan University Booth gate A. Y. Wu 22

National Taiwan University Array adder layout A. Y. Wu 23

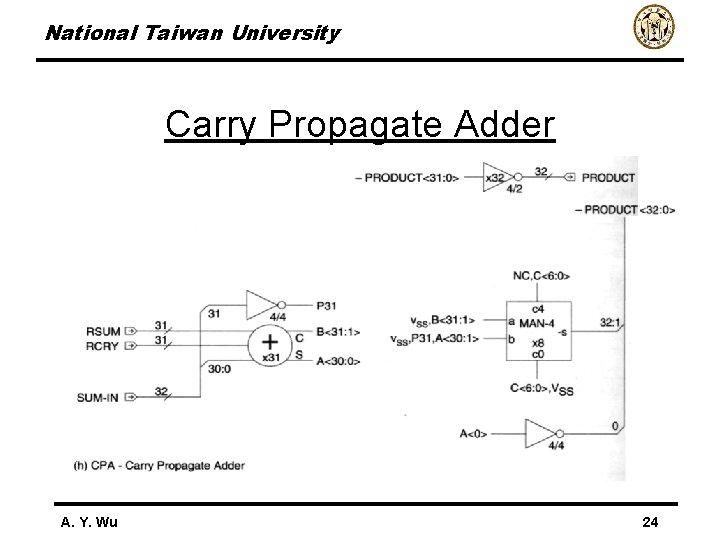

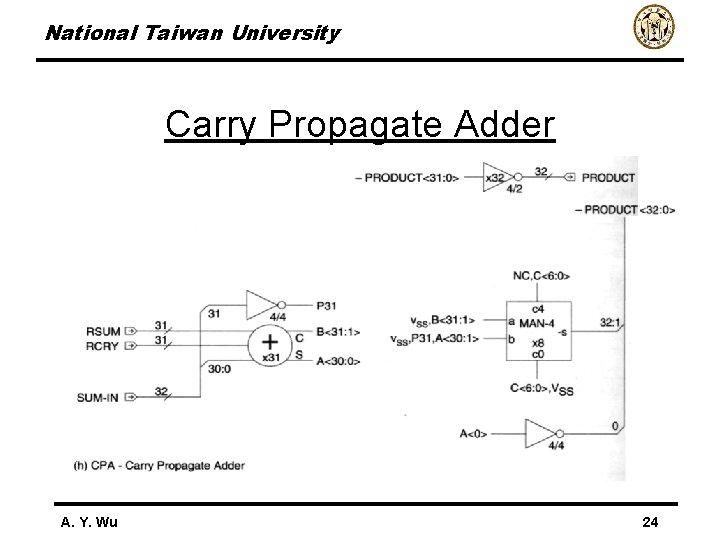

National Taiwan University Carry Propagate Adder A. Y. Wu 24

National Taiwan University Homework #6 (Cancelled) Design an 8 -bit Modified Booth-encoded (or String-encoding based) Wallace-tree Multiplier 1. 2. 3. 4. 5. 6. A. Y. Wu Draw the schematic diagram of your design. Verify your design first using C/C++ or Matlab programs. Write down the Verilog/VHDL code and perform simulation. Verify your Verilog/VHDL codes. That is, check your simulation results with the C/C++/Matlab results. Show your (1) Schematic (2) Source code (3) Simulation results in your report. Due date: June 28, 2002. 25