Naslovno dekodiranje postavljanje naprav v naslovni prostor Izbira

Naslovno dekodiranje – postavljanje naprav v naslovni prostor

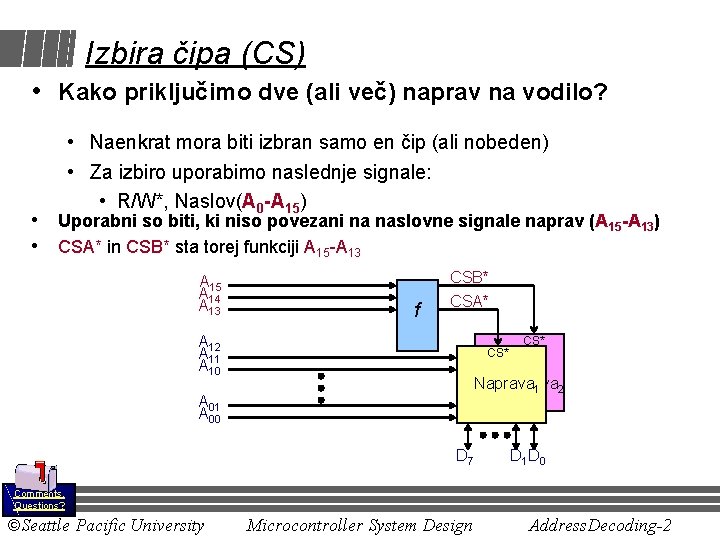

Izbira čipa (CS) • Kako priključimo dve (ali več) naprav na vodilo? • Naenkrat mora biti izbran samo en čip (ali nobeden) • Za izbiro uporabimo naslednje signale: • R/W*, Naslov(A 0 -A 15) • Uporabni so biti, ki niso povezani na naslovne signale naprav (A 15 -A 13) • CSA* in CSB* sta torej funkciji A 15 -A 13 A 15 A 14 A 13 f CSB* CSA* A 12 A 11 A 10 CS* Naprava 1 2 A 01 A 00 D 7 D 1 D 0 Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-2

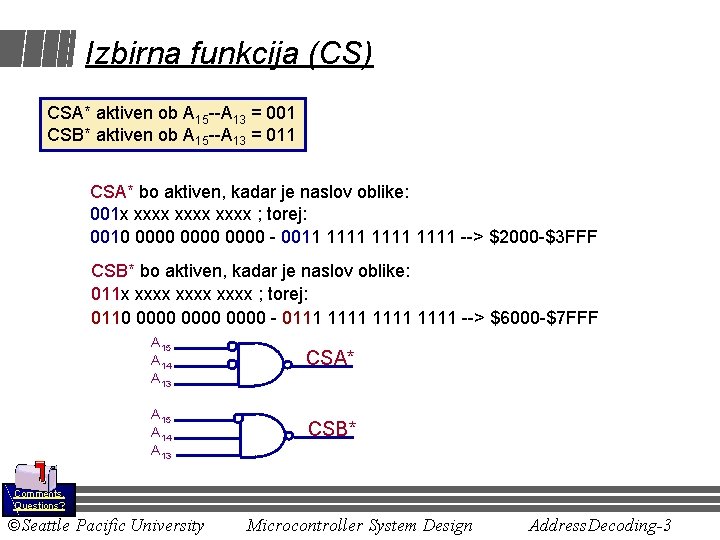

Izbirna funkcija (CS) CSA* aktiven ob A 15 --A 13 = 001 CSB* aktiven ob A 15 --A 13 = 011 CSA* bo aktiven, kadar je naslov oblike: 001 x xxxx ; torej: 0010 0000 - 0011 1111 --> $2000 -$3 FFF CSB* bo aktiven, kadar je naslov oblike: 011 x xxxx ; torej: 0110 0000 - 0111 1111 --> $6000 -$7 FFF A 15 A 14 A 13 CSA* A 15 A 14 A 13 CSB* Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-3

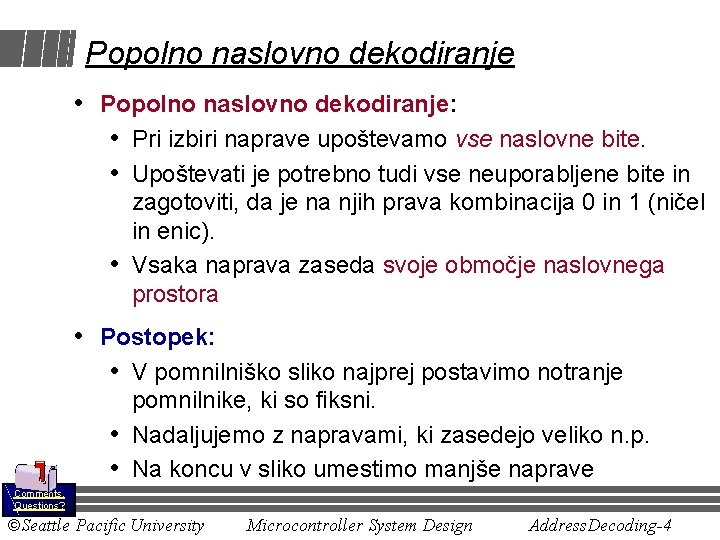

Popolno naslovno dekodiranje • Popolno naslovno dekodiranje: • Pri izbiri naprave upoštevamo vse naslovne bite. • Upoštevati je potrebno tudi vse neuporabljene bite in zagotoviti, da je na njih prava kombinacija 0 in 1 (ničel in enic). • Vsaka naprava zaseda svoje območje naslovnega prostora • Postopek: • V pomnilniško sliko najprej postavimo notranje pomnilnike, ki so fiksni. • Nadaljujemo z napravami, ki zasedejo veliko n. p. • Na koncu v sliko umestimo manjše naprave Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-4

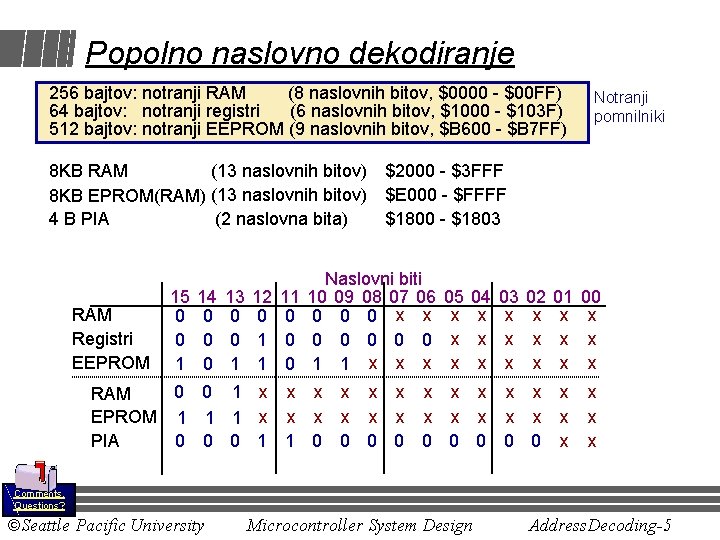

Popolno naslovno dekodiranje 256 bajtov: notranji RAM (8 naslovnih bitov, $0000 - $00 FF) 64 bajtov: notranji registri (6 naslovnih bitov, $1000 - $103 F) 512 bajtov: notranji EEPROM (9 naslovnih bitov, $B 600 - $B 7 FF) Notranji pomnilniki 8 KB RAM (13 naslovnih bitov) $2000 - $3 FFF 8 KB EPROM(RAM) (13 naslovnih bitov) $E 000 - $FFFF 4 B PIA (2 naslovna bita) $1800 - $1803 02 x x x 01 x x x 00 x x x 0 0 1 x x x RAM EPROM 1 1 1 x x x PIA 0 0 0 1 1 0 0 0 0 0 x x x RAM Registri EEPROM 15 0 0 1 14 0 0 0 13 0 0 1 12 0 1 1 11 0 0 0 Naslovni biti 10 09 08 07 06 0 0 0 x x 0 0 0 1 1 x x x 05 x x x 04 x x x 03 x x x Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-5

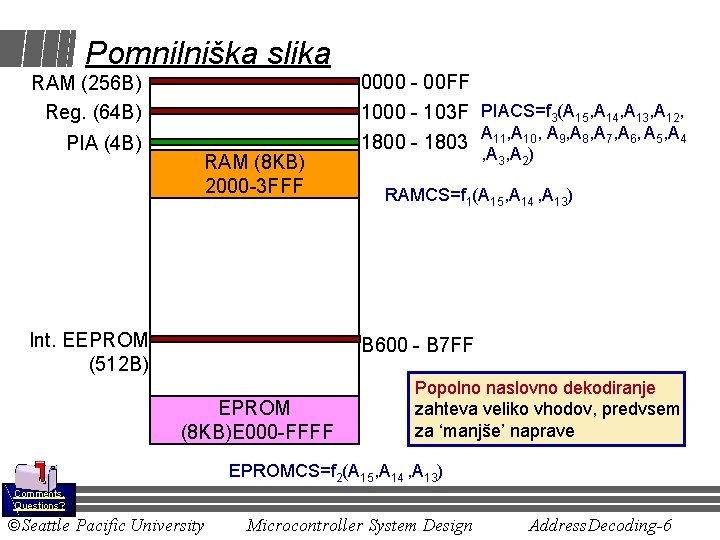

Pomnilniška slika 0000 - 00 FF 1000 - 103 F PIACS=f 3(A 15, A 14, A 13, A 12, RAM (256 B) Reg. (64 B) PIA (4 B) RAM (8 KB) 2000 -3 FFF Int. EEPROM (512 B) 1800 - 1803 A 11, A 10, A 9, A 8, A 7, A 6, A 5, A 4 , A 3, A 2) RAMCS=f 1(A 15, A 14 , A 13) B 600 - B 7 FF EPROM (8 KB)E 000 -FFFF Popolno naslovno dekodiranje zahteva veliko vhodov, predvsem za ‘manjše’ naprave EPROMCS=f 2(A 15, A 14 , A 13) Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-6

P. N. D. - povzetek • Popolno naslovno dekodiranje: vsak fizični naslov ima natanko en logični naslov • Funkcije CS imajo veliko vhodov • Naslovni prostor za naknadno dodajanje naprav • Dekodiranje naslovov je zapleteno • Običajno zahteva veliko dekoderjev (čipov) Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-7

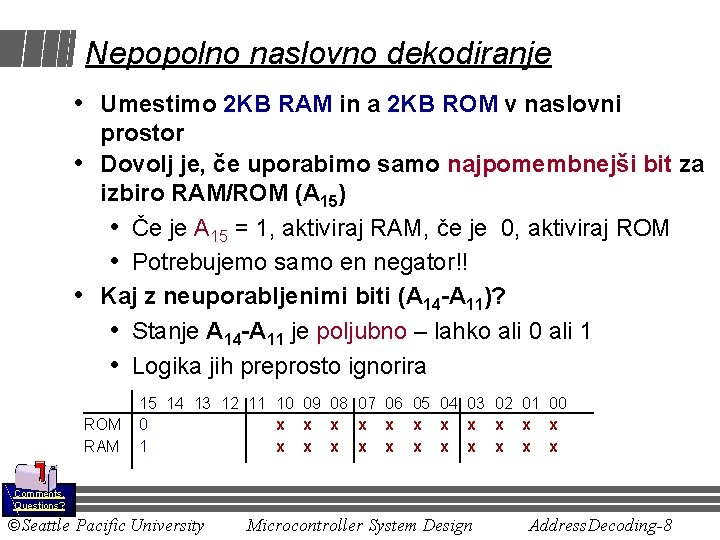

Nepopolno naslovno dekodiranje • Umestimo 2 KB RAM in a 2 KB ROM v naslovni prostor • Dovolj je, če uporabimo samo najpomembnejši bit za izbiro RAM/ROM (A 15) • Če je A 15 = 1, aktiviraj RAM, če je 0, aktiviraj ROM • Potrebujemo samo en negator!! • Kaj z neuporabljenimi biti (A 14 -A 11)? • Stanje A 14 -A 11 je poljubno – lahko ali 0 ali 1 • Logika jih preprosto ignorira ROM RAM 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 0 x x x 1 x x x Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-8

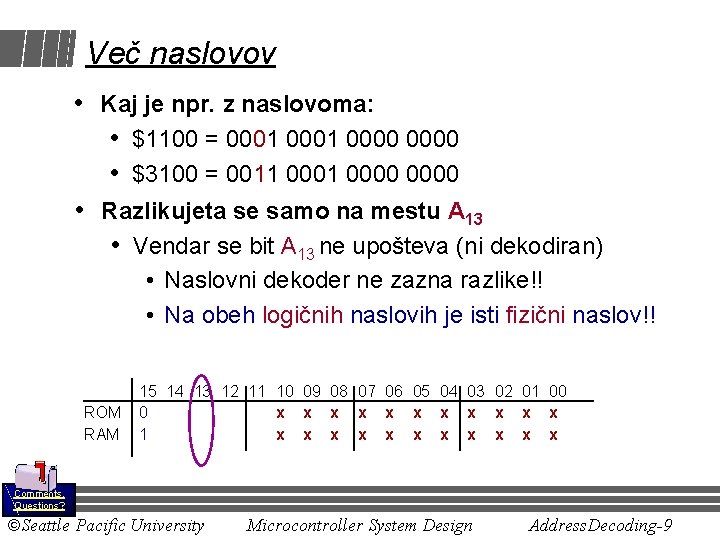

Več naslovov • Kaj je npr. z naslovoma: • $1100 = 0001 0000 • $3100 = 0011 0000 • Razlikujeta se samo na mestu A 13 • Vendar se bit A 13 ne upošteva (ni dekodiran) • Naslovni dekoder ne zazna razlike!! • Na obeh logičnih naslovih je isti fizični naslov!! ROM RAM 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 0 x x x 1 x x x Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-9

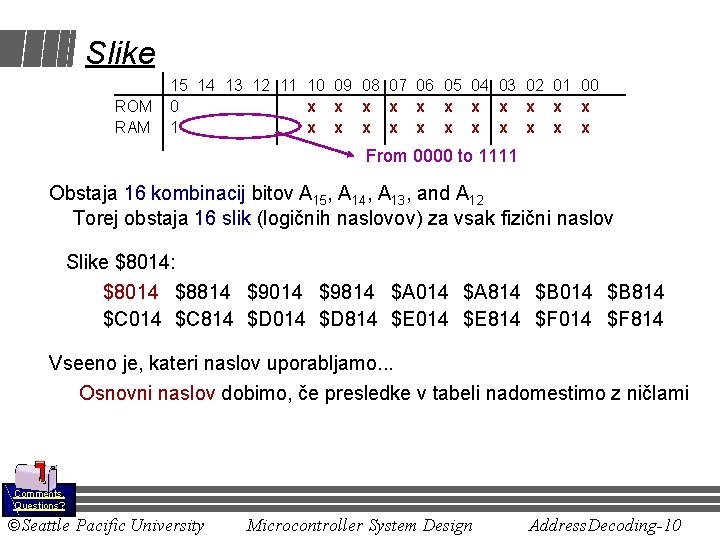

Slike ROM RAM 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 0 x x x 1 x x x From 0000 to 1111 Obstaja 16 kombinacij bitov A 15, A 14, A 13, and A 12 Torej obstaja 16 slik (logičnih naslovov) za vsak fizični naslov Slike $8014: $8014 $8814 $9014 $9814 $A 014 $A 814 $B 014 $B 814 $C 014 $C 814 $D 014 $D 814 $E 014 $E 814 $F 014 $F 814 Vseeno je, kateri naslov uporabljamo. . . Osnovni naslov dobimo, če presledke v tabeli nadomestimo z ničlami Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-10

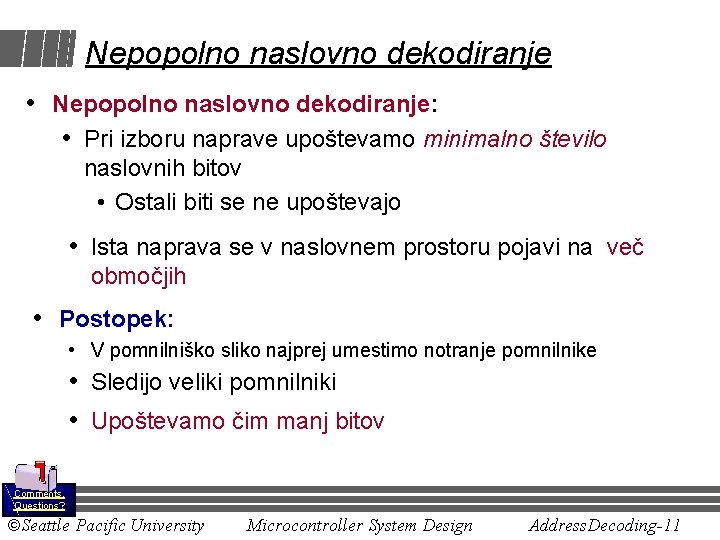

Nepopolno naslovno dekodiranje • Nepopolno naslovno dekodiranje: • Pri izboru naprave upoštevamo minimalno število naslovnih bitov • Ostali biti se ne upoštevajo • Ista naprava se v naslovnem prostoru pojavi na več območjih • Postopek: • V pomnilniško sliko najprej umestimo notranje pomnilnike • Sledijo veliki pomnilniki • Upoštevamo čim manj bitov Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-11

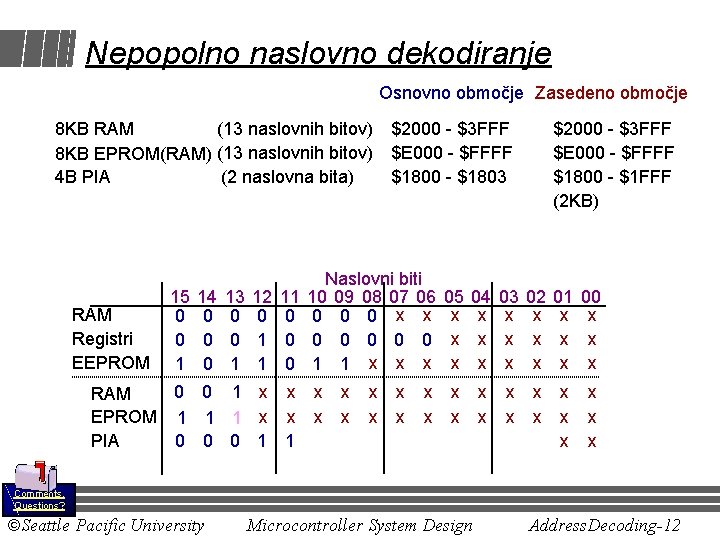

Nepopolno naslovno dekodiranje Osnovno območje Zasedeno območje 8 KB RAM (13 naslovnih bitov) $2000 - $3 FFF 8 KB EPROM(RAM) (13 naslovnih bitov) $E 000 - $FFFF 4 B PIA (2 naslovna bita) $1800 - $1803 RAM Registri EEPROM 15 0 0 1 14 0 0 0 13 0 0 1 12 0 1 1 11 0 0 0 1 x x RAM EPROM 1 1 1 x x PIA 0 0 0 1 1 Naslovni biti 10 09 08 07 06 0 0 0 x x 0 0 0 1 1 x x x x $2000 - $3 FFF $E 000 - $FFFF $1800 - $1 FFF (2 KB) 05 x x x 04 x x x 03 x x x 02 x x x 01 x x x 00 x x x x x Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-12

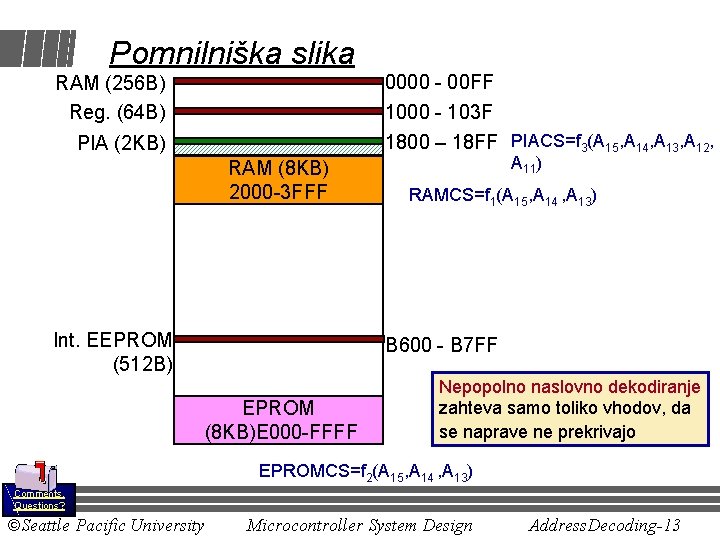

Pomnilniška slika 0000 - 00 FF 1000 - 103 F RAM (256 B) Reg. (64 B) 1800 – 18 FF PIACS=f 3(A 15, A 14, A 13, A 12, PIA (2 KB) RAM (8 KB) 2000 -3 FFF Int. EEPROM (512 B) A 11) RAMCS=f 1(A 15, A 14 , A 13) B 600 - B 7 FF EPROM (8 KB)E 000 -FFFF Nepopolno naslovno dekodiranje zahteva samo toliko vhodov, da se naprave ne prekrivajo EPROMCS=f 2(A 15, A 14 , A 13) Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-13

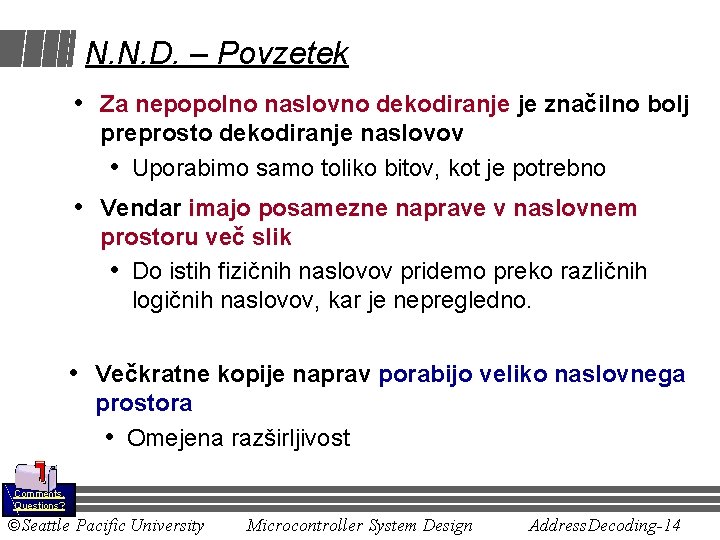

N. N. D. – Povzetek • Za nepopolno naslovno dekodiranje je značilno bolj preprosto dekodiranje naslovov • Uporabimo samo toliko bitov, kot je potrebno • Vendar imajo posamezne naprave v naslovnem prostoru več slik • Do istih fizičnih naslovov pridemo preko različnih logičnih naslovov, kar je nepregledno. • Večkratne kopije naprav porabijo veliko naslovnega prostora • Omejena razširljivost Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-14

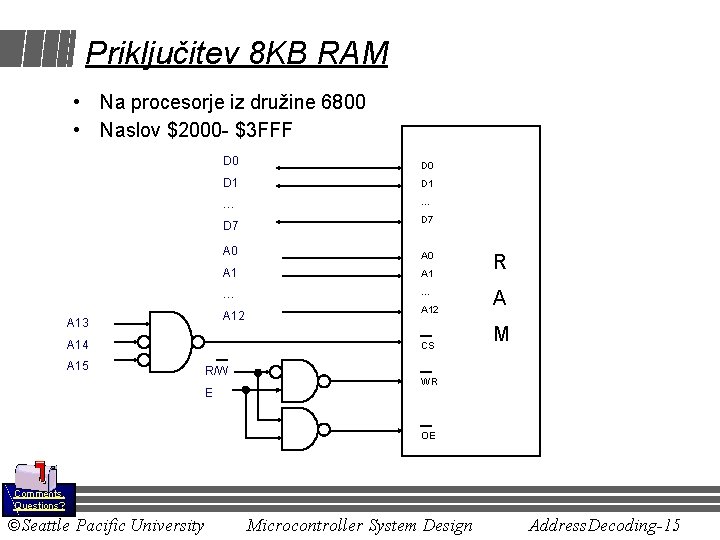

Priključitev 8 KB RAM • Na procesorje iz družine 6800 • Naslov $2000 - $3 FFF D 0 D 1 … … D 7 A 0 A 1 … … A 12 A 13 A 14 A 15 D 7 A 12 CS R/W E R A M WR OE Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-15

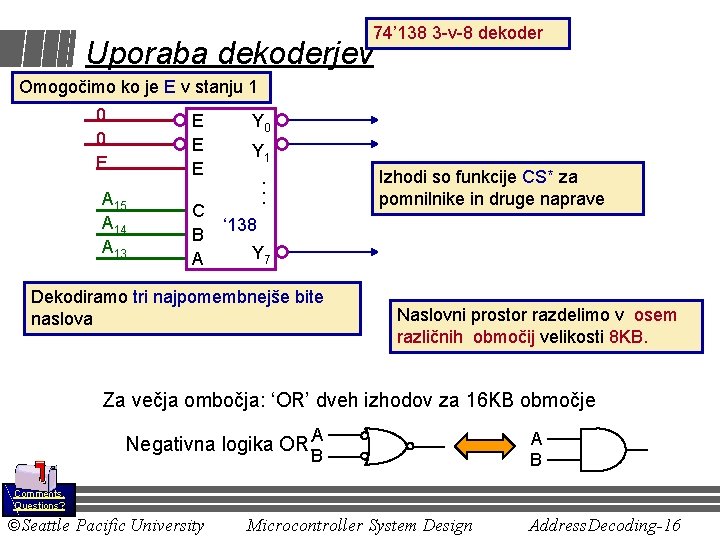

74’ 138 3 -v-8 dekoder Uporaba dekoderjev Omogočimo ko je E v stanju 1 0 0 E E C B A Y 1 Izhodi so funkcije CS* za pomnilnike in druge naprave . . . A 15 A 14 A 13 Y 0 ‘ 138 Y 7 Dekodiramo tri najpomembnejše bite naslova Naslovni prostor razdelimo v osem različnih območij velikosti 8 KB. Za večja ombočja: ‘OR’ dveh izhodov za 16 KB območje A B Negativna logika OR: A B Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-16

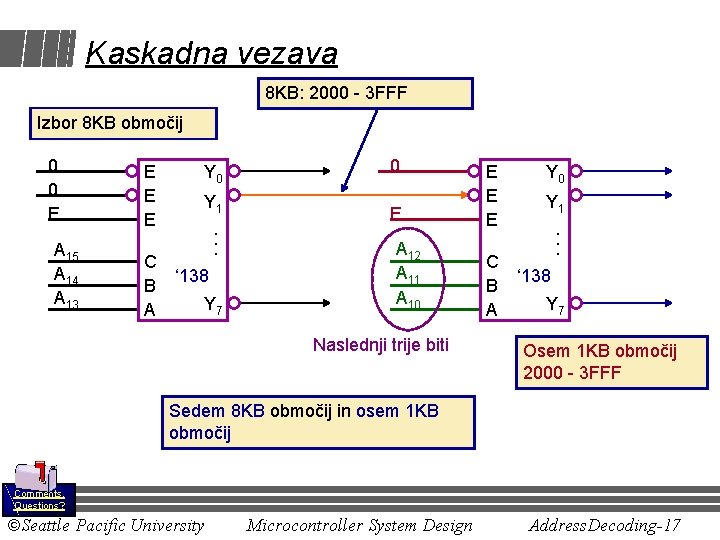

Kaskadna vezava 8 KB: 2000 - 3 FFF Izbor 8 KB območij 0 0 E Y 1 ‘ 138 Y 7 0 E A 12 A 11 A 10 Naslednji trije biti E E E C B A Y 0 Y 1. . . C B A Y 0 . . . A 15 A 14 A 13 E E E ‘ 138 Y 7 Osem 1 KB območij 2000 - 3 FFF Sedem 8 KB območij in osem 1 KB območij Comments, Questions? ãSeattle Pacific University Microcontroller System Design Address. Decoding-17

- Slides: 17