Nanometer Transistors and Their Models Jan M Rabaey

Nanometer Transistors and Their Models Jan M. Rabaey Low Power Design Essentials © 2008 Chapter 2

Chapter Outline § § Nanometer transistor behavior and models Sub-threshold currents and leakage Variability Device and technology innovations Low Power Design Essentials © 2008 2. 2

Nanometer Transistors and Their Models § Emerging devices in the sub-100 nm regime post challenges to low-power design – Leakage – Variability – Reliability § Yet also offer some opportunities – Increased mobility – Improved control (? ) § State-of-the-art low-power design should build on and exploit these properties – Requires clear understanding and good models Low Power Design Essentials © 2008 2. 3

The Sub-100 nm transistor § Velocity-saturated – Linear dependence between ID and VGS § Threshold voltage VTH strongly impacted by channel length L and VDS – Reduced threshold control through body biasing § Leaky – Subthreshold leakage – Gate leakage → Decreasing Ion over Ioff ratio Low Power Design Essentials © 2008 2. 4

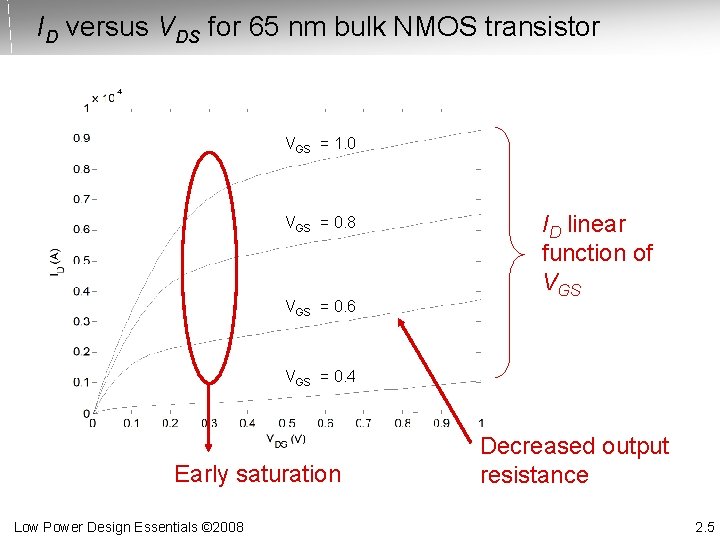

ID versus VDS for 65 nm bulk NMOS transistor VGS = 1. 0 VGS = 0. 8 VGS = 0. 6 ID linear function of VGS = 0. 4 Early saturation Low Power Design Essentials © 2008 Decreased output resistance 2. 5

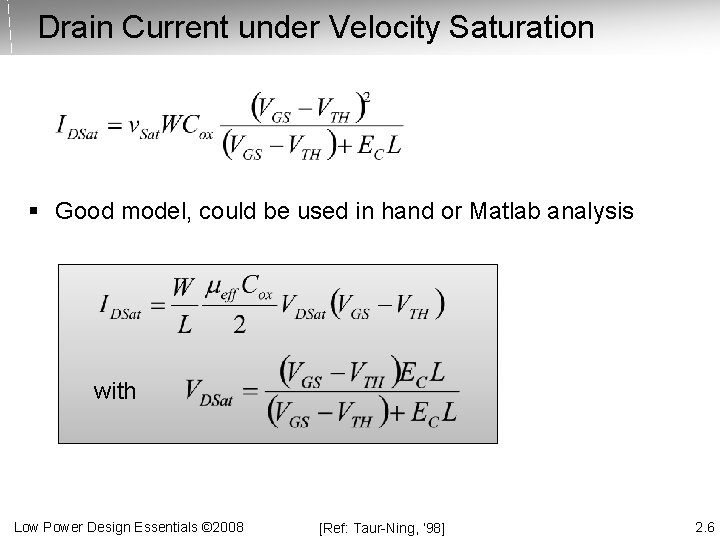

Drain Current under Velocity Saturation § Good model, could be used in hand or Matlab analysis with Low Power Design Essentials © 2008 [Ref: Taur-Ning, ’ 98] 2. 6

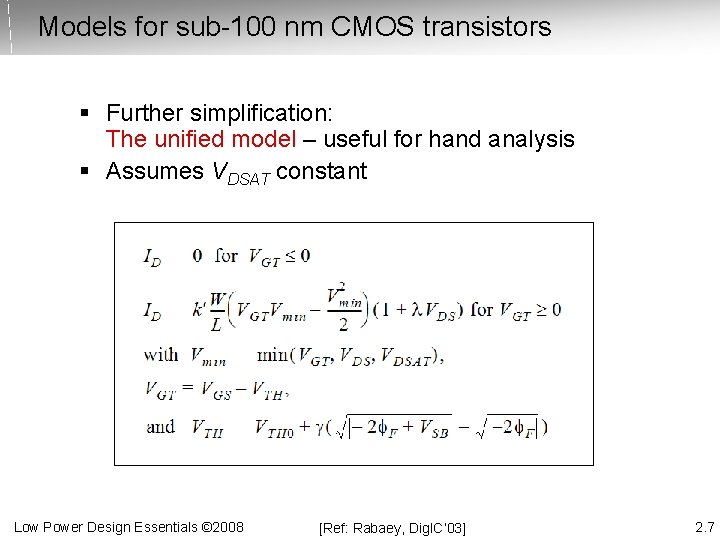

Models for sub-100 nm CMOS transistors § Further simplification: The unified model – useful for hand analysis § Assumes VDSAT constant Low Power Design Essentials © 2008 [Ref: Rabaey, Dig. IC’ 03] 2. 7

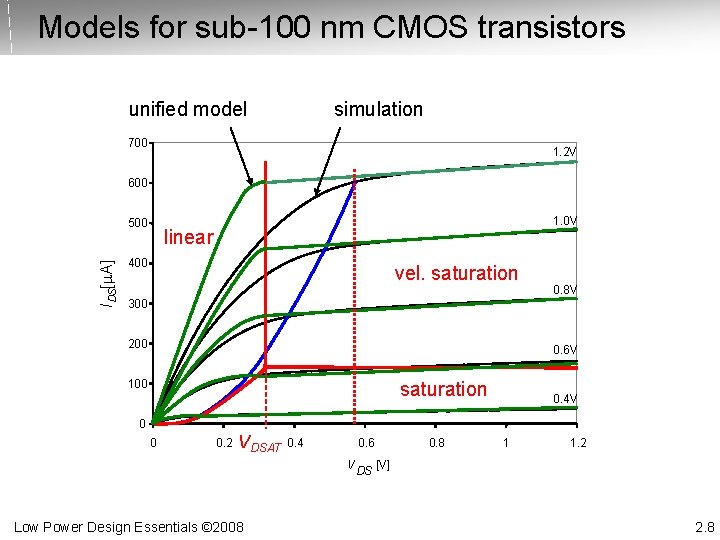

Models for sub-100 nm CMOS transistors unified model simulation 700 1. 2 V 600 IDS[m. A] 500 1. 0 V linear 400 vel. saturation 0. 8 V 300 200 0. 6 V 100 saturation 0. 4 V 0 0 0. 2 VDSAT 0. 4 0. 6 V Low Power Design Essentials © 2008 DS 0. 8 1 1. 2 [V] 2. 8

Alpha Power Law Model § Alternate approach, useful for hand analysis of propagation delay § This is not a physical model § Simply empirical: § Parameter is between 1 and 2. § In 65 nm – 180 nm CMOS technology ~ 1. 2. . 1. 3 Low Power Design Essentials © 2008 – Can fit (in minimum mean squares sense) to variety of ’s, VTH – Need to find one with minimum square error – fitted VTH can be different from physical [Ref: Sakurai, JSSC’ 90] 2. 9

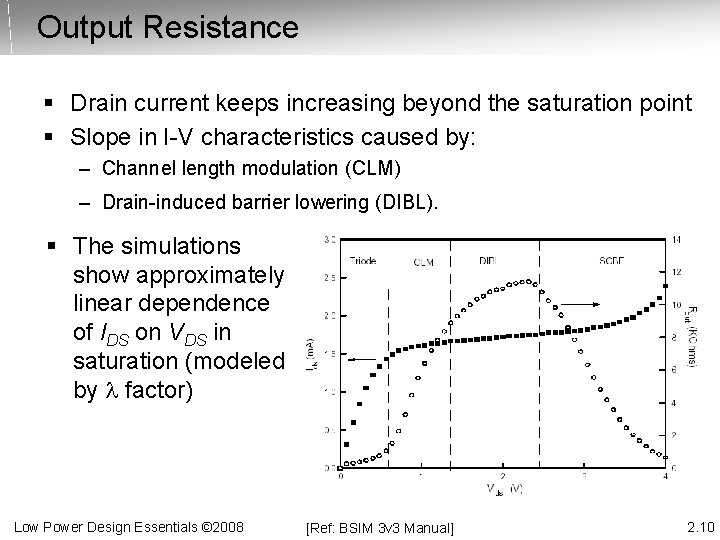

Output Resistance § Drain current keeps increasing beyond the saturation point § Slope in I-V characteristics caused by: – Channel length modulation (CLM) – Drain-induced barrier lowering (DIBL). § The simulations show approximately linear dependence of IDS on VDS in saturation (modeled by l factor) Low Power Design Essentials © 2008 [Ref: BSIM 3 v 3 Manual] 2. 10

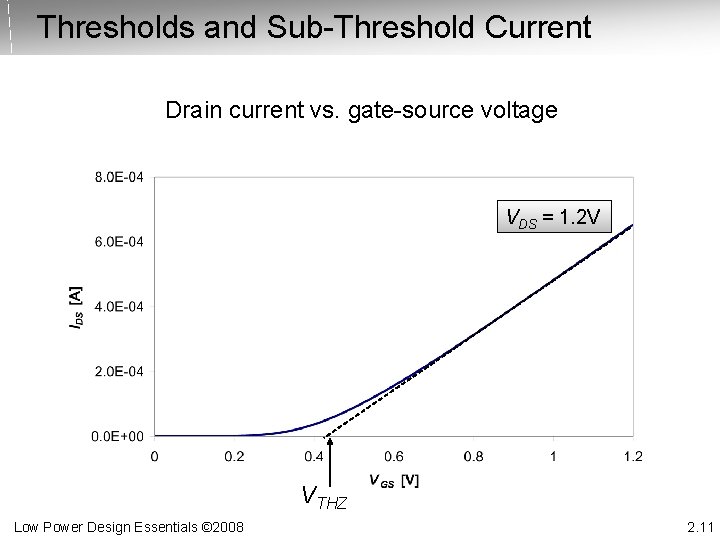

Thresholds and Sub-Threshold Current Drain current vs. gate-source voltage VDS = 1. 2 V VTHZ Low Power Design Essentials © 2008 2. 11

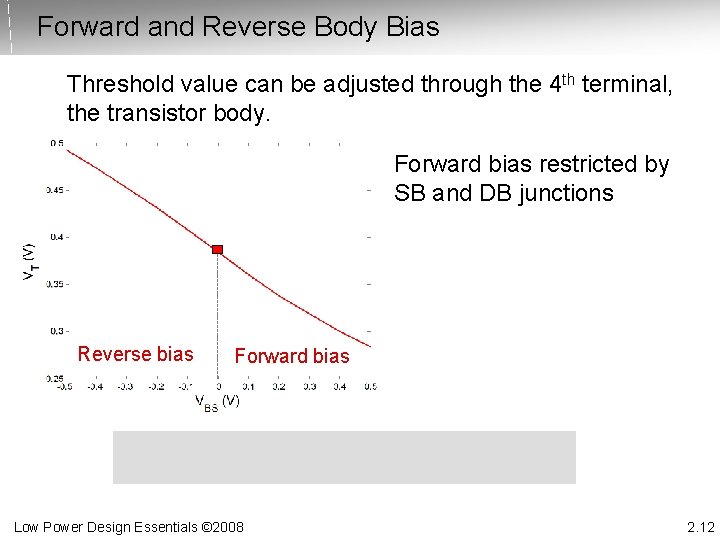

Forward and Reverse Body Bias Threshold value can be adjusted through the 4 th terminal, the transistor body. Forward bias restricted by SB and DB junctions Reverse bias Forward bias Low Power Design Essentials © 2008 2. 12

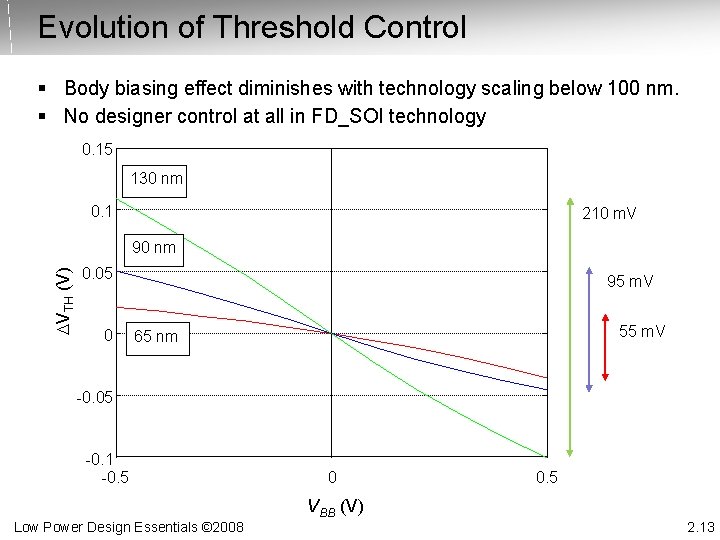

Evolution of Threshold Control § Body biasing effect diminishes with technology scaling below 100 nm. § No designer control at all in FD_SOI technology 0. 15 130 nm 0. 1 210 m. V DVTH (V) 90 nm 0. 05 0 95 m. V 55 m. V 65 nm -0. 05 -0. 1 -0. 5 0 0. 5 VBB (V) Low Power Design Essentials © 2008 2. 13

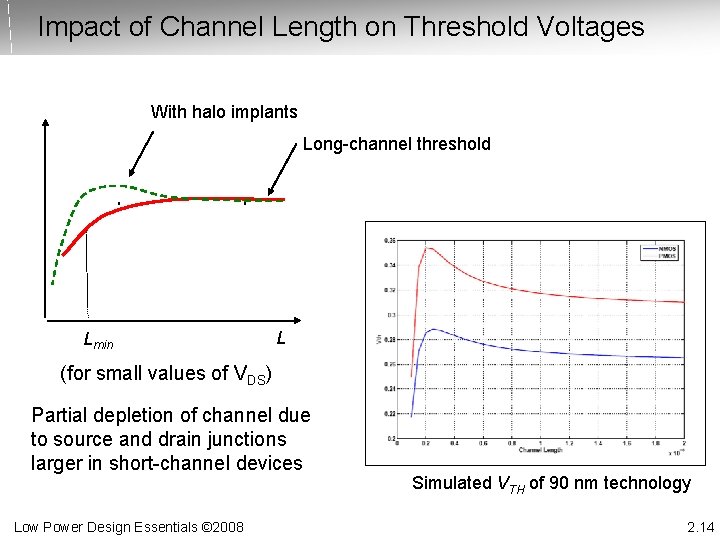

Impact of Channel Length on Threshold Voltages With halo implants Long-channel threshold Lmin L (for small values of VDS) Partial depletion of channel due to source and drain junctions larger in short-channel devices Low Power Design Essentials © 2008 Simulated VTH of 90 nm technology 2. 14

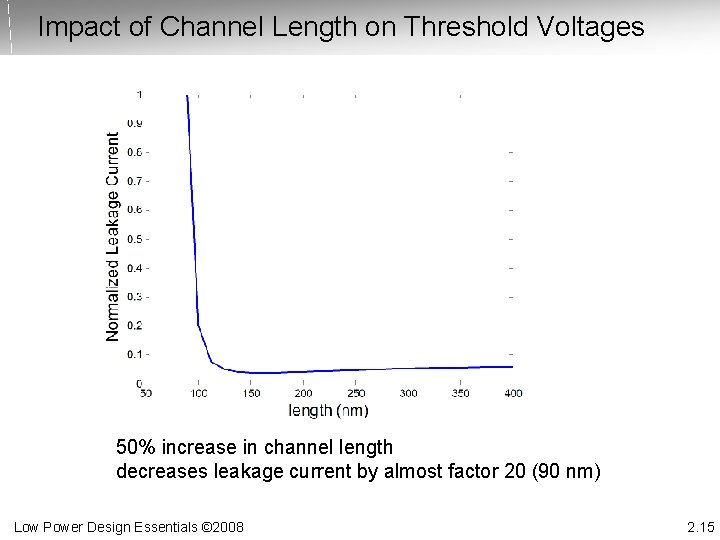

Impact of Channel Length on Threshold Voltages 50% increase in channel length decreases leakage current by almost factor 20 (90 nm) Low Power Design Essentials © 2008 2. 15

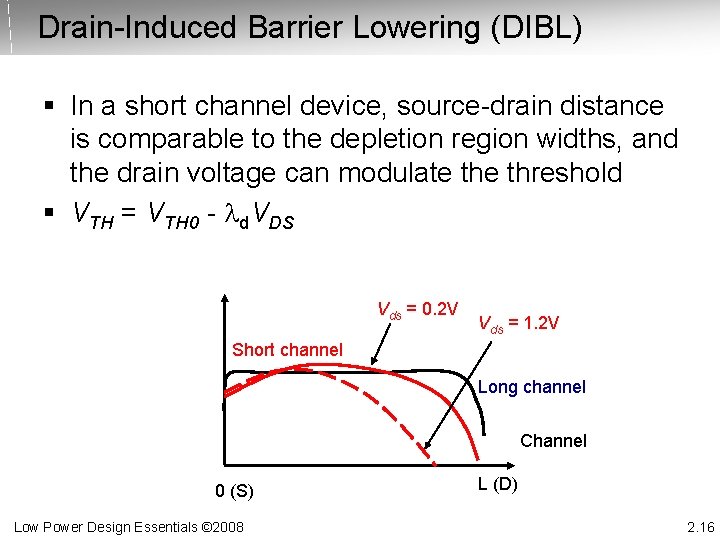

Drain-Induced Barrier Lowering (DIBL) § In a short channel device, source-drain distance is comparable to the depletion region widths, and the drain voltage can modulate threshold § VTH = VTH 0 - ld. VDS Vds = 0. 2 V Vds = 1. 2 V Short channel Long channel Channel 0 (S) Low Power Design Essentials © 2008 L (D) 2. 16

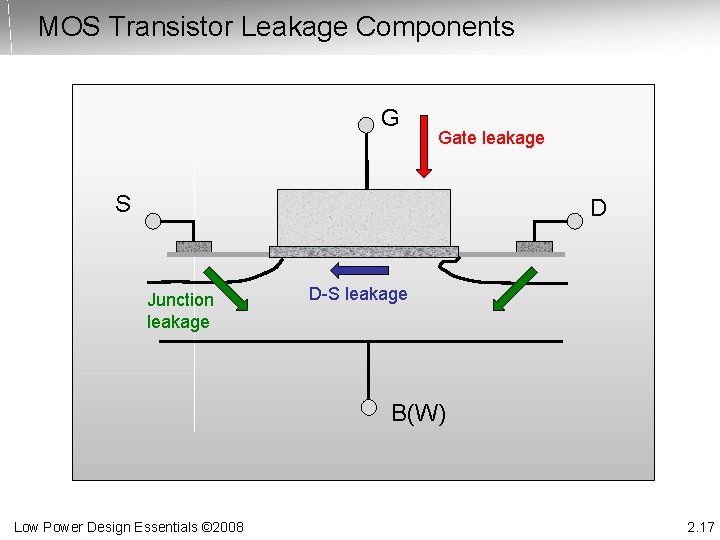

MOS Transistor Leakage Components G Gate leakage S D Junction leakage D-S leakage B(W) Low Power Design Essentials © 2008 2. 17

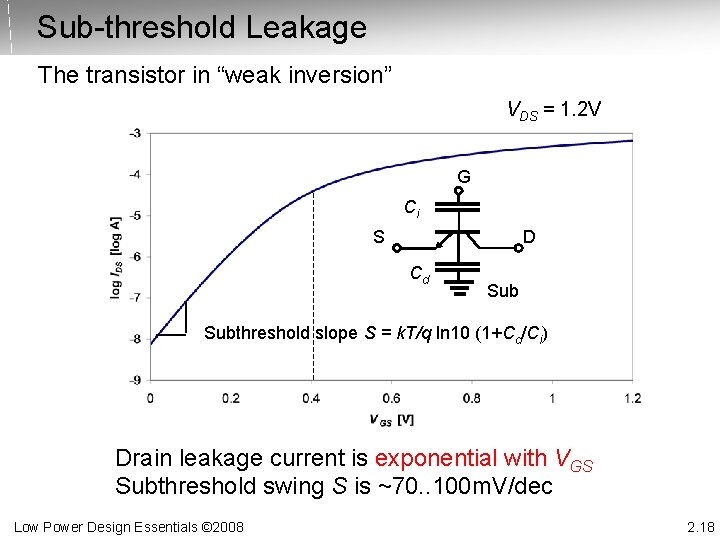

Sub-threshold Leakage The transistor in “weak inversion” VDS = 1. 2 V G Ci S D Cd Subthreshold slope S = k. T/q ln 10 (1+Cd/Ci) Drain leakage current is exponential with VGS Subthreshold swing S is ~70. . 100 m. V/dec Low Power Design Essentials © 2008 2. 18

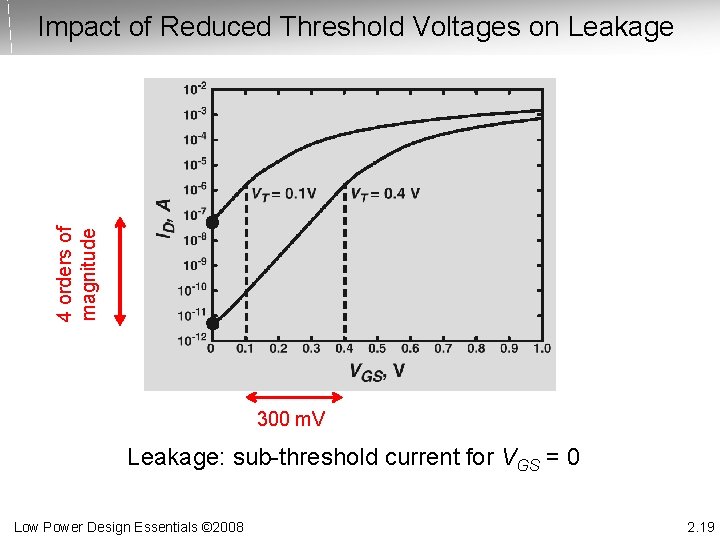

4 orders of magnitude Impact of Reduced Threshold Voltages on Leakage 300 m. V Leakage: sub-threshold current for VGS = 0 Low Power Design Essentials © 2008 2. 19

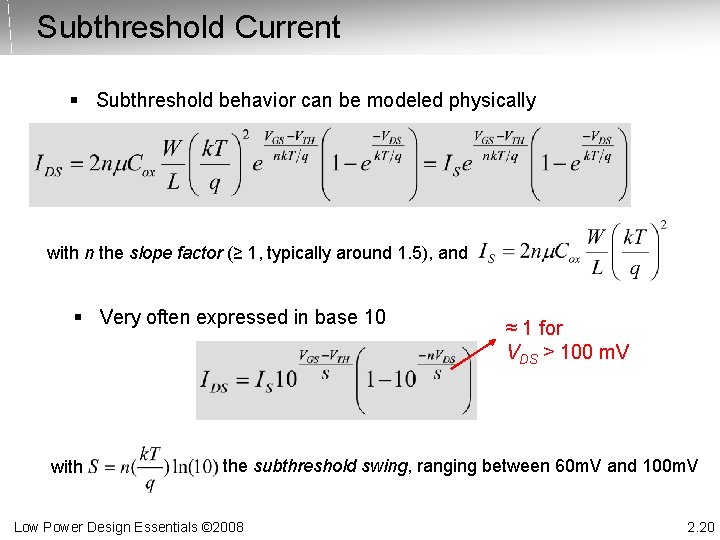

Subthreshold Current § Subthreshold behavior can be modeled physically with n the slope factor (≥ 1, typically around 1. 5), and § Very often expressed in base 10 with ≈ 1 for VDS > 100 m. V the subthreshold swing, ranging between 60 m. V and 100 m. V Low Power Design Essentials © 2008 2. 20

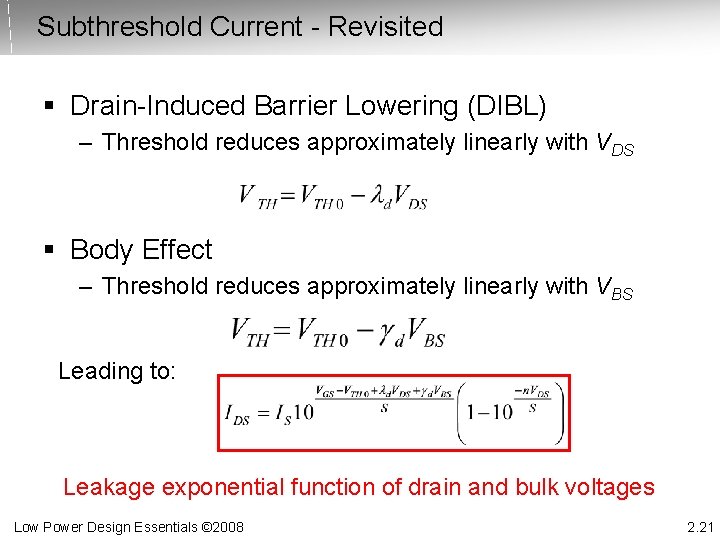

Subthreshold Current - Revisited § Drain-Induced Barrier Lowering (DIBL) – Threshold reduces approximately linearly with VDS § Body Effect – Threshold reduces approximately linearly with VBS Leading to: Leakage exponential function of drain and bulk voltages Low Power Design Essentials © 2008 2. 21

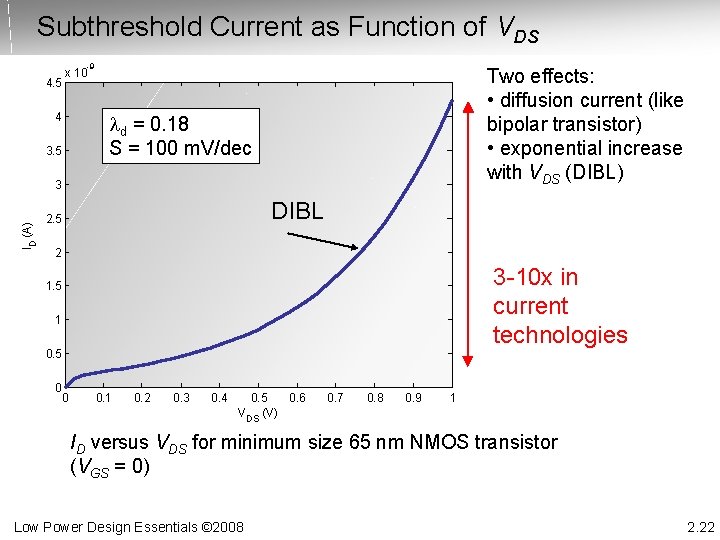

Subthreshold Current as Function of VDS -9 4. 5 Two effects: • diffusion current (like bipolar transistor) • exponential increase with VDS (DIBL) x 10 4 ld = 0. 18 S = 100 m. V/dec 3. 5 ID (A) 3 DIBL 2. 5 2 3 -10 x in current technologies 1. 5 1 0. 5 0 0 0. 1 0. 2 0. 3 0. 4 0. 5 0. 6 VDS (V) 0. 7 0. 8 0. 9 1 ID versus VDS for minimum size 65 nm NMOS transistor (VGS = 0) Low Power Design Essentials © 2008 2. 22

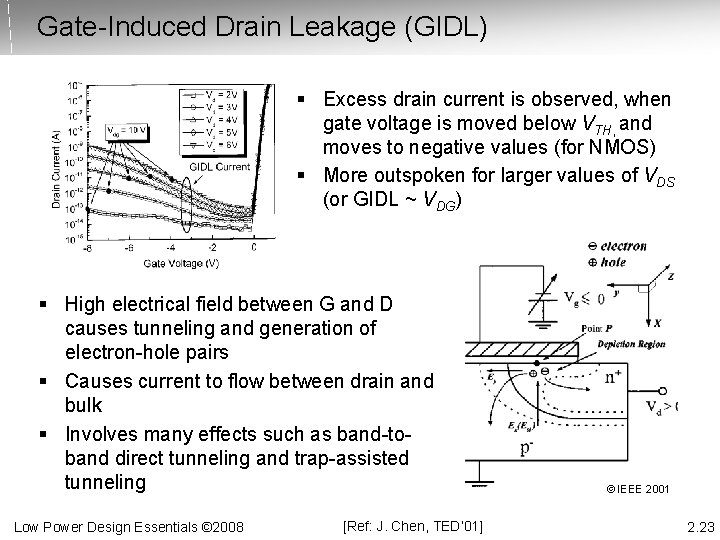

Gate-Induced Drain Leakage (GIDL) § Excess drain current is observed, when gate voltage is moved below VTH, and moves to negative values (for NMOS) § More outspoken for larger values of VDS (or GIDL ~ VDG) § High electrical field between G and D causes tunneling and generation of electron-hole pairs § Causes current to flow between drain and bulk § Involves many effects such as band-toband direct tunneling and trap-assisted tunneling Low Power Design Essentials © 2008 [Ref: J. Chen, TED’ 01] © IEEE 2001 2. 23

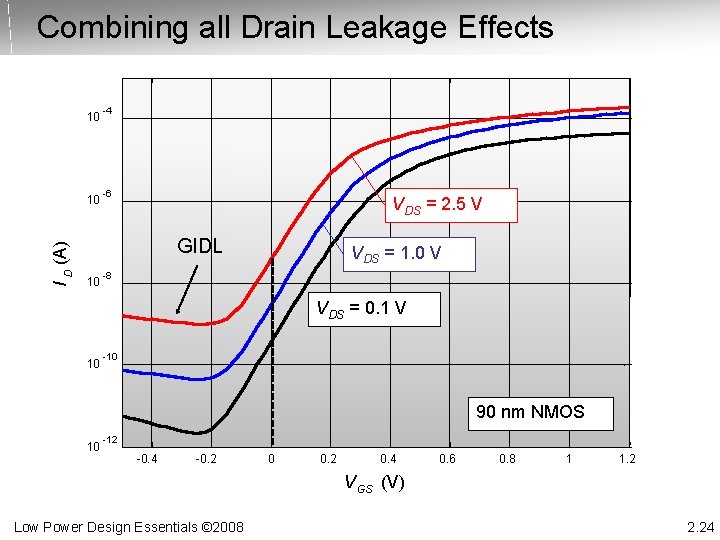

Combining all Drain Leakage Effects 10 I D (A) 10 -4 -6 VDS = 2. 5 V GIDL 10 VDS = 1. 0 V -8 VDS = 0. 1 V 10 -10 90 nm NMOS 10 -12 -0. 4 -0. 2 0. 4 0. 6 0. 8 1 1. 2 V GS (V) Low Power Design Essentials © 2008 2. 24

Gate Leakage Introduction of high-k dielectrics Gate 1. 2 nm Si. O 2 Silicon substrate Scaling leads to gate-oxide thickness of couple of molecules Causes gates to leak! MOS digital design has always been based on assumption of infinite input resistance! Hence: Fundamental impact on design strategy! Low Power Design Essentials © 2008 [Ref: K. Mistry, IEDM’ 07] 2. 25

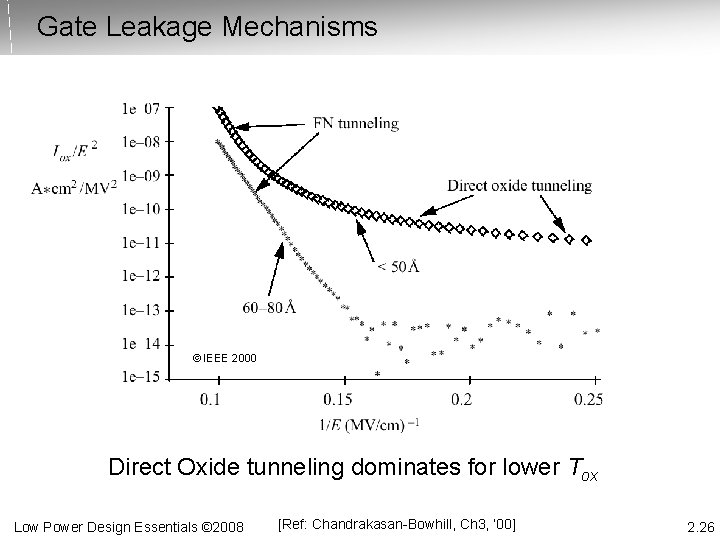

Gate Leakage Mechanisms © IEEE 2000 Direct Oxide tunneling dominates for lower Tox Low Power Design Essentials © 2008 [Ref: Chandrakasan-Bowhill, Ch 3, ‘ 00] 2. 26

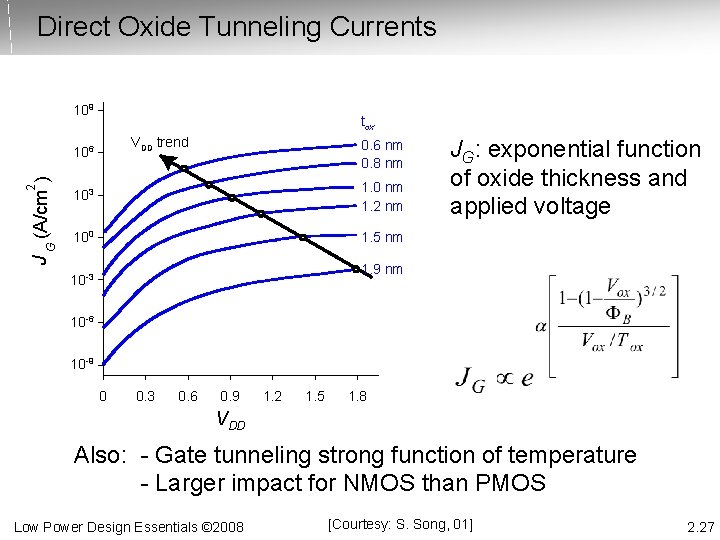

Direct Oxide Tunneling Currents 109 tox VDD trend 2 J (A/cm ) G 106 0. 6 nm 0. 8 nm 103 1. 0 nm 1. 2 nm 100 1. 5 nm JG: exponential function of oxide thickness and applied voltage 1. 9 nm 10 -3 10 -6 10 -9 0 0. 3 0. 6 0. 9 1. 2 1. 5 1. 8 VDD Also: - Gate tunneling strong function of temperature - Larger impact for NMOS than PMOS Low Power Design Essentials © 2008 [Courtesy: S. Song, 01] 2. 27

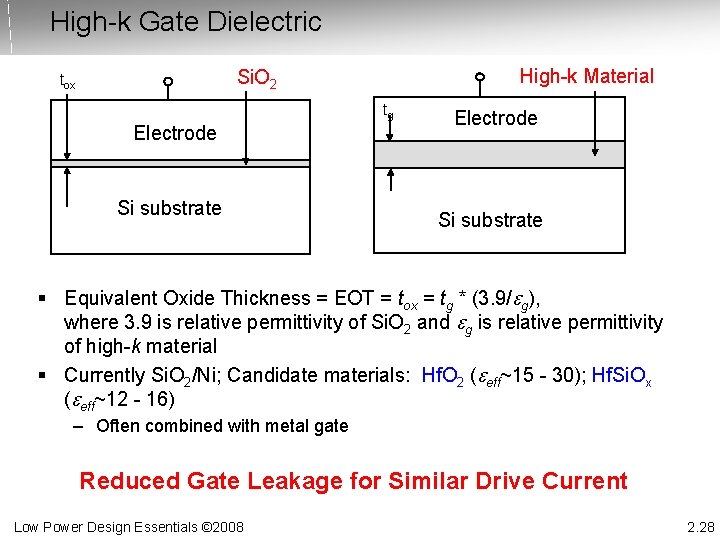

High-k Gate Dielectric High-k Material Si. O 2 tox tg Electrode Si substrate § Equivalent Oxide Thickness = EOT = tox = tg * (3. 9/eg), where 3. 9 is relative permittivity of Si. O 2 and eg is relative permittivity of high-k material § Currently Si. O 2/Ni; Candidate materials: Hf. O 2 (eeff~15 - 30); Hf. Si. Ox (eeff~12 - 16) – Often combined with metal gate Reduced Gate Leakage for Similar Drive Current Low Power Design Essentials © 2008 2. 28

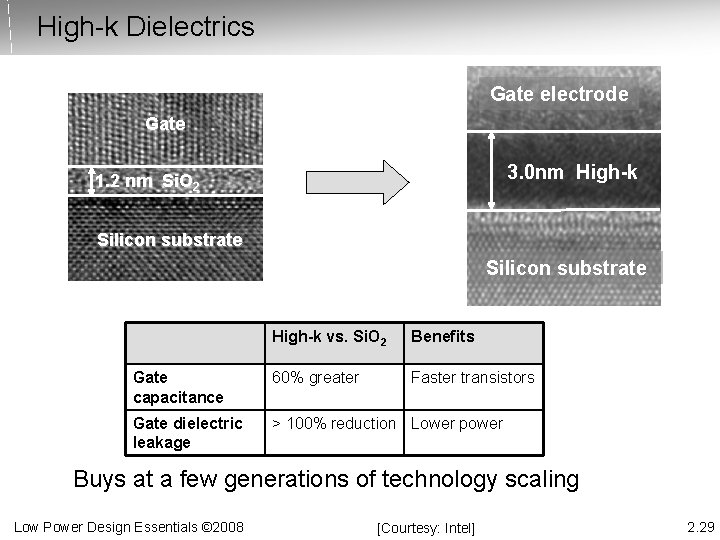

High-k Dielectrics Gate electrode Gate 3. 0 nm High-k 1. 2 nm Si. O 2 Silicon substrate High-k vs. Si. O 2 Benefits Gate capacitance 60% greater Faster transistors Gate dielectric leakage > 100% reduction Lower power Buys at a few generations of technology scaling Low Power Design Essentials © 2008 [Courtesy: Intel] 2. 29

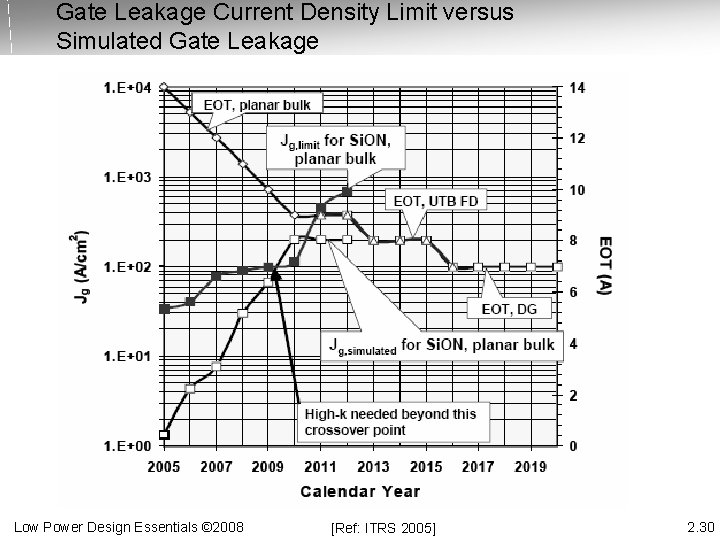

Gate Leakage Current Density Limit versus Simulated Gate Leakage Low Power Design Essentials © 2008 [Ref: ITRS 2005] 2. 30

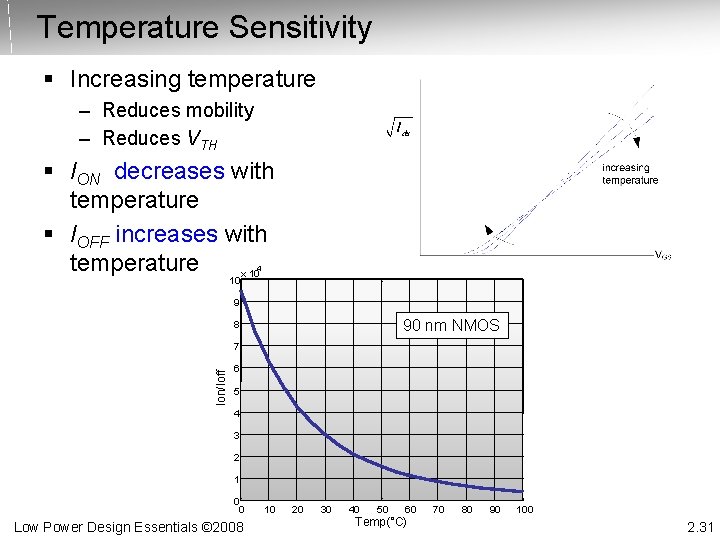

Temperature Sensitivity § Increasing temperature – Reduces mobility – Reduces VTH § ION decreases with temperature § IOFF increases with temperature x 10 4 10 9 90 nm NMOS 8 Ion/Ioff 7 6 5 4 3 2 1 0 0 Low Power Design Essentials © 2008 10 20 30 40 50 60 Temp(°C) 70 80 90 100 2. 31

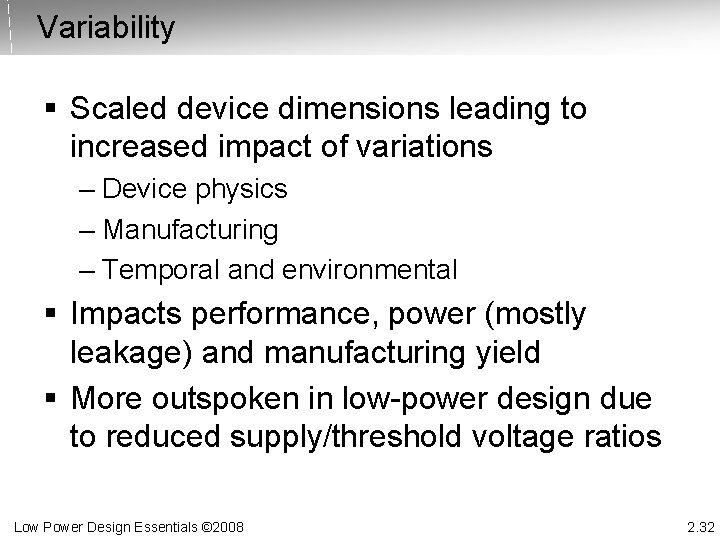

Variability § Scaled device dimensions leading to increased impact of variations – Device physics – Manufacturing – Temporal and environmental § Impacts performance, power (mostly leakage) and manufacturing yield § More outspoken in low-power design due to reduced supply/threshold voltage ratios Low Power Design Essentials © 2008 2. 32

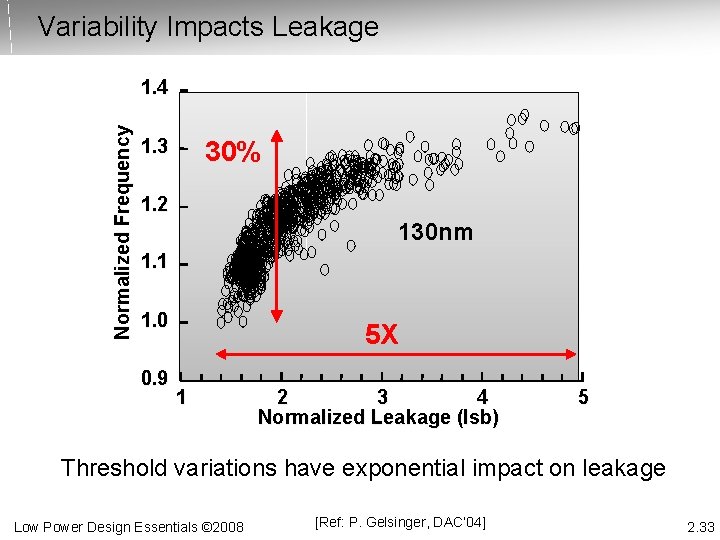

Variability Impacts Leakage Normalized Frequency 1. 4 1. 3 30% 1. 2 130 nm 1. 1 1. 0 0. 9 5 X 1 2 3 4 Normalized Leakage (Isb) 5 Threshold variations have exponential impact on leakage Low Power Design Essentials © 2008 [Ref: P. Gelsinger, DAC’ 04] 2. 33

Variability Sources § Physical – Changes in characteristics of devices and wires. – Caused by IC manufacturing process, device physics & wear-out (electro-migration). – Time scale: 109 sec (years). § Environmental – Changes in operational conditions (modes), VDD, temperature, local coupling. – Caused by the specifics of the design implementation. – Time scale: 10− 6 to 10− 9 sec (clock tick). Low Power Design Essentials © 2008 2. 34

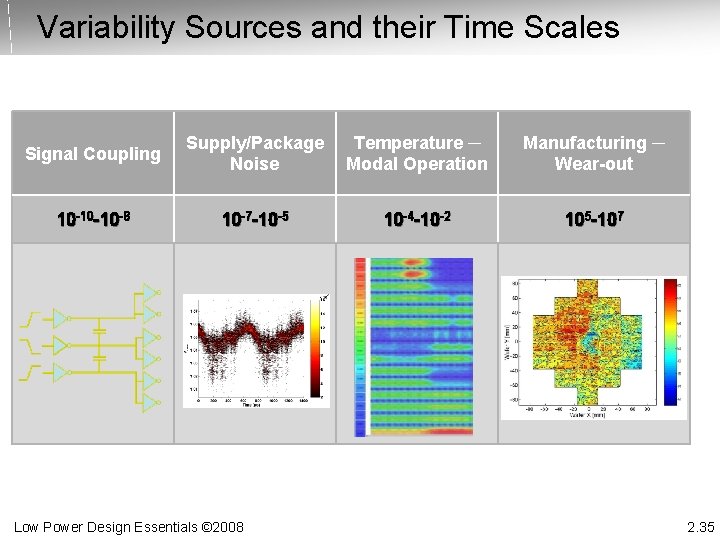

Variability Sources and their Time Scales Signal Coupling Supply/Package Noise Temperature ─ Modal Operation Manufacturing ─ Wear-out 10 -10 -10 -8 10 -7 -10 -5 10 -4 -10 -2 105 -107 Low Power Design Essentials © 2008 2. 35

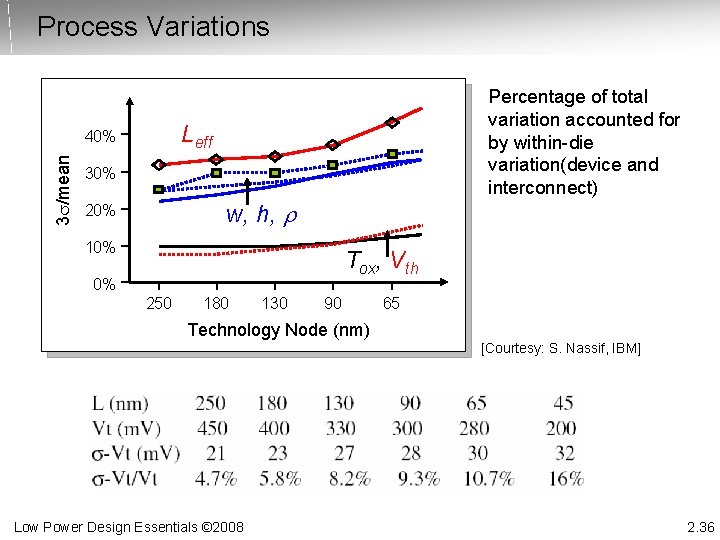

Process Variations Leff 40% 3 /mean Percentage of total variation accounted for by within-die variation(device and interconnect) 30% w, h, 20% 10% Tox, Vth 0% 250 180 130 90 65 Technology Node (nm) [Courtesy: S. Nassif, IBM] Low Power Design Essentials © 2008 2. 36

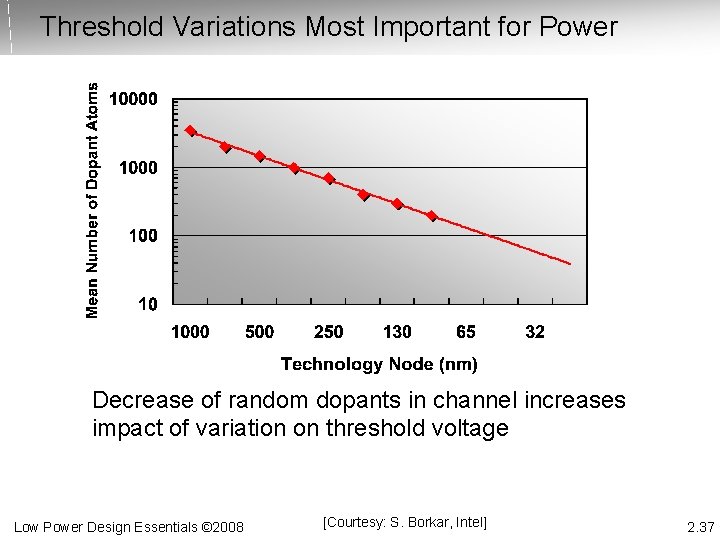

Threshold Variations Most Important for Power Decrease of random dopants in channel increases impact of variation on threshold voltage Low Power Design Essentials © 2008 [Courtesy: S. Borkar, Intel] 2. 37

Device and Technology Innovations § Power challenges introduced by nanometer MOS transistors can be partially addressed by new device structures and better materials – Higher mobility – Reduced leakage – Better control § However … – Most of these techniques provide only a one (two) technology generation boost – Need to accompanied by circuit and system level methodologies Low Power Design Essentials © 2008 2. 38

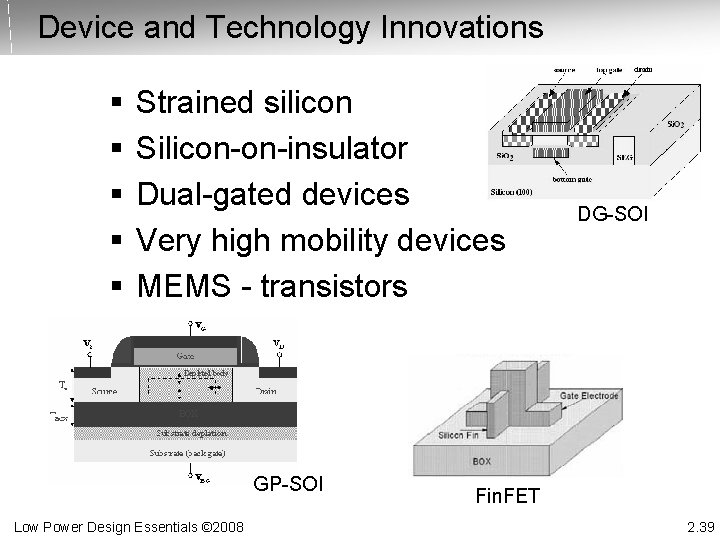

Device and Technology Innovations § § § Strained silicon Silicon-on-insulator Dual-gated devices Very high mobility devices MEMS - transistors GP-SOI Low Power Design Essentials © 2008 DG-SOI Fin. FET 2. 39

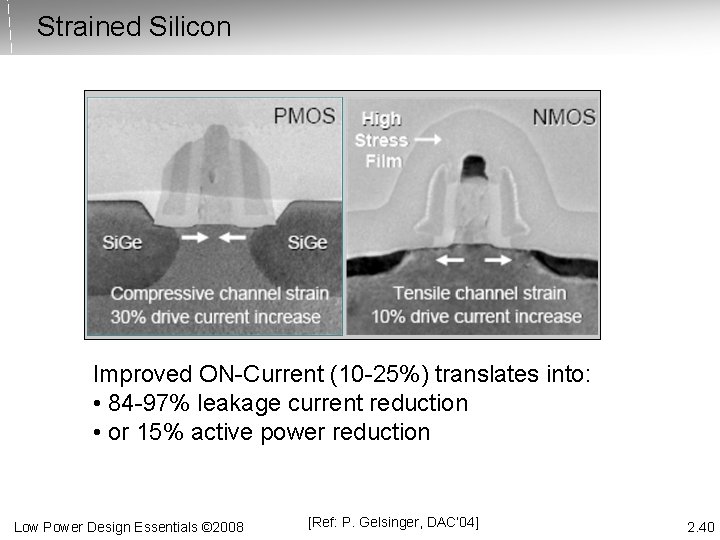

Strained Silicon Improved ON-Current (10 -25%) translates into: • 84 -97% leakage current reduction • or 15% active power reduction Low Power Design Essentials © 2008 [Ref: P. Gelsinger, DAC’ 04] 2. 40

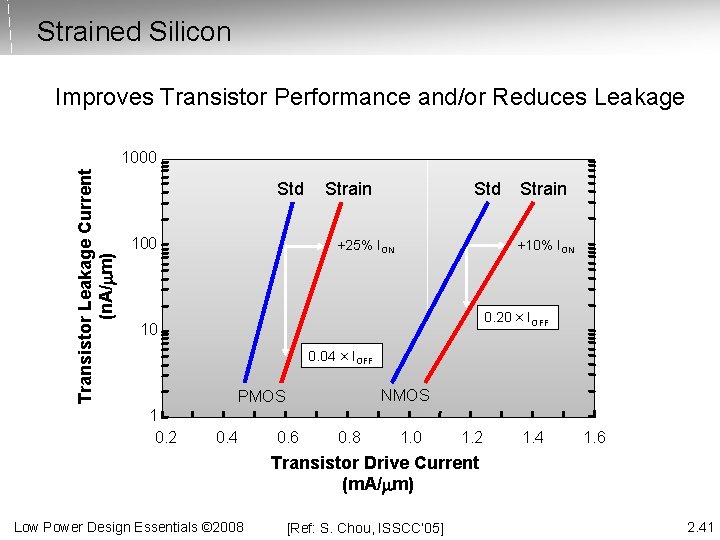

Strained Silicon Improves Transistor Performance and/or Reduces Leakage Transistor Leakage Current (n. A/mm) 1000 Std 100 Strain Std +25% ION Strain +10% ION 0. 20 × IOFF 10 0. 04 × IOFF NMOS PMOS 1 0. 2 0. 4 0. 6 0. 8 1. 0 1. 2 1. 4 1. 6 Transistor Drive Current (m. A/mm) Low Power Design Essentials © 2008 [Ref: S. Chou, ISSCC’ 05] 2. 41

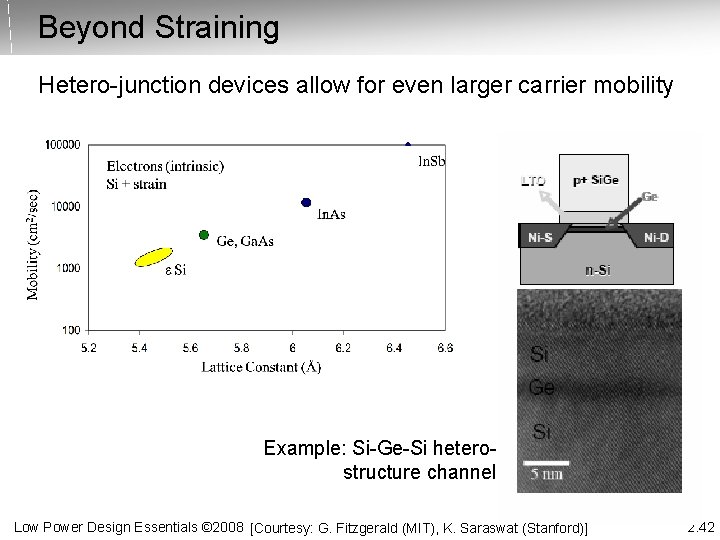

Beyond Straining Hetero-junction devices allow for even larger carrier mobility Example: Si-Ge-Si heterostructure channel Low Power Design Essentials © 2008 [Courtesy: G. Fitzgerald (MIT), K. Saraswat (Stanford)] 2. 42

![Silicon-on-Insulator (SOI) [Courtesy: IBM] G Thin silicon layer S D FD Thin Oxide Substrate Silicon-on-Insulator (SOI) [Courtesy: IBM] G Thin silicon layer S D FD Thin Oxide Substrate](http://slidetodoc.com/presentation_image/0369e1185f4abe2e7936fe0c81c6d07d/image-43.jpg)

Silicon-on-Insulator (SOI) [Courtesy: IBM] G Thin silicon layer S D FD Thin Oxide Substrate § Reduced capacitance (source and drain to bulk) results in lower dynamic power § Faster sub-threshold roll-off (close to 60 m. V/decade) § Random threshold fluctuations eliminated in fully depleted SOI § Reduced impact of soft-errors § But – More expensive – Secondary effects Low Power Design Essentials © 2008 2. 43

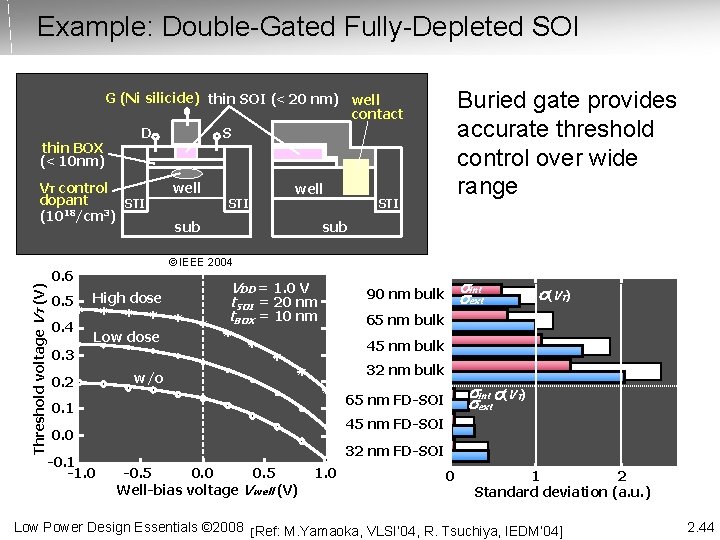

Example: Double-Gated Fully-Depleted SOI thin BOX (< 10 nm) Threshold voltage VT (V) VT control dopant STI (1018/cm 3) 0. 4 well STI well sub STI sub © IEEE 2004 0. 6 0. 5 Buried gate provides accurate threshold control over wide range G (Ni silicide) thin SOI (< 20 nm) well contact D S High dose VDD = 1. 0 V t. SOI = 20 nm t. BOX = 10 nm Low dose 65 nm bulk 32 nm bulk w/o int (VT) ext 65 nm FD-SOI 0. 1 45 nm FD-SOI 0. 0 -0. 1 -1. 0 ( V T ) 45 nm bulk 0. 3 0. 2 int ext 90 nm bulk 32 nm FD-SOI -0. 5 0. 0 0. 5 Well-bias voltage Vwell (V) 1. 0 0 2 1 Standard deviation (a. u. ) Low Power Design Essentials © 2008 [Ref: M. Yamaoka, VLSI’ 04, R. Tsuchiya, IEDM’ 04] 2. 44

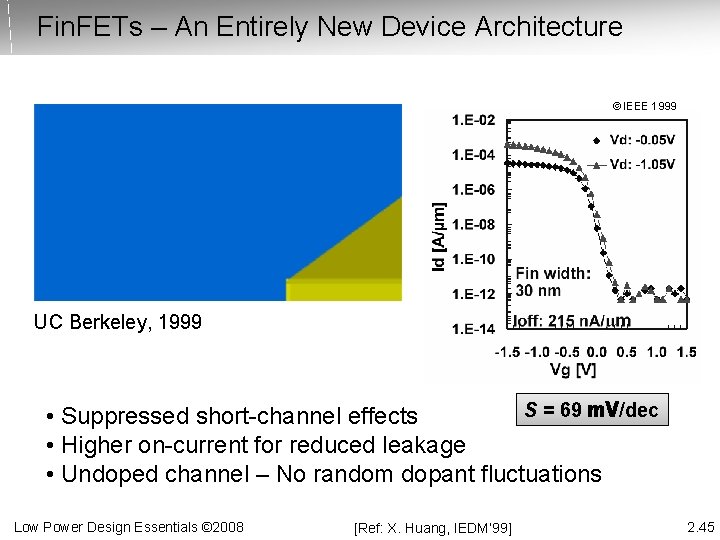

Fin. FETs – An Entirely New Device Architecture © IEEE 1999 UC Berkeley, 1999 S = 69 m. V/dec • Suppressed short-channel effects • Higher on-current for reduced leakage • Undoped channel – No random dopant fluctuations Low Power Design Essentials © 2008 [Ref: X. Huang, IEDM’ 99] 2. 45

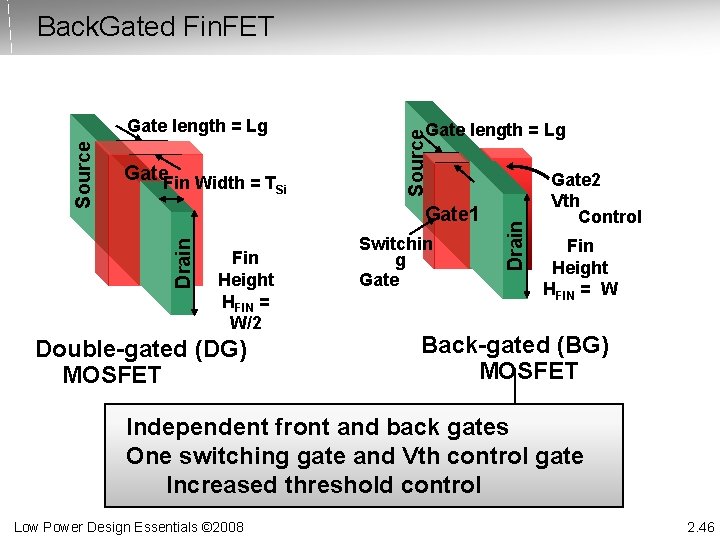

Back. Gated Fin. FET Gate length = Lg Gate 1 Fin Height HFIN = W/2 Double-gated (DG) MOSFET Switchin g Gate Drain Si Source Gate. Fin Width = T Drain Source Gate length = Lg Gate 2 Vth Control Fin Height HFIN = W Back-gated (BG) MOSFET Independent front and back gates One switching gate and Vth control gate Increased threshold control Low Power Design Essentials © 2008 2. 46

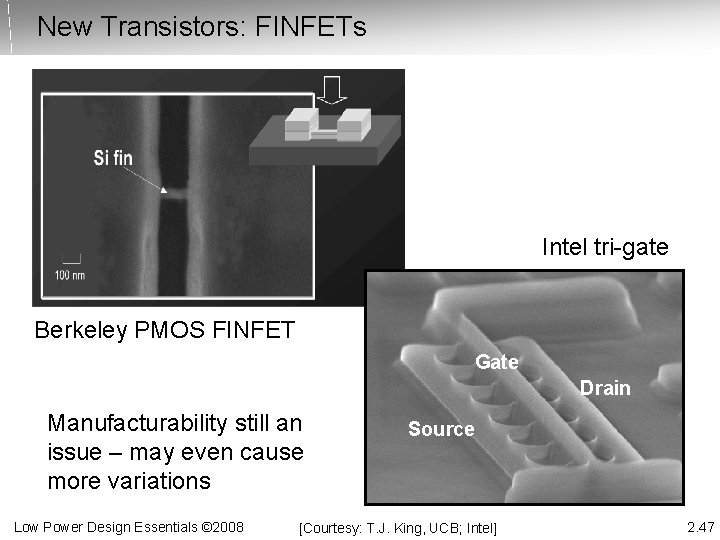

New Transistors: FINFETs Intel tri-gate Berkeley PMOS FINFET Gate Drain Manufacturability still an issue – may even cause more variations Low Power Design Essentials © 2008 Source [Courtesy: T. J. King, UCB; Intel] 2. 47

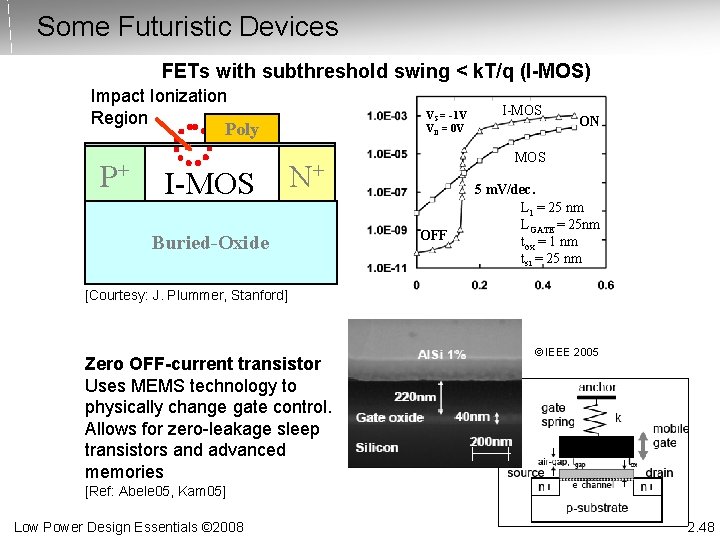

Some Futuristic Devices FETs with subthreshold swing < k. T/q (I-MOS) Impact Ionization Region Poly P+ I-MOS VS = -1 V VD = 0 V ON MOS N+ Buried-Oxide I-MOS OFF 5 m. V/dec. LI = 25 nm LGATE = 25 nm tox = 1 nm tsi = 25 nm [Courtesy: J. Plummer, Stanford] Zero OFF-current transistor Uses MEMS technology to physically change gate control. Allows for zero-leakage sleep transistors and advanced memories © IEEE 2005 [Ref: Abele 05, Kam 05] Low Power Design Essentials © 2008 2. 48

Summary § Plenty of opportunity for scaling in the nanometer age § Deep-submicron behavior of MOS transistors has substantial impact on design § Power dissipation mostly impacted by increased leakage (SD and gate) and increasing impact of process variations § Novel devices and materials will ensure scaling to a few nanometers Low Power Design Essentials © 2008 2. 49

References Books and Book Chapters § A. Chandrakasan, W. Bowhill, F. Fox (eds. ), “Design of High-Performance Microprocessor Circuits”, IEEE Press 2001. § J. Rabaey, A. Chandrakasan, B. Nikolic, “Digital Integrated Circuits: A Design Perspective, ” 2 nd ed, Prentice Hall 2003. § Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices, Cambridge University Press, 1998. Articles § Abele, N. ; Fritschi, R. ; Boucart, K. ; Casset, F. ; Ancey, P. ; Ionescu, A. M. , “Suspended-gate MOSFET: bringing new MEMS § § § § functionality into solid-state MOS transistor, ” Proc. Electron Devices Meeting, 2005. IEDM Technical Digest. IEEE International, pp 479 -481, Dec. 2005 BSIM 3 V 3 User Manual, http: //www. eecs. berkeley. edu/Pubs/Tech. Rpts/1998/3486. html J. H. Chen et al, “An Analytic Three-Terminal Band-to-Band Tunneling Model on GIDL in MOSFET, ” IEEE Trans. On Electron Devices, Vol. 48 No 7, pp. 1400 -1405, July 2001. S. Chou, “Innovation and Integration in the Nanoelectronics Era, ” Digest ISSCC 2005, pp. 36 -38, February 2005. P. Gelsinger, “Giga-scale Integration for Tera-Ops Performance, ” 41 st DAC Keynote, DAC, 2004, (www. dac. com) X. Huang et al (1999) "Sub 50 -nm Fin. FET: PMOS“, International Electron Devices Meeting Technical Digest, p. 67. December 5 -8, 1999. International Technology Roadmap for Semiconductors, http: //www. itrs. net/ H. Kam et al. , “A new nano-electro-mechanical field effect transistor (NEMFET) design for low-power electronics, “ IEDM Tech. Digest, pp. 463 - 466, Dec. 2005. K. Mistry et al, “A 45 nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193 nm Dry Patterning, and 100% Pb-free Packaging. Proceedings, ” IEDM, pp. 247, Washington, Dec. 2007. Predictive Technology Model (PTM), http: //www. eas. asu. edu/~ptm/ T. Sakurai and R. Newton. “Alpha-power law mosfet model and its applications to cmos inverter delay and other formulas. , ” IEEE Journal of Solid-State Circuits, 25(2), 1990. R. Tsuchiya et al, “Silicon on thin BOX: a new paradigm of the CMOSFET for low-power high- performance application featuring wide-range back-bias control, ” Proceedings IEDM 2004, pp. 631 -634, Dec. 2004. M. Yamaoka et al, “Low power SRAM menu for SOC application using Yin-Yang-feedback memory cell technology, ” Digest of Technical Papers VLSI Symposium, pp. 288 -291, June 2004. W. Zhao, Y. Cao, “New generation of predictive technology model for sub-45 nm early design exploration, ” IEEE Transactions on Electron Devices, vol. 53, no. 11, pp. 2816 -2823, November 2006 Low Power Design Essentials © 2008 2. 50

- Slides: 50