NA 62 M Sozzi Presentazione preventivi INFN Pisa

- Slides: 35

NA 62 M. Sozzi Presentazione preventivi INFN Pisa – Luglio 2013 MS - NA 62 – Luglio 2013

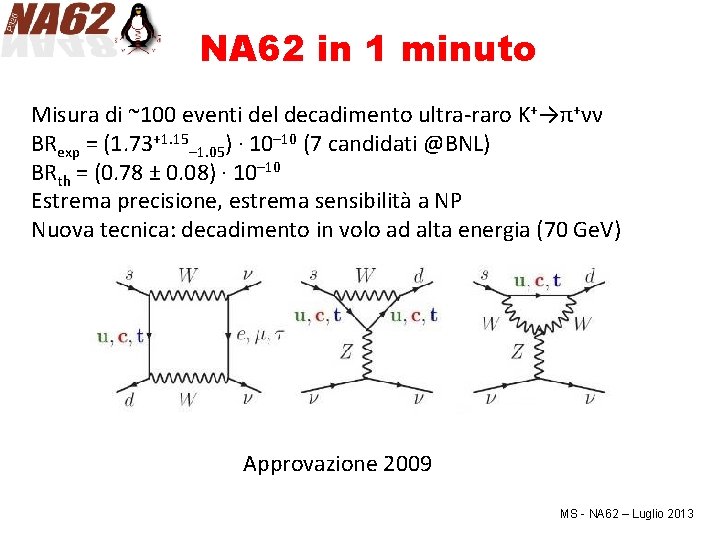

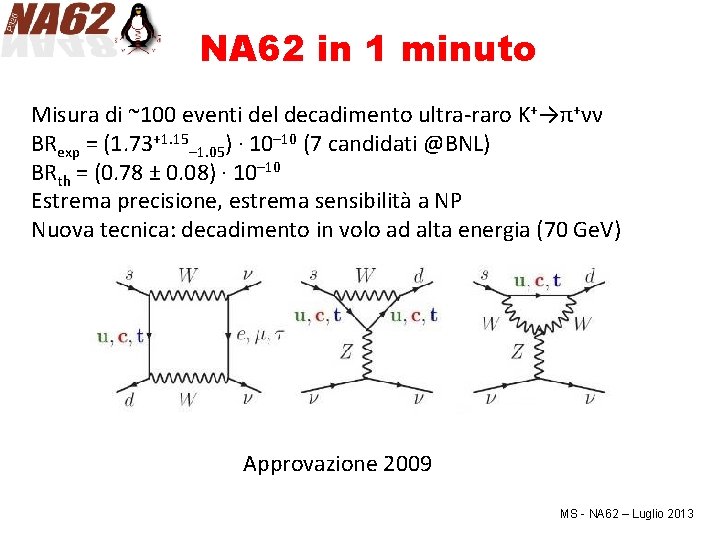

NA 62 in 1 minuto Misura di ~100 eventi del decadimento ultra-raro K+→π+νν BRexp = (1. 73+1. 15– 1. 05) · 10– 10 (7 candidati @BNL) BRth = (0. 78 ± 0. 08) · 10– 10 Estrema precisione, estrema sensibilità a NP Nuova tecnica: decadimento in volo ad alta energia (70 Ge. V) Approvazione 2009 MS - NA 62 – Luglio 2013

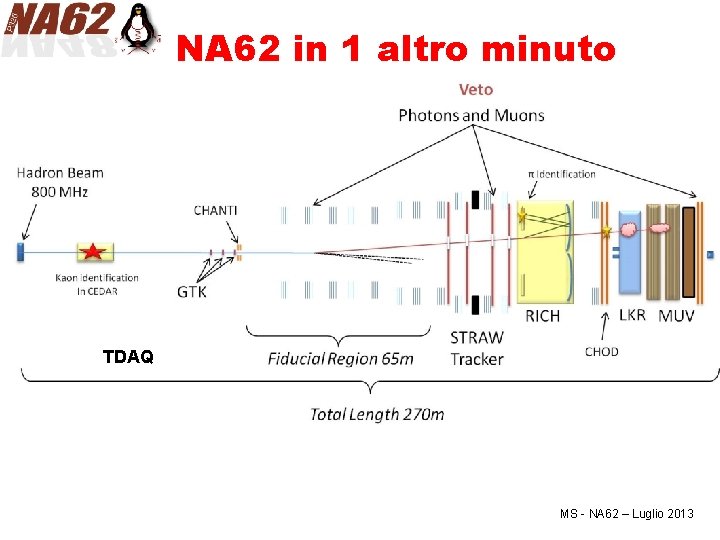

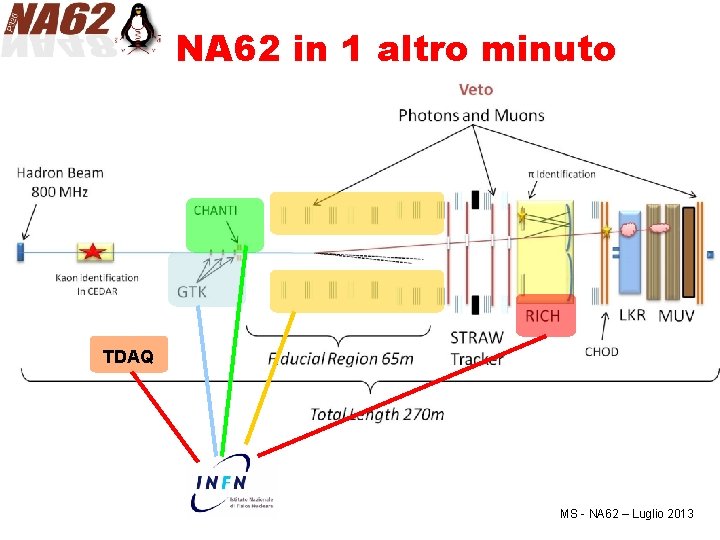

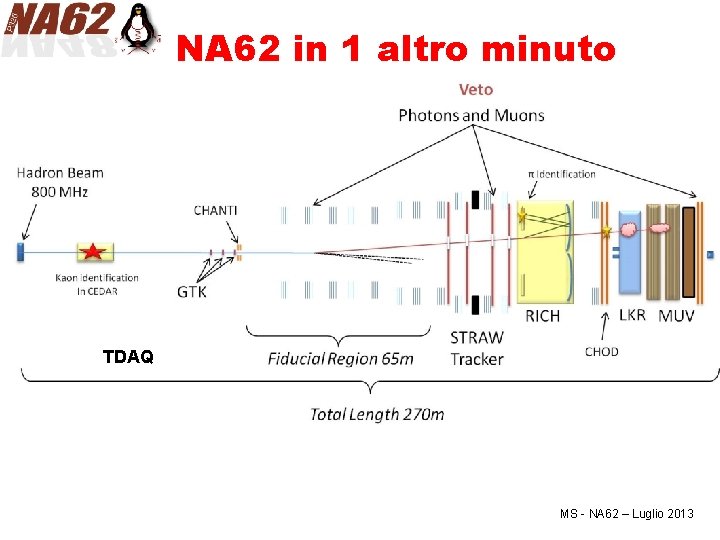

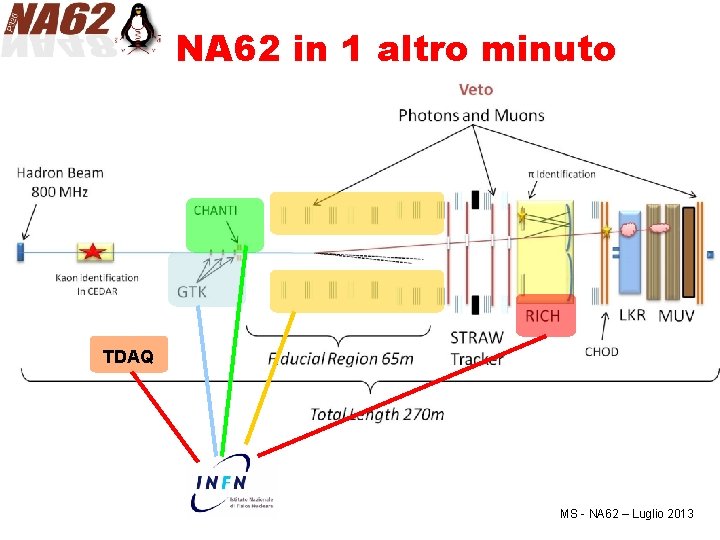

NA 62 in 1 altro minuto TDAQ MS - NA 62 – Luglio 2013

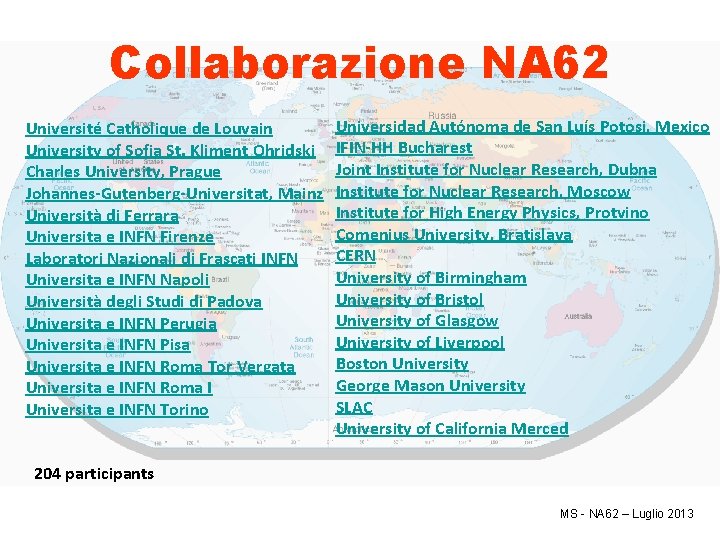

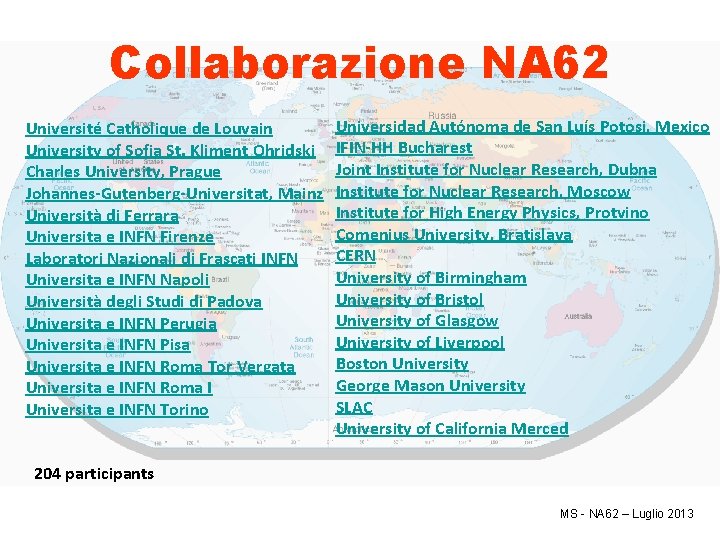

Collaborazione NA 62 Université Catholique de Louvain University of Sofia St. Kliment Ohridski Charles University, Prague Johannes-Gutenberg-Universitat, Mainz Università di Ferrara Universita e INFN Firenze Laboratori Nazionali di Frascati INFN Universita e INFN Napoli Università degli Studi di Padova Universita e INFN Perugia Universita e INFN Pisa Universita e INFN Roma Tor Vergata Universita e INFN Roma I Universita e INFN Torino Universidad Autónoma de San Luís Potosi, Mexico IFIN-HH Bucharest Joint Institute for Nuclear Research, Dubna Institute for Nuclear Research, Moscow Institute for High Energy Physics, Protvino Comenius University, Bratislava CERN University of Birmingham University of Bristol University of Glasgow University of Liverpool Boston University George Mason University SLAC University of California Merced 204 participants MS - NA 62 – Luglio 2013

Nuovo beam dump MS - NA 62 – Luglio 2013

Sala ECN 3 Fascio disponibile a ottobre 2012 MS - NA 62 – Luglio 2013

MS - NA 62 – Luglio 2013

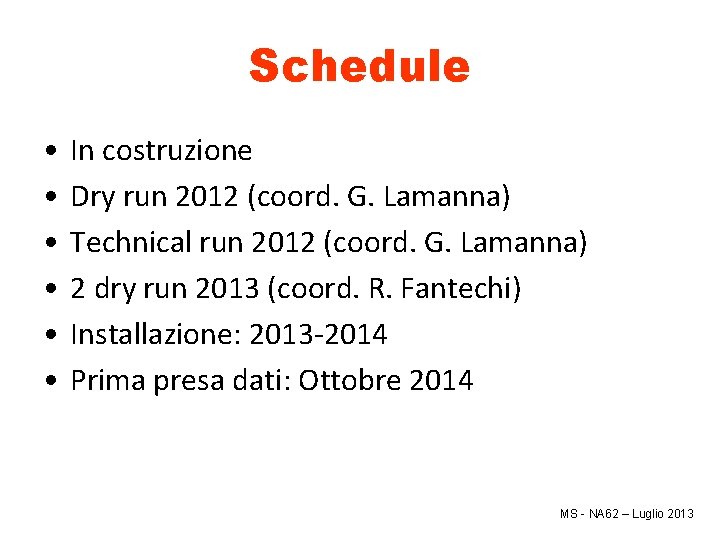

Schedule • • • In costruzione Dry run 2012 (coord. G. Lamanna) Technical run 2012 (coord. G. Lamanna) 2 dry run 2013 (coord. R. Fantechi) Installazione: 2013 -2014 Prima presa dati: Ottobre 2014 MS - NA 62 – Luglio 2013

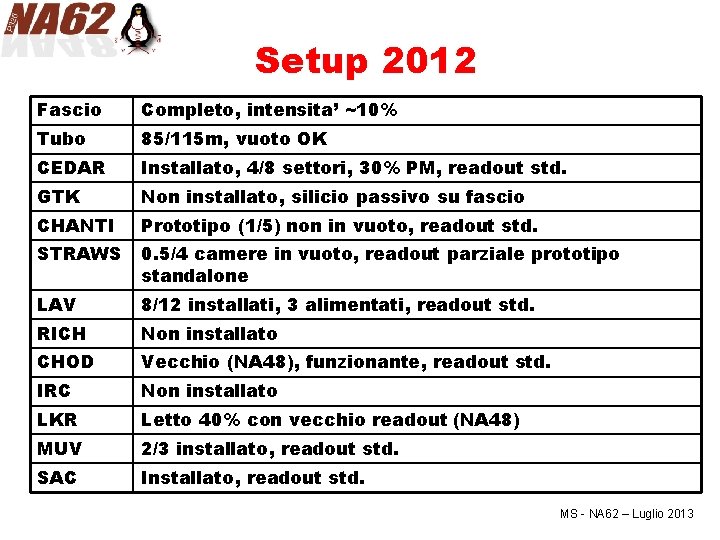

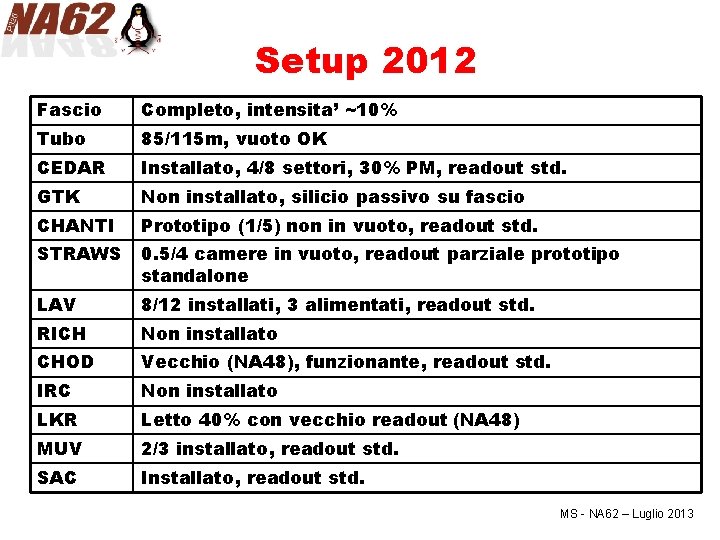

Setup 2012 Fascio Completo, intensita’ ~10% Tubo 85/115 m, vuoto OK CEDAR Installato, 4/8 settori, 30% PM, readout std. GTK Non installato, silicio passivo su fascio CHANTI Prototipo (1/5) non in vuoto, readout std. STRAWS 0. 5/4 camere in vuoto, readout parziale prototipo standalone LAV 8/12 installati, 3 alimentati, readout std. RICH Non installato CHOD Vecchio (NA 48), funzionante, readout std. IRC Non installato LKR Letto 40% con vecchio readout (NA 48) MUV 2/3 installato, readout std. SAC Installato, readout std. MS - NA 62 – Luglio 2013

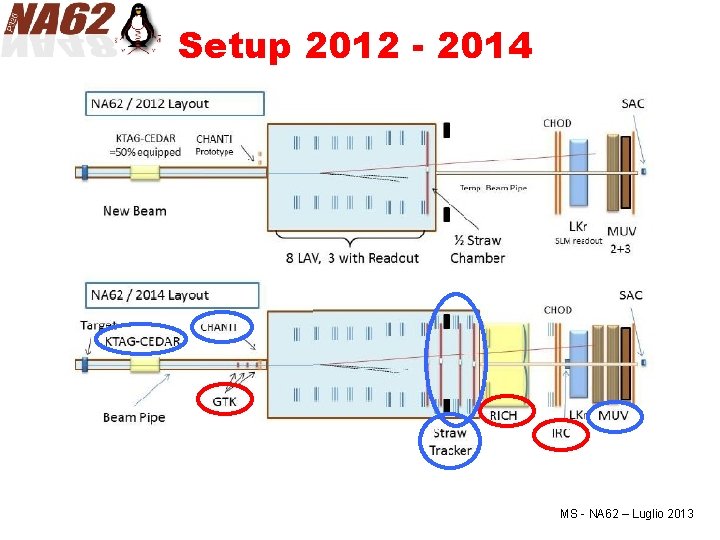

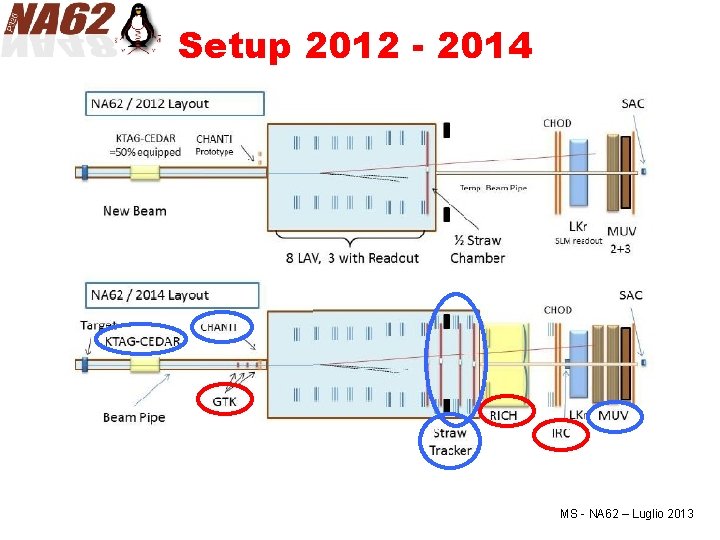

Setup 2012 - 2014 MS - NA 62 – Luglio 2013

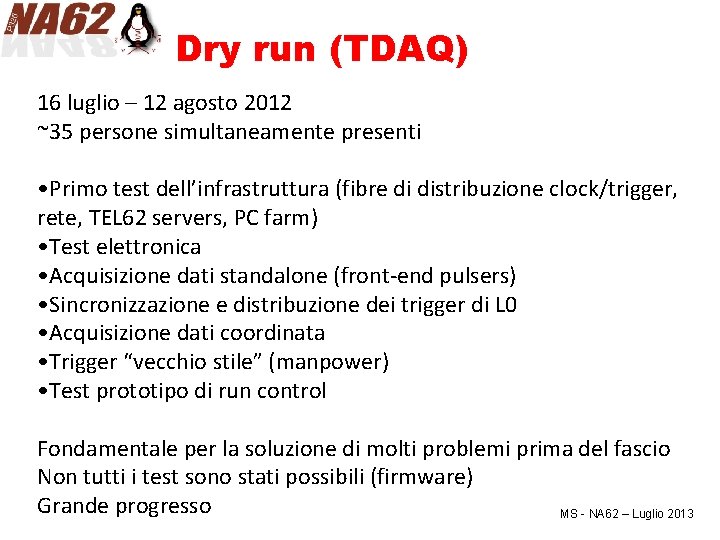

Dry run (TDAQ) 16 luglio – 12 agosto 2012 ~35 persone simultaneamente presenti • Primo test dell’infrastruttura (fibre di distribuzione clock/trigger, rete, TEL 62 servers, PC farm) • Test elettronica • Acquisizione dati standalone (front-end pulsers) • Sincronizzazione e distribuzione dei trigger di L 0 • Acquisizione dati coordinata • Trigger “vecchio stile” (manpower) • Test prototipo di run control Fondamentale per la soluzione di molti problemi prima del fascio Non tutti i test sono stati possibili (firmware) Grande progresso MS - NA 62 – Luglio 2013

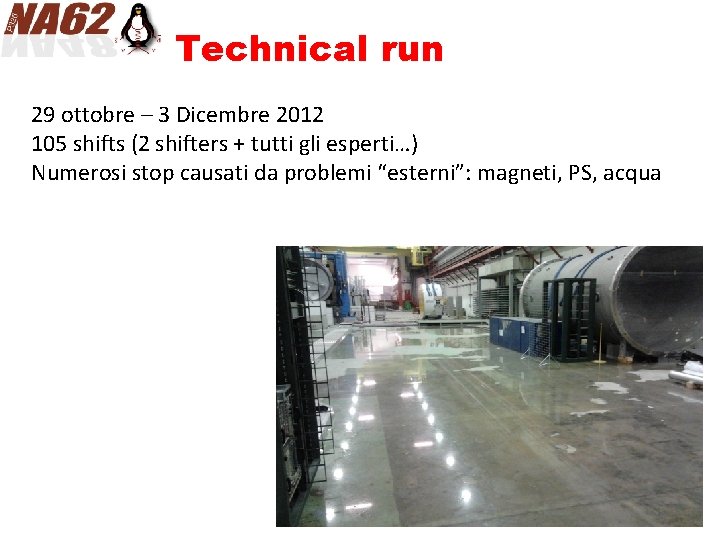

Technical run 29 ottobre – 3 Dicembre 2012 105 shifts (2 shifters + tutti gli esperti…) Numerosi stop causati da problemi “esterni”: magneti, PS, acqua MS - NA 62 – Luglio 2013

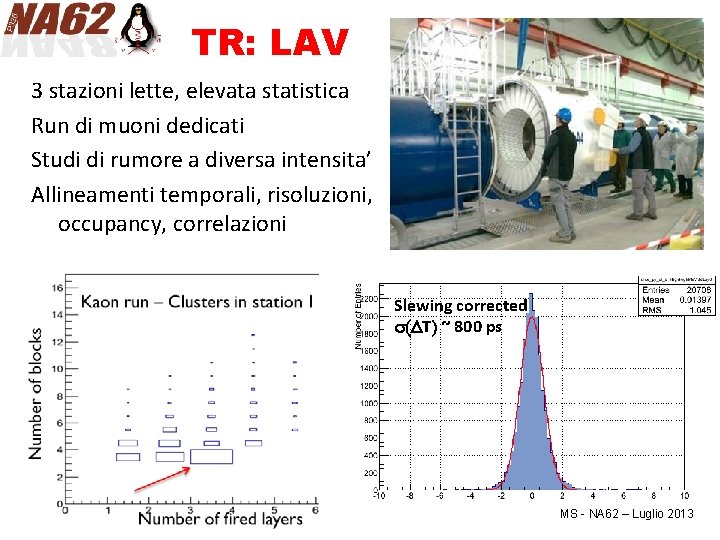

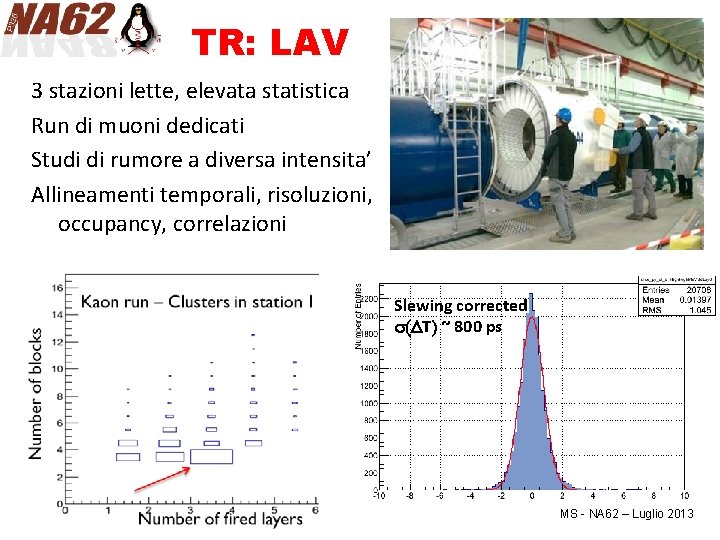

TR: LAV 3 stazioni lette, elevata statistica Run di muoni dedicati Studi di rumore a diversa intensita’ Allineamenti temporali, risoluzioni, occupancy, correlazioni Slewing corrected s(DT) ~ 800 ps MS - NA 62 – Luglio 2013

TR: TDAQ Test… Crates Network issues TTCex phase stability Firmware loading Not yet radiation tests Noise in TDCs tested Trigger synchronization and counting Clock/trigger phase synchronization Data transfer to farm Standalone trigger generation/distribution Trigger synchronization, data extraction from memories Long runs, rate tests… MS - NA 62 – Luglio 2013

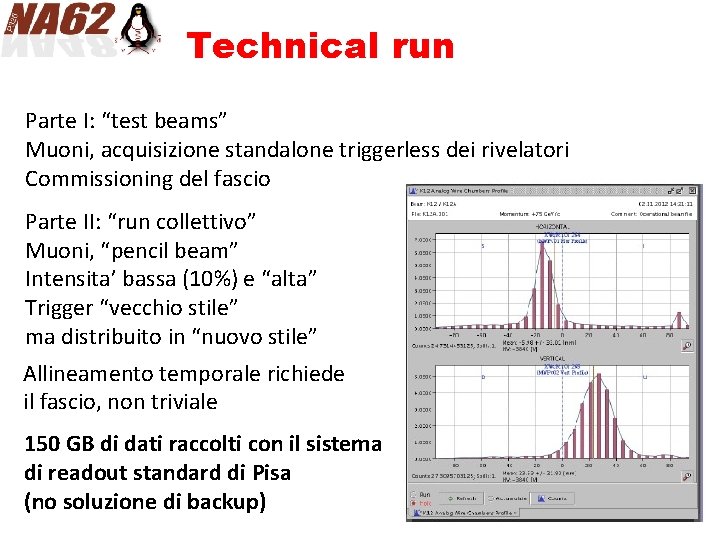

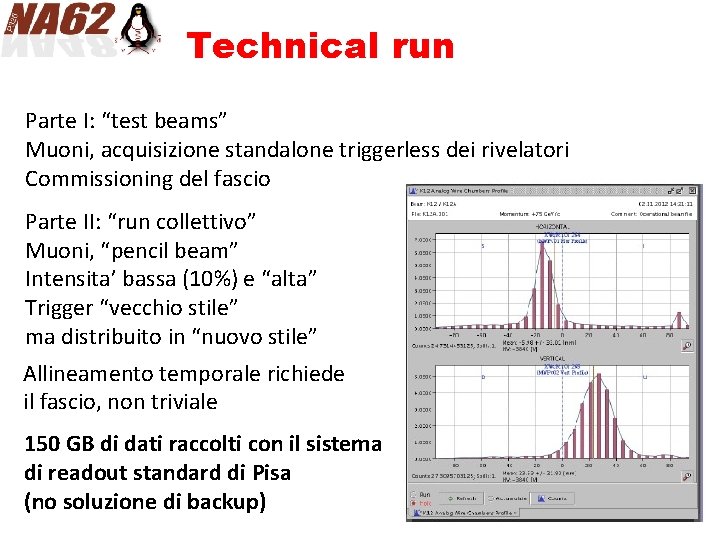

Technical run Parte I: “test beams” Muoni, acquisizione standalone triggerless dei rivelatori Commissioning del fascio Parte II: “run collettivo” Muoni, “pencil beam” Intensita’ bassa (10%) e “alta” Trigger “vecchio stile” ma distribuito in “nuovo stile” Allineamento temporale richiede il fascio, non triviale 150 GB di dati raccolti con il sistema di readout standard di Pisa (no soluzione di backup) MS - NA 62 – Luglio 2013

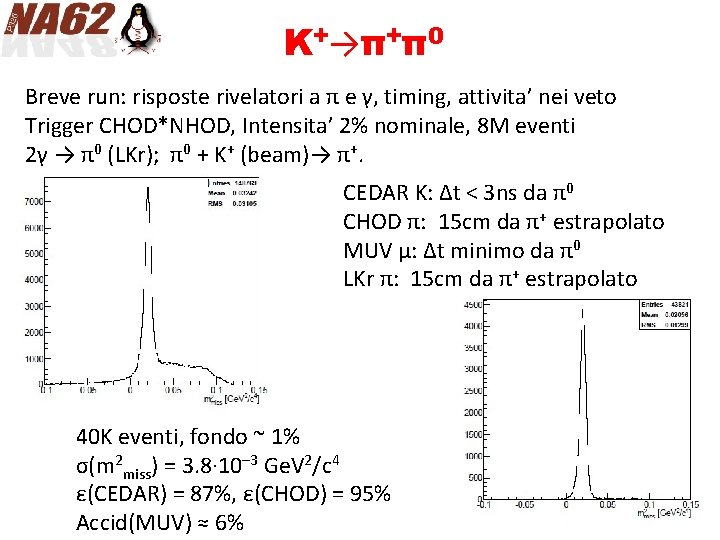

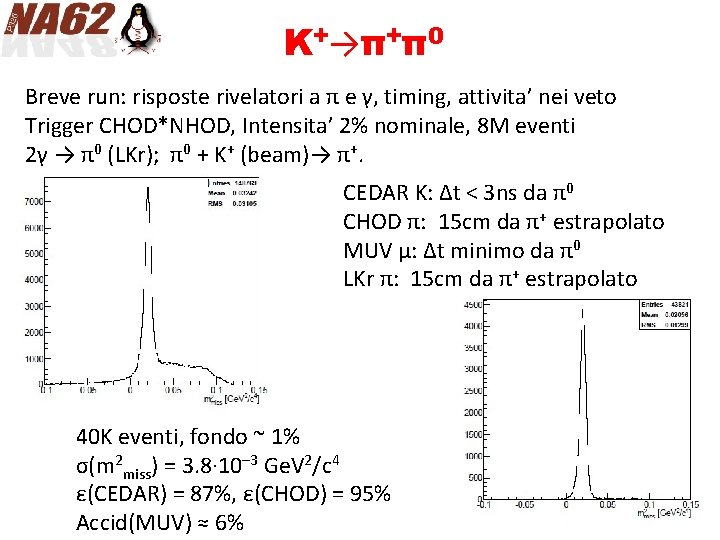

K+→π+π0 Breve run: risposte rivelatori a π e γ, timing, attivita’ nei veto Trigger CHOD*NHOD, Intensita’ 2% nominale, 8 M eventi 2γ → π0 (LKr); π0 + K+ (beam)→ π+. CEDAR K: Δt < 3 ns da π0 CHOD π: 15 cm da π+ estrapolato MUV μ: Δt minimo da π0 LKr π: 15 cm da π+ estrapolato 40 K eventi, fondo ~ 1% σ(m 2 miss) = 3. 8· 10– 3 Ge. V 2/c 4 ε(CEDAR) = 87%, ε(CHOD) = 95% Accid(MUV) ≈ 6% MS - NA 62 – Luglio 2013

NA 62 Italia Ferrara (GTK, L 0 TP) Firenze (RICH) LNF (LAV) Napoli (LAV) Perugia (elettronica RICH, vecchio CHOD) Pisa (TDAQ, LAV) – Leader WG TDAQ, RN Roma I (Computing) Roma II (trigger calorimetro) Torino (GTK, L 0 TP) MS - NA 62 – Luglio 2013

NA 62 in 1 altro minuto TDAQ MS - NA 62 – Luglio 2013

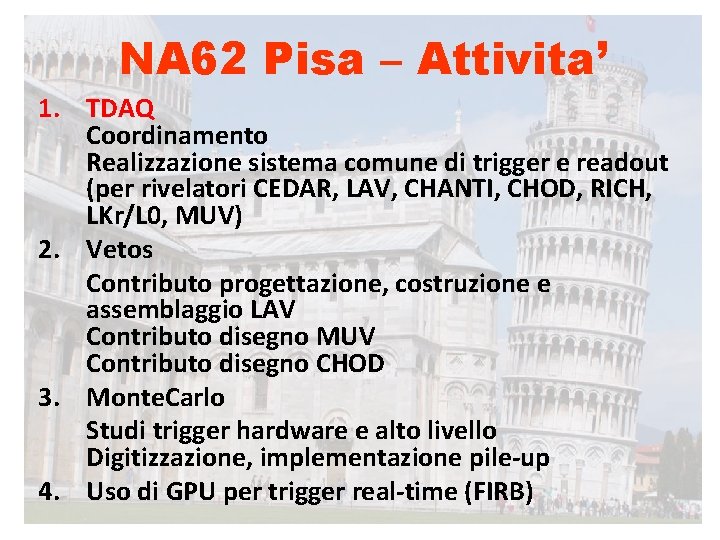

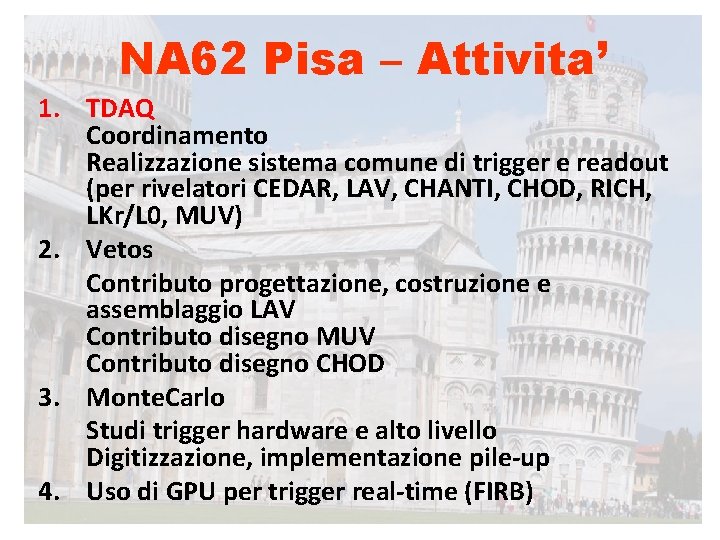

NA 62 Pisa – Attivita’ 1. TDAQ Coordinamento Realizzazione sistema comune di trigger e readout (per rivelatori CEDAR, LAV, CHANTI, CHOD, RICH, LKr/L 0, MUV) 2. Vetos Contributo progettazione, costruzione e assemblaggio LAV Contributo disegno MUV Contributo disegno CHOD 3. Monte. Carlo Studi trigger hardware e alto livello Digitizzazione, implementazione pile-up 4. Uso di GPU per trigger real-time (FIRB) MS - NA 62 – Luglio 2013

LAV – Large Angle Vetos MS - NA 62 – Luglio 2013

LAV – Attività 2014 Sopralluoghi ditte per materiale Costruzione piastre supporto (S. Piero) Partecipazione a costruzione e test A 12 (LNF) Impegno simile a 2013 Partecipazione a trasporto e installazione A 12 al CERN Circa 2 settimane Spese: materiale (~6 K), trasporto (~5 K), attrezzatura movimentazione (…) MS - NA 62 – Luglio 2013

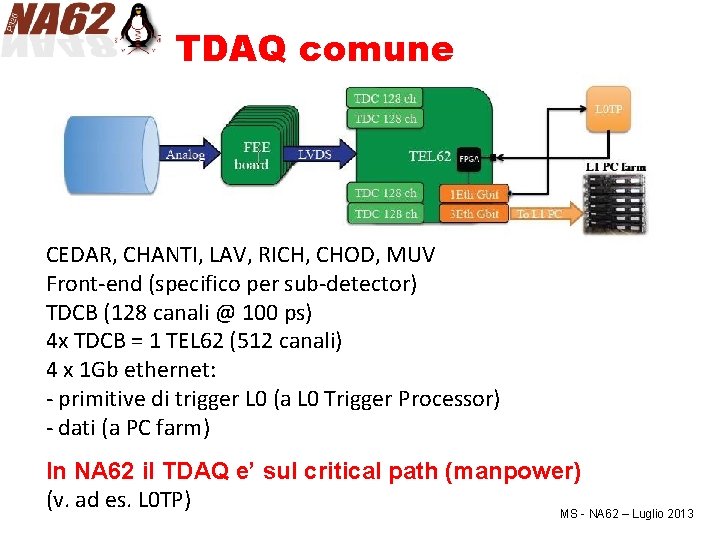

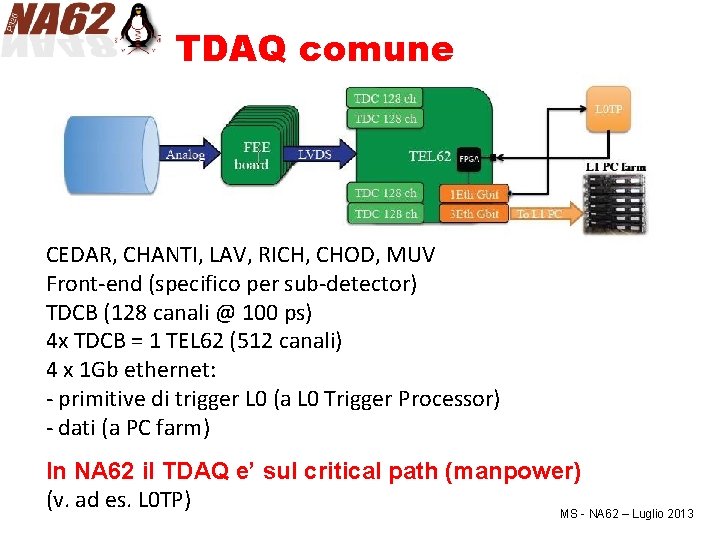

TDAQ comune CEDAR, CHANTI, LAV, RICH, CHOD, MUV Front-end (specifico per sub-detector) TDCB (128 canali @ 100 ps) 4 x TDCB = 1 TEL 62 (512 canali) 4 x 1 Gb ethernet: - primitive di trigger L 0 (a L 0 Trigger Processor) - dati (a PC farm) In NA 62 il TDAQ e’ sul critical path (manpower) (v. ad es. L 0 TP) MS - NA 62 – Luglio 2013

TDCB Basate su CERN HPTDC Usate da: CEDAR, CHANTI, LAV, RICH, CHOD, MUV, SAC, IRC 29 schede costruite (~110 totale necessario) Disegno OK, pronte per la produzione, FW riscritto Attivita’ 2014: • Produzione • Test di 100 schede: prototipo scheda di test in arrivo, FW da testare e setup da allestire • Installazione, commissioning MS - NA 62 – Luglio 2013

TEL 62 Major upgrade delle TELL 1(LHCb) Usate da: CEDAR, CHANTI, LAV, RICH, LKr/L 0 trig, CHOD, MUV 15 schede costruite (~90 totale necessario) Problemi su molte schede da capire (montaggio? PCB? ) MS - NA 62 – Luglio 2013

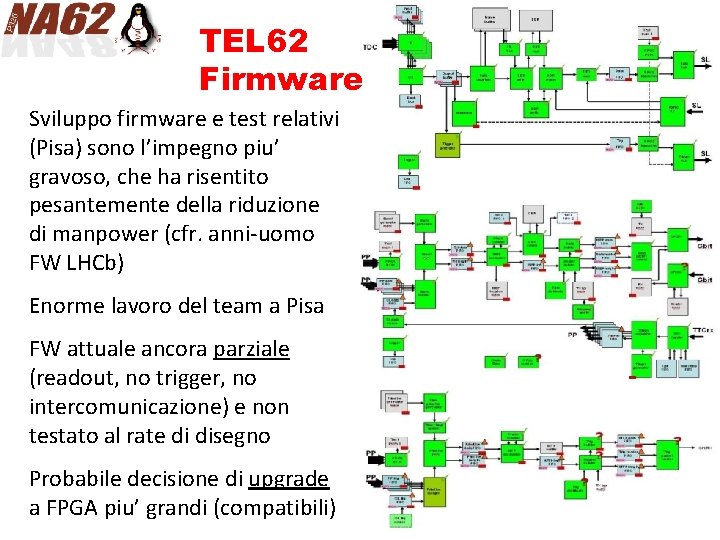

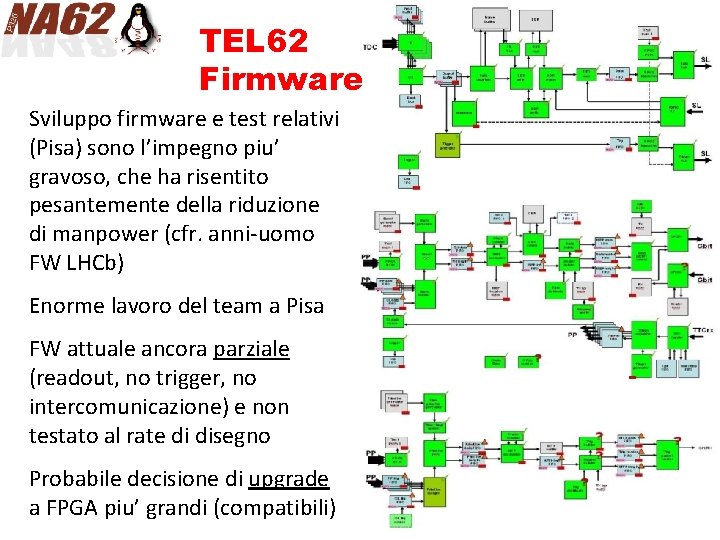

TEL 62 Firmware Sviluppo firmware e test relativi (Pisa) sono l’impegno piu’ gravoso, che ha risentito pesantemente della riduzione di manpower (cfr. anni-uomo FW LHCb) Enorme lavoro del team a Pisa FW attuale ancora parziale (readout, no trigger, no intercomunicazione) e non testato al rate di disegno Probabile decisione di upgrade a FPGA piu’ grandi (compatibili) MS - NA 62 – Luglio 2013

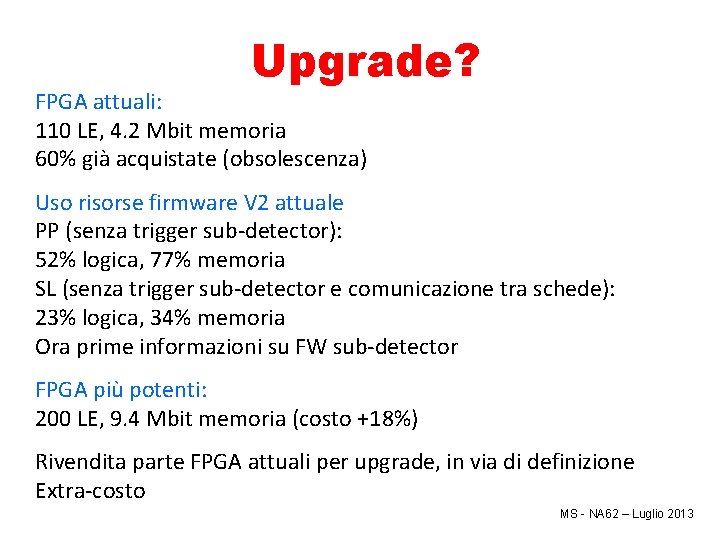

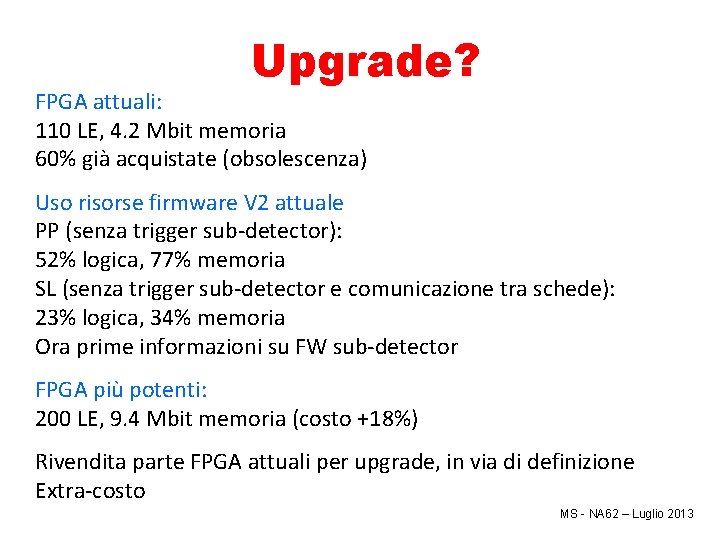

Upgrade? FPGA attuali: 110 LE, 4. 2 Mbit memoria 60% già acquistate (obsolescenza) Uso risorse firmware V 2 attuale PP (senza trigger sub-detector): 52% logica, 77% memoria SL (senza trigger sub-detector e comunicazione tra schede): 23% logica, 34% memoria Ora prime informazioni su FW sub-detector FPGA più potenti: 200 LE, 9. 4 Mbit memoria (costo +18%) Rivendita parte FPGA attuali per upgrade, in via di definizione Extra-costo MS - NA 62 – Luglio 2013

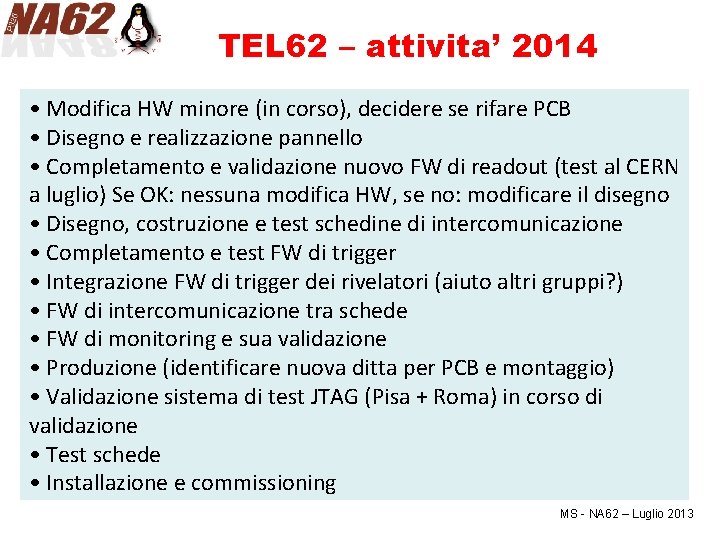

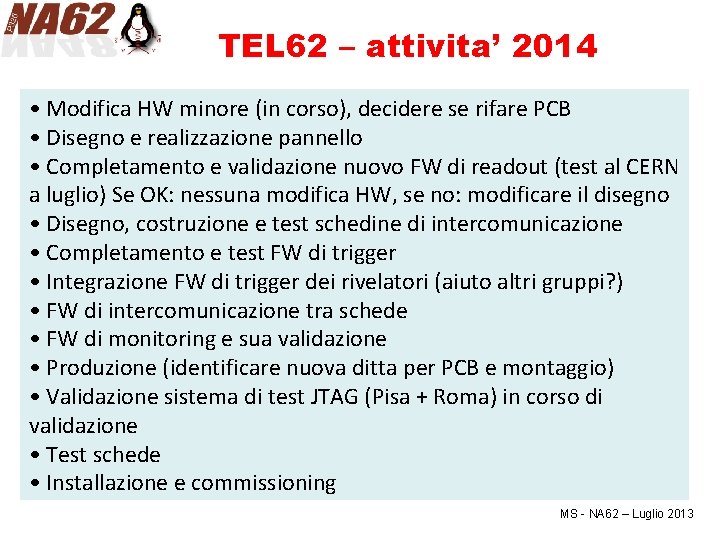

TEL 62 – attivita’ 2014 • Modifica HW minore (in corso), decidere se rifare PCB • Disegno e realizzazione pannello • Completamento e validazione nuovo FW di readout (test al CERN a luglio) Se OK: nessuna modifica HW, se no: modificare il disegno • Disegno, costruzione e test schedine di intercomunicazione • Completamento e test FW di trigger • Integrazione FW di trigger dei rivelatori (aiuto altri gruppi? ) • FW di intercomunicazione tra schede • FW di monitoring e sua validazione • Produzione (identificare nuova ditta per PCB e montaggio) • Validazione sistema di test JTAG (Pisa + Roma) in corso di validazione • Test schede • Installazione e commissioning MS - NA 62 – Luglio 2013

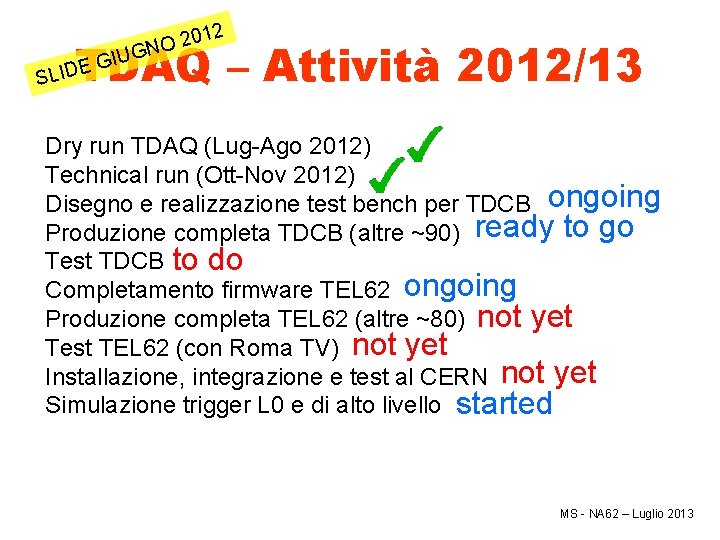

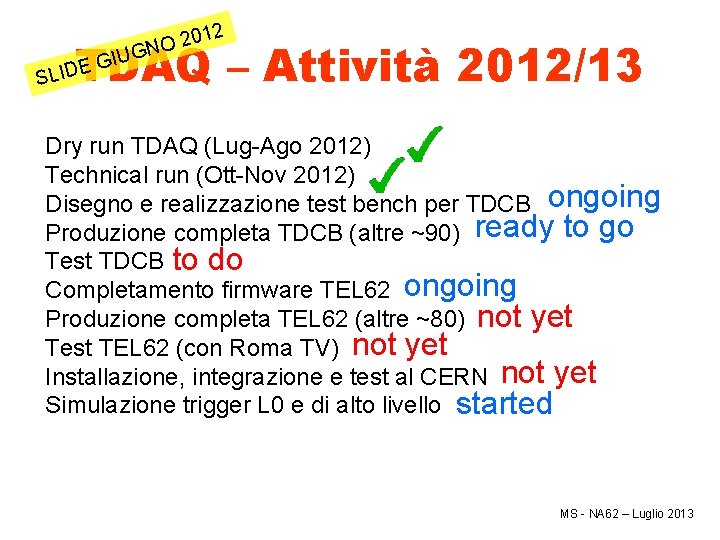

12 0 2 NO TDAQ – Attività 2012/13 UG GI E D I SL Dry run TDAQ (Lug-Ago 2012) Technical run (Ott-Nov 2012) Disegno e realizzazione test bench per TDCB ongoing Produzione completa TDCB (altre ~90) ready to go Test TDCB to do Completamento firmware TEL 62 ongoing Produzione completa TEL 62 (altre ~80) not yet Test TEL 62 (con Roma TV) not yet Installazione, integrazione e test al CERN not yet Simulazione trigger L 0 e di alto livello started MS - NA 62 – Luglio 2013

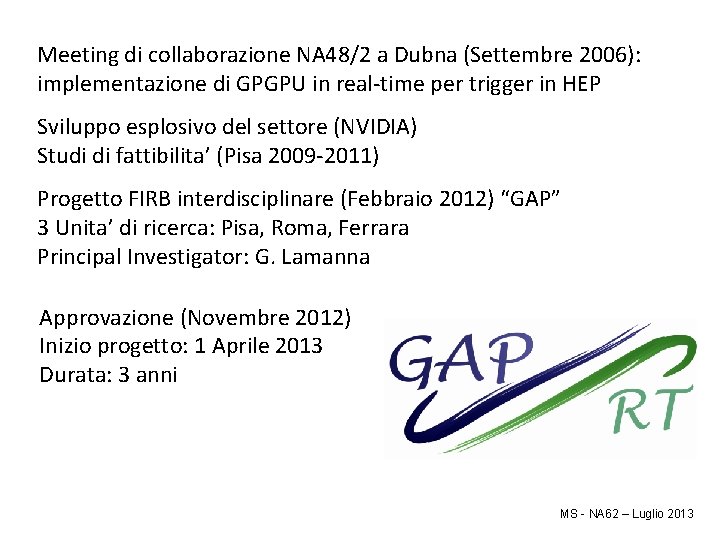

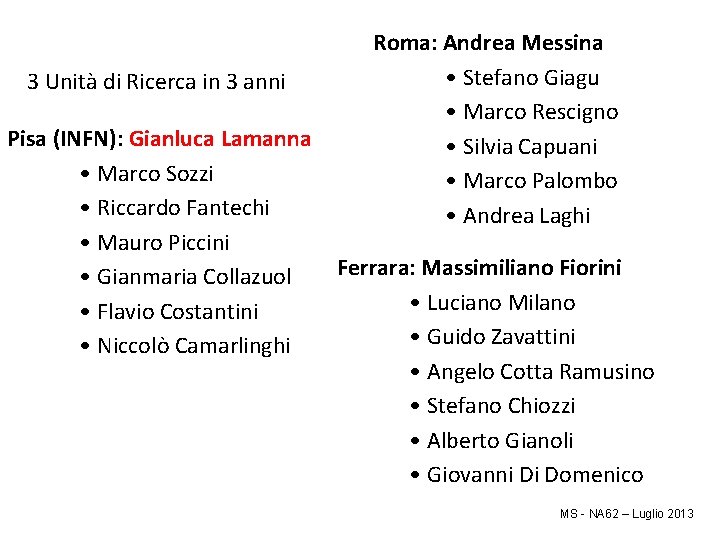

Meeting di collaborazione NA 48/2 a Dubna (Settembre 2006): implementazione di GPGPU in real-time per trigger in HEP Sviluppo esplosivo del settore (NVIDIA) Studi di fattibilita’ (Pisa 2009 -2011) Progetto FIRB interdisciplinare (Febbraio 2012) “GAP” 3 Unita’ di ricerca: Pisa, Roma, Ferrara Principal Investigator: G. Lamanna Approvazione (Novembre 2012) Inizio progetto: 1 Aprile 2013 Durata: 3 anni MS - NA 62 – Luglio 2013

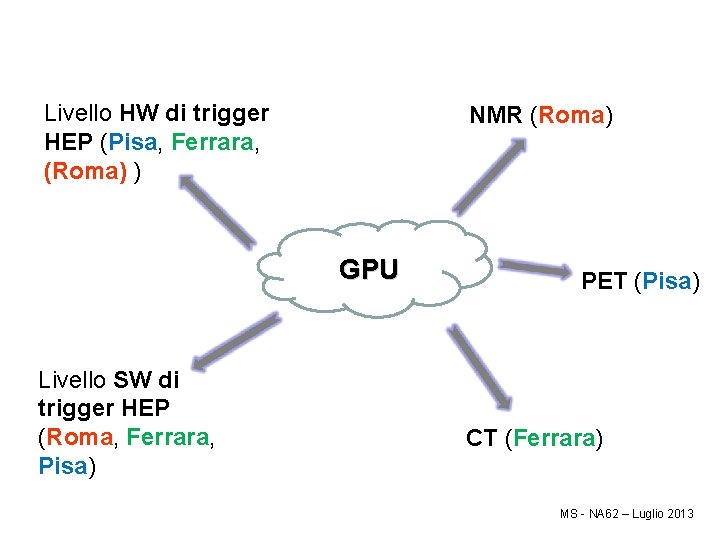

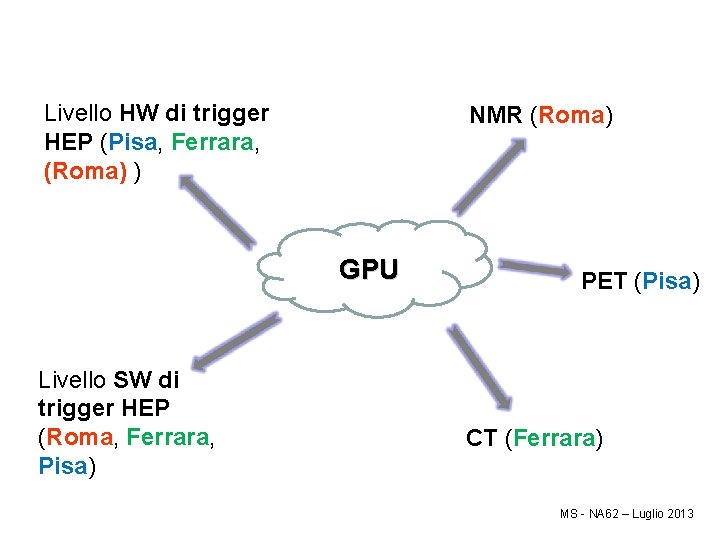

Livello HW di trigger HEP (Pisa, Ferrara, (Roma) ) NMR (Roma) GPU Livello SW di trigger HEP (Roma, Ferrara, Pisa) PET (Pisa) CT (Ferrara) MS - NA 62 – Luglio 2013

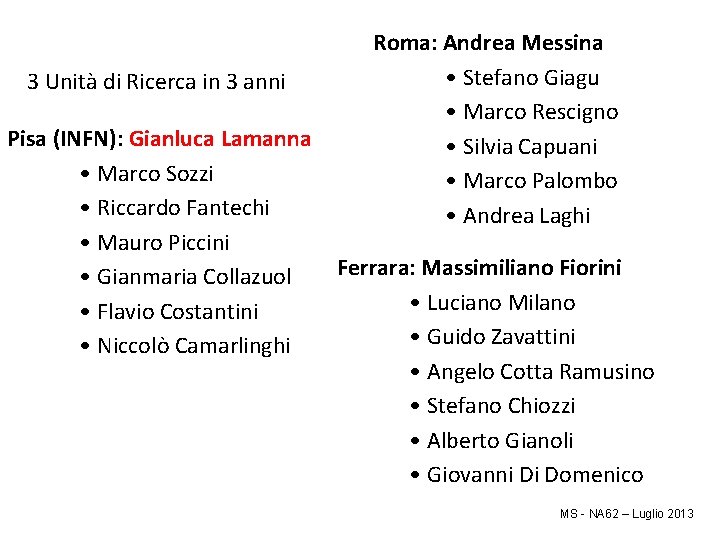

3 Unità di Ricerca in 3 anni Pisa (INFN): Gianluca Lamanna • Marco Sozzi • Riccardo Fantechi • Mauro Piccini • Gianmaria Collazuol • Flavio Costantini • Niccolò Camarlinghi Roma: Andrea Messina • Stefano Giagu • Marco Rescigno • Silvia Capuani • Marco Palombo • Andrea Laghi Ferrara: Massimiliano Fiorini • Luciano Milano • Guido Zavattini • Angelo Cotta Ramusino • Stefano Chiozzi • Alberto Gianoli • Giovanni Di Domenico MS - NA 62 – Luglio 2013

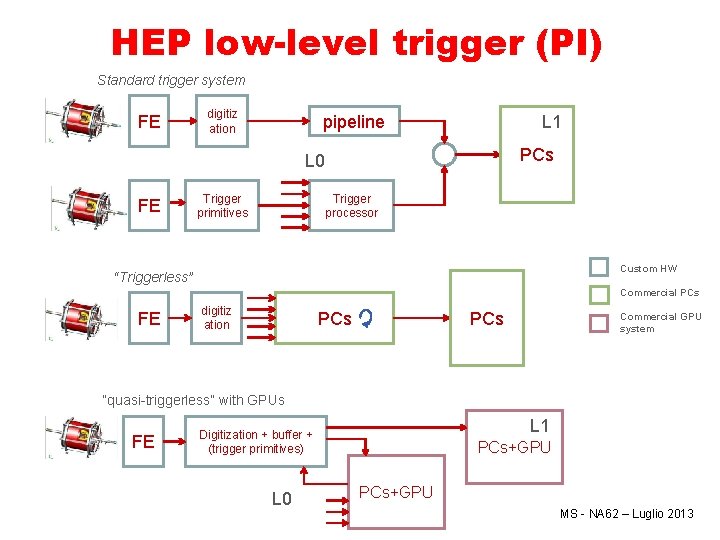

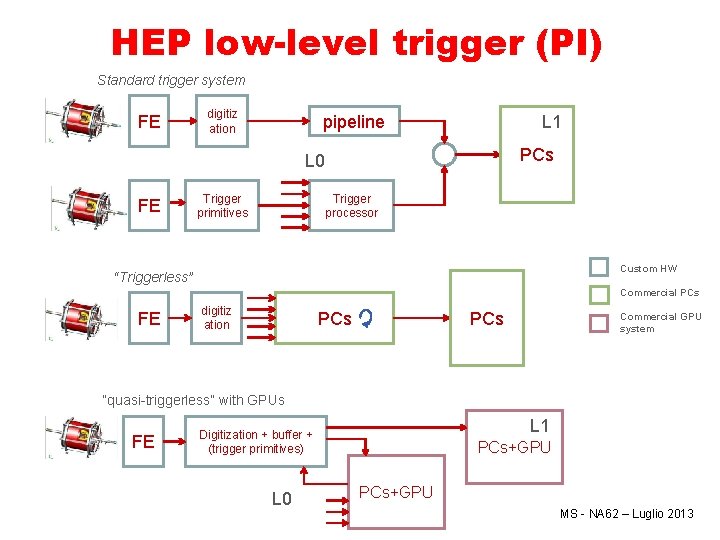

HEP low-level trigger (PI) Standard trigger system FE digitiz ation pipeline L 1 PCs L 0 FE Trigger primitives Trigger processor Custom HW “Triggerless” Commercial PCs FE digitiz ation PCs Commercial GPU system “quasi-triggerless” with GPUs FE L 1 Digitization + buffer + (trigger primitives) L 0 PCs+GPU MS - NA 62 – Luglio 2013

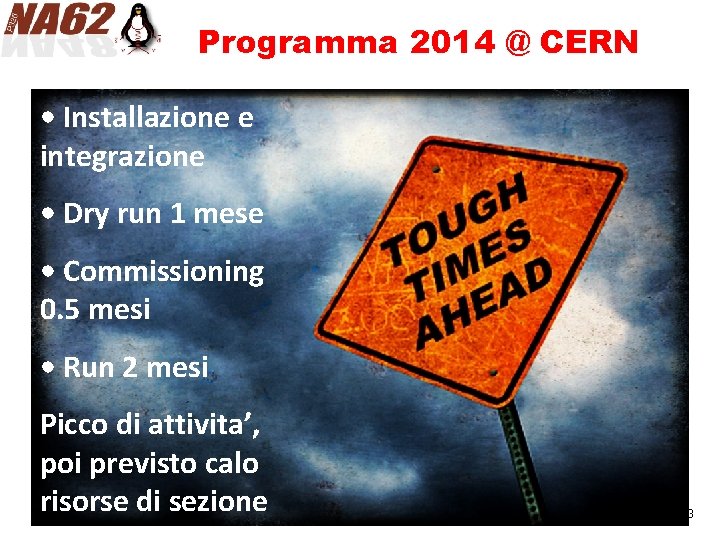

Programma 2014 @ CERN • Installazione e integrazione • Dry run 1 mese • Commissioning 0. 5 mesi • Run 2 mesi Picco di attivita’, poi previsto calo risorse di sezione MS - NA 62 – Luglio 2013

Angelucci Bruno Cerri Claudio Costantini Flavio Fantechi Riccardo Giudici Sergio Lamanna Gianluca Mannelli Italo Piandani Roberto Pinzino Jacopo Pedreschi Elena Sozzi Marco Raffaelli Fabrizio Spinella Franco Bianucci Sandro Minuti Massimo Beretta Luca Petragnani Giulio Dottorando (3) 100% Primo Ricercatore --Prof. Ordinario 100% Primo Ricercatore 89%+11% FIRB (100%) Ricercatore 100% Art. 23 FIRB 0%+100% FIRB (100%) Prof. Ordinario --Ass. ricerca R. Toscana 100% Dottorando (2) 100% Ass. Ric. Dip. 100% Prof. Associato 100% Dirigente Tecnologo 30% Tecnologo 70% Coll. Tecn. ER 30% Coll. Tecn. ER 50% Tecn 25% 10 Ric. /8 FTE (-1/0), 3 Tecn. /1. 9 FTE (-1/-0. 4), 2 CT/0. 8 FTE (+1/+0. 5) Mantenere team e risorse invariate. MS! - NA 62 – Luglio 2013

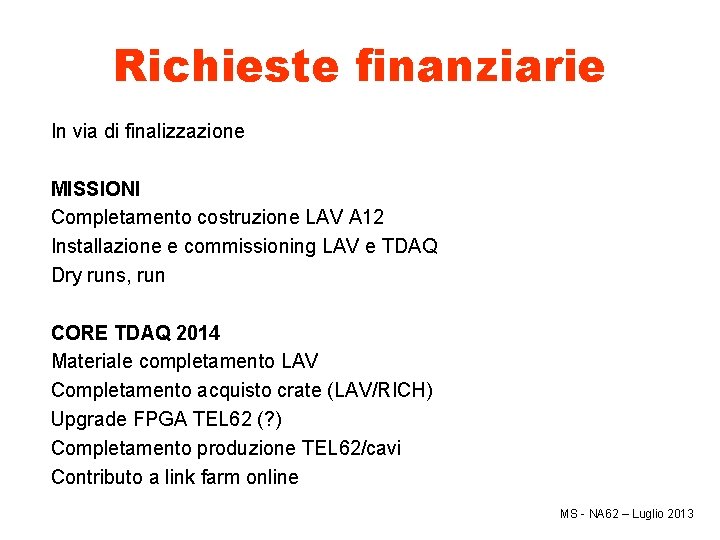

Richieste finanziarie In via di finalizzazione MISSIONI Completamento costruzione LAV A 12 Installazione e commissioning LAV e TDAQ Dry runs, run CORE TDAQ 2014 Materiale completamento LAV Completamento acquisto crate (LAV/RICH) Upgrade FPGA TEL 62 (? ) Completamento produzione TEL 62/cavi Contributo a link farm online MS - NA 62 – Luglio 2013