n n n n n TimerInterrupt RTCInterrupt TimerInterrupt

- Slides: 19

大網 n n 說明 習題 n n n Timer/Interrupt RTC/Interrupt 問題與討論

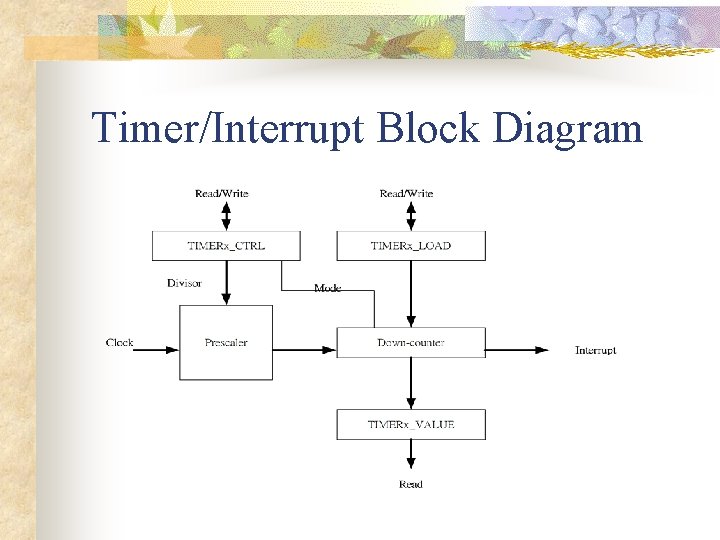

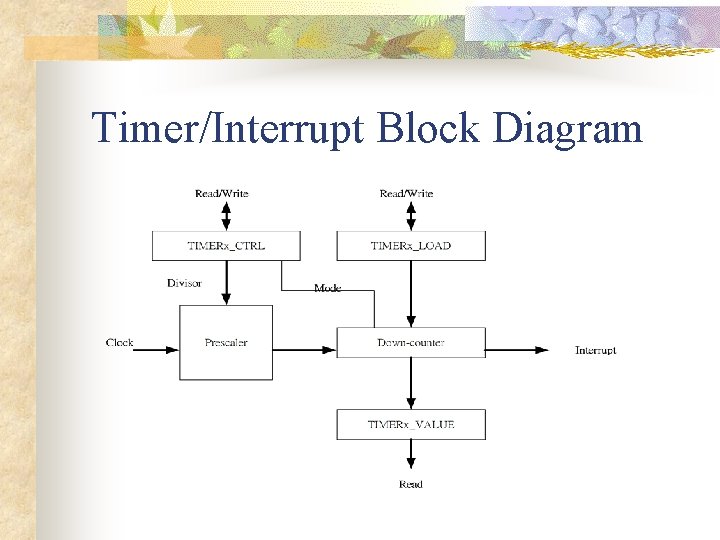

Timer/Interrupt Block Diagram

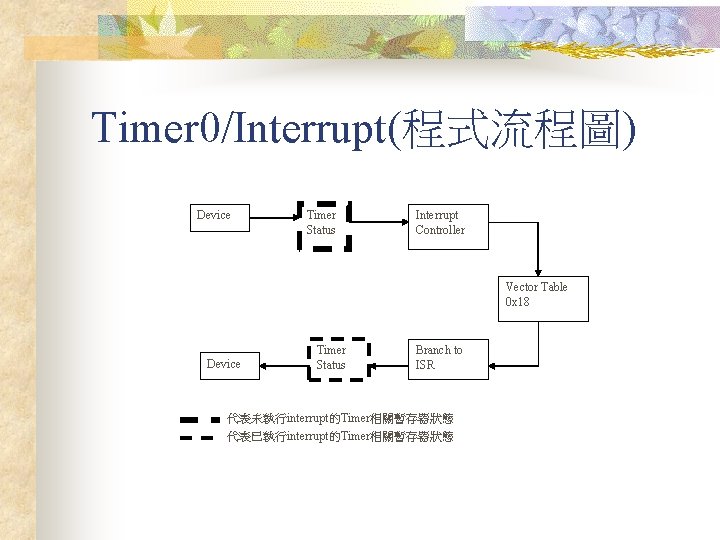

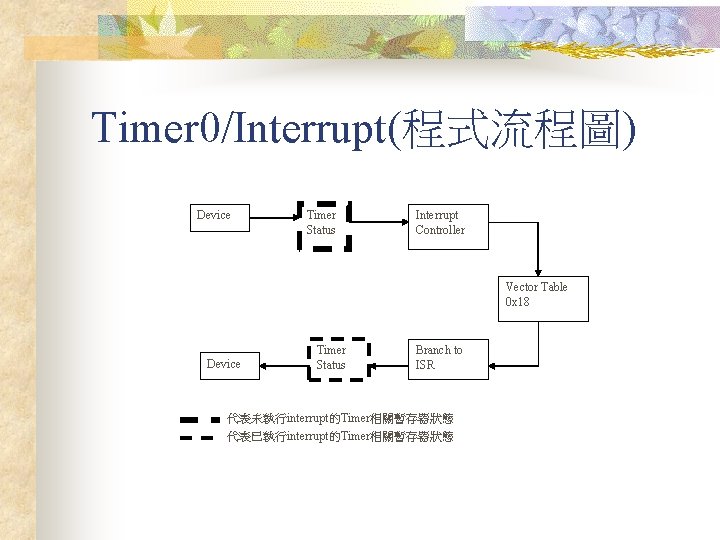

Timer 0/Interrupt(程式流程圖) Device Timer Status Interrupt Controller Vector Table 0 x 18 Device Timer Status Branch to ISR 代表未執行interrupt的Timer相關暫存器狀態 代表已執行interrupt的Timer相關暫存器狀態

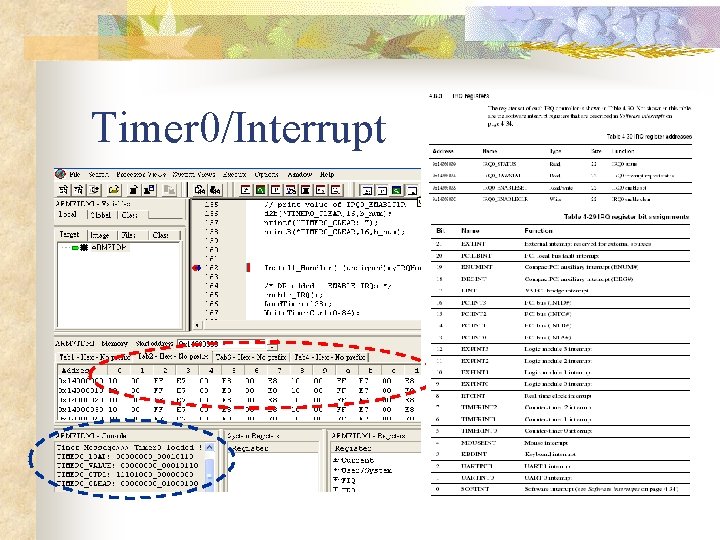

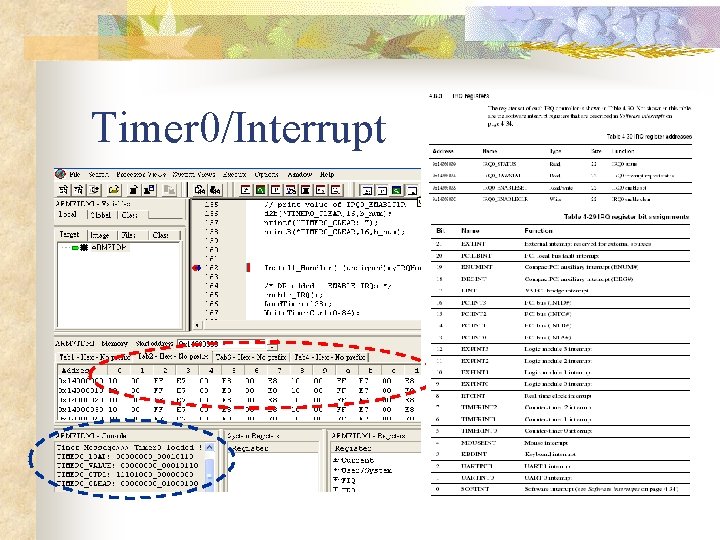

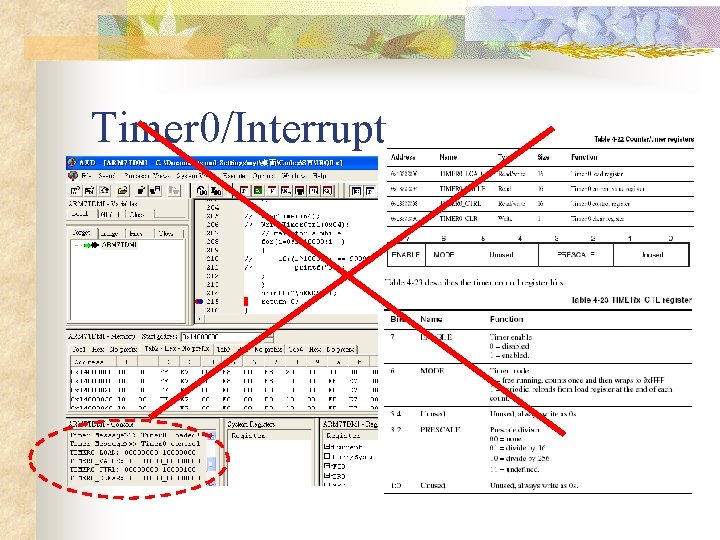

Timer 0/Interrupt

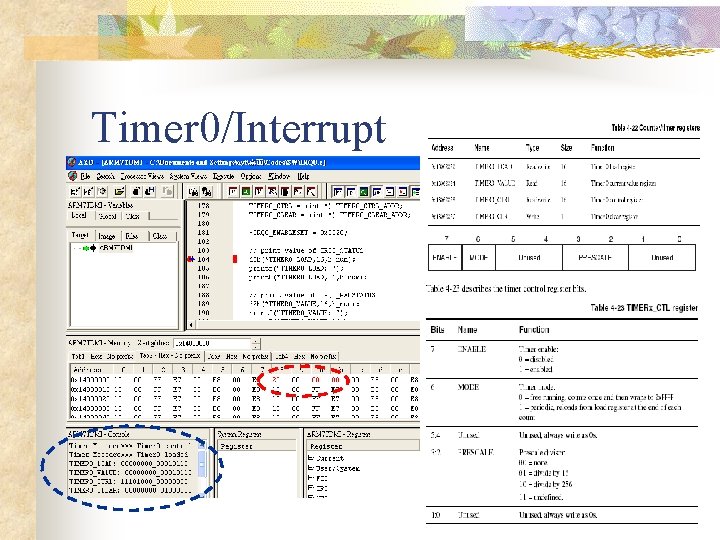

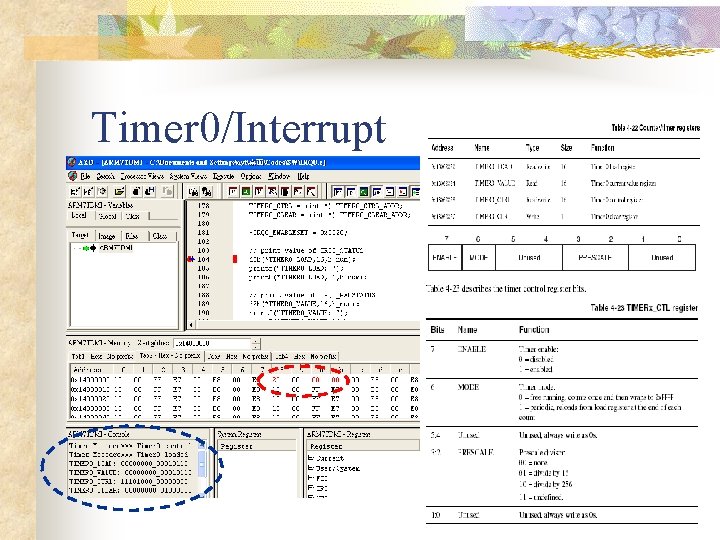

Timer 0/Interrupt

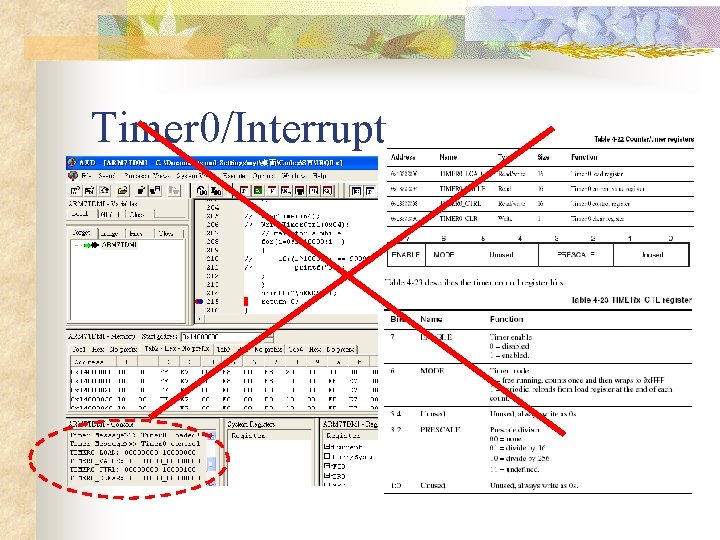

Timer 0/Interrupt

3. 2. 3 Timer/Interrupt n n The example must be run on the integrator to work. Using Armulator will not be able to show the correct results. Should be: n Using Armulator is totally MEANINGLESS!

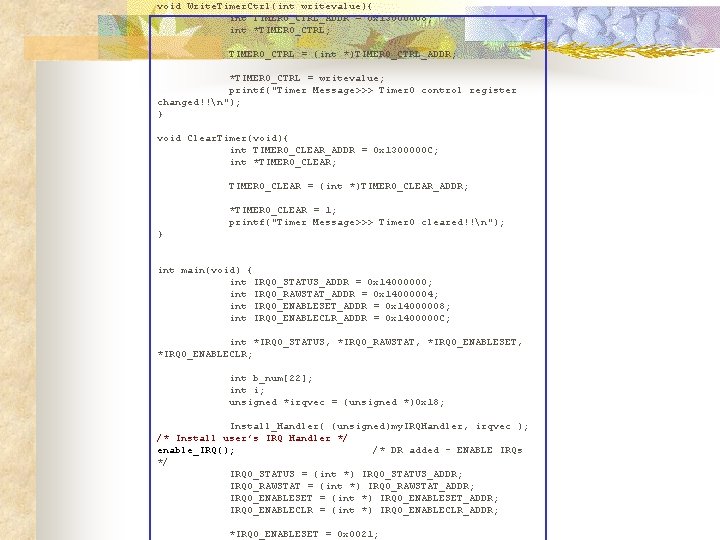

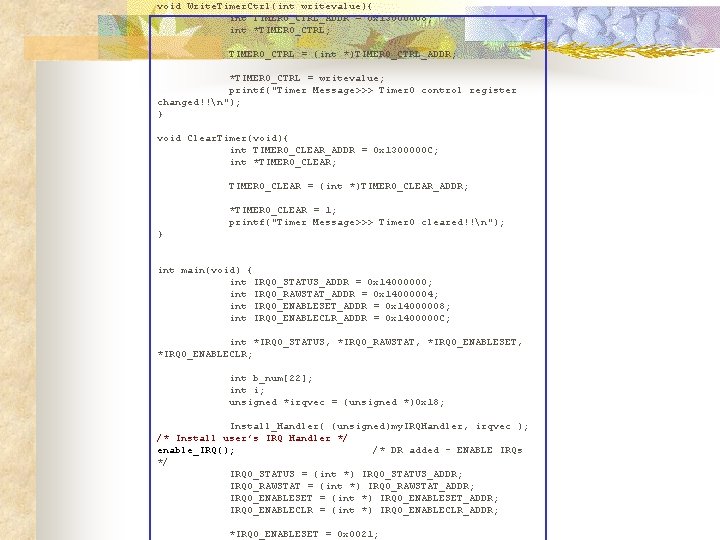

void Write. Timer. Ctrl(int writevalue){ int TIMER 0_CTRL_ADDR = 0 x 13000008; int *TIMER 0_CTRL; TIMER 0_CTRL = (int *)TIMER 0_CTRL_ADDR; *TIMER 0_CTRL = writevalue; printf("Timer Message>>> Timer 0 control register changed!!n"); } void Clear. Timer(void){ int TIMER 0_CLEAR_ADDR = 0 x 1300000 C; int *TIMER 0_CLEAR; TIMER 0_CLEAR = (int *)TIMER 0_CLEAR_ADDR; *TIMER 0_CLEAR = 1; printf("Timer Message>>> Timer 0 cleared!!n"); } int main(void) { int IRQ 0_STATUS_ADDR = 0 x 14000000; int IRQ 0_RAWSTAT_ADDR = 0 x 14000004; int IRQ 0_ENABLESET_ADDR = 0 x 14000008; int IRQ 0_ENABLECLR_ADDR = 0 x 1400000 C; int *IRQ 0_STATUS, *IRQ 0_RAWSTAT, *IRQ 0_ENABLESET, *IRQ 0_ENABLECLR; int b_num[22]; int i; unsigned *irqvec = (unsigned *)0 x 18; Install_Handler( (unsigned)my. IRQHandler, irqvec ); /* Install user’s IRQ Handler */ enable_IRQ(); /* DR added - ENABLE IRQs */ IRQ 0_STATUS = (int *) IRQ 0_STATUS_ADDR; IRQ 0_RAWSTAT = (int *) IRQ 0_RAWSTAT_ADDR; IRQ 0_ENABLESET = (int *) IRQ 0_ENABLESET_ADDR; IRQ 0_ENABLECLR = (int *) IRQ 0_ENABLECLR_ADDR; *IRQ 0_ENABLESET = 0 x 0021;

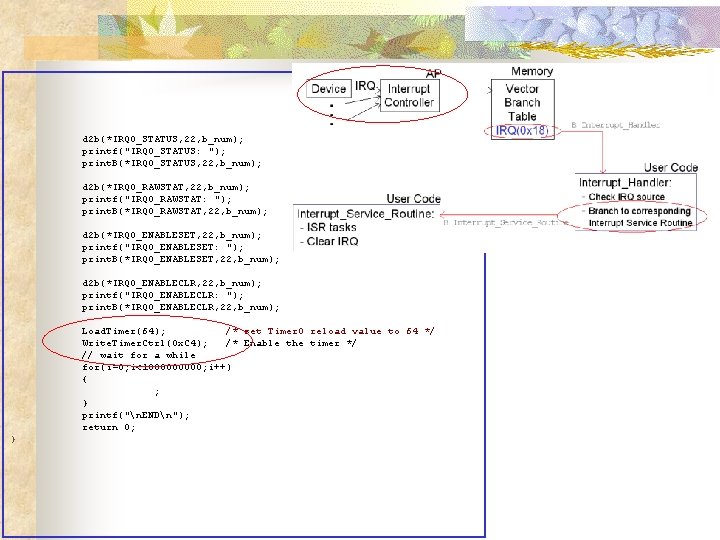

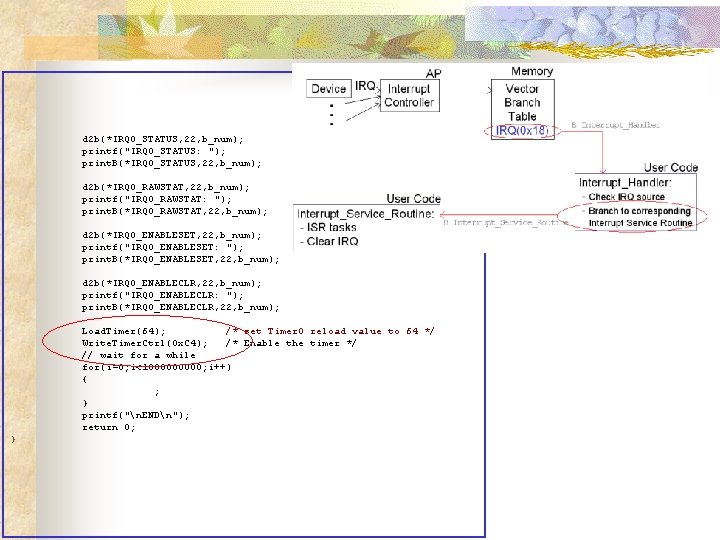

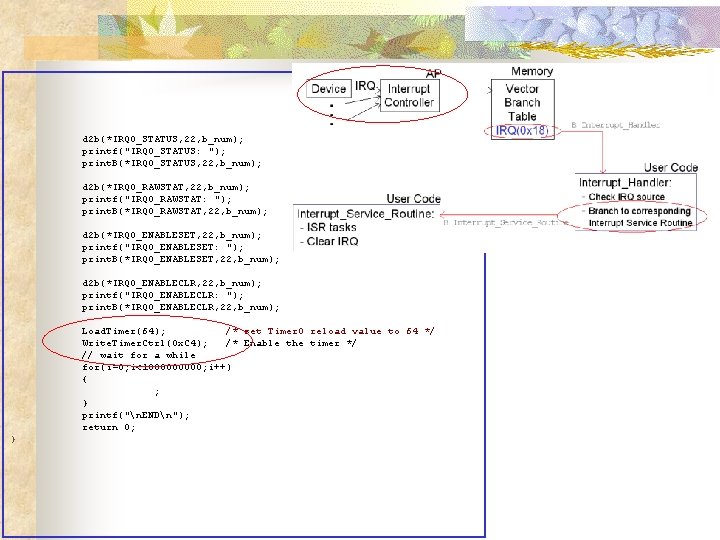

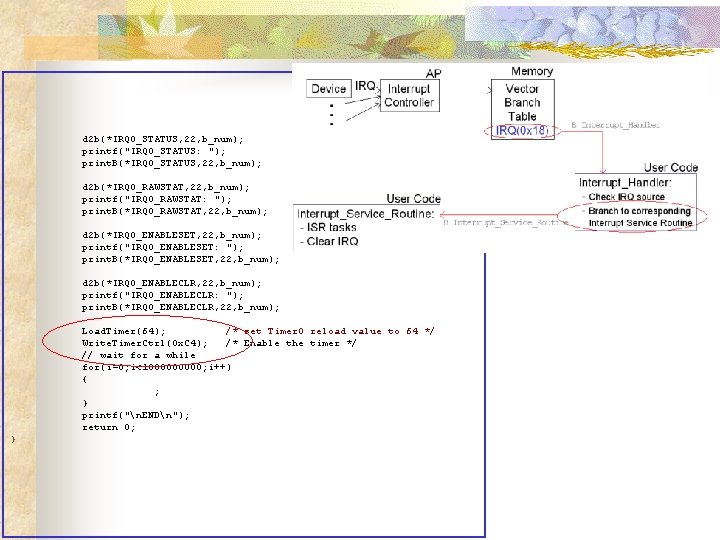

d 2 b(*IRQ 0_STATUS, 22, b_num); printf("IRQ 0_STATUS: "); print. B(*IRQ 0_STATUS, 22, b_num); d 2 b(*IRQ 0_RAWSTAT, 22, b_num); printf("IRQ 0_RAWSTAT: "); print. B(*IRQ 0_RAWSTAT, 22, b_num); d 2 b(*IRQ 0_ENABLESET, 22, b_num); printf("IRQ 0_ENABLESET: "); print. B(*IRQ 0_ENABLESET, 22, b_num); d 2 b(*IRQ 0_ENABLECLR, 22, b_num); printf("IRQ 0_ENABLECLR: "); print. B(*IRQ 0_ENABLECLR, 22, b_num); Load. Timer(64); /* set Timer 0 reload value to 64 */ Write. Timer. Ctrl(0 x. C 4); /* Enable the timer */ // wait for a while for(i=0; i<100000; i++) { ; } printf("n. ENDn"); return 0; }

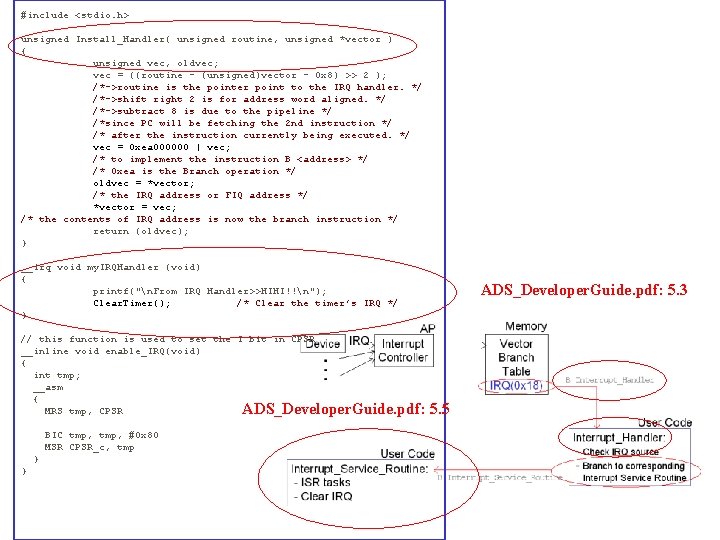

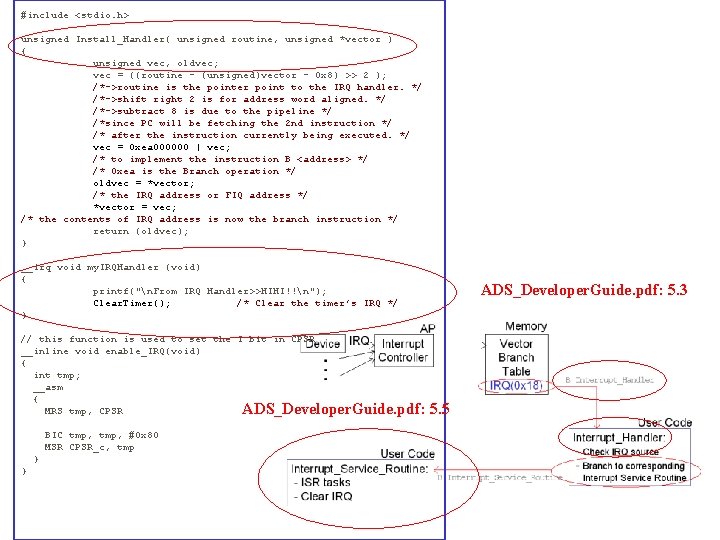

#include <stdio. h> unsigned Install_Handler( unsigned routine, unsigned *vector ) { unsigned vec, oldvec; vec = ((routine - (unsigned)vector - 0 x 8) >> 2 ); /*->routine is the pointer point to the IRQ handler. */ /*->shift right 2 is for address word aligned. */ /*->subtract 8 is due to the pipeline */ /*since PC will be fetching the 2 nd instruction */ /* after the instruction currently being executed. */ vec = 0 xea 000000 | vec; /* to implement the instruction B <address> */ /* 0 xea is the Branch operation */ oldvec = *vector; /* the IRQ address or FIQ address */ *vector = vec; /* the contents of IRQ address is now the branch instruction */ return (oldvec); } __irq void my. IRQHandler (void) { printf("n. From IRQ Handler>>HIHI!!n"); Clear. Timer(); /* Clear the timer’s IRQ */ } // this function is used to set the I bit in CPSR __inline void enable_IRQ(void) { int tmp; __asm { MRS tmp, CPSR ADS_Developer. Guide. pdf: 5. 5 BIC tmp, #0 x 80 MSR CPSR_c, tmp } } ADS_Developer. Guide. pdf: 5. 3

d 2 b(*IRQ 0_STATUS, 22, b_num); printf("IRQ 0_STATUS: "); print. B(*IRQ 0_STATUS, 22, b_num); d 2 b(*IRQ 0_RAWSTAT, 22, b_num); printf("IRQ 0_RAWSTAT: "); print. B(*IRQ 0_RAWSTAT, 22, b_num); d 2 b(*IRQ 0_ENABLESET, 22, b_num); printf("IRQ 0_ENABLESET: "); print. B(*IRQ 0_ENABLESET, 22, b_num); d 2 b(*IRQ 0_ENABLECLR, 22, b_num); printf("IRQ 0_ENABLECLR: "); print. B(*IRQ 0_ENABLECLR, 22, b_num); Load. Timer(64); /* set Timer 0 reload value to 64 */ Write. Timer. Ctrl(0 x. C 4); /* Enable the timer */ // wait for a while for(i=0; i<100000; i++) { ; } printf("n. ENDn"); return 0; }

必看文件 n n n DUI_0098 B_AP_UG. pdf: Ch 3 Ch 4 ADS_Developer. Guide. pdf: 5. 3 5. 5 將參考文件加註於程式碼

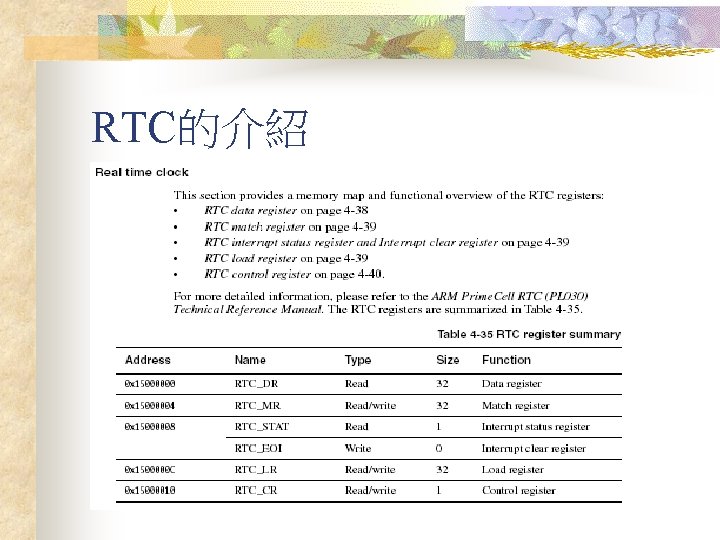

Introduction of RTC n n n “Real” in Real Time Clock means “authentic” not “simultaneous. ” It is triggered per second, like a clock on your watch. As a system application clock (like watch)

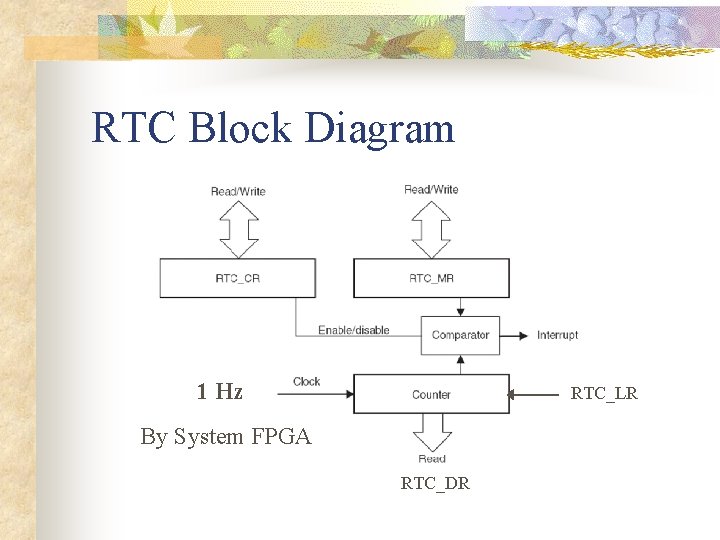

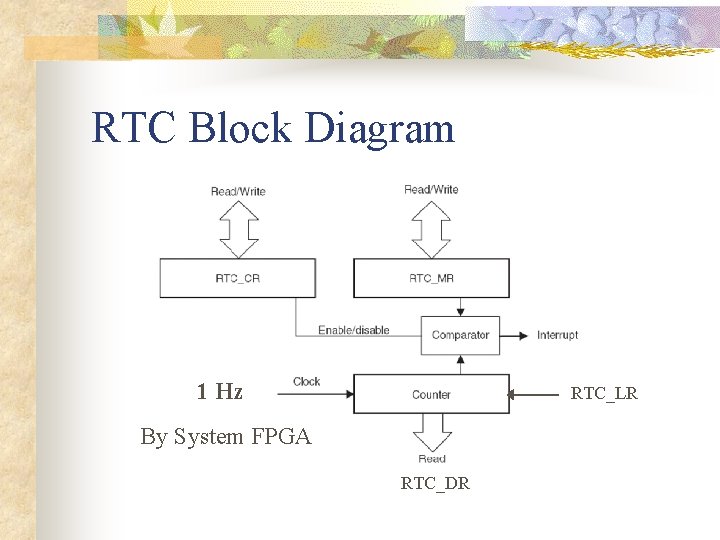

RTC Block Diagram 1 Hz RTC_LR By System FPGA RTC_DR

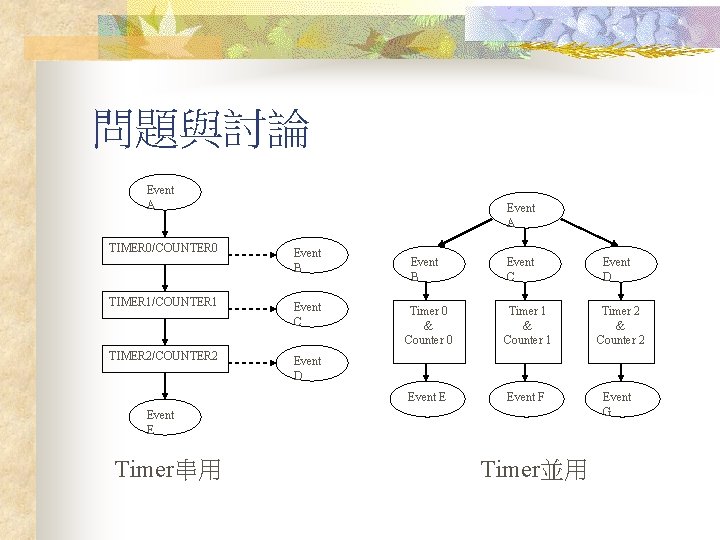

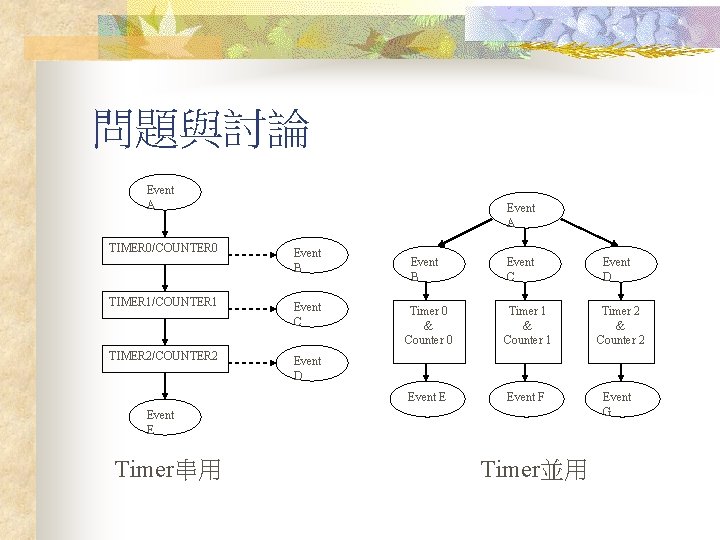

問題與討論 Event A TIMER 0/COUNTER 0 Event A Event B TIMER 1/COUNTER 1 Event C TIMER 2/COUNTER 2 Event D Event B Event C Timer 0 & Counter 0 Timer 1 & Counter 1 Event E Event F Event E Timer串用 Timer並用 Event D Timer 2 & Counter 2 Event G

參考資料 n n n ADS_Compiler. Linker. Util_C. pdf ADS_Developer. Guide_C. pdf DUI 0098 B_AP_UG. pdf