MVSIS Group Minxi Gao JieHong Jiang Yunjian Jiang

![[cadntws 11: /home/wjiang/mvsis/examples/bob] mvsis UC Berkeley, MVSIS 0. 95 (compiled 24 -May-01 at 2: [cadntws 11: /home/wjiang/mvsis/examples/bob] mvsis UC Berkeley, MVSIS 0. 95 (compiled 24 -May-01 at 2:](https://slidetodoc.com/presentation_image_h/250a746c9662d9fcb379ae88ef6f8ef4/image-17.jpg)

![[cadntws 11: /home/wjiang/mvsis/examples/bob] mvsis UC Berkeley, MVSIS 0. 95 (compiled 24 -May-01 at 2: [cadntws 11: /home/wjiang/mvsis/examples/bob] mvsis UC Berkeley, MVSIS 0. 95 (compiled 24 -May-01 at 2:](https://slidetodoc.com/presentation_image_h/250a746c9662d9fcb379ae88ef6f8ef4/image-23.jpg)

- Slides: 28

MVSIS Group Minxi Gao, , Jie-Hong Jiang, Yunjian Jiang, Yinghua Li, Subarna Sinha and Robert K. Brayton Dept. of Electrical Engineering and Computer Science University of California, Berkeley

Outline Motivation: From binary to multi-value Design specification MVSIS optimizations n n Node simplification Kernel and cube extraction Pairing and encoding Network manipulation Demo Conclusions

History Multi-valued logic Incomplete references E. L. Post, “Introdution to a general theory of elementary propositions”, Amer. J. Math. , Jun 1921 J. C. Muzio and D. M. Miller, “On the minimization of many-valued functions”, Proc. 9 th Int. Symp. Multiple-valued Logic, 1979 S. L. Hurst, “Multiple-valued logic – its status and its future”, IEEE Trans. On Computers, Jun 1984 J. C. Muzio and T. C. Wesselkamper, “Multiple-valued switching theory” Bristol: Hilger, 1986 R. K. Brayton and S. P. Khatri, “Multi-valued logic synthesis”, Proc. 12 th Int. Conf. On VLSI Design, Jan 1999

Motivations Synchronous hardware synthesis Software synthesis from synchronous specifications Asynchronous hardware synthesis Multi-valued devices? n n Current-mode CMOS devices Optical logic circuits

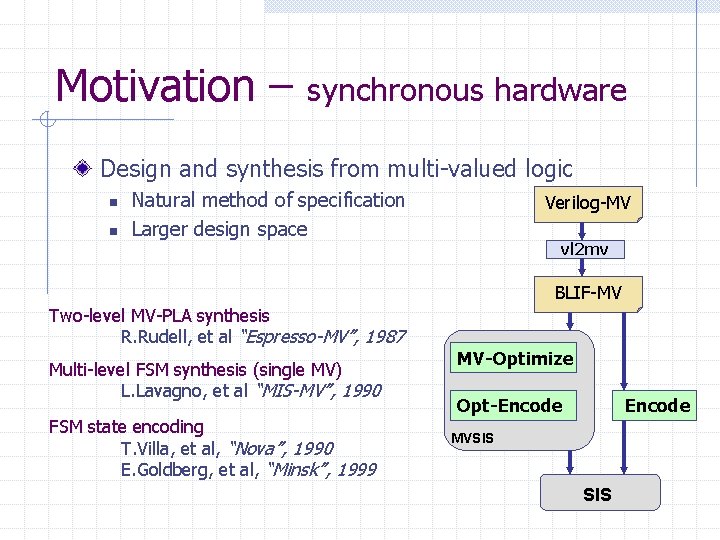

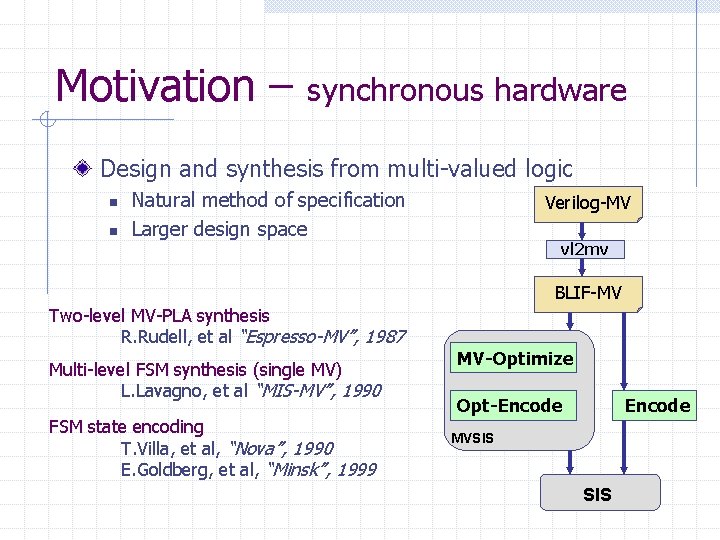

Motivation – synchronous hardware Design and synthesis from multi-valued logic n n Natural method of specification Larger design space Verilog-MV vl 2 mv BLIF-MV Two-level MV-PLA synthesis R. Rudell, et al “Espresso-MV”, 1987 Multi-level FSM synthesis (single MV) L. Lavagno, et al “MIS-MV”, 1990 FSM state encoding T. Villa, et al, “Nova”, 1990 E. Goldberg, et al, “Minsk”, 1999 MV-Optimize Opt-Encode MVSIS

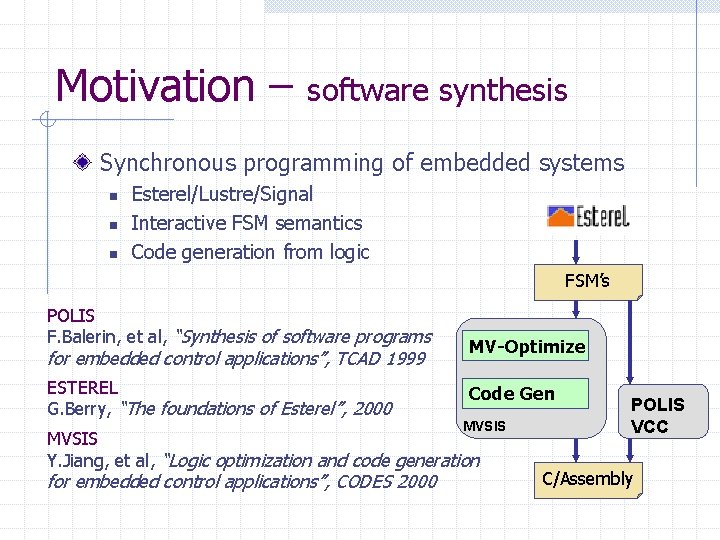

Motivation – software synthesis Synchronous programming of embedded systems n n n Esterel/Lustre/Signal Interactive FSM semantics Code generation from logic FSM’s POLIS F. Balerin, et al, “Synthesis of software programs for embedded control applications”, TCAD 1999 ESTEREL G. Berry, “The foundations of Esterel”, 2000 MV-Optimize Code Gen MVSIS Y. Jiang, et al, “Logic optimization and code generation for embedded control applications”, CODES 2000 POLIS VCC C/Assembly

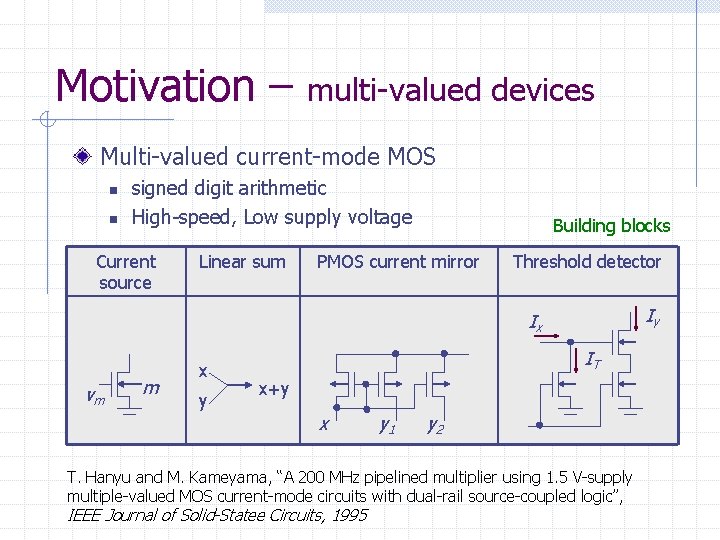

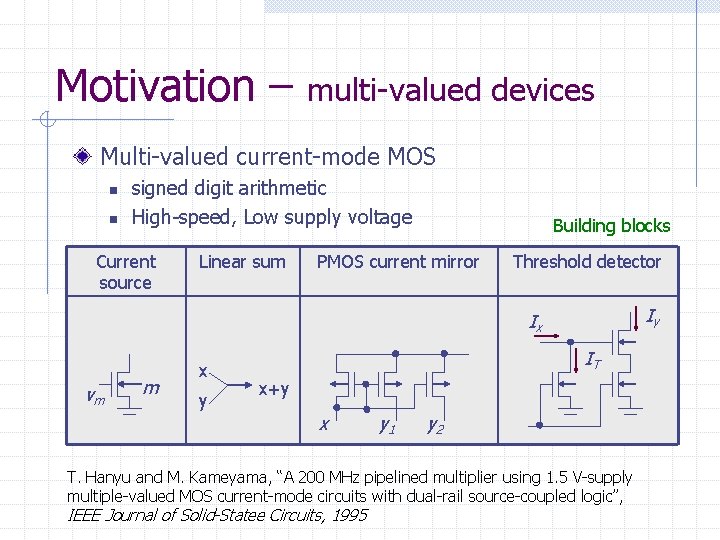

Motivation – multi-valued devices Multi-valued current-mode MOS n n signed digit arithmetic High-speed, Low supply voltage Current source Linear sum Building blocks PMOS current mirror Threshold detector Iy Ix vm m x y IT x+y x y 1 y 2 T. Hanyu and M. Kameyama, “A 200 MHz pipelined multiplier using 1. 5 V-supply multiple-valued MOS current-mode circuits with dual-rail source-coupled logic”, IEEE Journal of Solid-Statee Circuits, 1995

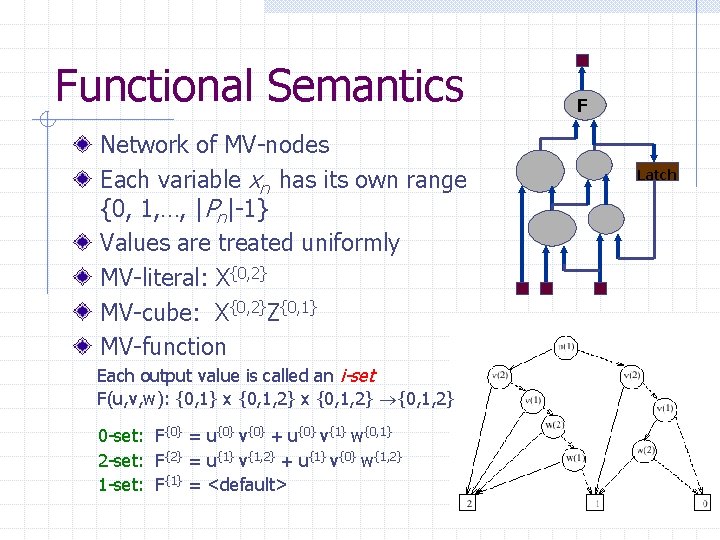

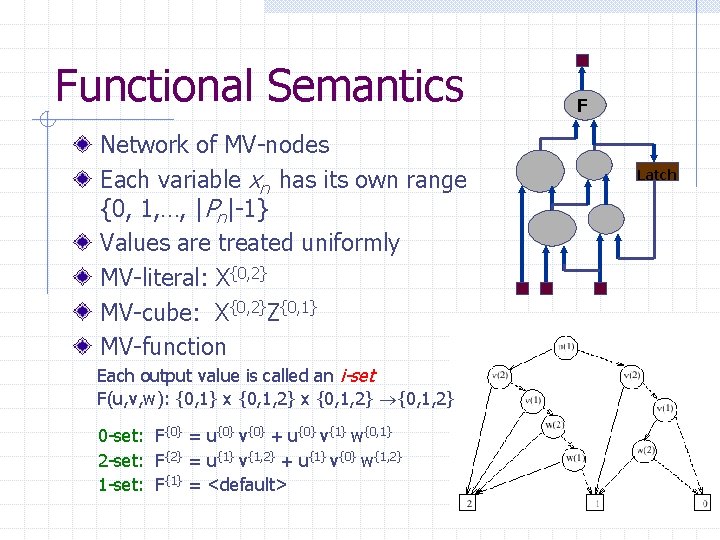

Functional Semantics Network of MV-nodes Each variable xn has its own range {0, 1, …, |Pn|-1} Values are treated uniformly MV-literal: X{0, 2} MV-cube: X{0, 2}Z{0, 1} MV-function Each output value is called an i-set F(u, v, w): {0, 1} x {0, 1, 2} 0 -set: F{0} = u{0} v{0} + u{0} v{1} w{0, 1} 2 -set: F{2} = u{1} v{1, 2} + u{1} v{0} w{1, 2} 1 -set: F{1} = <default> F Latch

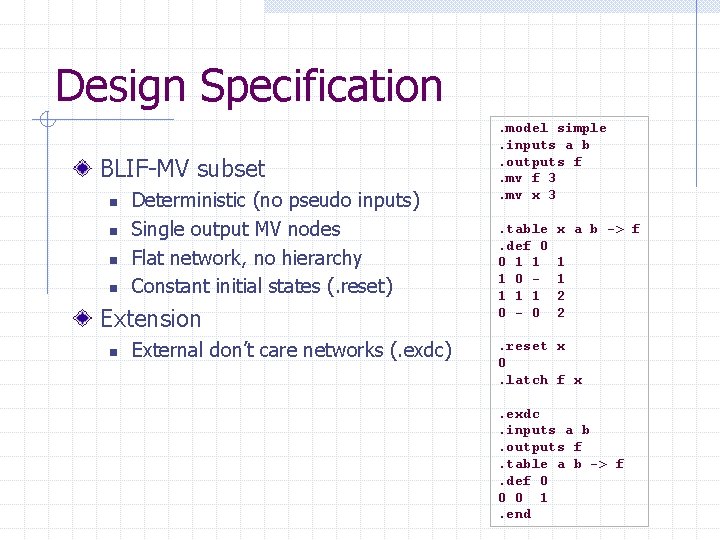

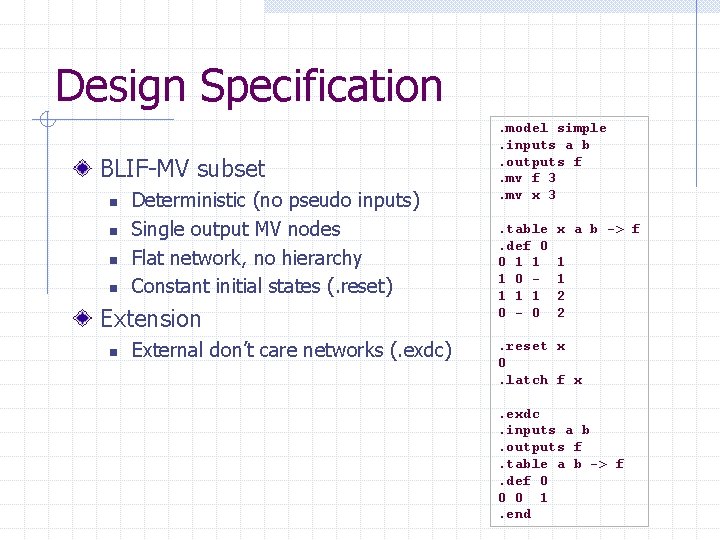

Design Specification BLIF-MV subset n n Deterministic (no pseudo inputs) Single output MV nodes Flat network, no hierarchy Constant initial states (. reset) Extension n External don’t care networks (. exdc) . model simple. inputs a b. outputs f. mv f 3. mv x 3. table. def 0 0 1 1 1 0 - 0 x a b -> f 1 1 2 2 . reset x 0. latch f x. exdc. inputs a b. outputs f. table a b -> f. def 0 0 0 1. end

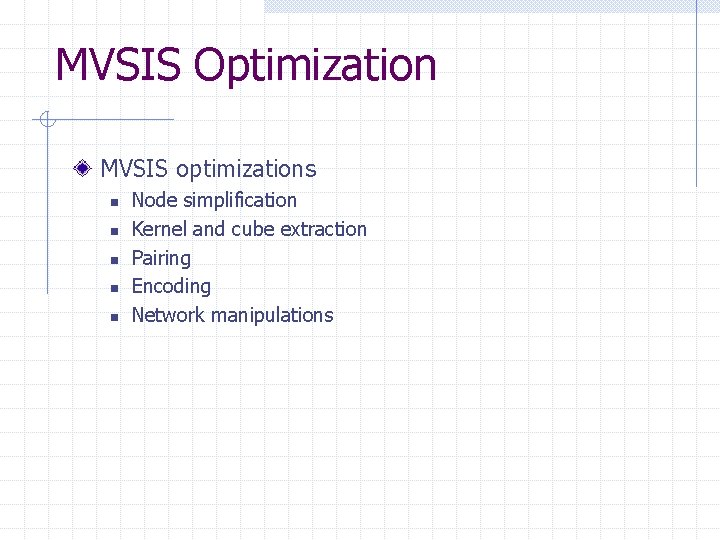

MVSIS Optimization MVSIS optimizations n n n Node simplification Kernel and cube extraction Pairing Encoding Network manipulations

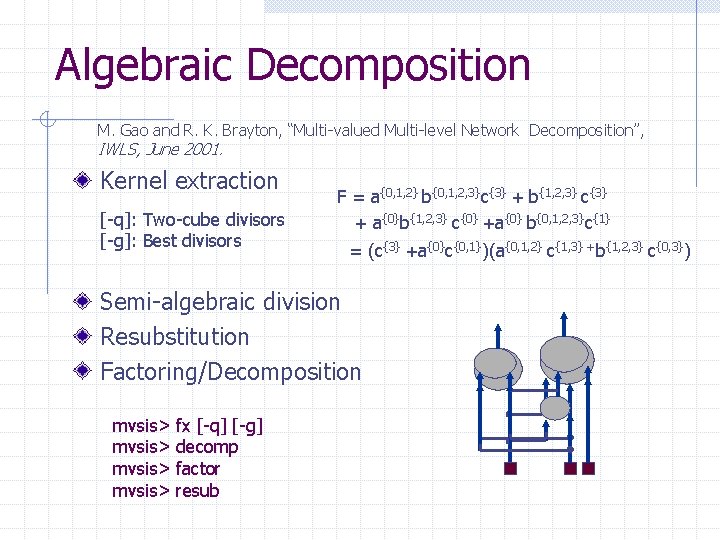

Node Simplification a 100 101 110 b 11 10 10 c 011 110 d 101 011 110 z 0 0 0 100 11 101 1 111 01 100 111 1 100 11 110 1 Two-level: Espresso-MV <default> 2 101 01 100 001 010 01 001 101 - Minimize each i-set independently Don’t care: input minterm that produces all output values Partial care: input minterm that produces a subset of output values Multi-level Compatible observability don’t cares (CODC) Satisfiability don’t cares (SDC) External don’t cares (XDC) Q 1 Q 2. . . Qr Di i image mvsis> simplify mvsis> fullsimp mvsis> reset_default P 1 P 2. . . Pn care set DCi

Algebraic Decomposition M. Gao and R. K. Brayton, “Multi-valued Multi-level Network Decomposition”, IWLS, June 2001. Kernel extraction [-q]: Two-cube divisors [-g]: Best divisors F = a{0, 1, 2} b{0, 1, 2, 3}c{3} + b{1, 2, 3} c{3} + a{0}b{1, 2, 3} c{0} +a{0} b{0, 1, 2, 3}c{1} = (c{3} +a{0}c{0, 1})(a{0, 1, 2} c{1, 3} +b{1, 2, 3} c{0, 3}) Semi-algebraic division Resubstitution Factoring/Decomposition mvsis> fx [-q] [-g] decomp factor resub

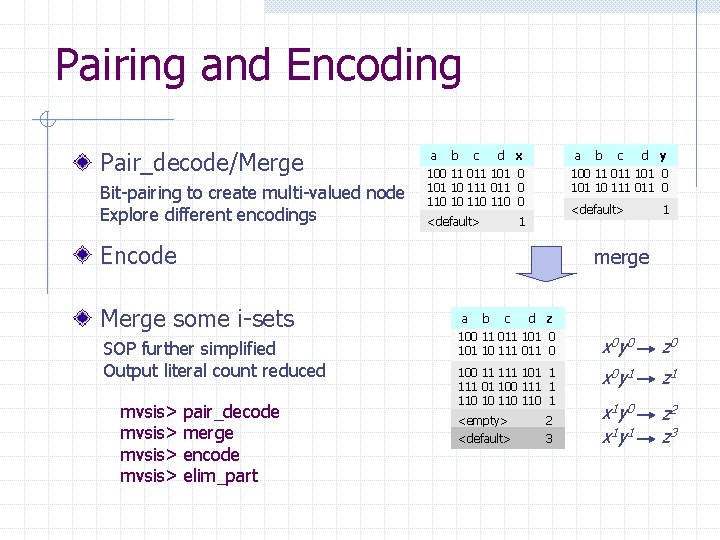

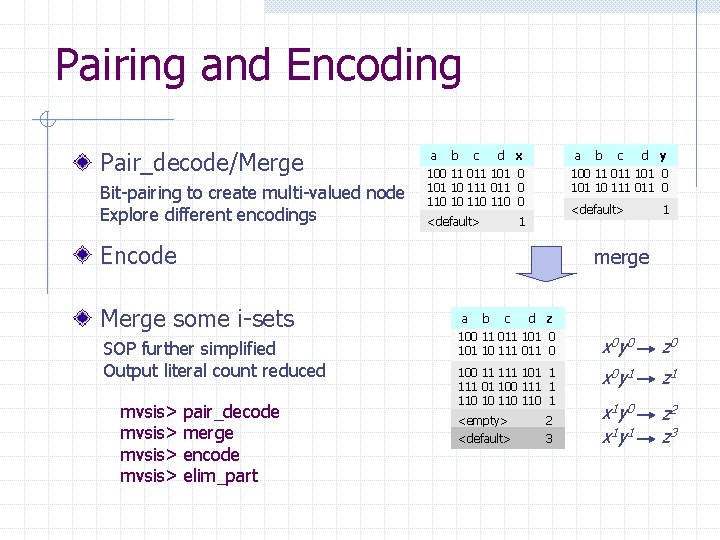

Pairing and Encoding Pair_decode/Merge Bit-pairing to create multi-valued node Explore different encodings a 100 101 110 b 11 10 10 c 011 110 d 101 011 110 <default> x 0 0 0 a b c d y 100 11 011 101 0 101 10 111 0 <default> 1 Encode merge Merge some i-sets SOP further simplified Output literal count reduced mvsis> 1 pair_decode merge encode elim_part a b c d z 100 11 011 101 0 101 10 111 0 x 0 y 0 z 0 100 11 101 1 111 01 100 111 1 110 10 110 1 x 0 y 1 z 1 x 1 y 0 x 1 y 1 z 2 z 3 <empty> <default> 2 3

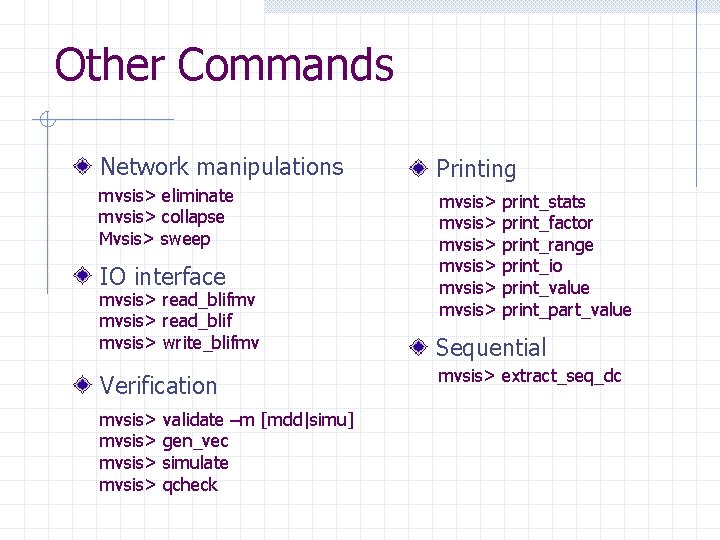

Other Commands Network manipulations Printing mvsis> eliminate mvsis> collapse Mvsis> sweep mvsis> mvsis> IO interface mvsis> read_blifmv mvsis> read_blif mvsis> write_blifmv Verification mvsis> validate –m [mdd|simu] gen_vec simulate qcheck print_stats print_factor print_range print_io print_value print_part_value Sequential mvsis> extract_seq_dc

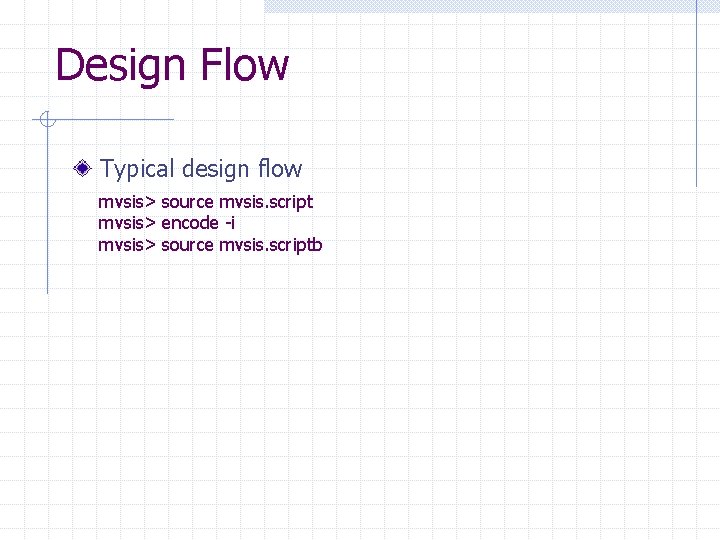

Design Flow Typical design flow mvsis> source mvsis. script mvsis> encode -i mvsis> source mvsis. scriptb

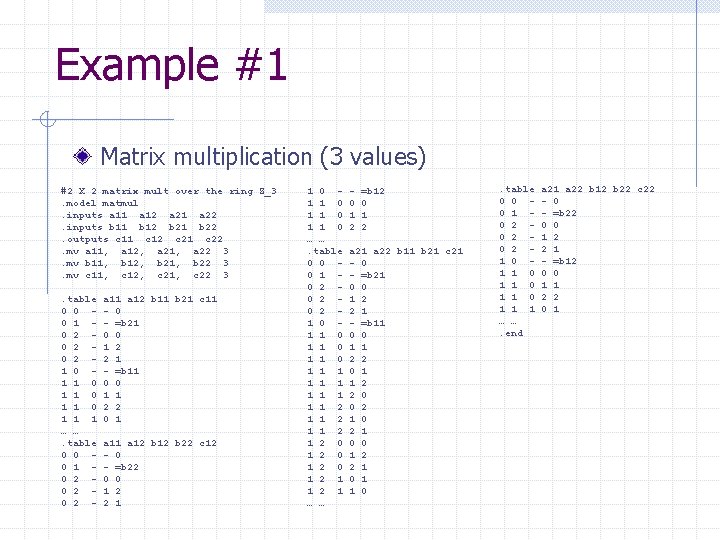

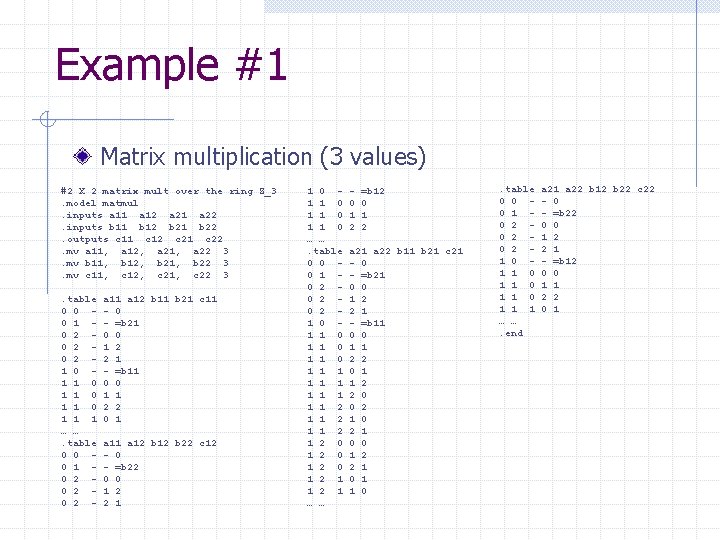

Example #1 Matrix multiplication (3 values) #2 X 2 matrix mult over the ring Z_3. model matmul. inputs a 11 a 12 a 21 a 22. inputs b 11 b 12 b 21 b 22. outputs c 11 c 12 c 21 c 22. mv a 11, a 12, a 21, a 22 3. mv b 11, b 12, b 21, b 22 3. mv c 11, c 12, c 21, c 22 3. table 0 0 0 1 0 2 0 2 1 0 1 1 1 … …. table 0 0 0 1 0 2 0 2 - a 11 a 12 b 11 b 21 c 11 - 0 - =b 21 0 0 1 2 2 1 - =b 11 0 0 1 1 2 2 0 1 a 12 b 22 c 12 - 0 - =b 22 0 0 1 2 2 1 1 0 … …. table 0 0 0 1 0 2 0 2 1 0 1 1 1 1 1 1 2 1 2 0 1 2 1 … … 0 1 2 =b 12 0 1 2 a 21 a 22 b 11 b 21 c 21 - 0 - =b 21 0 0 1 2 2 1 - =b 11 0 0 1 1 2 2 0 0 2 1 0 0 1 2 2 1 0 1 1 0 . table 0 0 0 1 0 2 0 2 1 0 1 1 1 … …. end a 21 a 22 b 12 b 22 c 22 - 0 - =b 22 0 0 1 2 2 1 - =b 12 0 0 1 1 2 2 0 1

![cadntws 11 homewjiangmvsisexamplesbob mvsis UC Berkeley MVSIS 0 95 compiled 24 May01 at 2 [cadntws 11: /home/wjiang/mvsis/examples/bob] mvsis UC Berkeley, MVSIS 0. 95 (compiled 24 -May-01 at 2:](https://slidetodoc.com/presentation_image_h/250a746c9662d9fcb379ae88ef6f8ef4/image-17.jpg)

[cadntws 11: /home/wjiang/mvsis/examples/bob] mvsis UC Berkeley, MVSIS 0. 95 (compiled 24 -May-01 at 2: 19 PM) mvsis> help alias chng_name collapse decomp delete echo elim_part eliminate encode extract_seq_dc factor fullsimp fx gen_vec help history merge pair_decode print_altname print_factor print_io print_level print_part_value print_range print_stats print_value qcheck quit read_blifmv reset_default reset_name resub runtime set simplify simulate source sweep unalias undo unset usage validate write_blifmv mvsis> read_blifmv matmul-c mvsis> chng_name changing to short-name mode mvsis> print_stats matmul: 4 nodes, 4 POs, 128 cubes(sop), 480 lits(sop) mvsis>

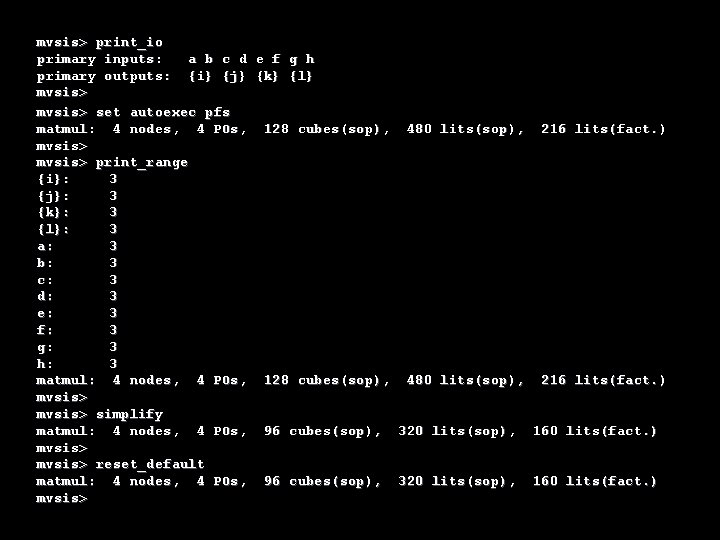

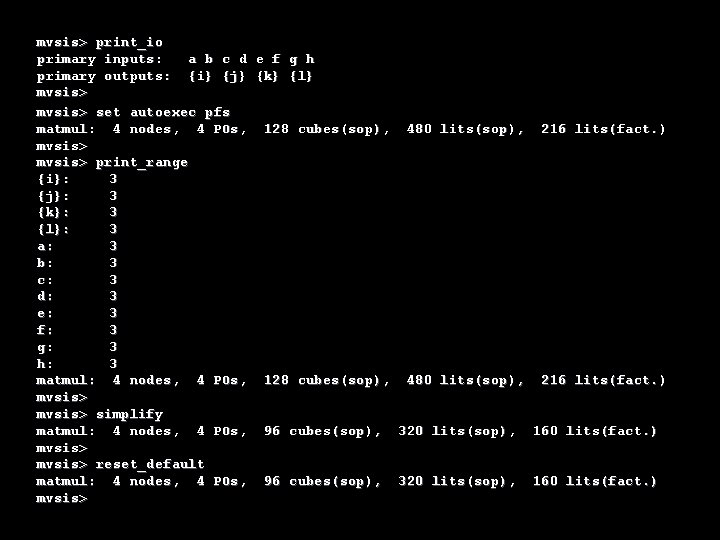

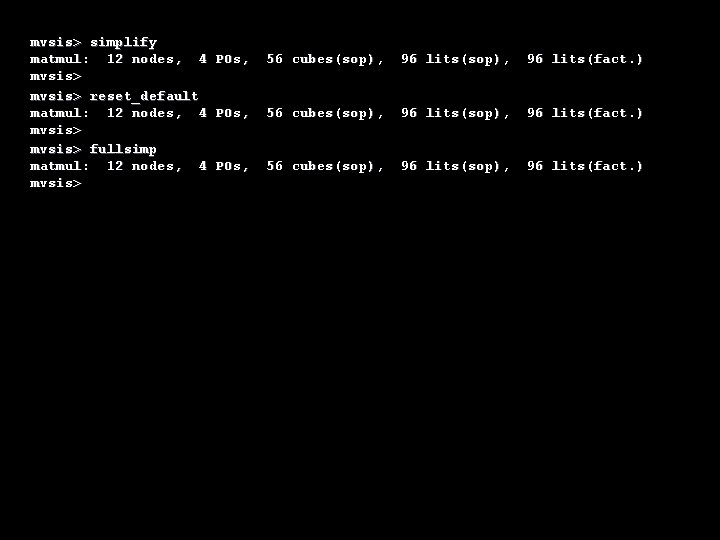

mvsis> print_io primary inputs: a b c d e f g h primary outputs: {i} {j} {k} {l} mvsis> set autoexec pfs matmul: 4 nodes, 4 POs, 128 cubes(sop), 480 lits(sop), 216 lits(fact. ) mvsis> print_range {i}: 3 {j}: 3 {k}: 3 {l}: 3 a: 3 b: 3 c: 3 d: 3 e: 3 f: 3 g: 3 h: 3 matmul: 4 nodes, 4 POs, 128 cubes(sop), 480 lits(sop), 216 lits(fact. ) mvsis> simplify matmul: 4 nodes, 4 POs, 96 cubes(sop), 320 lits(sop), 160 lits(fact. ) mvsis> reset_default matmul: 4 nodes, 4 POs, 96 cubes(sop), 320 lits(sop), 160 lits(fact. ) mvsis>

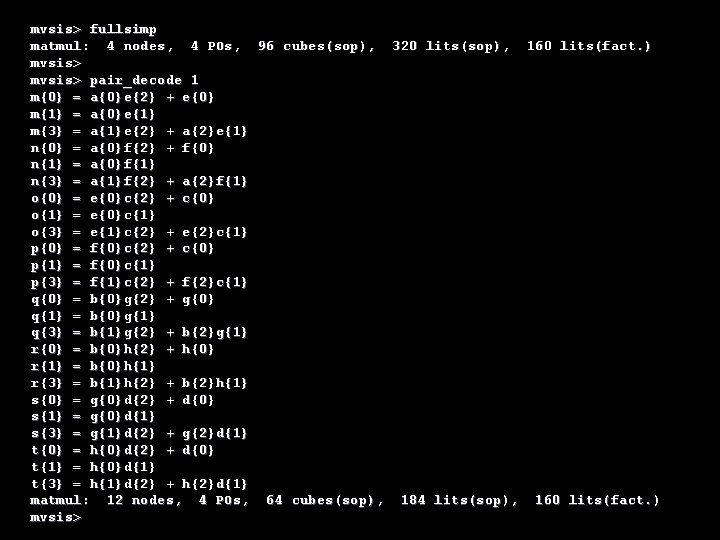

mvsis> fullsimp matmul: 4 nodes, 4 POs, 96 cubes(sop), 320 lits(sop), 160 lits(fact. ) mvsis> pair_decode 1 m{0} = a{0}e{2} + e{0} m{1} = a{0}e{1} m{3} = a{1}e{2} + a{2}e{1} n{0} = a{0}f{2} + f{0} n{1} = a{0}f{1} n{3} = a{1}f{2} + a{2}f{1} o{0} = e{0}c{2} + c{0} o{1} = e{0}c{1} o{3} = e{1}c{2} + e{2}c{1} p{0} = f{0}c{2} + c{0} p{1} = f{0}c{1} p{3} = f{1}c{2} + f{2}c{1} q{0} = b{0}g{2} + g{0} q{1} = b{0}g{1} q{3} = b{1}g{2} + b{2}g{1} r{0} = b{0}h{2} + h{0} r{1} = b{0}h{1} r{3} = b{1}h{2} + b{2}h{1} s{0} = g{0}d{2} + d{0} s{1} = g{0}d{1} s{3} = g{1}d{2} + g{2}d{1} t{0} = h{0}d{2} + d{0} t{1} = h{0}d{1} t{3} = h{1}d{2} + h{2}d{1} matmul: 12 nodes, 4 POs, 64 cubes(sop), 184 lits(sop), 160 lits(fact. ) mvsis>

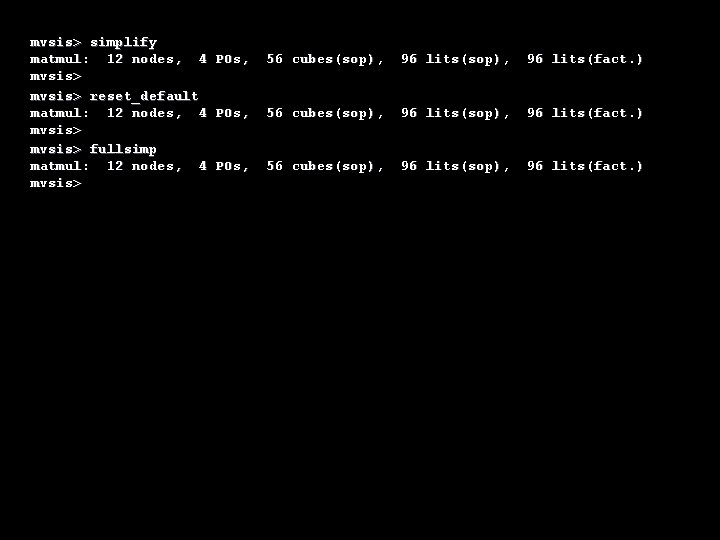

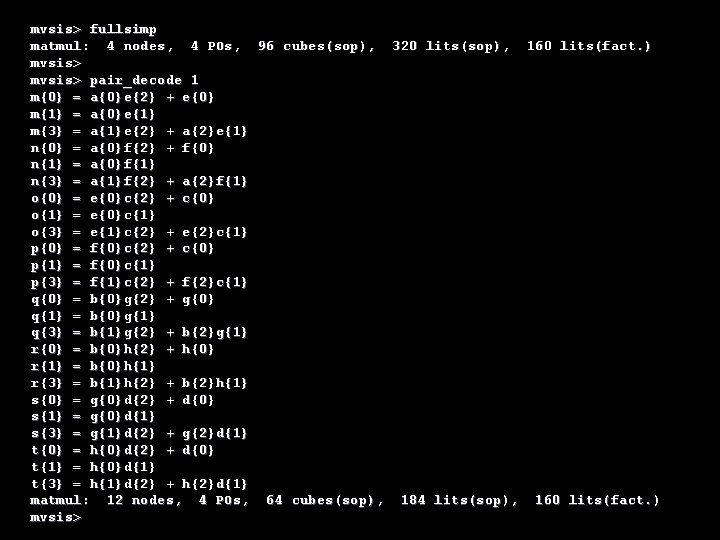

mvsis> simplify matmul: 12 nodes, 4 POs, mvsis> reset_default matmul: 12 nodes, 4 POs, mvsis> fullsimp matmul: 12 nodes, 4 POs, mvsis> 56 cubes(sop), 96 lits(sop), 96 lits(fact. ) 56 cubes(sop), 96 lits(fact. )

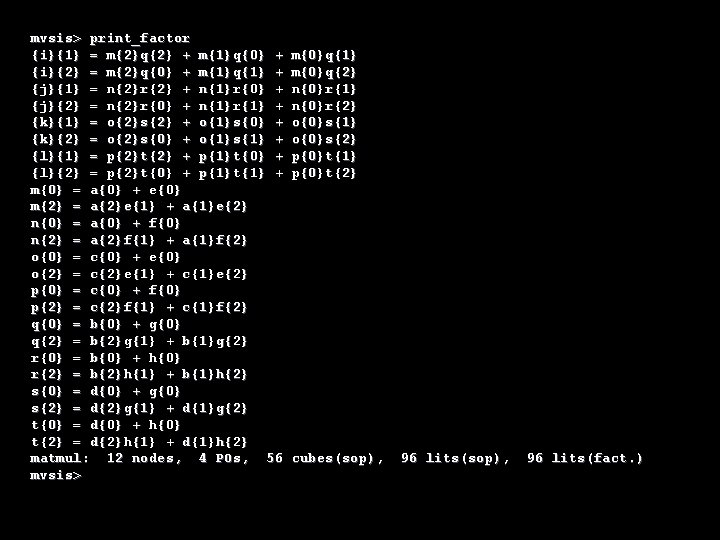

mvsis> print_factor {i}{1} = m{2}q{2} + m{1}q{0} + {i}{2} = m{2}q{0} + m{1}q{1} + {j}{1} = n{2}r{2} + n{1}r{0} + {j}{2} = n{2}r{0} + n{1}r{1} + {k}{1} = o{2}s{2} + o{1}s{0} + {k}{2} = o{2}s{0} + o{1}s{1} + {l}{1} = p{2}t{2} + p{1}t{0} + {l}{2} = p{2}t{0} + p{1}t{1} + m{0} = a{0} + e{0} m{2} = a{2}e{1} + a{1}e{2} n{0} = a{0} + f{0} n{2} = a{2}f{1} + a{1}f{2} o{0} = c{0} + e{0} o{2} = c{2}e{1} + c{1}e{2} p{0} = c{0} + f{0} p{2} = c{2}f{1} + c{1}f{2} q{0} = b{0} + g{0} q{2} = b{2}g{1} + b{1}g{2} r{0} = b{0} + h{0} r{2} = b{2}h{1} + b{1}h{2} s{0} = d{0} + g{0} s{2} = d{2}g{1} + d{1}g{2} t{0} = d{0} + h{0} t{2} = d{2}h{1} + d{1}h{2} matmul: 12 nodes, 4 POs, 56 mvsis> m{0}q{1} m{0}q{2} n{0}r{1} n{0}r{2} o{0}s{1} o{0}s{2} p{0}t{1} p{0}t{2} cubes(sop), 96 lits(fact. )

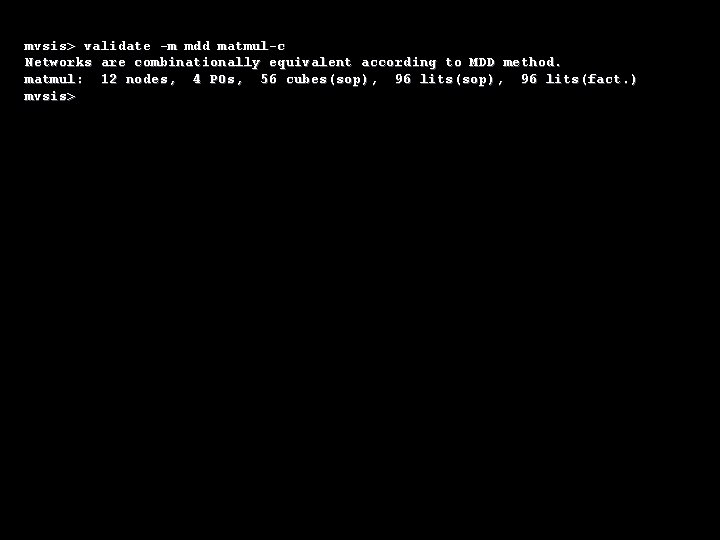

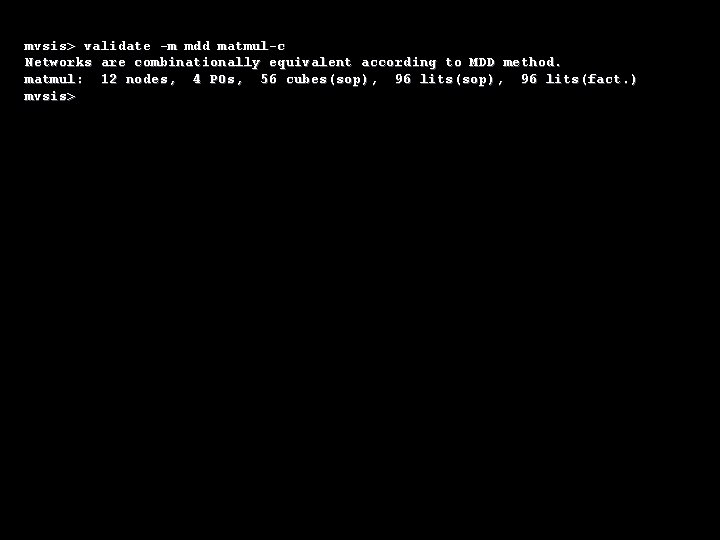

mvsis> validate -m mdd matmul-c Networks are combinationally equivalent according to MDD method. matmul: 12 nodes, 4 POs, 56 cubes(sop), 96 lits(fact. ) mvsis>

![cadntws 11 homewjiangmvsisexamplesbob mvsis UC Berkeley MVSIS 0 95 compiled 24 May01 at 2 [cadntws 11: /home/wjiang/mvsis/examples/bob] mvsis UC Berkeley, MVSIS 0. 95 (compiled 24 -May-01 at 2:](https://slidetodoc.com/presentation_image_h/250a746c9662d9fcb379ae88ef6f8ef4/image-23.jpg)

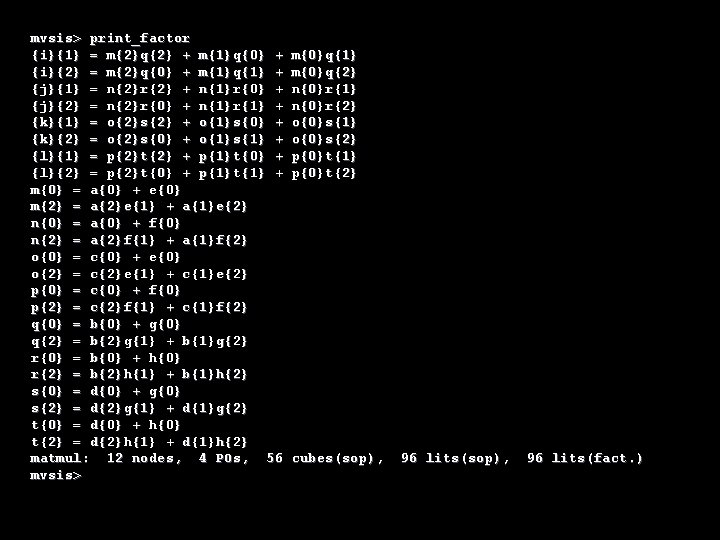

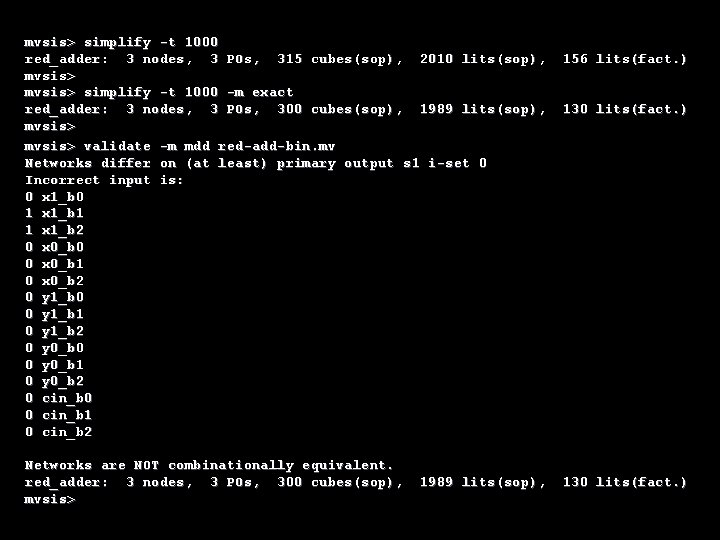

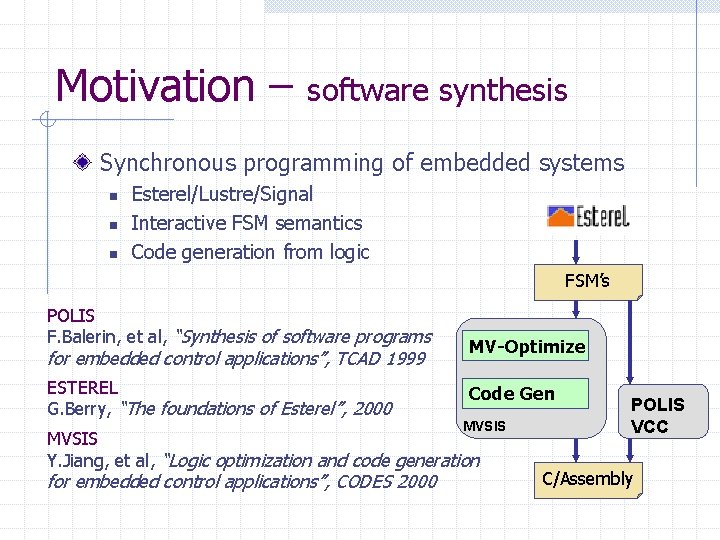

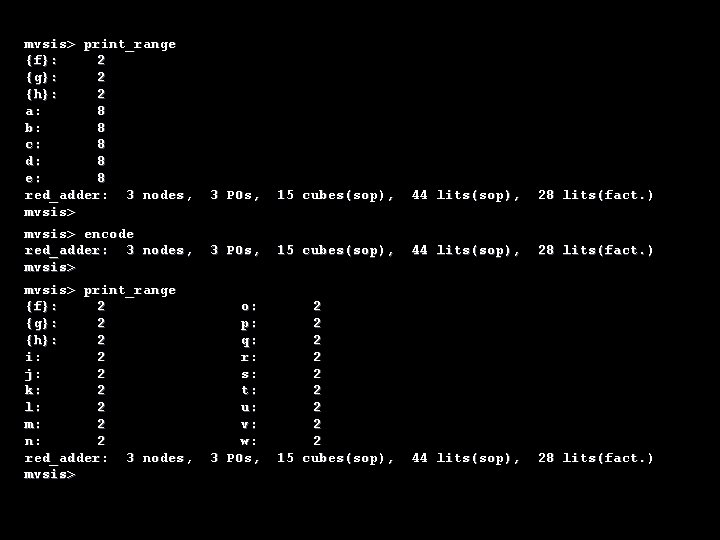

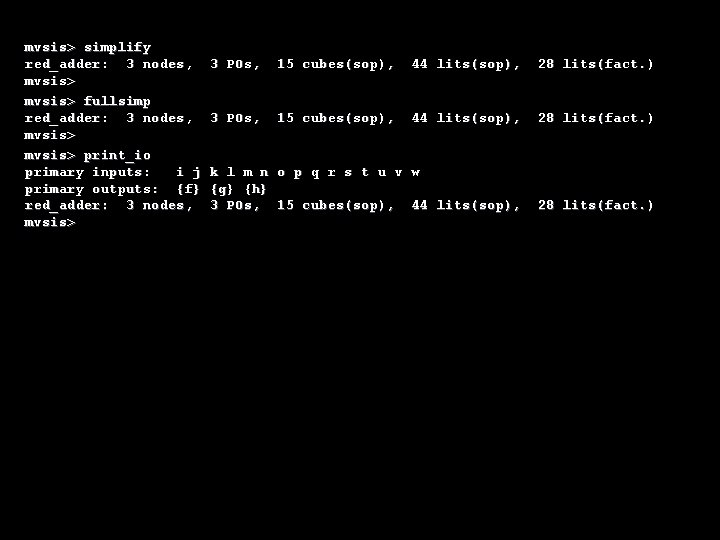

[cadntws 11: /home/wjiang/mvsis/examples/bob] mvsis UC Berkeley, MVSIS 0. 95 (compiled 24 -May-01 at 2: 19 PM) mvsis> read_blifmv red-add. mv mvsis> chng_name changing to short-name mode mvsis> print_io primary inputs: a b c d e primary outputs: {f} {g} {h} mvsis> set autoexec pfs red_adder: 3 nodes, 3 POs, 48 cubes(sop), 240 lits(sop), 69 lits(fact. ) mvsis> reset_default red_adder: 3 nodes, 3 POs, 48 cubes(sop), 240 lits(sop), 69 lits(fact. ) mvsis> simplify red_adder: 3 nodes, 3 POs, 15 cubes(sop), 44 lits(sop), 28 lits(fact. ) mvsis> fullsimp red_adder: 3 nodes, 3 POs, 15 cubes(sop), 44 lits(sop), 28 lits(fact. ) mvsis>

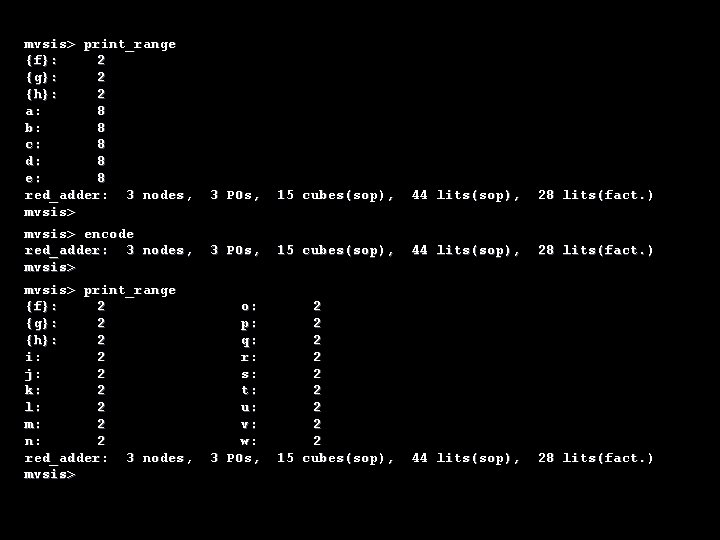

mvsis> print_range {f}: 2 {g}: 2 {h}: 2 a: 8 b: 8 c: 8 d: 8 e: 8 red_adder: 3 nodes, mvsis> 3 POs, 15 cubes(sop), 44 lits(sop), 28 lits(fact. ) mvsis> encode red_adder: 3 nodes, mvsis> 3 POs, 15 cubes(sop), 44 lits(sop), 28 lits(fact. ) mvsis> print_range {f}: 2 {g}: 2 {h}: 2 i: 2 j: 2 k: 2 l: 2 m: 2 n: 2 red_adder: 3 nodes, mvsis> o: p: q: r: s: t: u: v: w: 3 POs, 2 2 2 2 2 15 cubes(sop), 44 lits(sop), 28 lits(fact. )

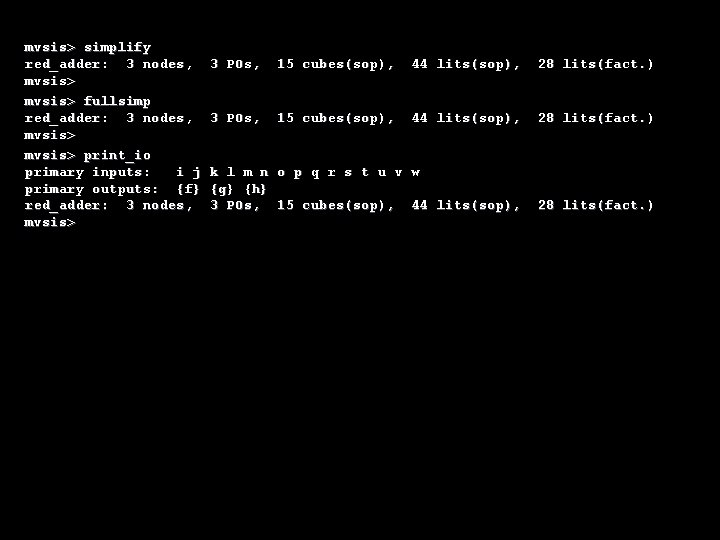

mvsis> simplify red_adder: 3 nodes, mvsis> fullsimp red_adder: 3 nodes, mvsis> print_io primary inputs: i j primary outputs: {f} red_adder: 3 nodes, mvsis> 3 POs, 15 cubes(sop), 44 lits(sop), 28 lits(fact. ) k l m n o p q r s t u v w {g} {h} 3 POs, 15 cubes(sop), 44 lits(sop), 28 lits(fact. )

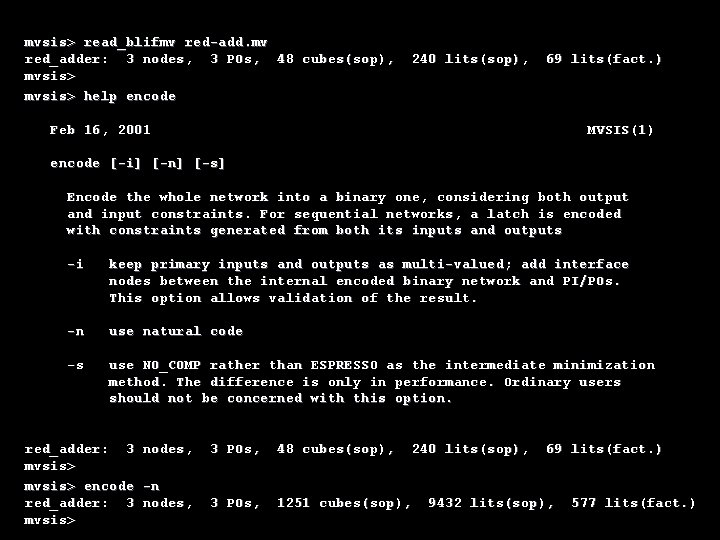

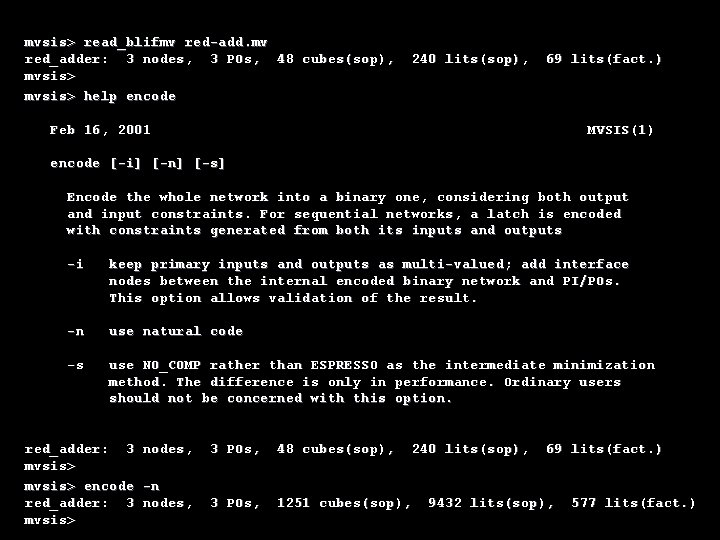

mvsis> read_blifmv red-add. mv red_adder: 3 nodes, 3 POs, 48 cubes(sop), mvsis> help encode 240 lits(sop), 69 lits(fact. ) Feb 16, 2001 MVSIS(1) encode [-i] [-n] [-s] Encode the whole network into a binary one, considering both output and input constraints. For sequential networks, a latch is encoded with constraints generated from both its inputs and outputs -i keep primary inputs and outputs as multi-valued; add interface nodes between the internal encoded binary network and PI/POs. This option allows validation of the result. -n use natural code -s use NO_COMP rather than ESPRESSO as the intermediate minimization method. The difference is only in performance. Ordinary users should not be concerned with this option. red_adder: 3 nodes, mvsis> encode -n red_adder: 3 nodes, mvsis> 3 POs, 48 cubes(sop), 240 lits(sop), 3 POs, 1251 cubes(sop), 69 lits(fact. ) 9432 lits(sop), 577 lits(fact. )

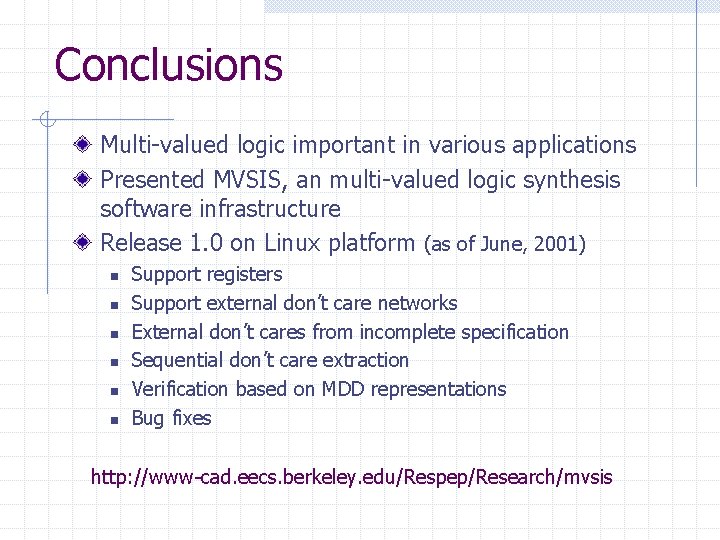

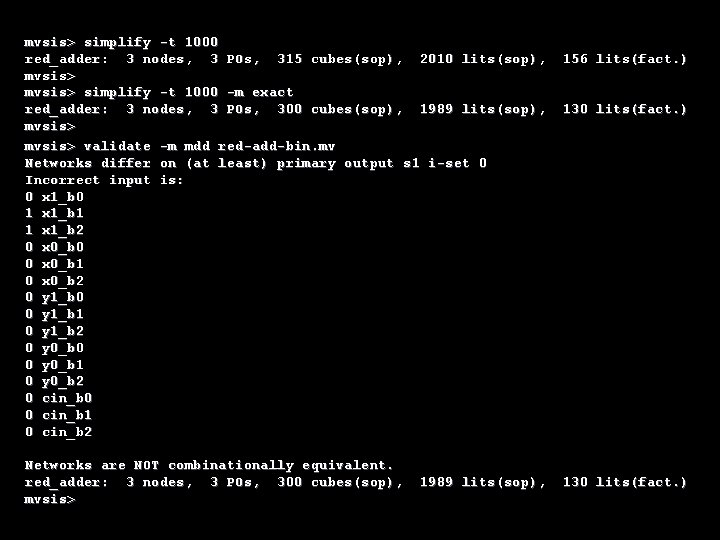

mvsis> simplify -t 1000 red_adder: 3 nodes, 3 POs, 315 cubes(sop), 2010 lits(sop), mvsis> simplify -t 1000 -m exact red_adder: 3 nodes, 3 POs, 300 cubes(sop), 1989 lits(sop), mvsis> validate -m mdd red-add-bin. mv Networks differ on (at least) primary output s 1 i-set 0 Incorrect input is: 0 x 1_b 0 1 x 1_b 1 1 x 1_b 2 0 x 0_b 0 0 x 0_b 1 0 x 0_b 2 0 y 1_b 0 0 y 1_b 1 0 y 1_b 2 0 y 0_b 0 0 y 0_b 1 0 y 0_b 2 0 cin_b 0 0 cin_b 1 0 cin_b 2 Networks are NOT combinationally equivalent. red_adder: 3 nodes, 3 POs, 300 cubes(sop), mvsis> 1989 lits(sop), 156 lits(fact. ) 130 lits(fact. )

Conclusions Multi-valued logic important in various applications Presented MVSIS, an multi-valued logic synthesis software infrastructure Release 1. 0 on Linux platform (as of June, 2001) n n n Support registers Support external don’t care networks External don’t cares from incomplete specification Sequential don’t care extraction Verification based on MDD representations Bug fixes http: //www-cad. eecs. berkeley. edu/Respep/Research/mvsis