Multiprocessor Multicomputer Motherboard CPU Multicore multiprocessor multicomputer Computer

Multiprocessor & Multicomputer

Motherboard

CPU

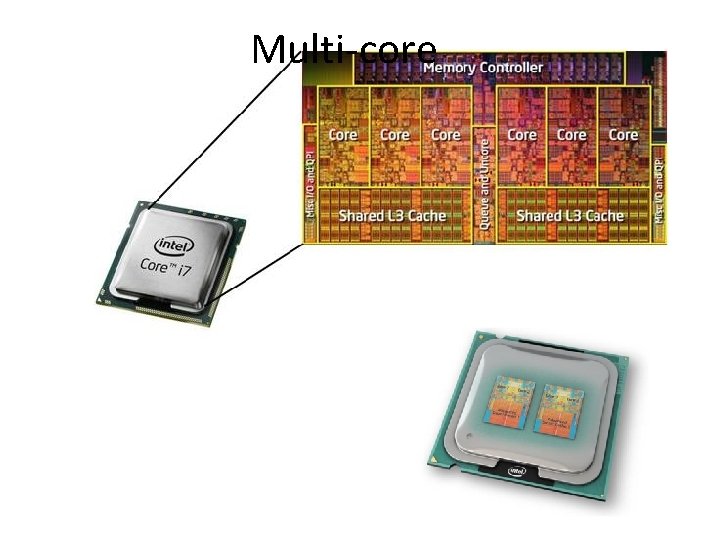

Multi-core

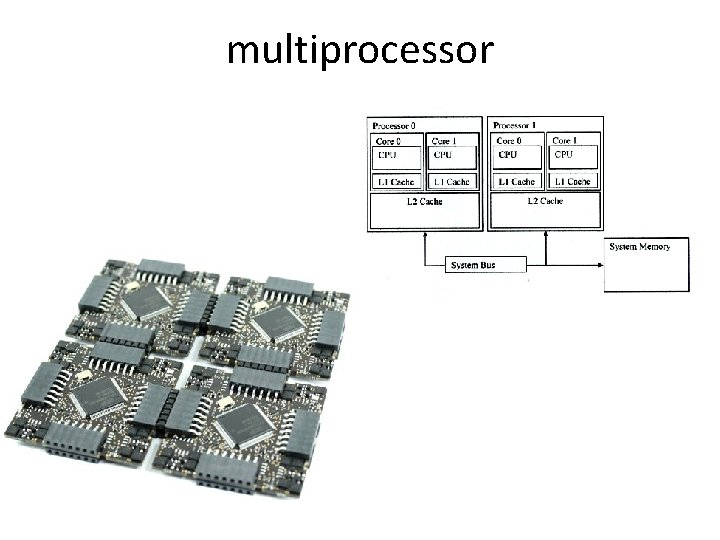

multiprocessor

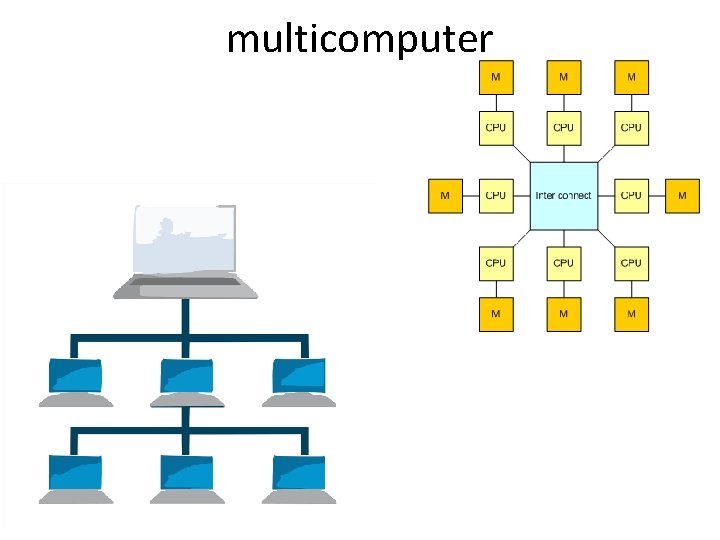

multicomputer

Computer Arithmetic

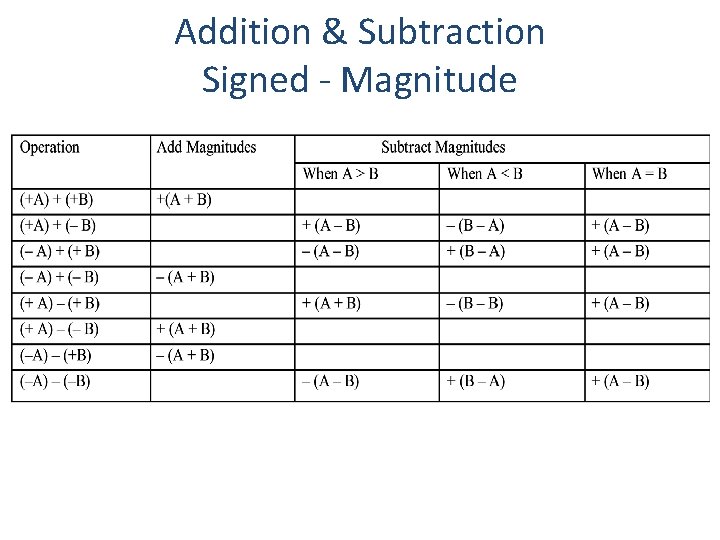

Addition & Subtraction Signed - Magnitude

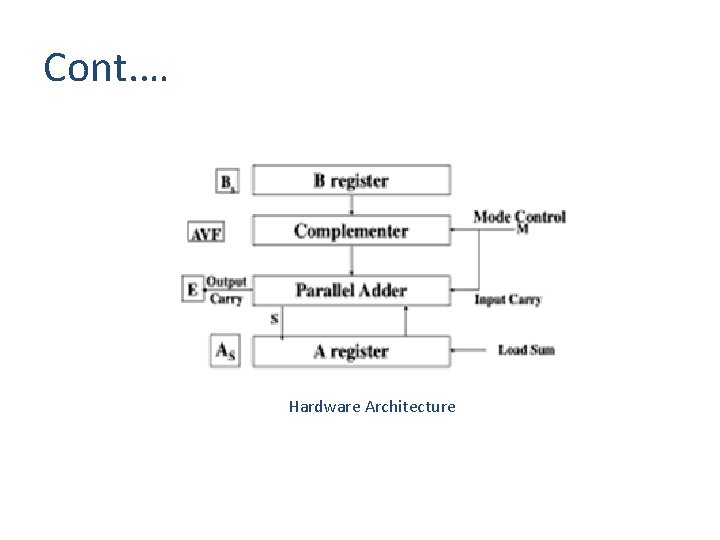

Cont. … Hardware Architecture

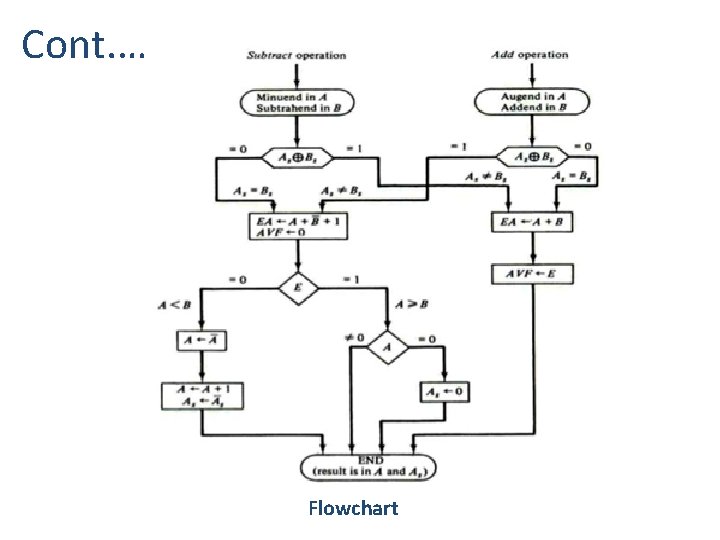

Cont. … Flowchart

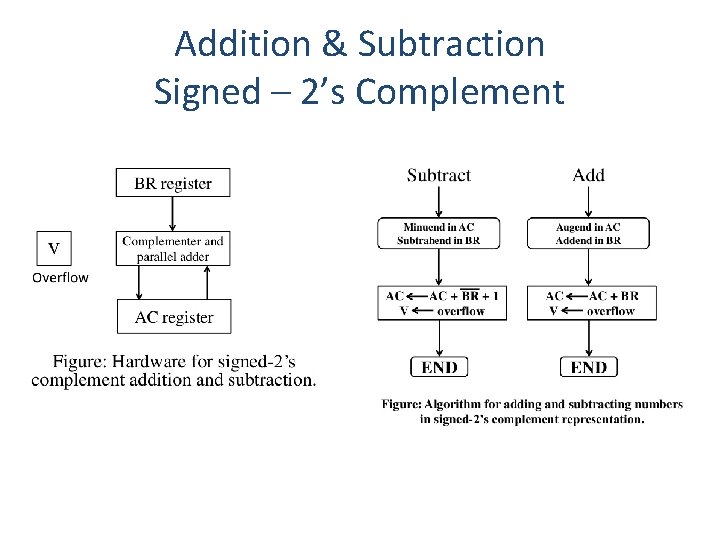

Addition & Subtraction Signed – 2’s Complement

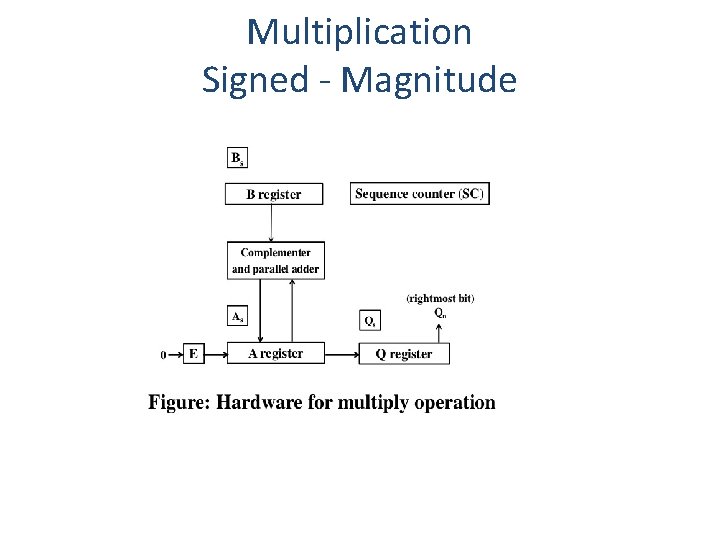

Multiplication Signed - Magnitude

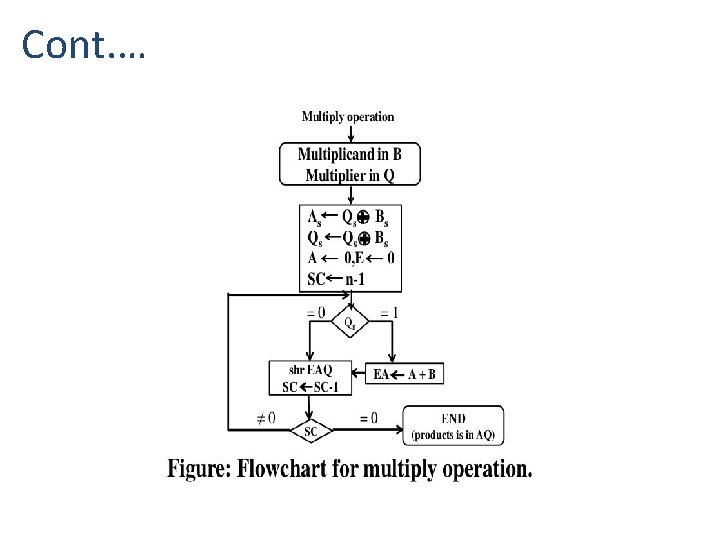

Cont. …

Cont. … Example Number 1 X Number 2 Multiplicand in B Multiplier in Q shr(EAQ) Final Product in AQ E A Q SC

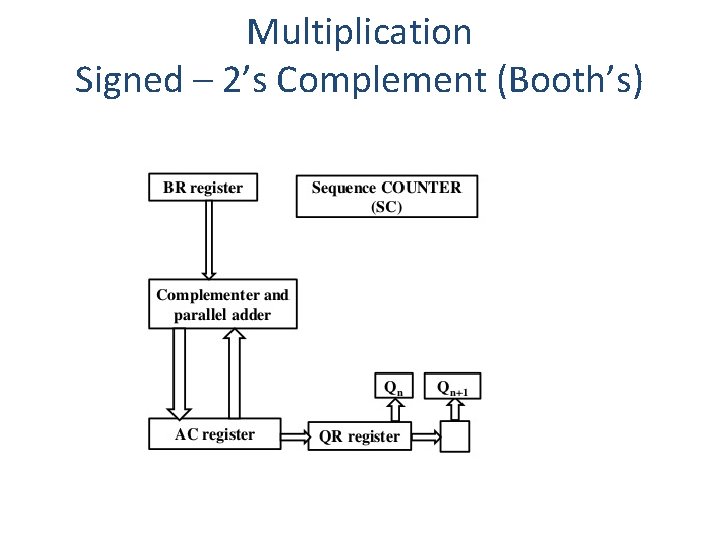

Multiplication Signed – 2’s Complement (Booth’s)

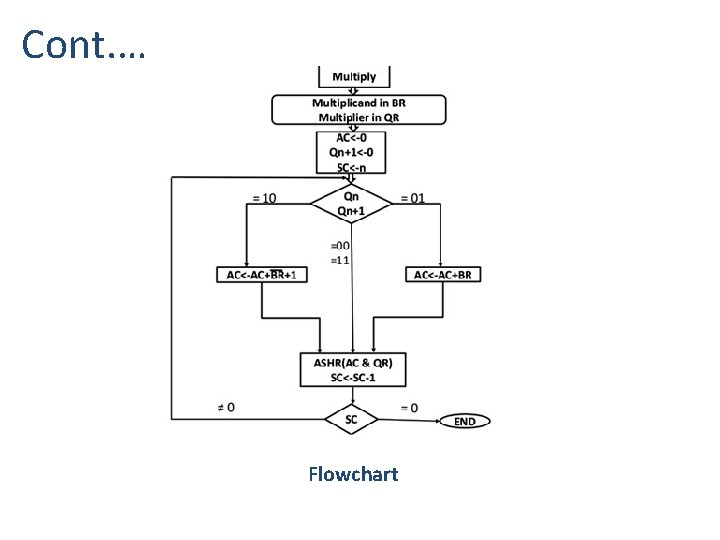

Cont. … Flowchart

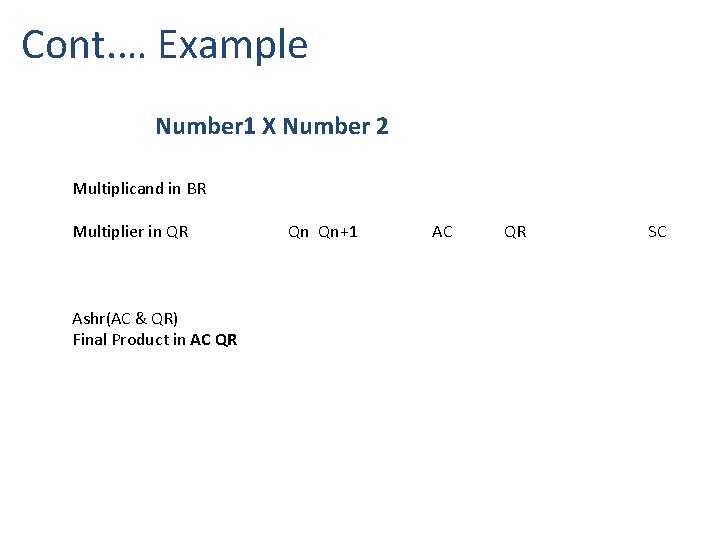

Cont. … Example Number 1 X Number 2 Multiplicand in BR Multiplier in QR Ashr(AC & QR) Final Product in AC QR Qn Qn+1 AC QR SC

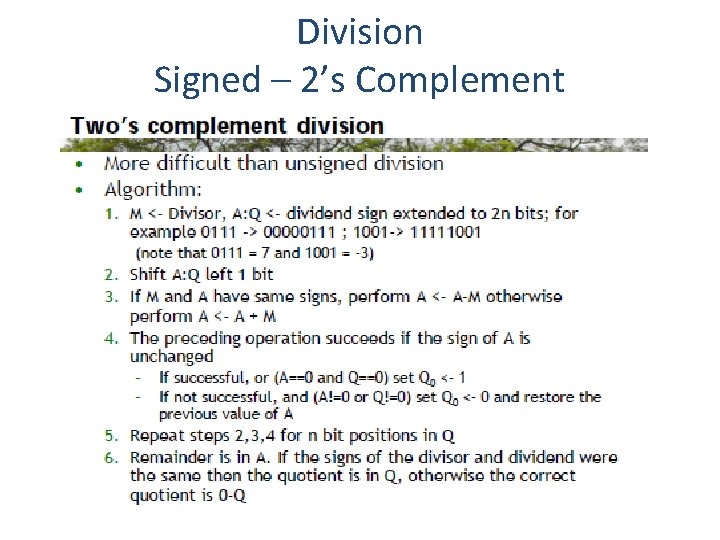

Division Signed – 2’s Complement

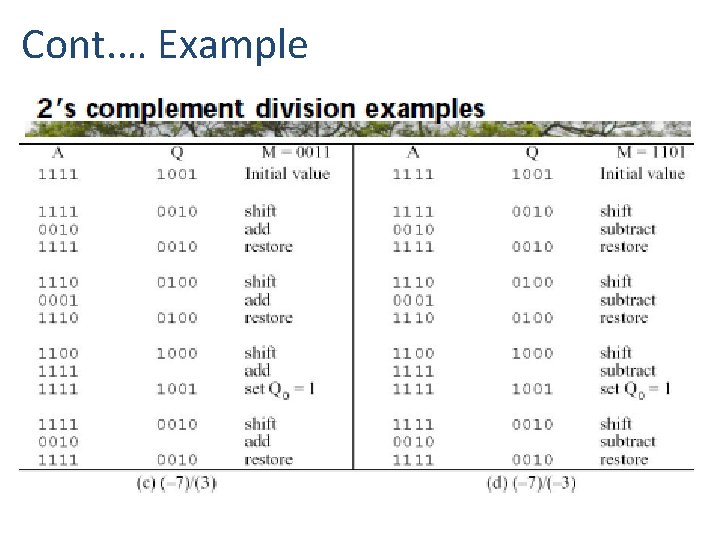

Cont. … Example

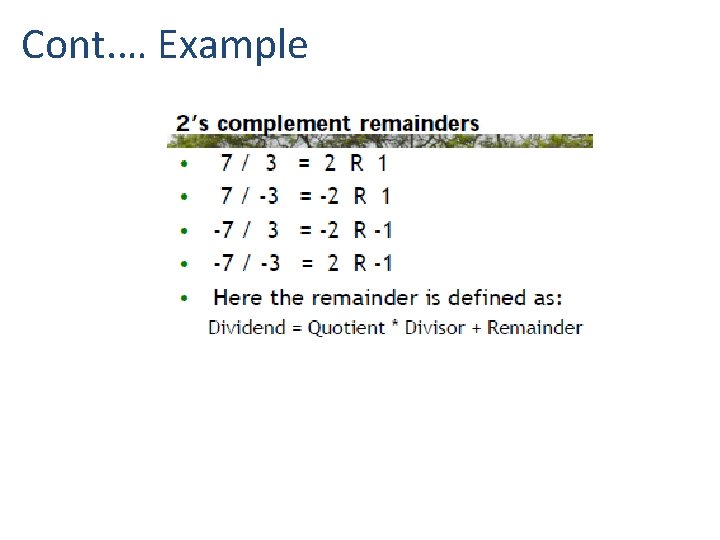

Cont. … Example

Cont. … Example

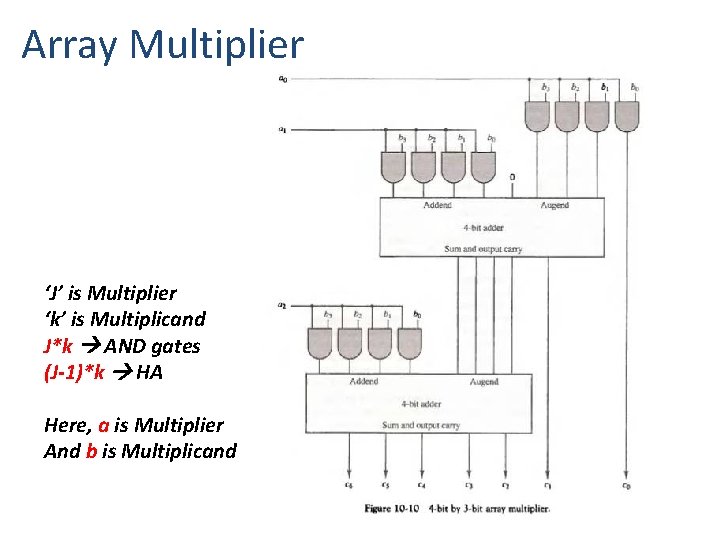

Array Multiplier ‘J’ is Multiplier ‘k’ is Multiplicand J*k AND gates (J-1)*k HA Here, a is Multiplier And b is Multiplicand

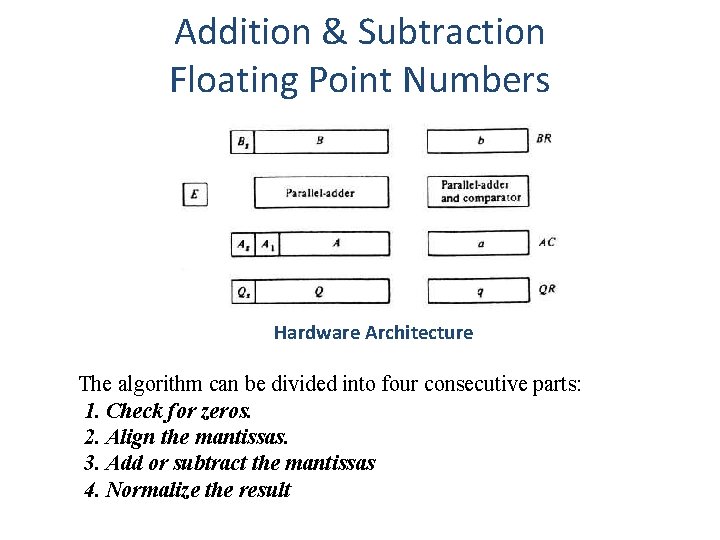

Addition & Subtraction Floating Point Numbers Hardware Architecture The algorithm can be divided into four consecutive parts: 1. Check for zeros. 2. Align the mantissas. 3. Add or subtract the mantissas 4. Normalize the result

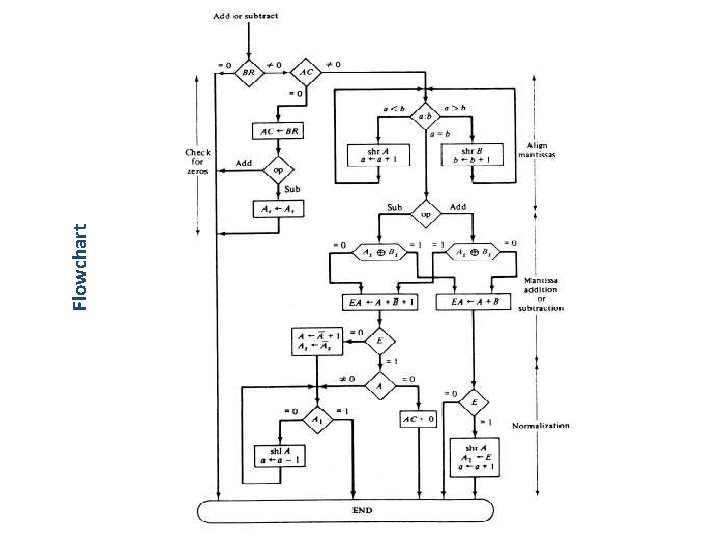

Flowchart

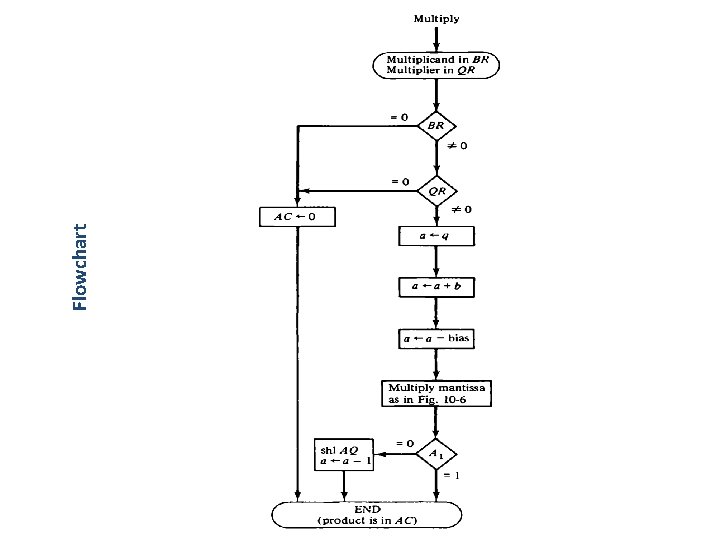

Multiplication Floating Point Numbers The algorithm can be divided into four consecutive parts: 1. Check for zeros. 2. Add the Exponents. 3. Multiply the mantissas. 4. Normalize the Product.

Flowchart

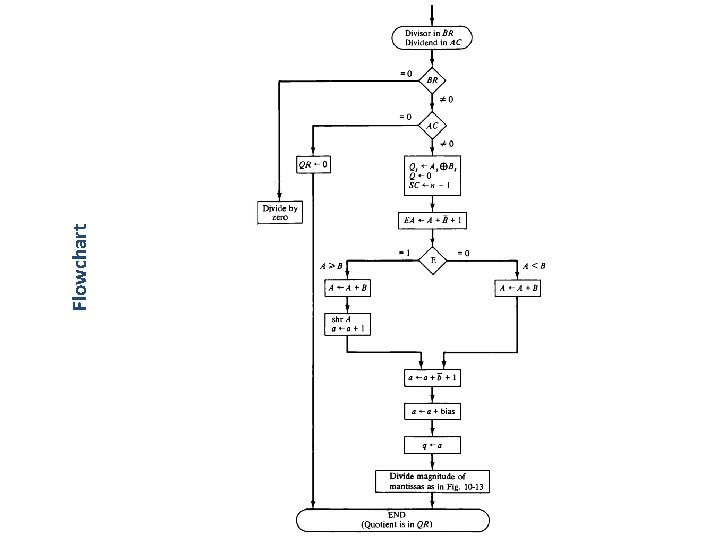

Division Floating Point Numbers The algorithm can be divided into four consecutive parts: 1. Check for zeros. 2. Subtract the Exponents. 3. Divide the mantissas.

Flowchart

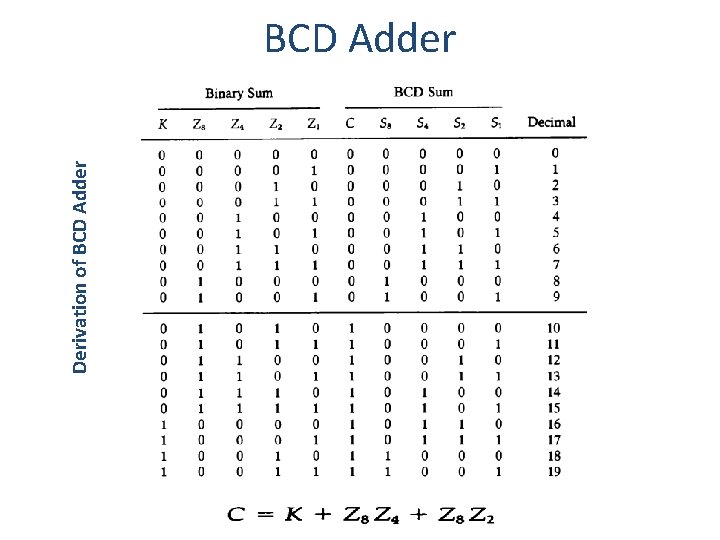

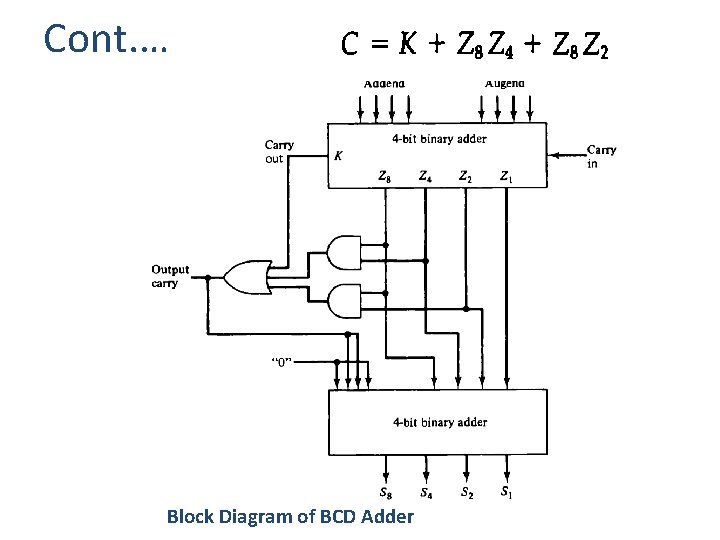

Derivation of BCD Adder

Cont. … Block Diagram of BCD Adder

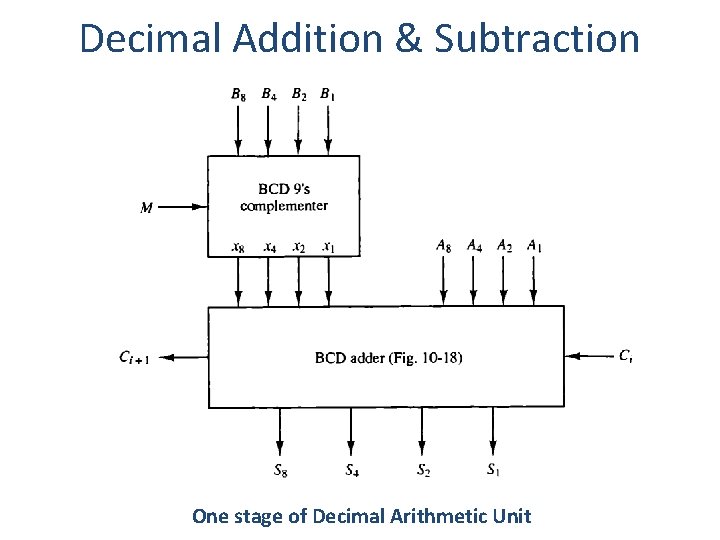

Decimal Addition & Subtraction One stage of Decimal Arithmetic Unit

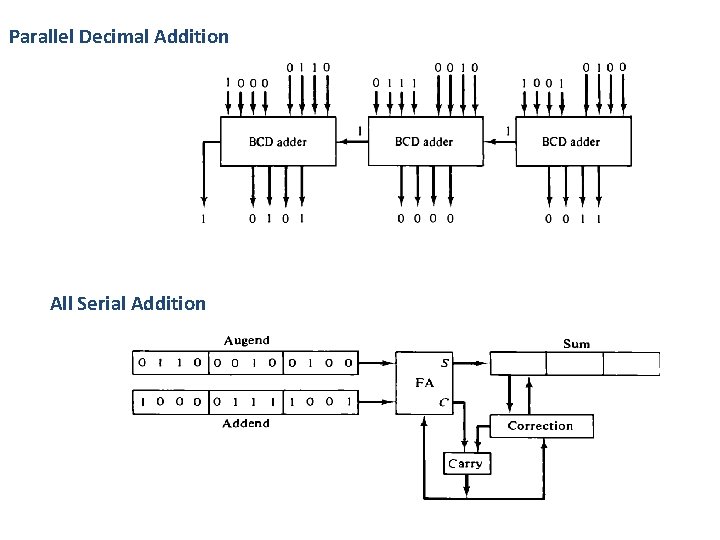

Parallel Decimal Addition All Serial Addition

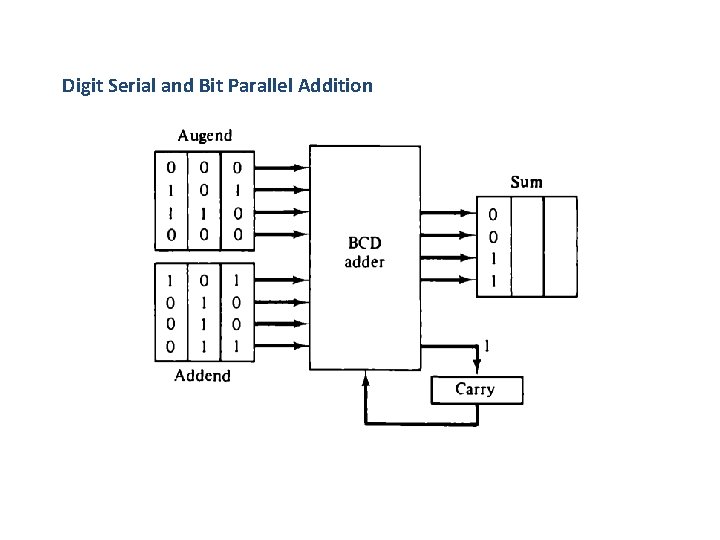

Digit Serial and Bit Parallel Addition

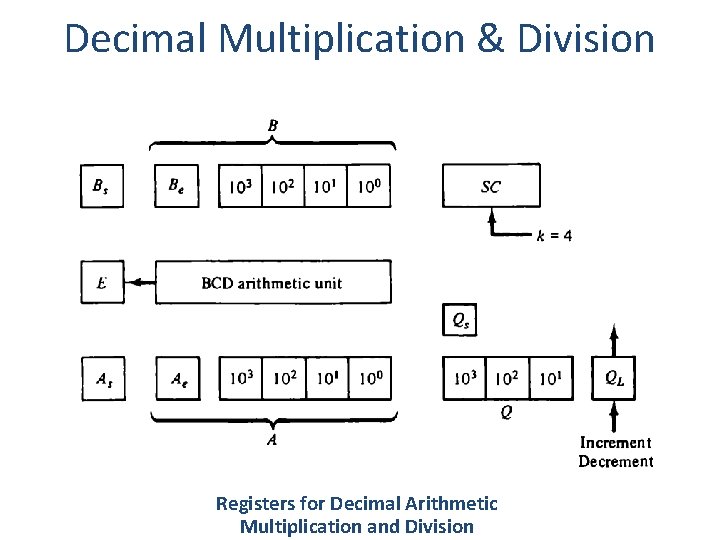

Decimal Multiplication & Division Registers for Decimal Arithmetic Multiplication and Division

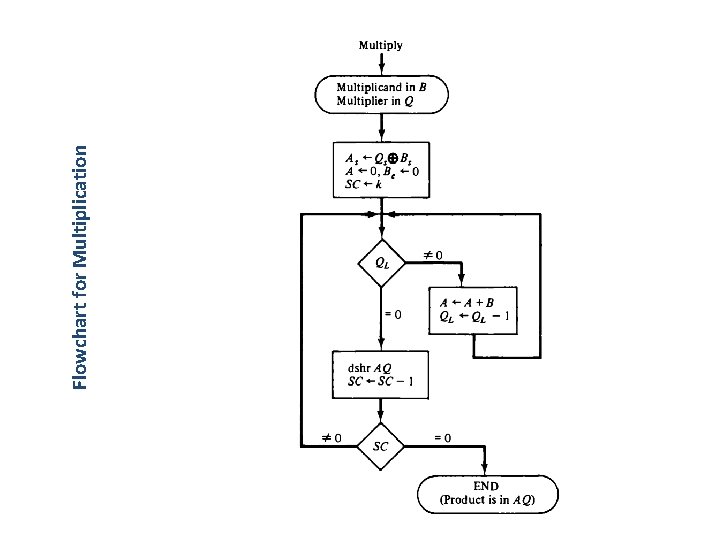

Flowchart for Multiplication

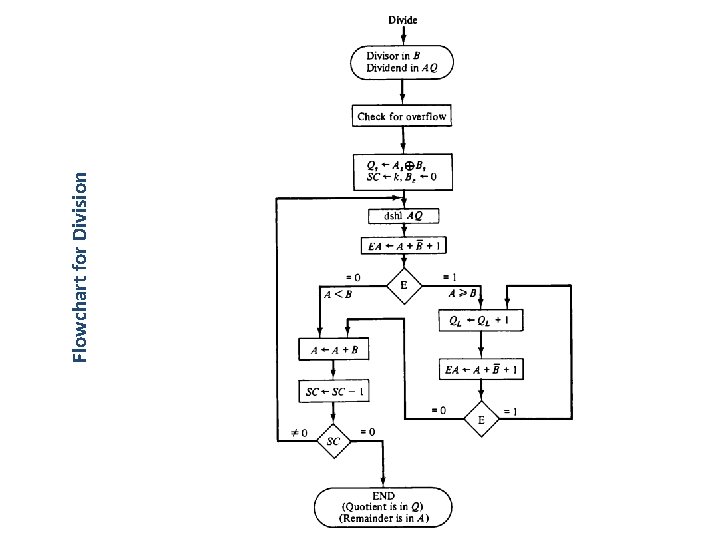

Flowchart for Division

- Slides: 37