Multiplier Functions Discussion D 7 2 Example 19

- Slides: 23

Multiplier: Functions Discussion D 7. 2 Example 19

Multiplier • • Binary Multiplication A VHDL Multiplier The Multiplication Operator A Multiplication Function

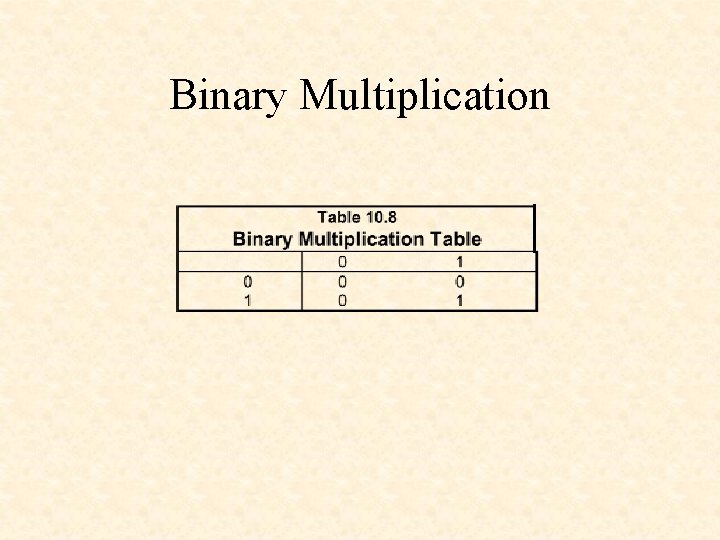

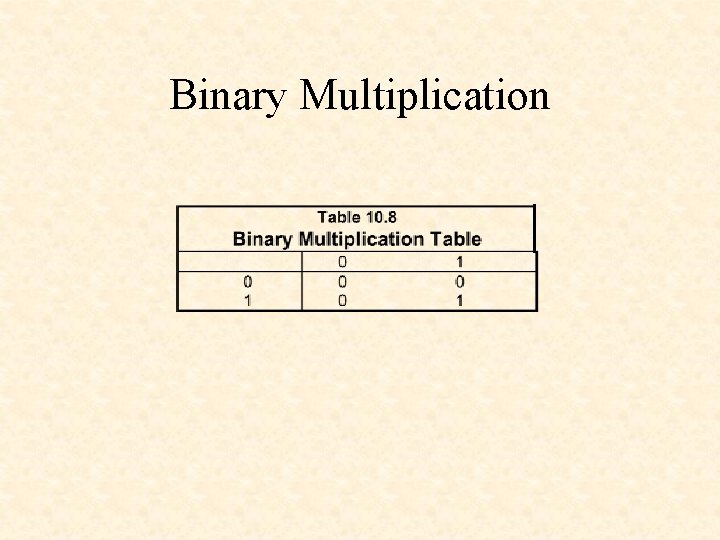

Binary Multiplication

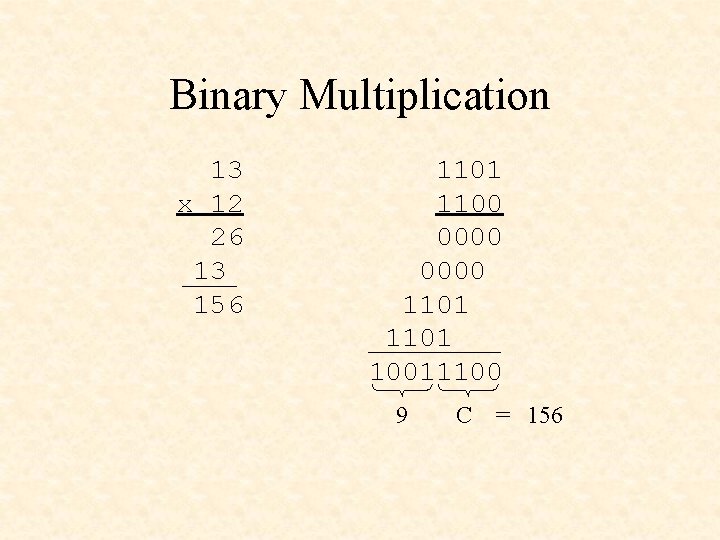

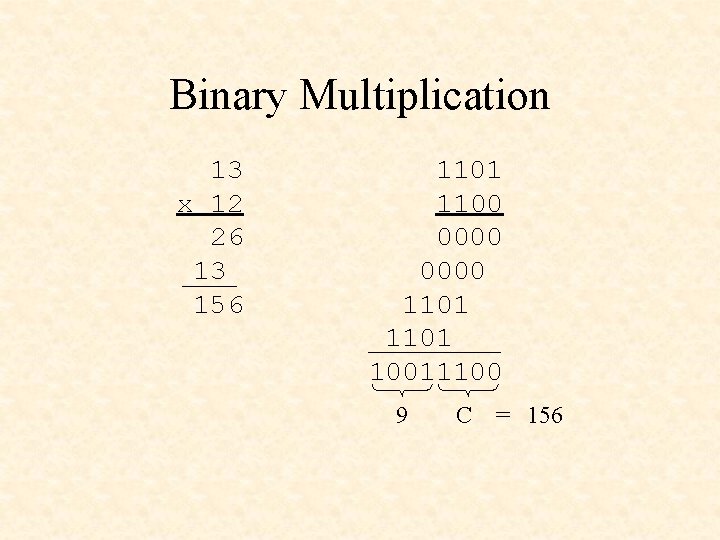

Binary Multiplication 13 x 12 26 13 156 1101 1100 0000 1101 10011100 9 C = 156

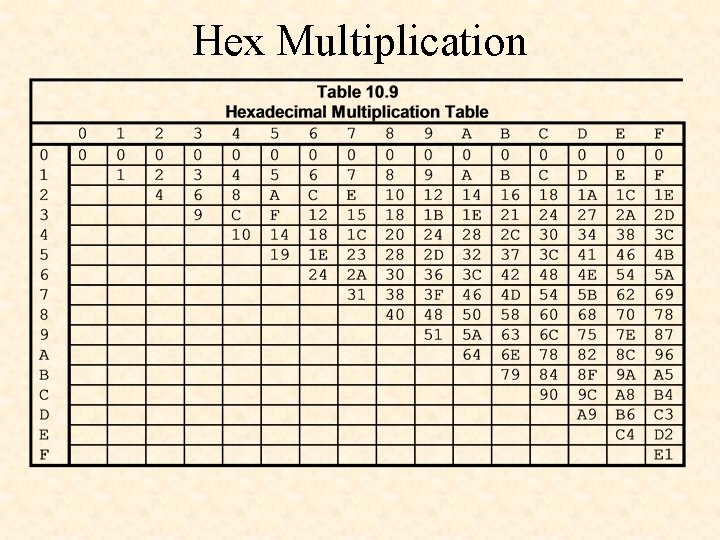

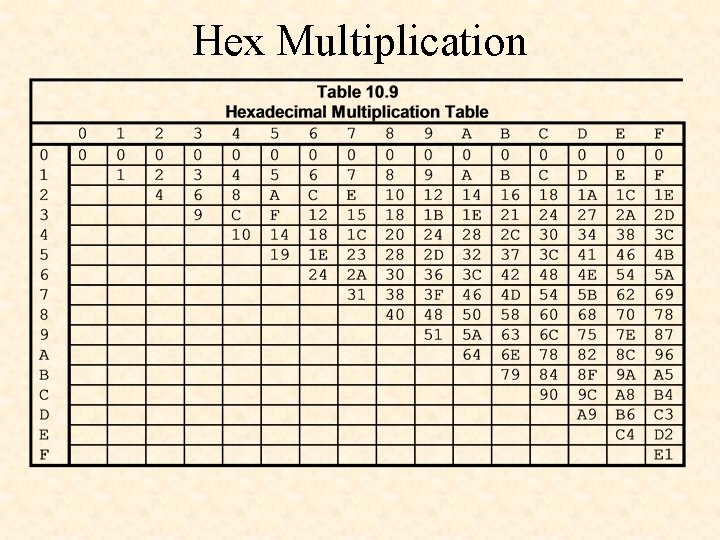

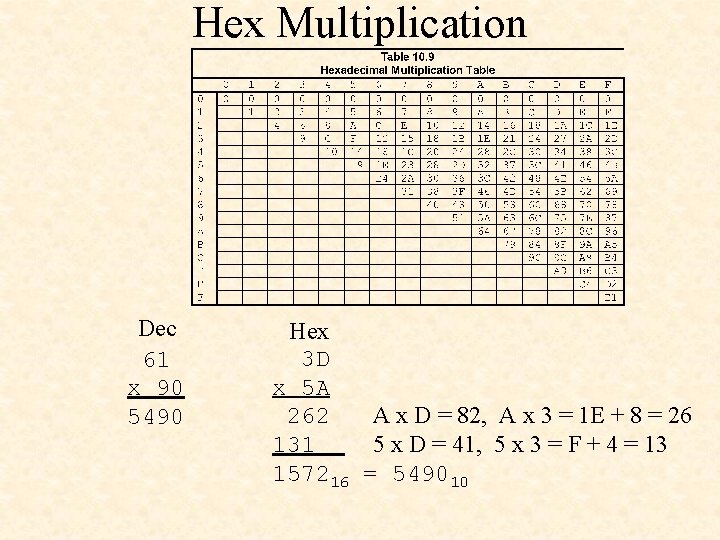

Hex Multiplication

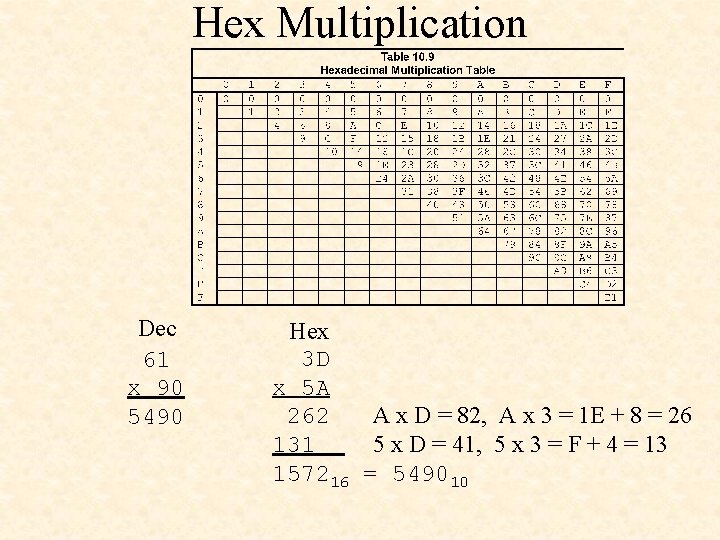

Hex Multiplication Dec 61 x 90 5490 Hex 3 D x 5 A 262 A x D = 82, A x 3 = 1 E + 8 = 26 131 5 x D = 41, 5 x 3 = F + 4 = 13 157216 = 549010

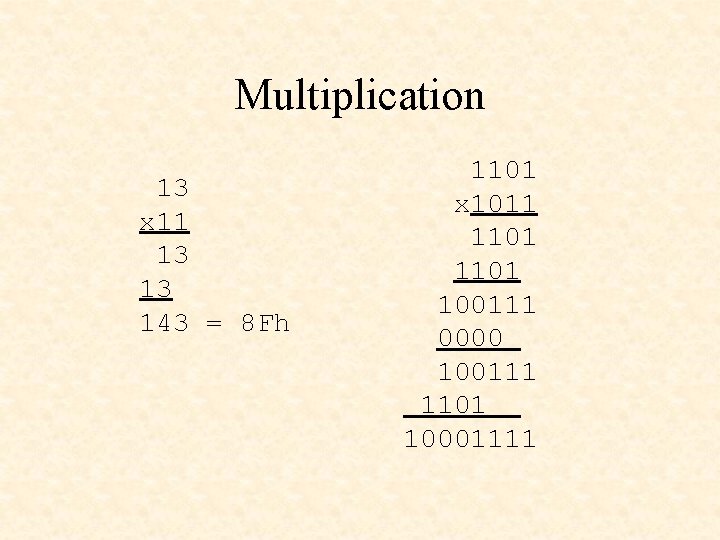

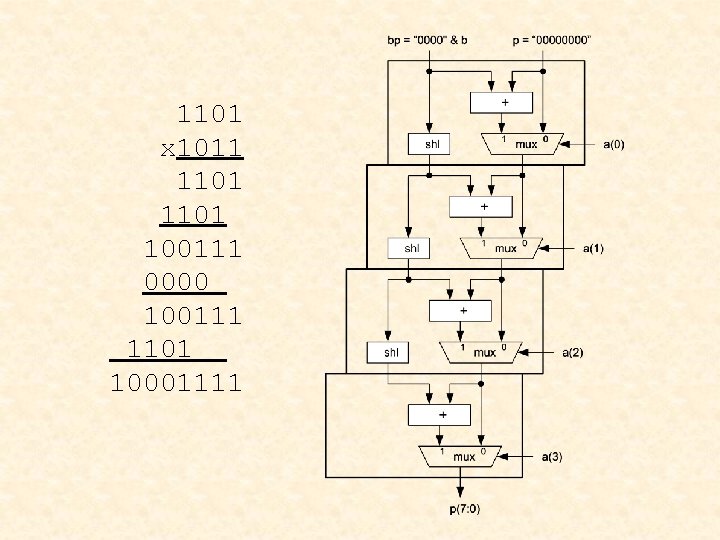

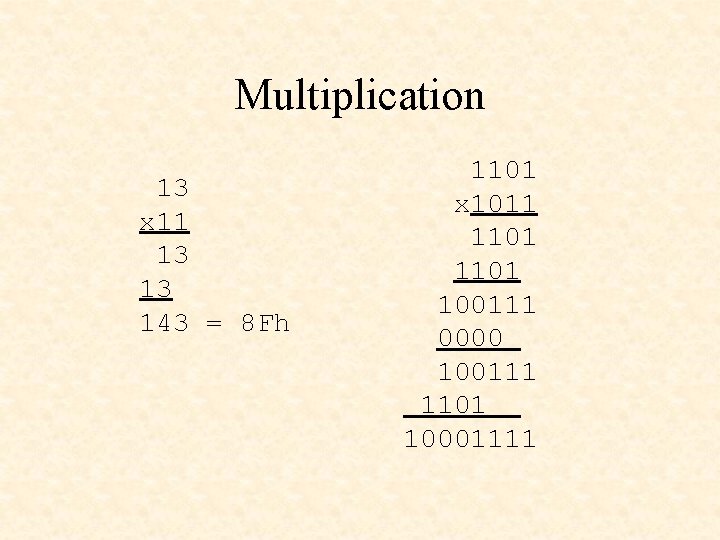

Multiplication 13 x 11 13 13 143 = 8 Fh 1101 x 1011 1101 100111 0000 100111 1101 10001111

Multiplier • • Binary Multiplication A VHDL Multiplier The Multiplication Operator A Multiplication Function

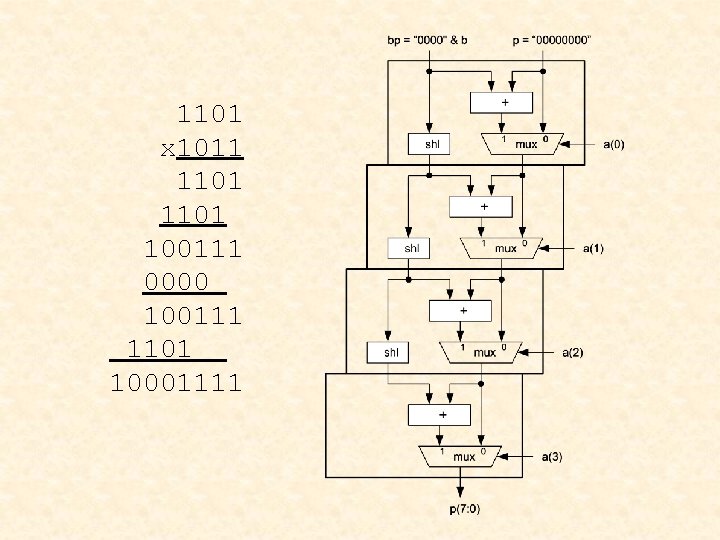

1101 x 1011 1101 100111 0000 100111 1101 10001111

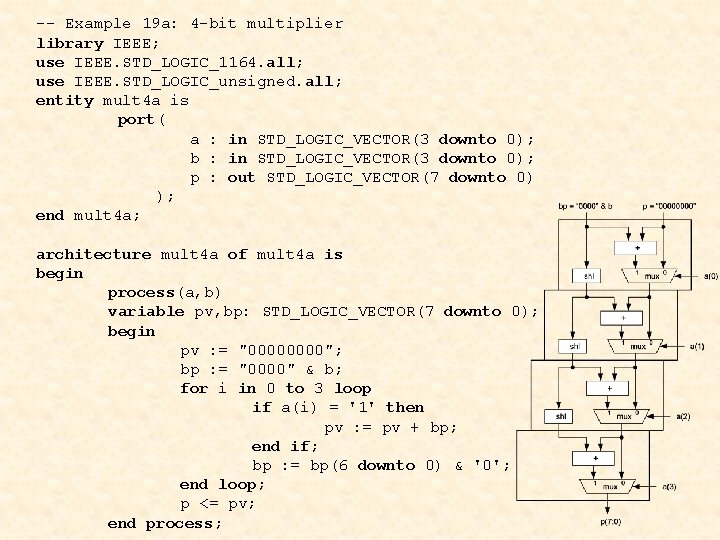

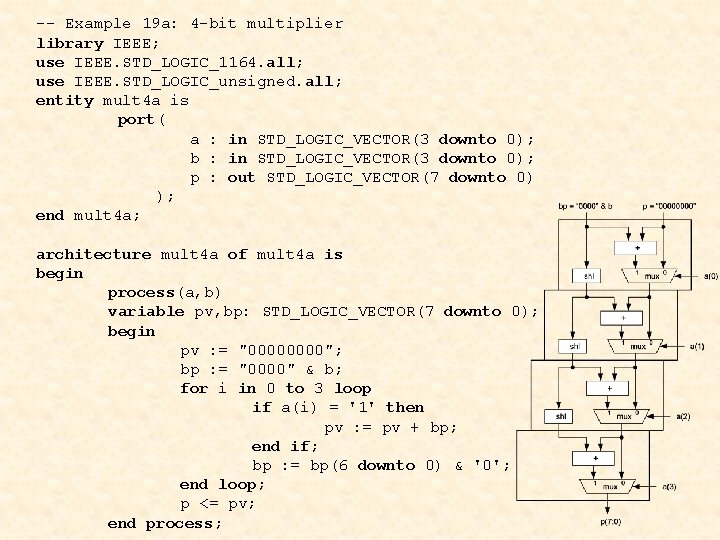

-- Example 19 a: 4 -bit multiplier library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_unsigned. all; entity mult 4 a is port( a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); p : out STD_LOGIC_VECTOR(7 downto 0) ); end mult 4 a; architecture mult 4 a of mult 4 a is begin process(a, b) variable pv, bp: STD_LOGIC_VECTOR(7 downto 0); begin pv : = "0000"; bp : = "0000" & b; for i in 0 to 3 loop if a(i) = '1' then pv : = pv + bp; end if; bp : = bp(6 downto 0) & '0'; end loop; p <= pv; end process;

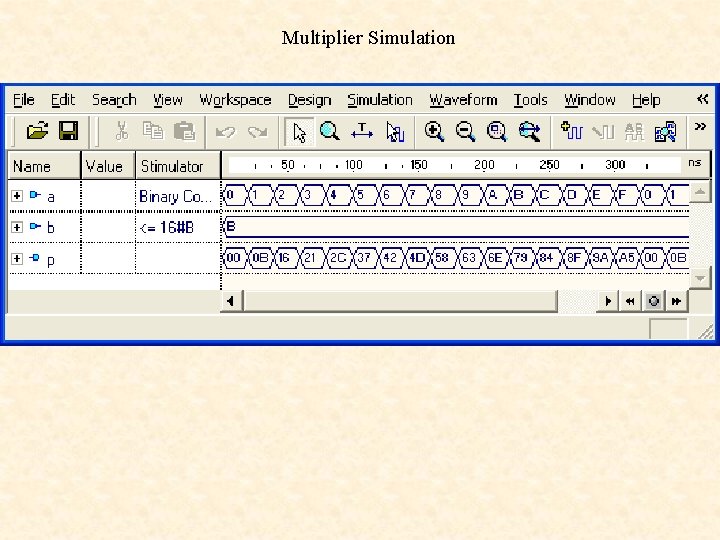

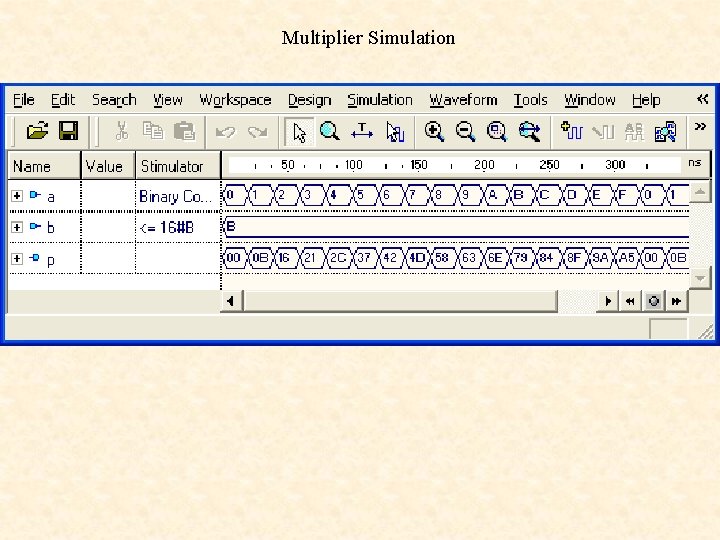

Multiplier Simulation

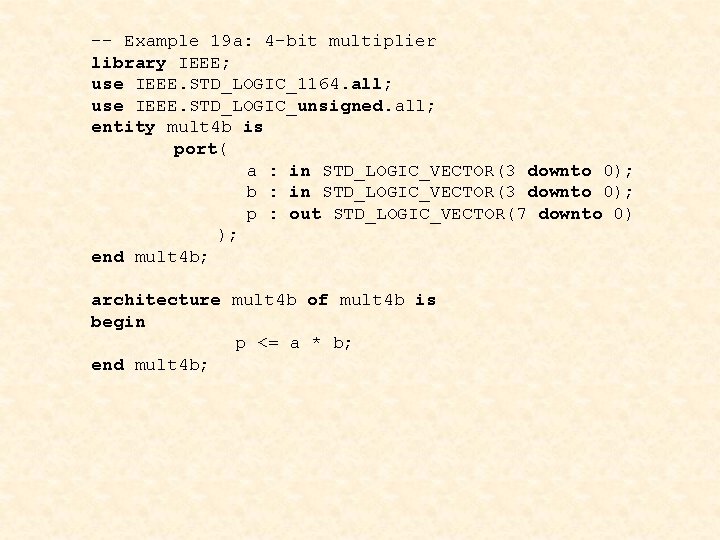

Multiplier • • Binary Multiplication A VHDL Multiplier The Multiplication Operator A Multiplication Function

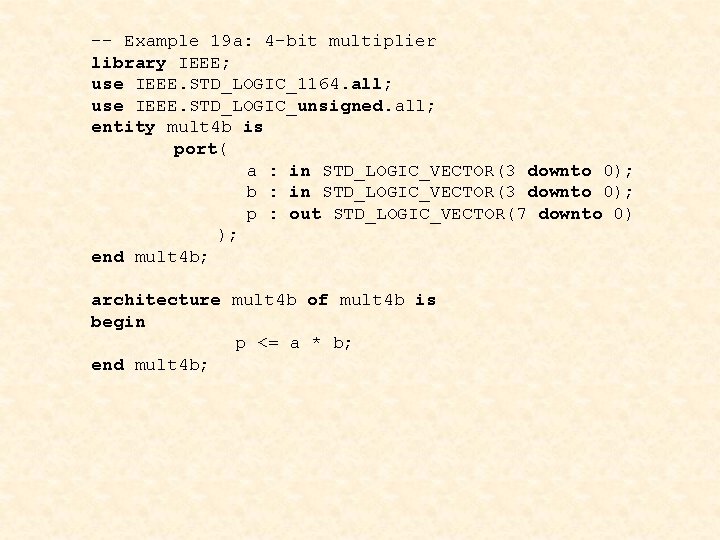

-- Example 19 a: 4 -bit multiplier library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_unsigned. all; entity mult 4 b is port( a : in STD_LOGIC_VECTOR(3 downto 0); b : in STD_LOGIC_VECTOR(3 downto 0); p : out STD_LOGIC_VECTOR(7 downto 0) ); end mult 4 b; architecture mult 4 b of mult 4 b is begin p <= a * b; end mult 4 b;

Multiplier • • Binary Multiplication A VHDL Multiplier The Multiplication Operator A Multiplication Function

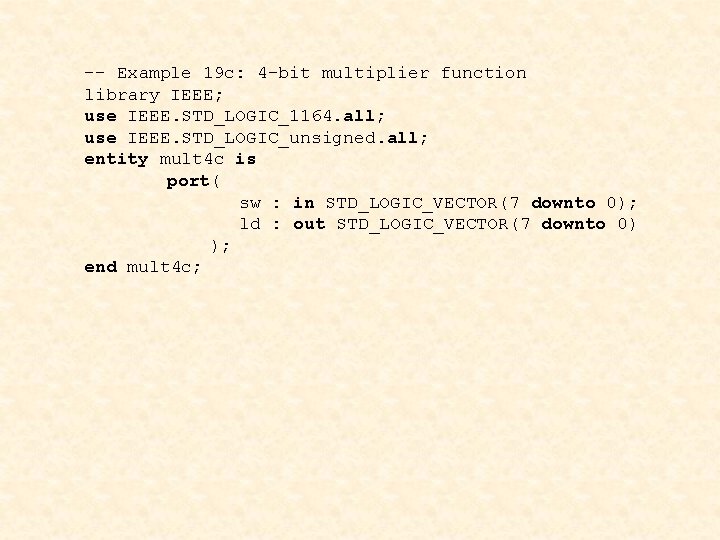

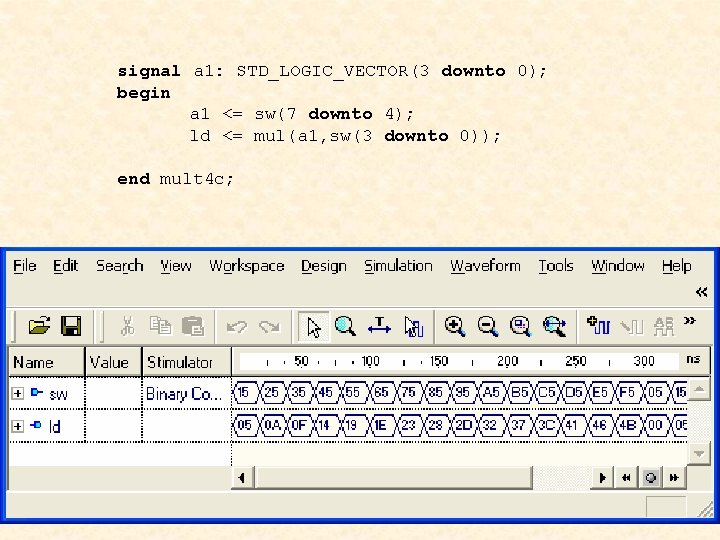

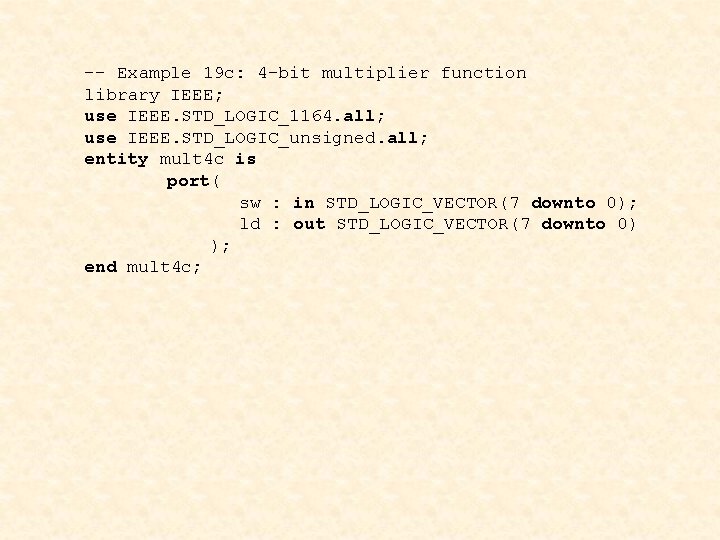

-- Example 19 c: 4 -bit multiplier function library IEEE; use IEEE. STD_LOGIC_1164. all; use IEEE. STD_LOGIC_unsigned. all; entity mult 4 c is port( sw : in STD_LOGIC_VECTOR(7 downto 0); ld : out STD_LOGIC_VECTOR(7 downto 0) ); end mult 4 c;

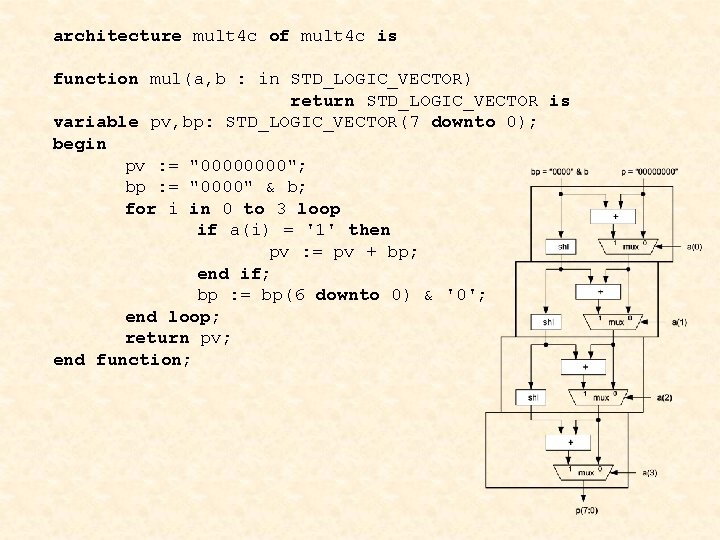

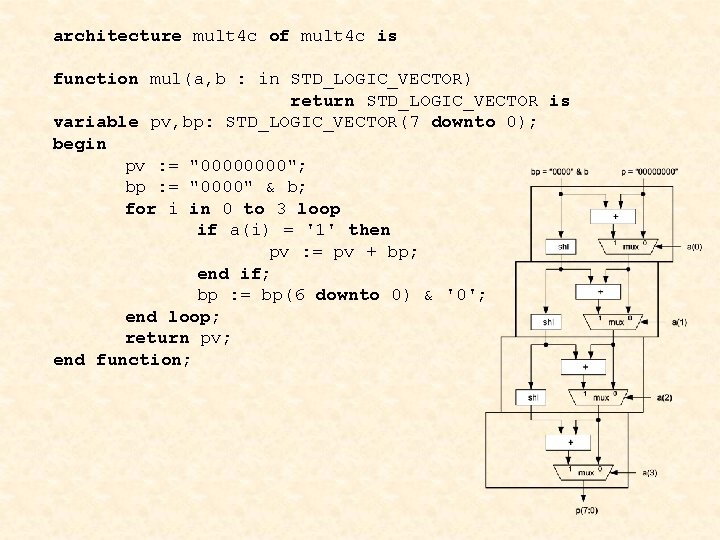

architecture mult 4 c of mult 4 c is function mul(a, b : in STD_LOGIC_VECTOR) return STD_LOGIC_VECTOR is variable pv, bp: STD_LOGIC_VECTOR(7 downto 0); begin pv : = "0000"; bp : = "0000" & b; for i in 0 to 3 loop if a(i) = '1' then pv : = pv + bp; end if; bp : = bp(6 downto 0) & '0'; end loop; return pv; end function;

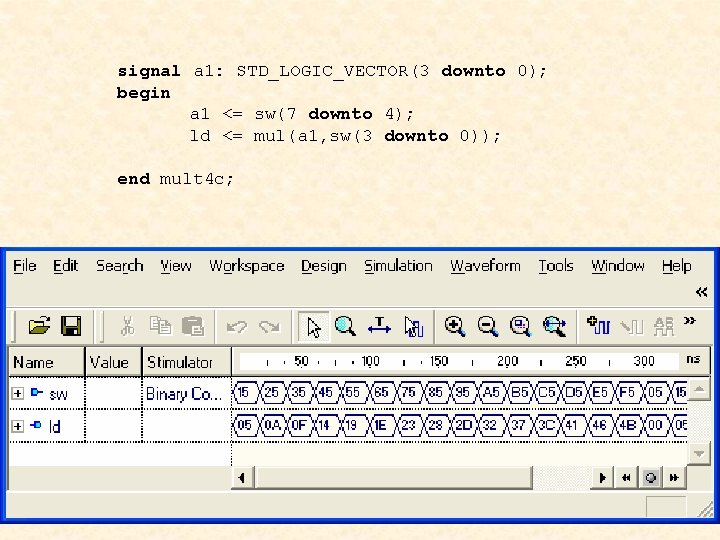

signal a 1: STD_LOGIC_VECTOR(3 downto 0); begin a 1 <= sw(7 downto 4); ld <= mul(a 1, sw(3 downto 0)); end mult 4 c;

Multiplier • • Binary Multiplication A VHDL Multiplier The Multiplication Operator (revisited) A Multiplication Function

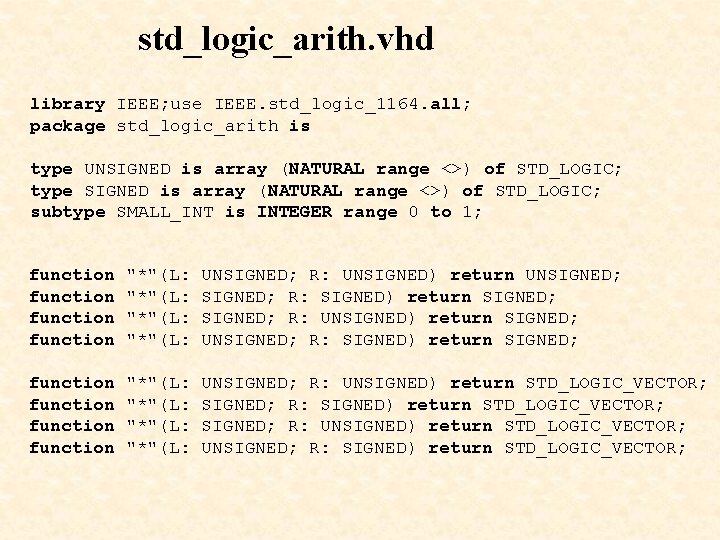

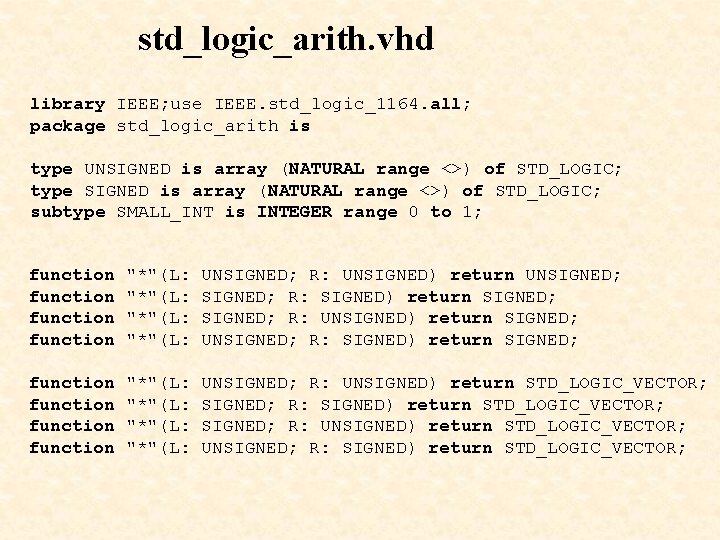

std_logic_arith. vhd library IEEE; use IEEE. std_logic_1164. all; package std_logic_arith is type UNSIGNED is array (NATURAL range <>) of STD_LOGIC; type SIGNED is array (NATURAL range <>) of STD_LOGIC; subtype SMALL_INT is INTEGER range 0 to 1; function "*"(L: UNSIGNED; R: UNSIGNED) return UNSIGNED; R: SIGNED) return SIGNED; R: UNSIGNED) return SIGNED; UNSIGNED; R: SIGNED) return SIGNED; function "*"(L: UNSIGNED; R: UNSIGNED) return STD_LOGIC_VECTOR; UNSIGNED; R: SIGNED) return STD_LOGIC_VECTOR;

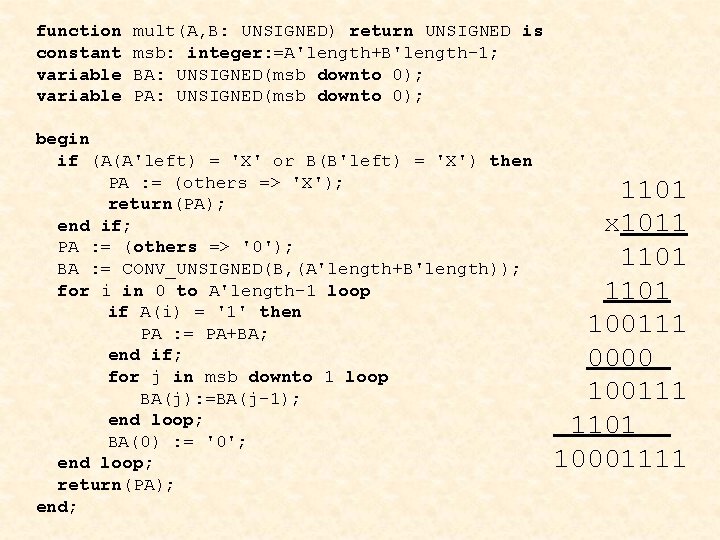

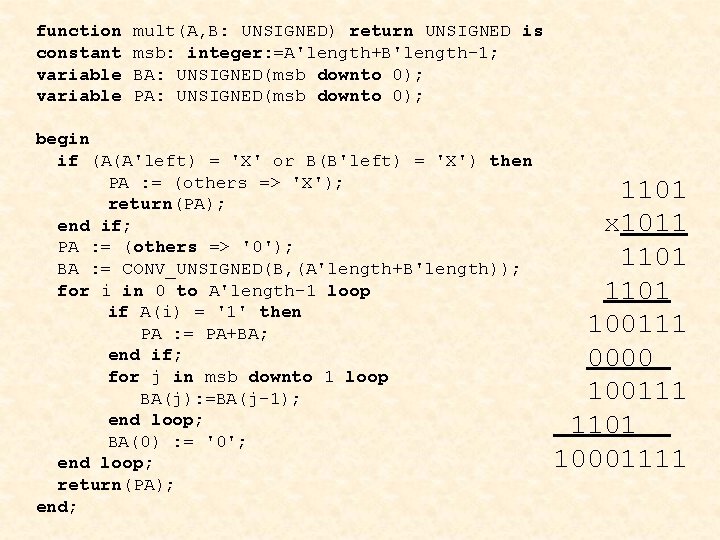

function constant variable mult(A, B: UNSIGNED) return UNSIGNED is msb: integer: =A'length+B'length-1; BA: UNSIGNED(msb downto 0); PA: UNSIGNED(msb downto 0); begin if (A(A'left) = 'X' or B(B'left) = 'X') then PA : = (others => 'X'); return(PA); end if; PA : = (others => '0'); BA : = CONV_UNSIGNED(B, (A'length+B'length)); for i in 0 to A'length-1 loop if A(i) = '1' then PA : = PA+BA; end if; for j in msb downto 1 loop BA(j): =BA(j-1); end loop; BA(0) : = '0'; end loop; return(PA); end; 1101 x 1011 1101 100111 0000 100111 1101 10001111

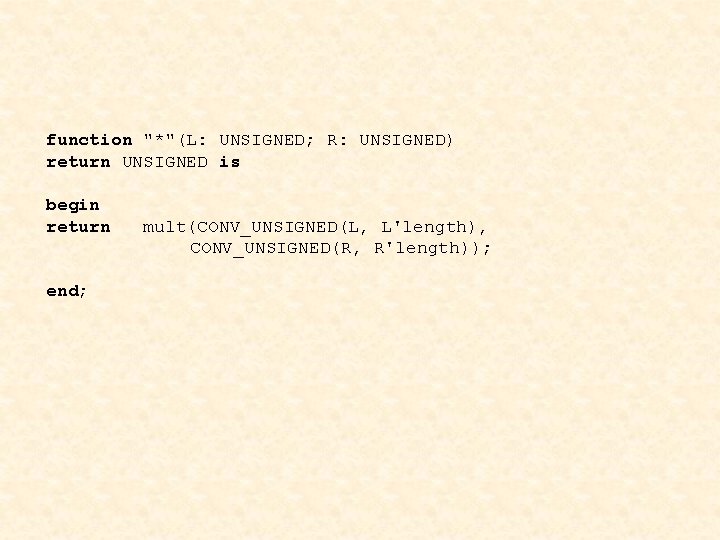

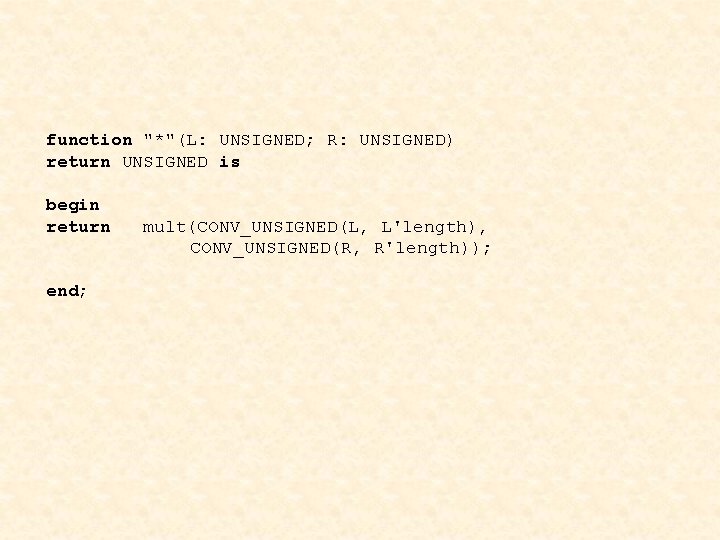

function "*"(L: UNSIGNED; R: UNSIGNED) return UNSIGNED is begin return end; mult(CONV_UNSIGNED(L, L'length), CONV_UNSIGNED(R, R'length));

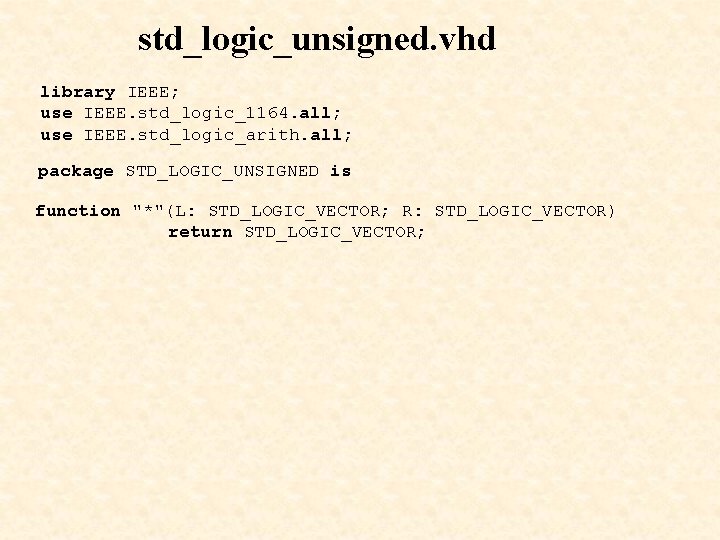

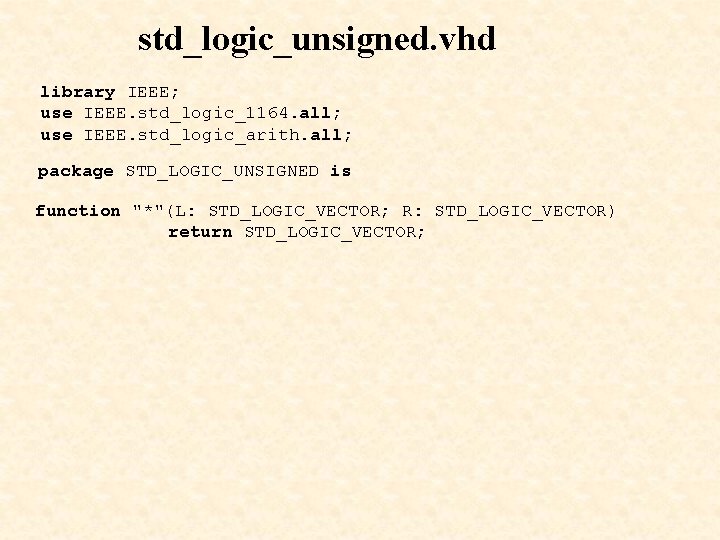

std_logic_unsigned. vhd library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_arith. all; package STD_LOGIC_UNSIGNED is function "*"(L: STD_LOGIC_VECTOR; R: STD_LOGIC_VECTOR) return STD_LOGIC_VECTOR;

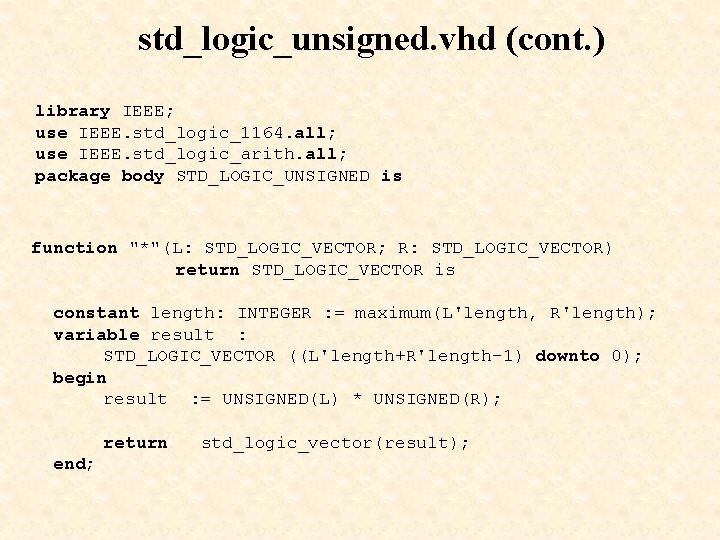

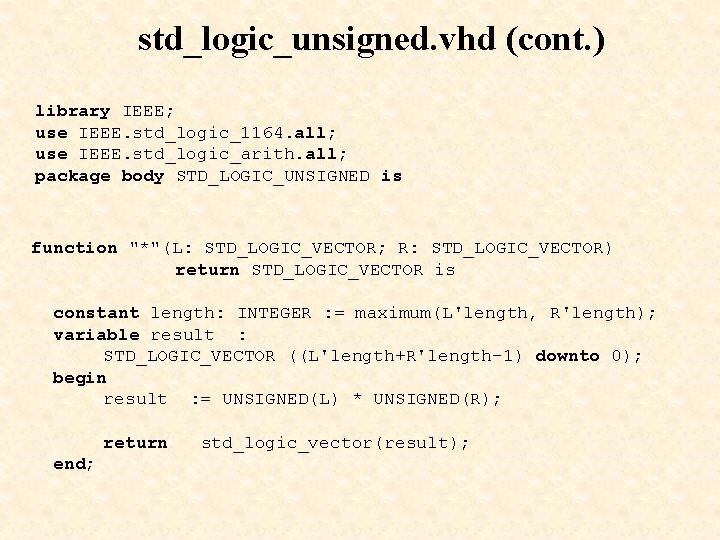

std_logic_unsigned. vhd (cont. ) library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_arith. all; package body STD_LOGIC_UNSIGNED is function "*"(L: STD_LOGIC_VECTOR; R: STD_LOGIC_VECTOR) return STD_LOGIC_VECTOR is constant length: INTEGER : = maximum(L'length, R'length); variable result : STD_LOGIC_VECTOR ((L'length+R'length-1) downto 0); begin result : = UNSIGNED(L) * UNSIGNED(R); return end; std_logic_vector(result);