Multiplexers ENGIN 112 L 15 Magnitude Comparator and

- Slides: 13

Multiplexers ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

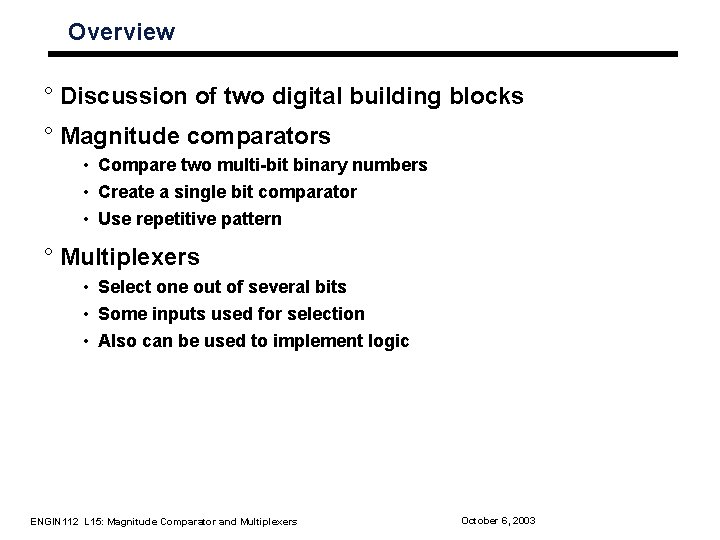

Overview ° Discussion of two digital building blocks ° Magnitude comparators • Compare two multi-bit binary numbers • Create a single bit comparator • Use repetitive pattern ° Multiplexers • Select one out of several bits • Some inputs used for selection • Also can be used to implement logic ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

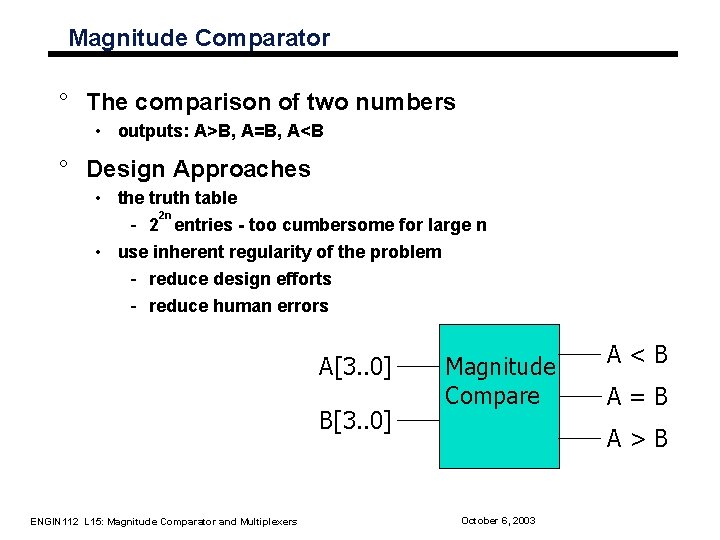

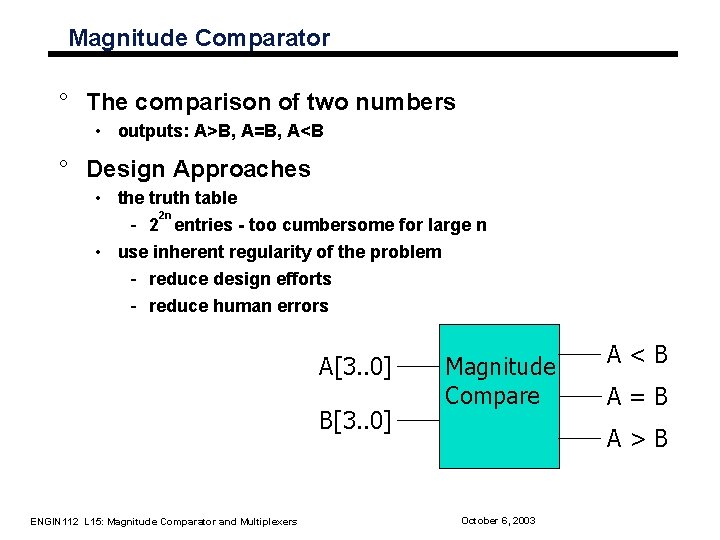

Magnitude Comparator ° The comparison of two numbers • outputs: A>B, A=B, A<B ° Design Approaches • the truth table 2 n - 2 entries - too cumbersome for large n • use inherent regularity of the problem - reduce design efforts - reduce human errors A[3. . 0] B[3. . 0] ENGIN 112 L 15: Magnitude Comparator and Multiplexers Magnitude Compare A<B A=B A>B October 6, 2003

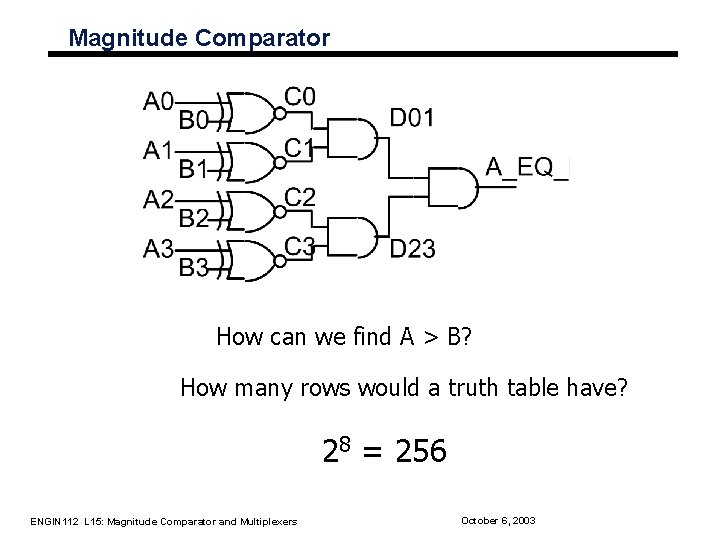

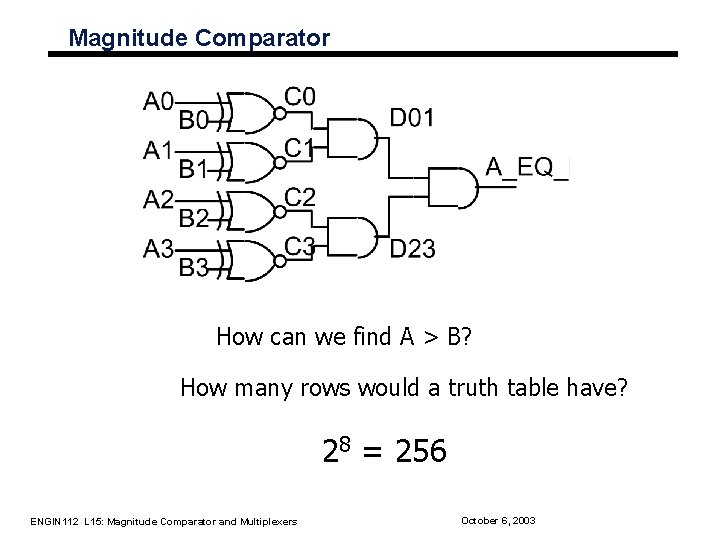

Magnitude Comparator How can we find A > B? How many rows would a truth table have? 28 = 256 ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

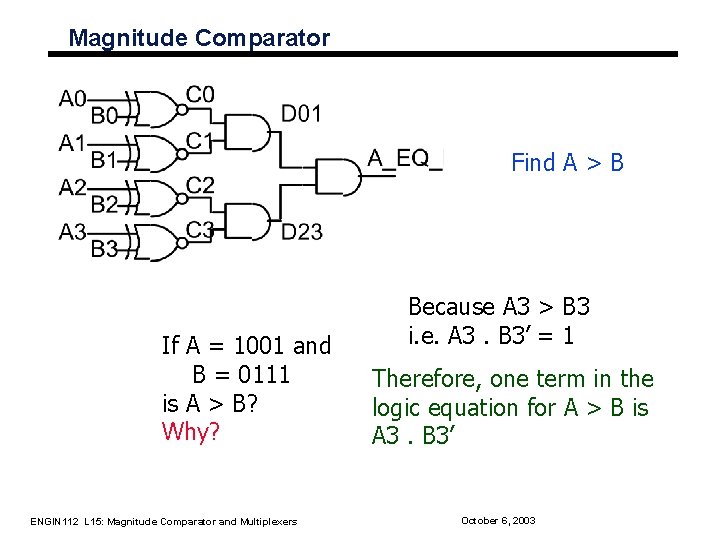

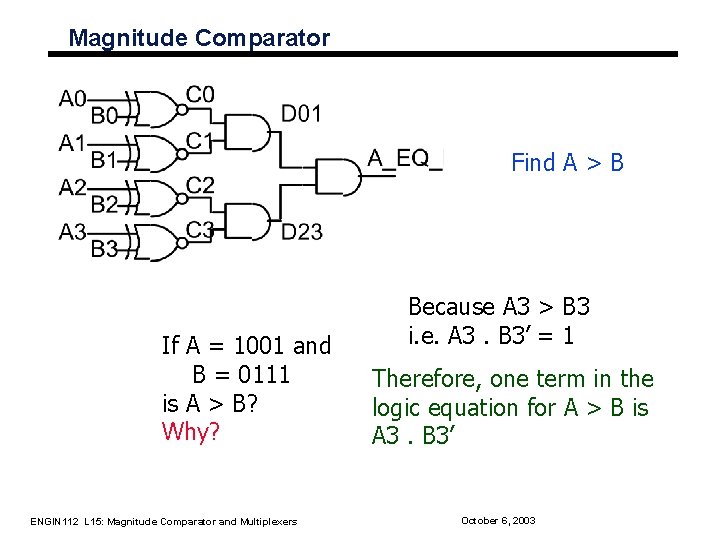

Magnitude Comparator Find A > B If A = 1001 and B = 0111 is A > B? Why? ENGIN 112 L 15: Magnitude Comparator and Multiplexers Because A 3 > B 3 i. e. A 3. B 3’ = 1 Therefore, one term in the logic equation for A > B is A 3. B 3’ October 6, 2003

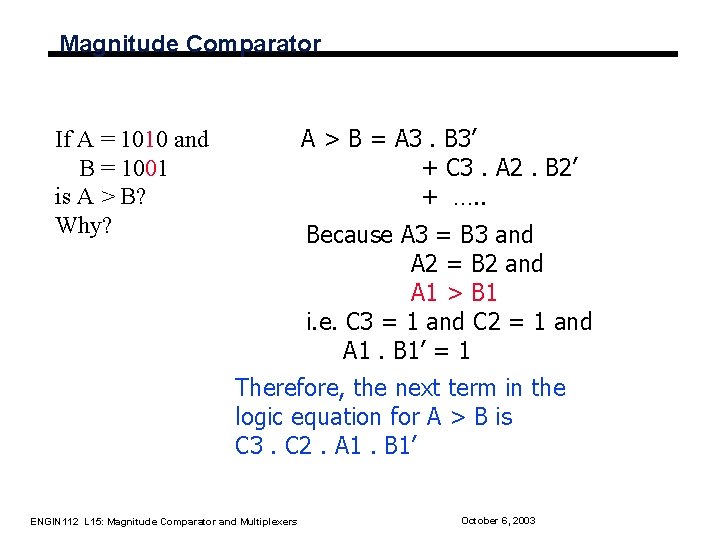

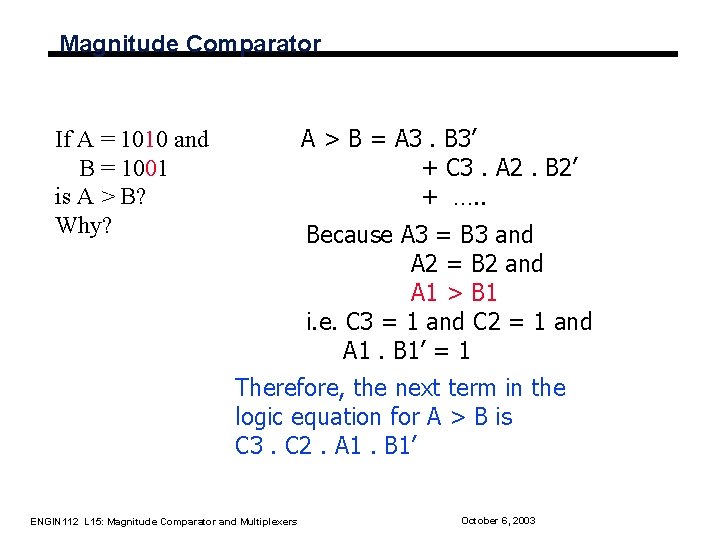

Magnitude Comparator A > B = A 3. B 3’ + C 3. A 2. B 2’ + …. . If A = 1010 and B = 1001 is A > B? Why? Because A 3 = B 3 and A 2 = B 2 and A 1 > B 1 i. e. C 3 = 1 and C 2 = 1 and A 1. B 1’ = 1 Therefore, the next term in the logic equation for A > B is C 3. C 2. A 1. B 1’ ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

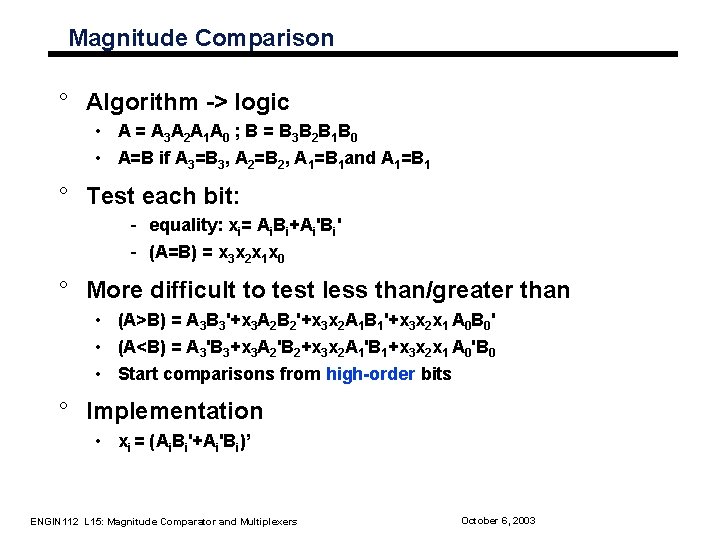

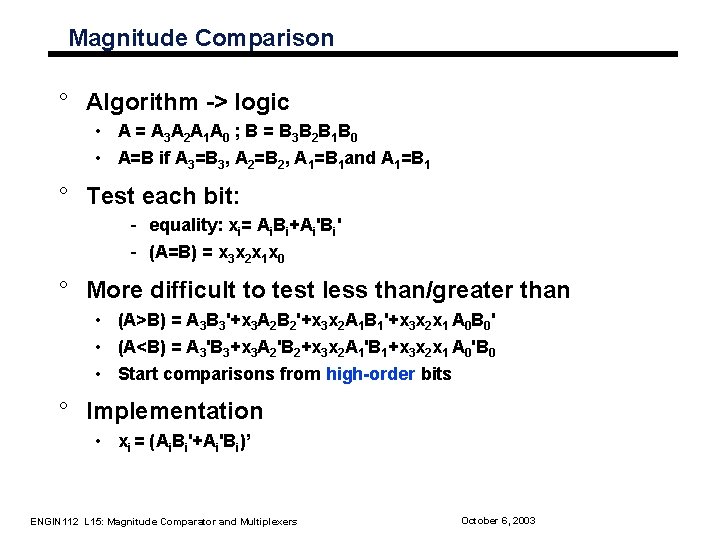

Magnitude Comparison ° Algorithm -> logic • A = A 3 A 2 A 1 A 0 ; B = B 3 B 2 B 1 B 0 • A=B if A 3=B 3, A 2=B 2, A 1=B 1 and A 1=B 1 ° Test each bit: - equality: xi= Ai. Bi+Ai'Bi' - (A=B) = x 3 x 2 x 1 x 0 ° More difficult to test less than/greater than • (A>B) = A 3 B 3'+x 3 A 2 B 2'+x 3 x 2 A 1 B 1'+x 3 x 2 x 1 A 0 B 0' • (A<B) = A 3'B 3+x 3 A 2'B 2+x 3 x 2 A 1'B 1+x 3 x 2 x 1 A 0'B 0 • Start comparisons from high-order bits ° Implementation • xi = (Ai. Bi'+Ai'Bi)’ ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

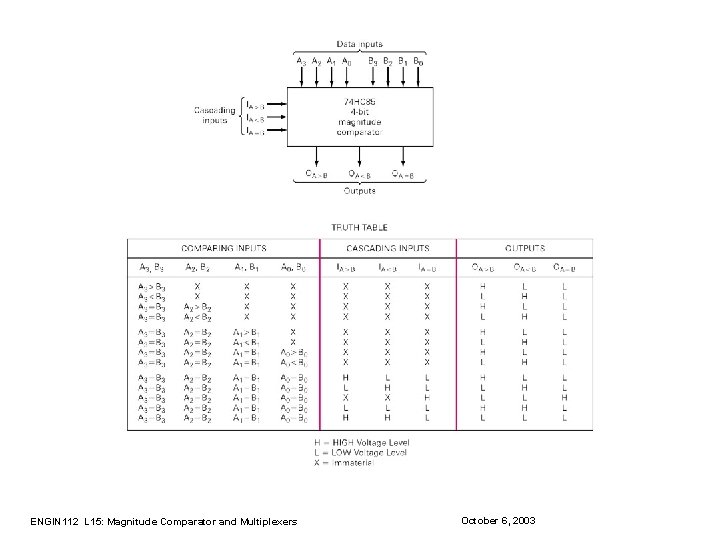

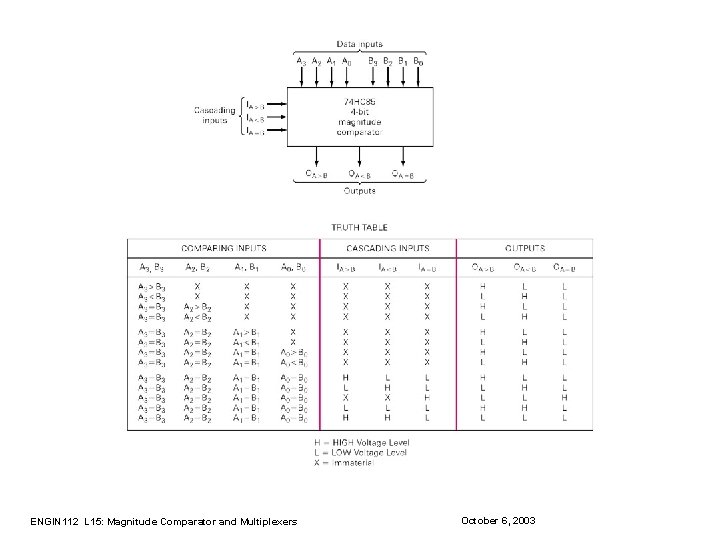

Magnitude Comparison ° Hardware chips ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

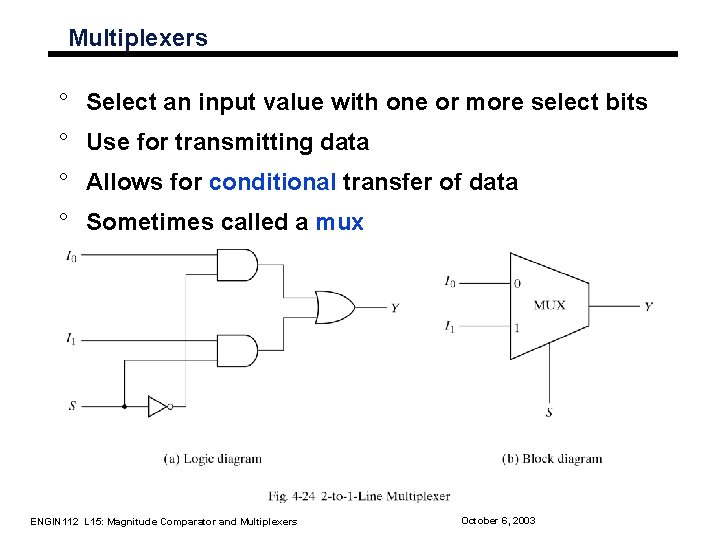

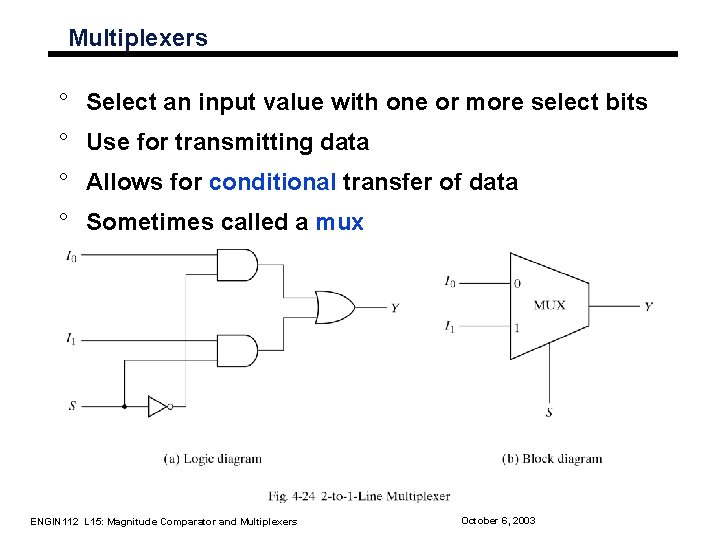

Multiplexers ° Select an input value with one or more select bits ° Use for transmitting data ° Allows for conditional transfer of data ° Sometimes called a mux ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

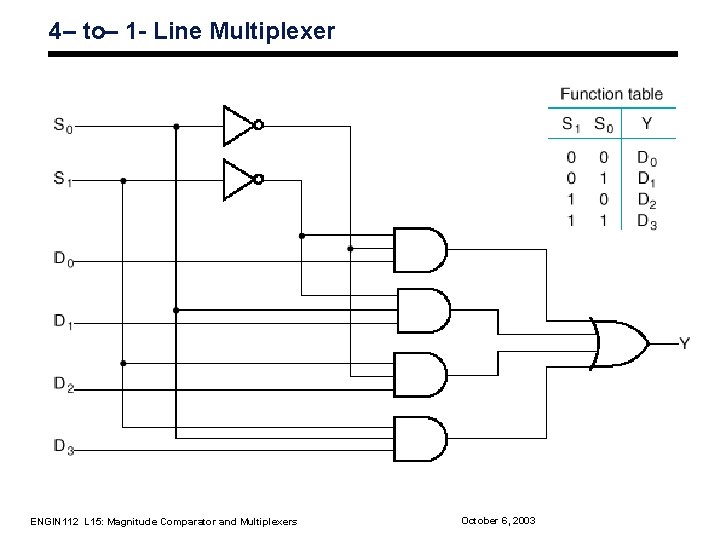

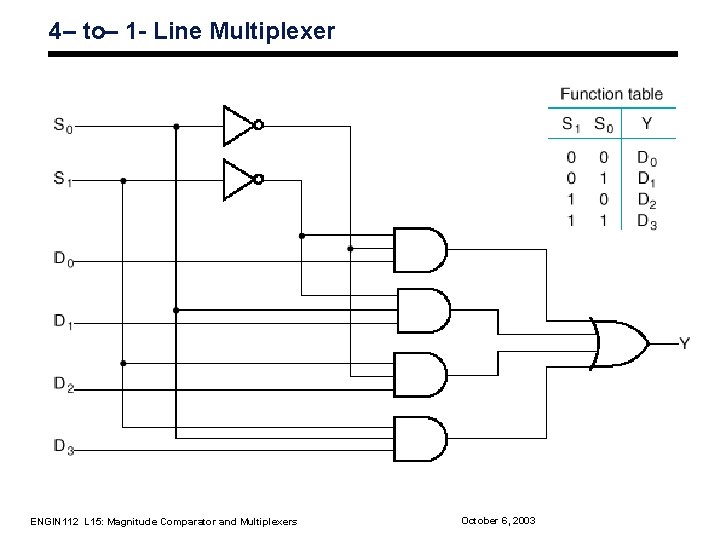

4– to– 1 - Line Multiplexer ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

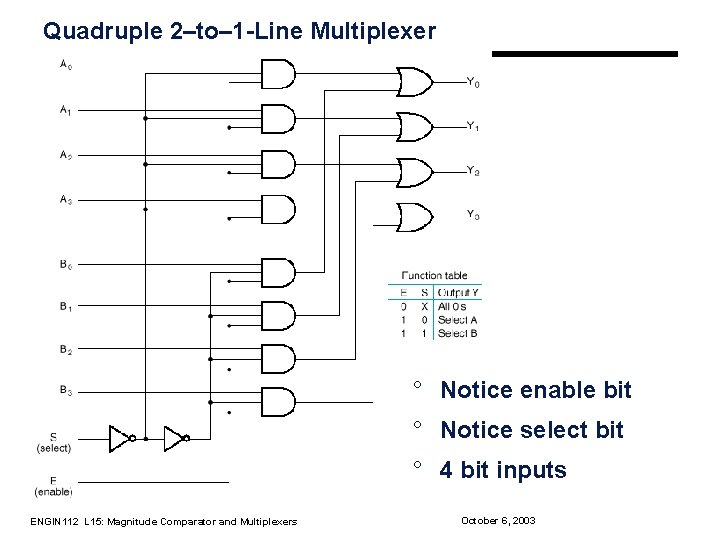

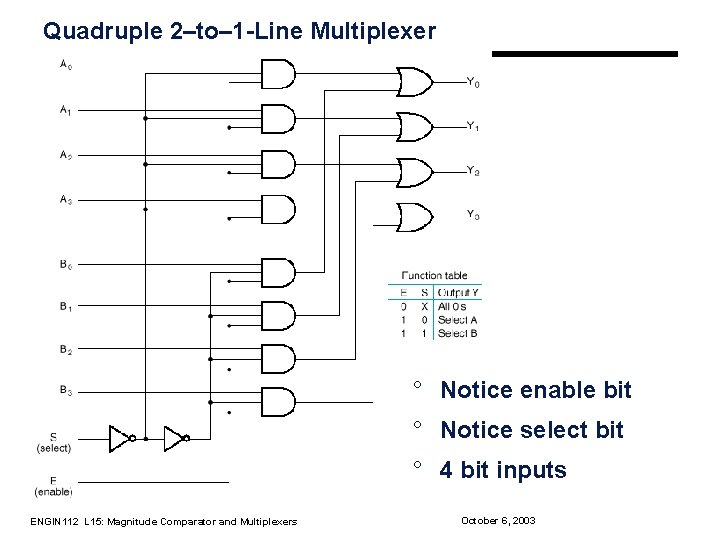

Quadruple 2–to– 1 -Line Multiplexer ° Notice enable bit ° Notice select bit ° 4 bit inputs ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

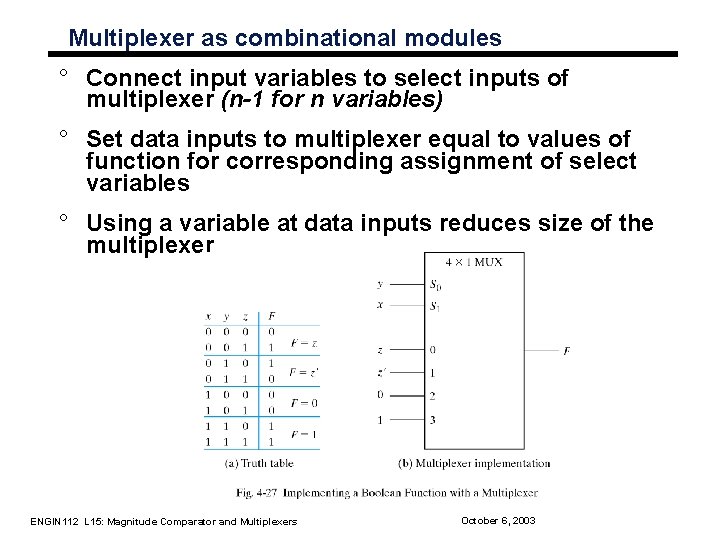

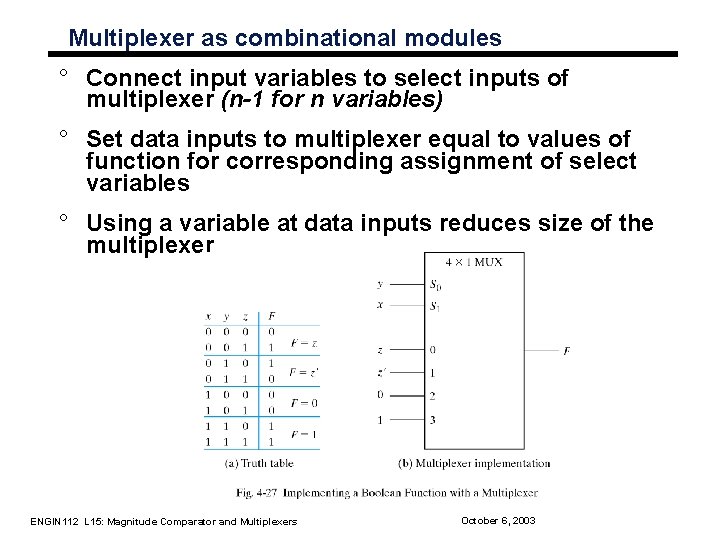

Multiplexer as combinational modules ° Connect input variables to select inputs of multiplexer (n-1 for n variables) ° Set data inputs to multiplexer equal to values of function for corresponding assignment of select variables ° Using a variable at data inputs reduces size of the multiplexer ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003

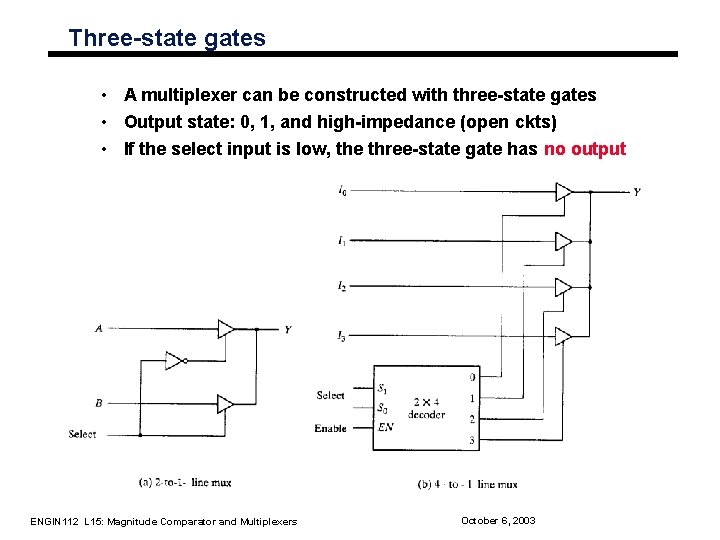

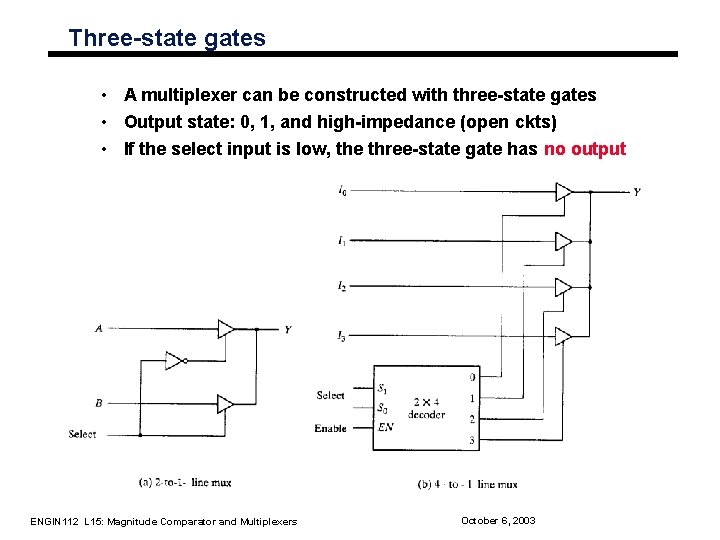

Three-state gates • A multiplexer can be constructed with three-state gates • Output state: 0, 1, and high-impedance (open ckts) • If the select input is low, the three-state gate has no output ENGIN 112 L 15: Magnitude Comparator and Multiplexers October 6, 2003