MultiModule FMC Adapter MMA 1 0 Rev A

- Slides: 5

Multi-Module FMC Adapter MMA 1. 0 Rev A RD 53 A Testing Meeting Sept. 26, 2017

FMC Adapter Goals Interface to Multiple Single Chip Cards (SCC): • • Use mini-Display. Port connectors/cables, 4 on FMC, 4 on daughter board (4 or 8 SCCs) Use bi-directional buffers on all differential pairs Maintain compatibility with CML and LVDS AC couple all differential pairs Configurable ports for flexibility (allows for use as an emulator) Firmware can choose port usage as Data, HIT-OR, or clock source, etc. Use LPC connections on FMC board/ Use HPC connections on daughter board Do not use Xpress. K 7 FMC signals that are non-FMC compliant. Options for differential buffer: • On Semi, FIN 1101: Single buffer, 1. 6 Gbps, low power 9 m. A, but need 40 per board. • TI, DS 90 LV 004: Quad pack, 1. 5 Gbps, 117 m. A, (need 10 per board), implies separate power • TI DS 15 MB 200: Dual bi-directional buffers with multiplexing, 1. 5 Gbps, 225 m. A, (need 10 per board) 9/26/2017 Ben Bylsma -- RD 53 A Testing Meeting 2

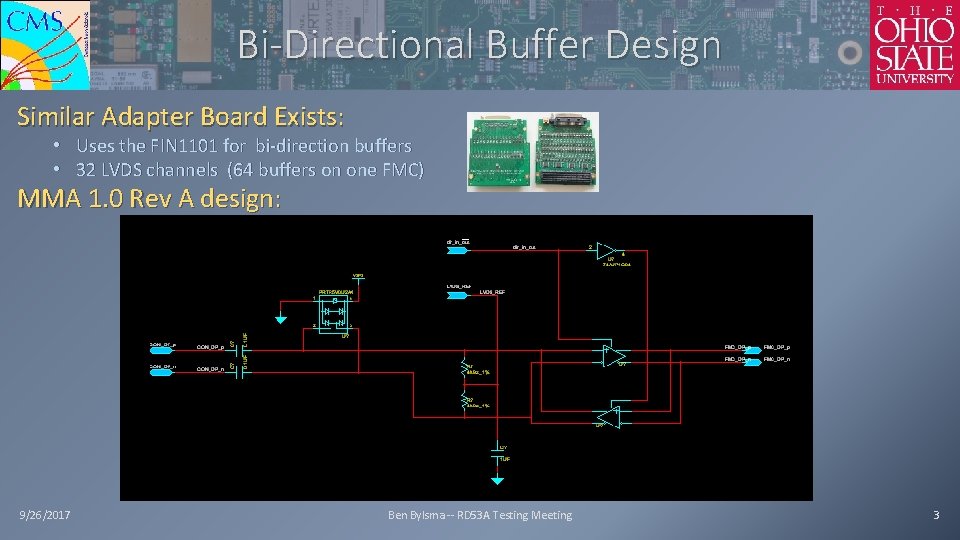

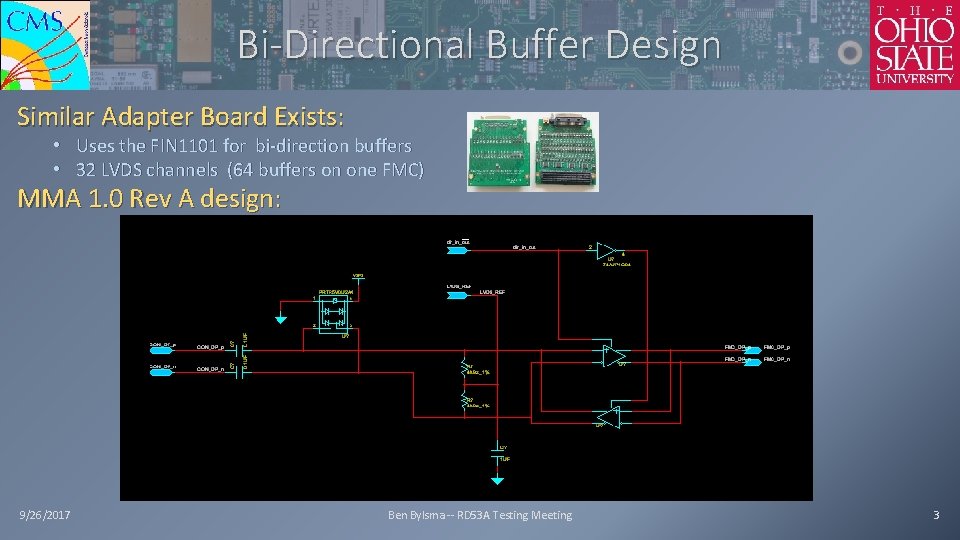

Bi-Directional Buffer Design Similar Adapter Board Exists: • • Uses the FIN 1101 for bi-direction buffers 32 LVDS channels (64 buffers on one FMC) MMA 1. 0 Rev A design: 9/26/2017 Ben Bylsma -- RD 53 A Testing Meeting 3

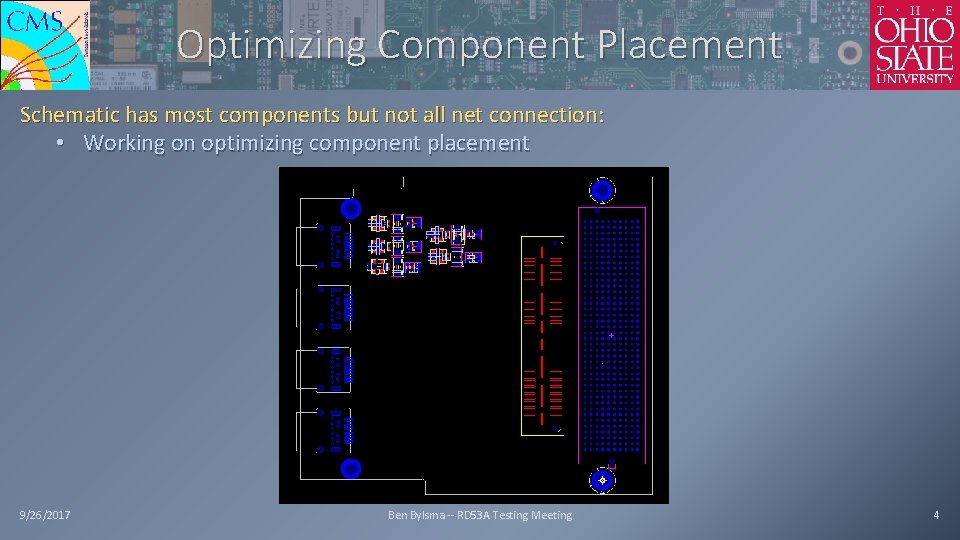

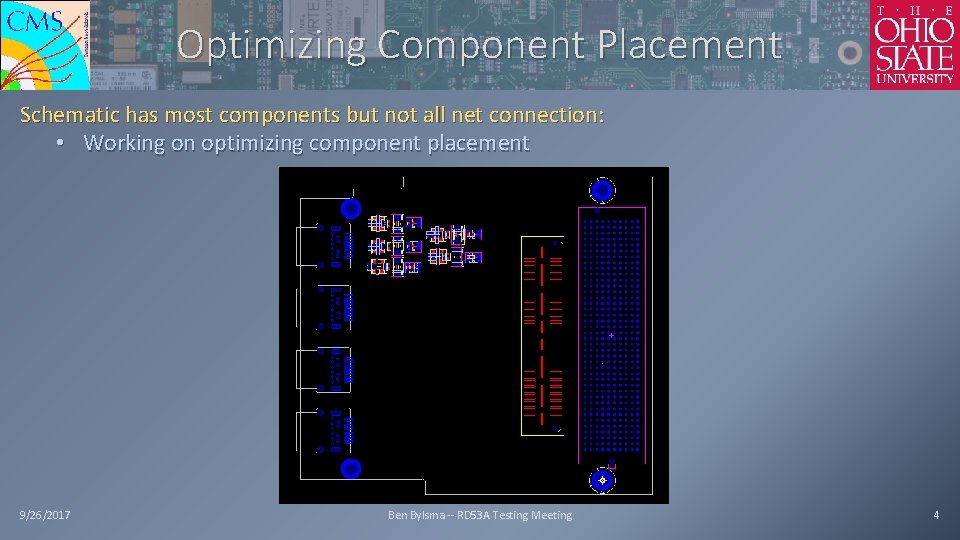

Optimizing Component Placement Schematic has most components but not all net connection: • Working on optimizing component placement 9/26/2017 Ben Bylsma -- RD 53 A Testing Meeting 4

Question Yet to be Answered • • 9/26/2017 FMC Connector pinout QSH Connector pinout and location Single ended signals to route to FPGA Route enable signals for buffer direction to FPGA or use serial to parallel registers? Ben Bylsma -- RD 53 A Testing Meeting 5