MPGD Detectors and Electronics at CIAE Xinglong Li

- Slides: 19

MPGD Detectors and Electronics at CIAE Xinglong Li, Xiaomei Li, Shouyang Hu, Jing Zhou, etc. China Institute of Atomic Energy

Outline • MPGD detectors R&D – GEM foil – Micro. Megas detector • APV 25 digitization system – Test results – Upgrade • Summary

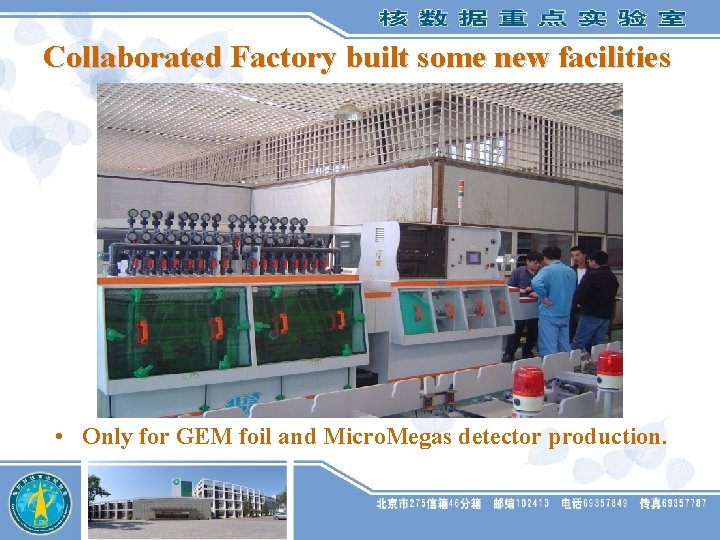

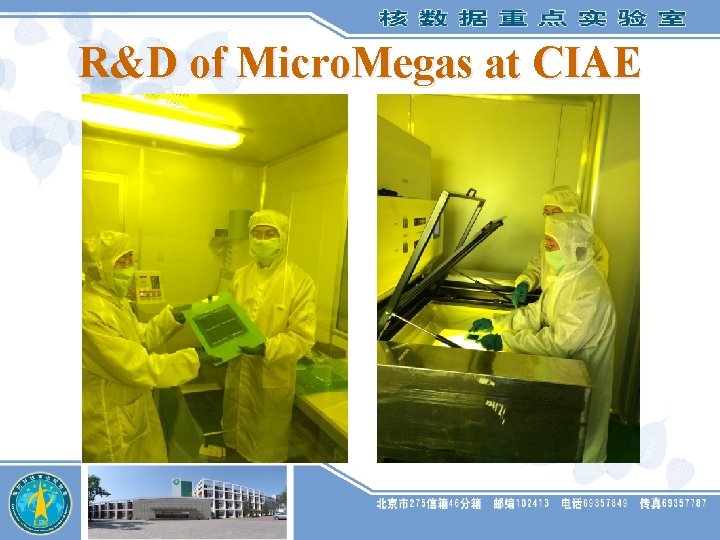

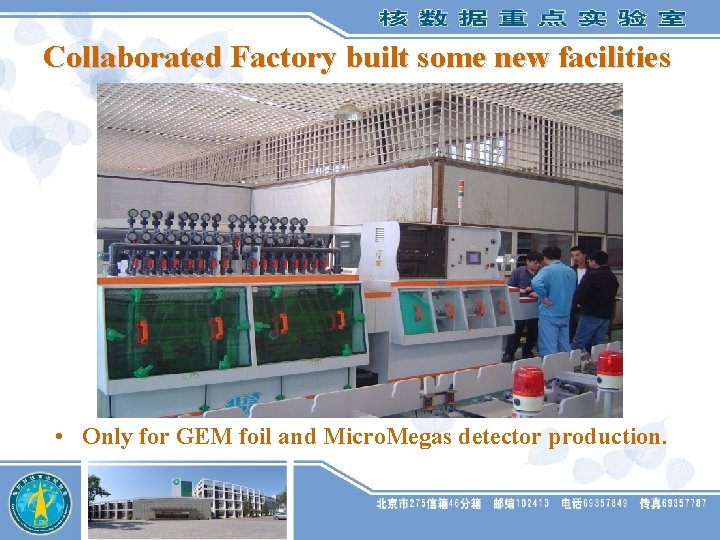

Collaborated Factory built some new facilities • Only for GEM foil and Micro. Megas detector production.

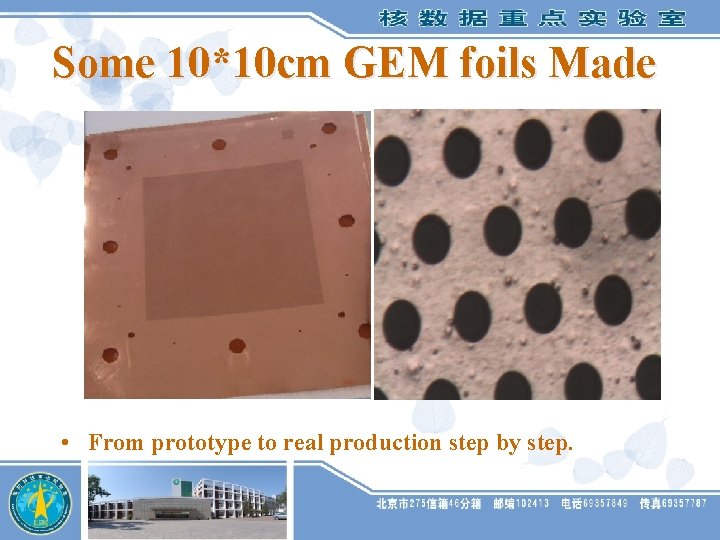

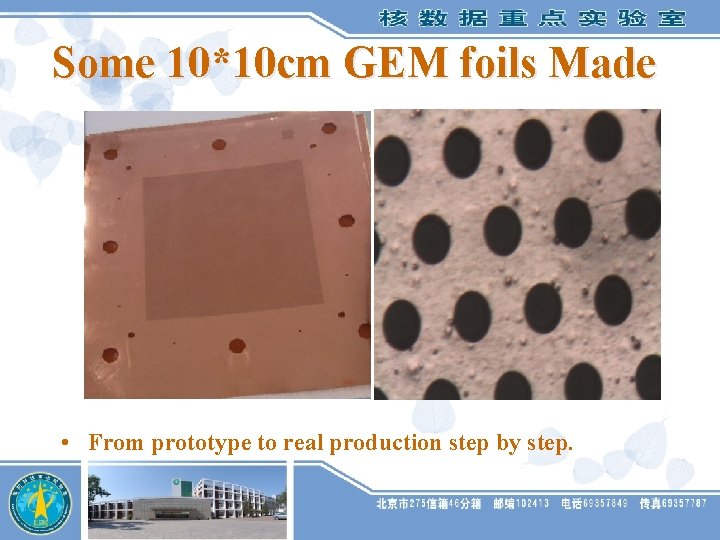

Some 10*10 cm GEM foils Made • From prototype to real production step by step.

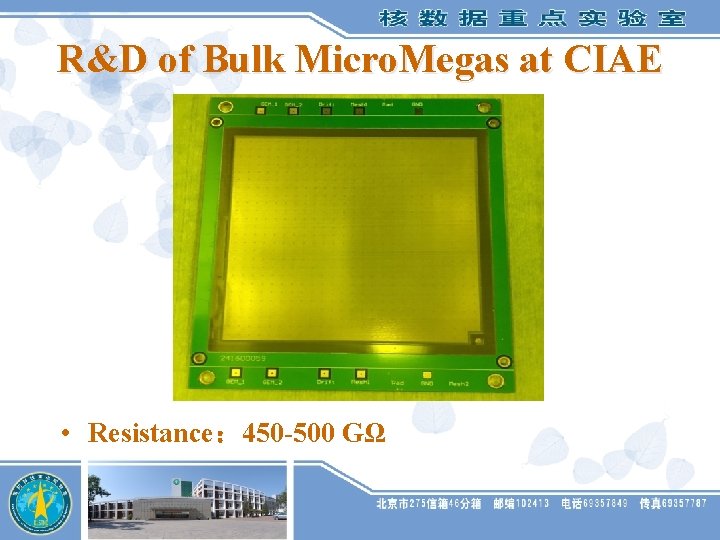

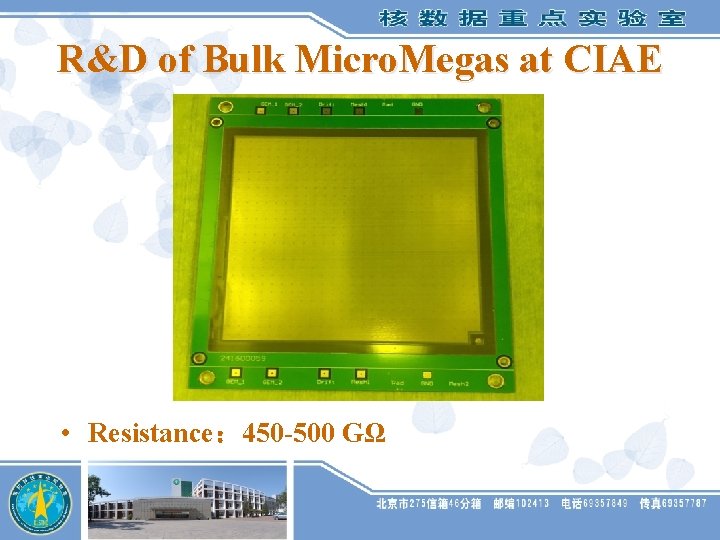

R&D of Bulk Micro. Megas at CIAE • Resistance: 450 -500 GΩ

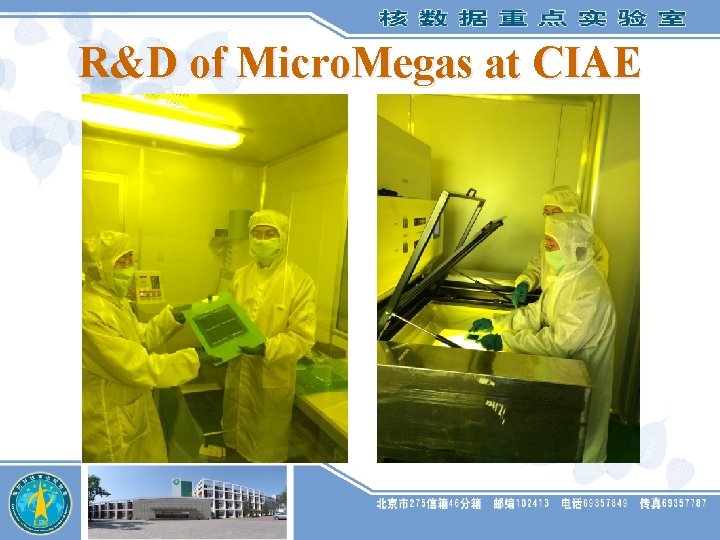

R&D of Micro. Megas at CIAE

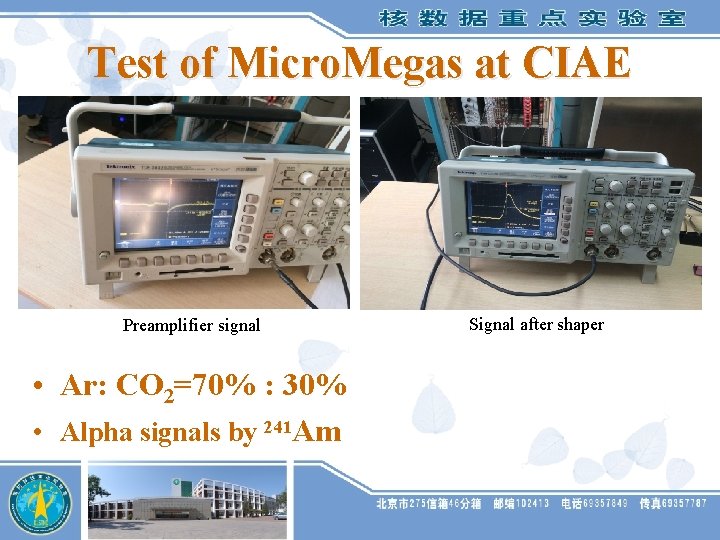

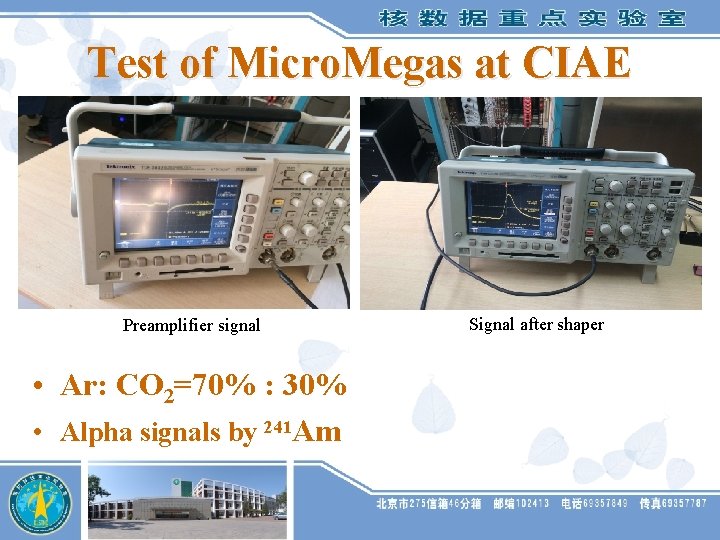

Test of Micro. Megas at CIAE Preamplifier signal • Ar: CO 2=70% : 30% • Alpha signals by 241 Am Signal after shaper

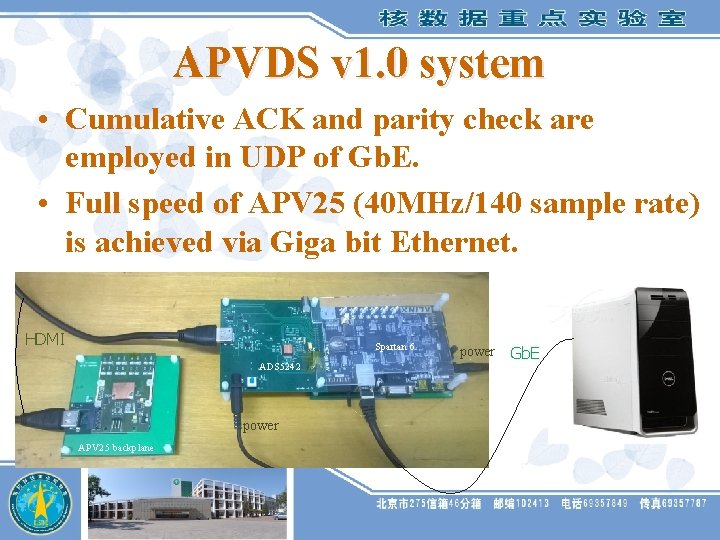

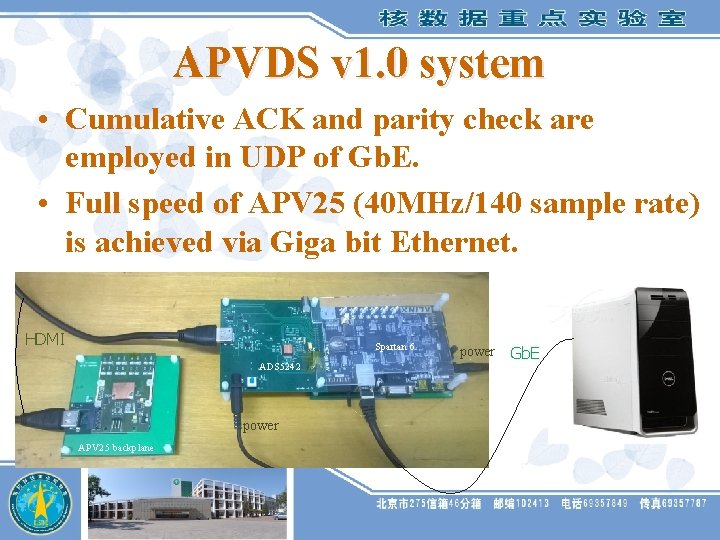

APVDS v 1. 0 system • Cumulative ACK and parity check are employed in UDP of Gb. E. • Full speed of APV 25 (40 MHz/140 sample rate) is achieved via Giga bit Ethernet. HDMI Spartan 6 ADS 5242 power APV 25 backplane power Gb. E

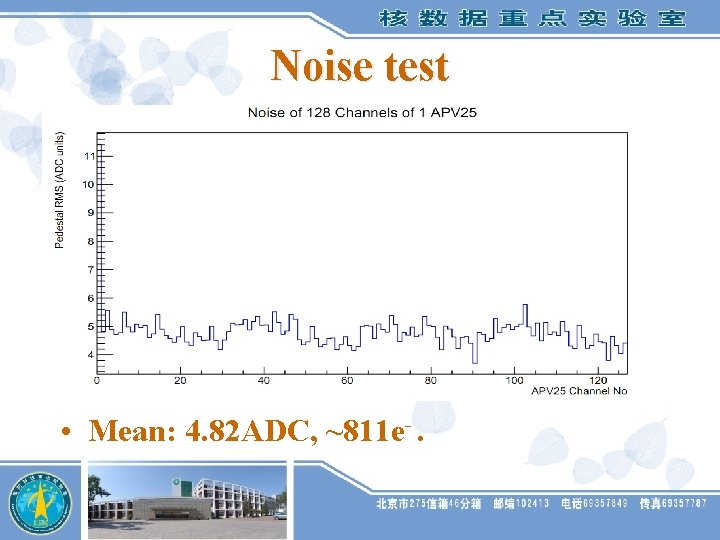

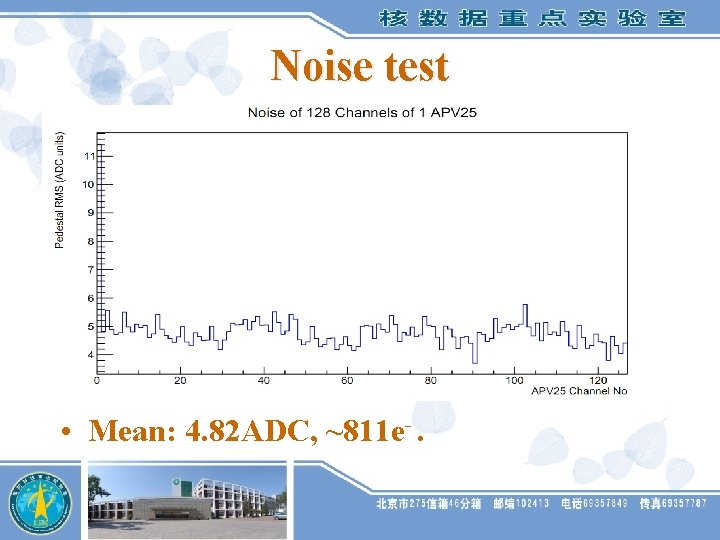

Noise test • Mean: 4. 82 ADC, ~811 e-.

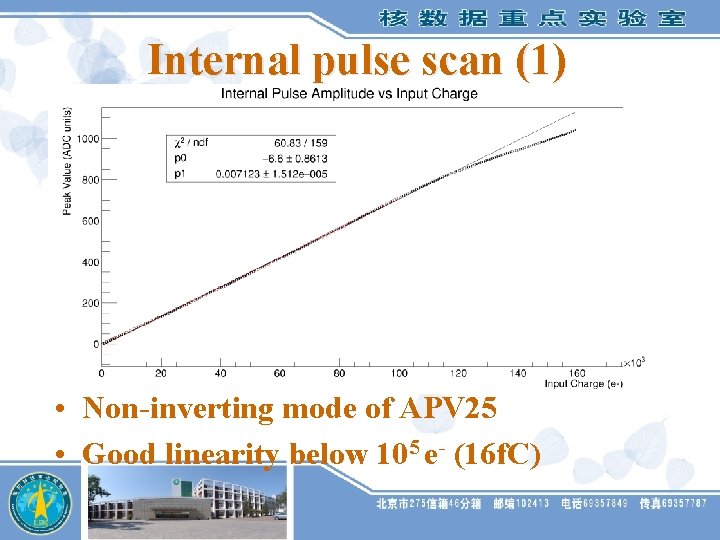

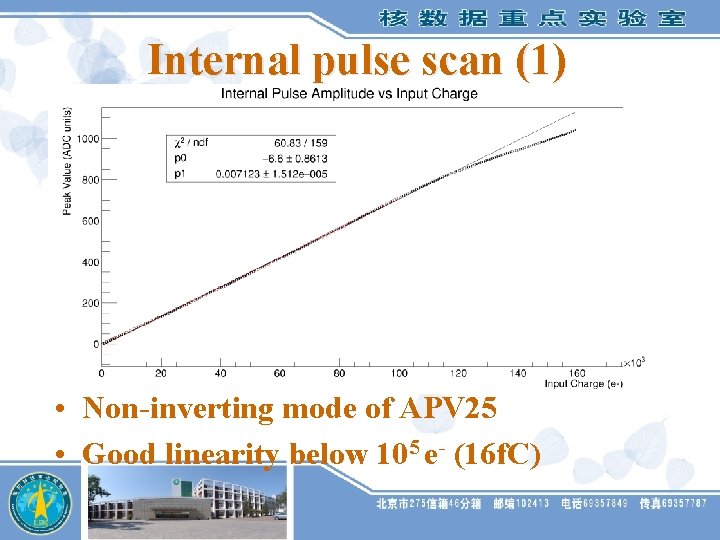

Internal pulse scan (1) • Non-inverting mode of APV 25 • Good linearity below 105 e- (16 f. C)

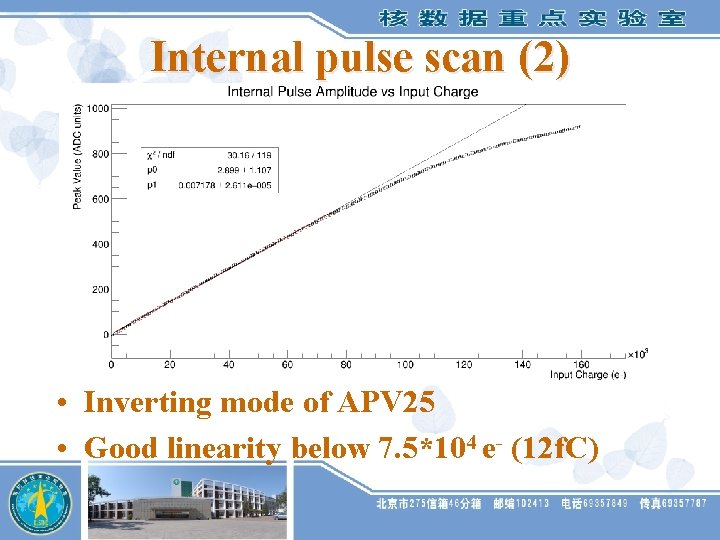

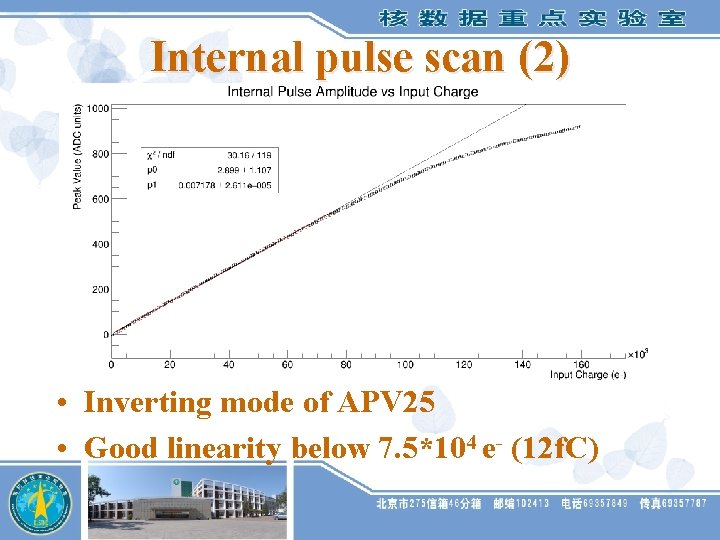

Internal pulse scan (2) • Inverting mode of APV 25 • Good linearity below 7. 5*104 e- (12 f. C)

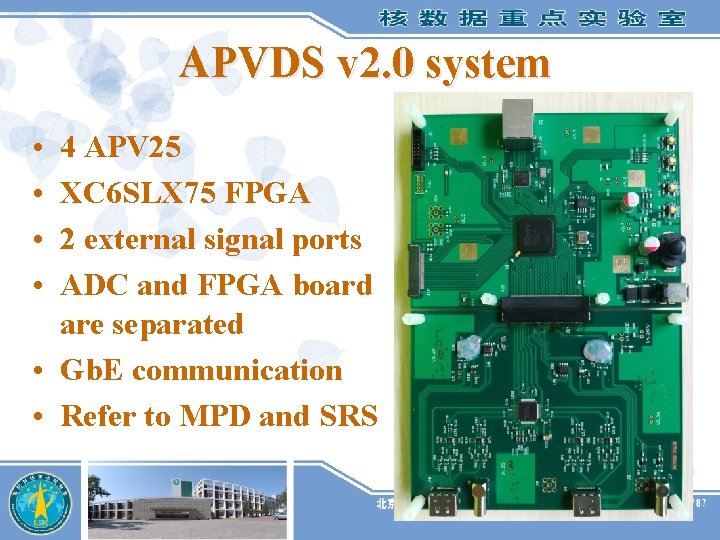

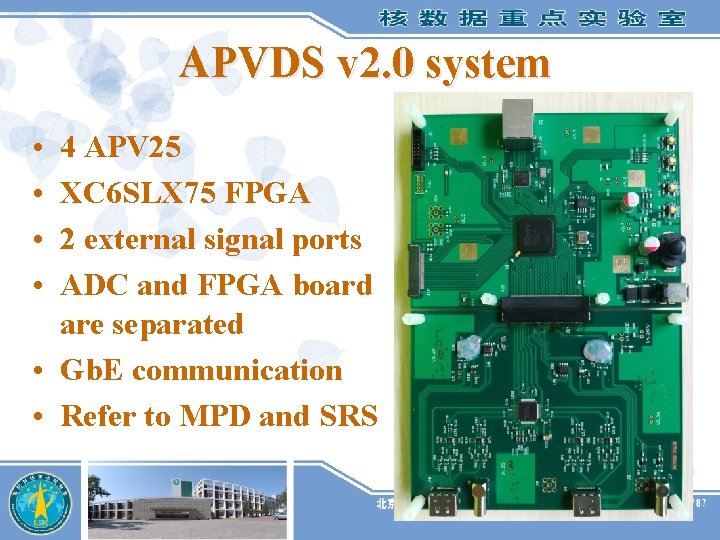

APVDS v 2. 0 system • • 4 APV 25 XC 6 SLX 75 FPGA 2 external signal ports ADC and FPGA board are separated • Gb. E communication • Refer to MPD and SRS

Summary • GEM foil and Micro. Megas detectors R&D is undergoing at Collaborated Factory and CIAE lab. • We just got 0. 9 millions RMB fund to support the R&D of GEM foil. We are looking for more channels to support our work. • The test results of APVDS v 1. 0 system are good enough for MPGD. • APVDS v 2. 0 hardware is finished. The logic of FPGA and software to be completed. • Next step is the combined test of Micromegas and APVDS.

Thanks for your attention!

backup

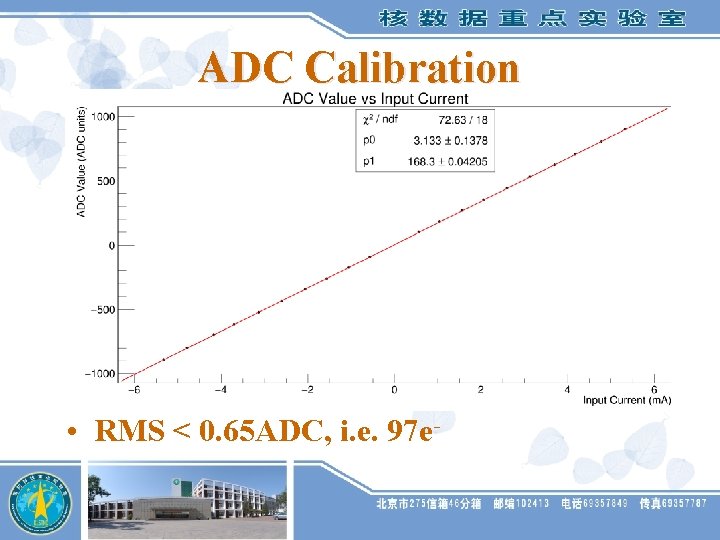

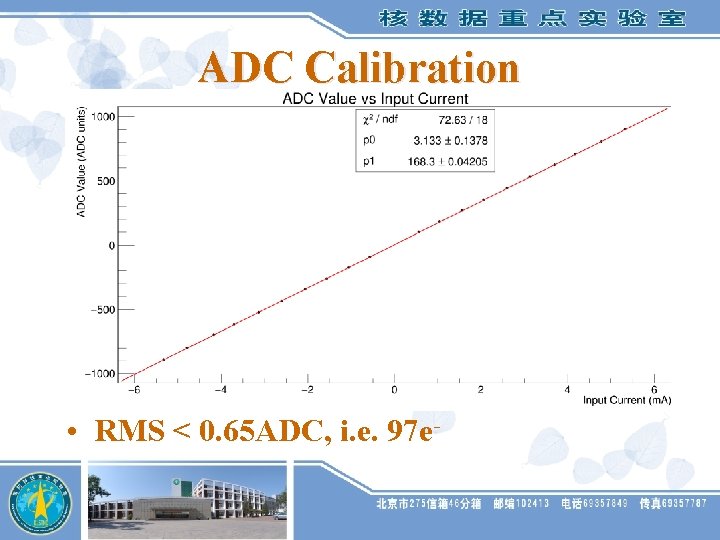

ADC Calibration • RMS < 0. 65 ADC, i. e. 97 e-

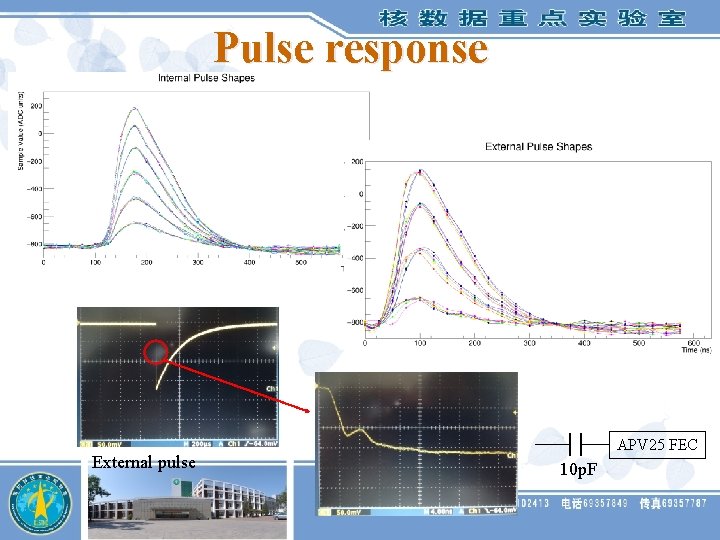

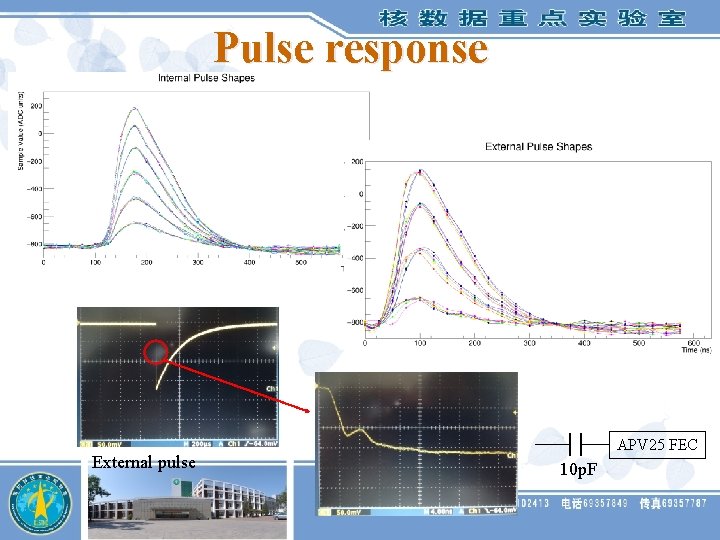

Pulse response External pulse APV 25 FEC 10 p. F

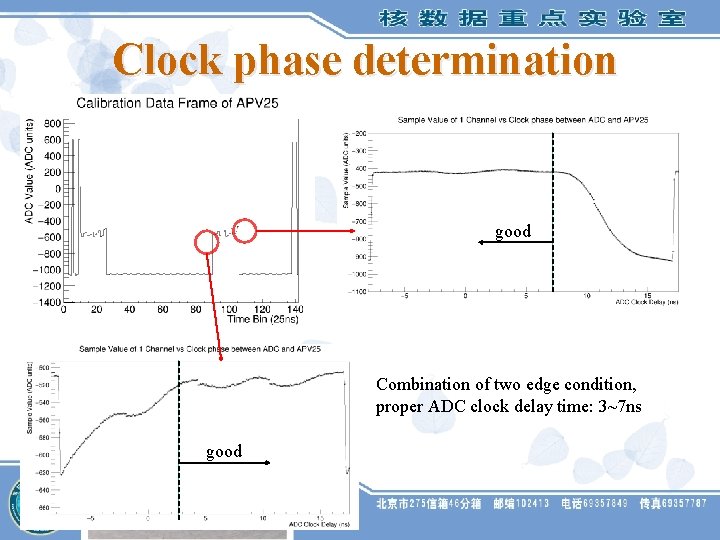

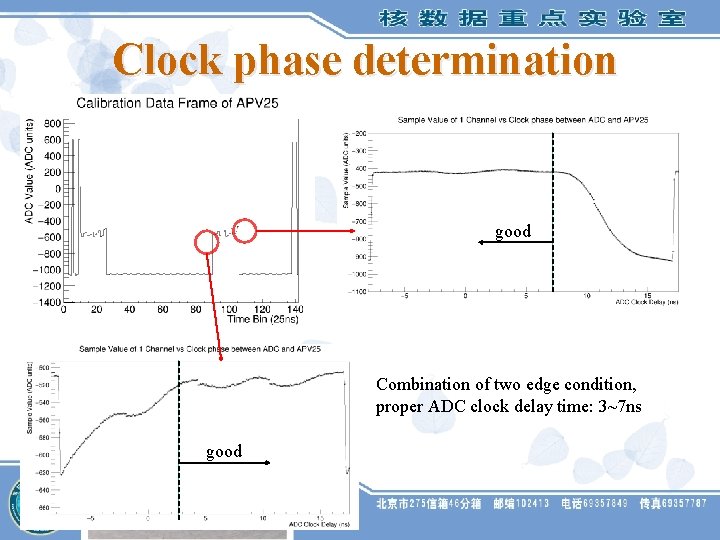

Clock phase determination good Combination of two edge condition, proper ADC clock delay time: 3~7 ns good

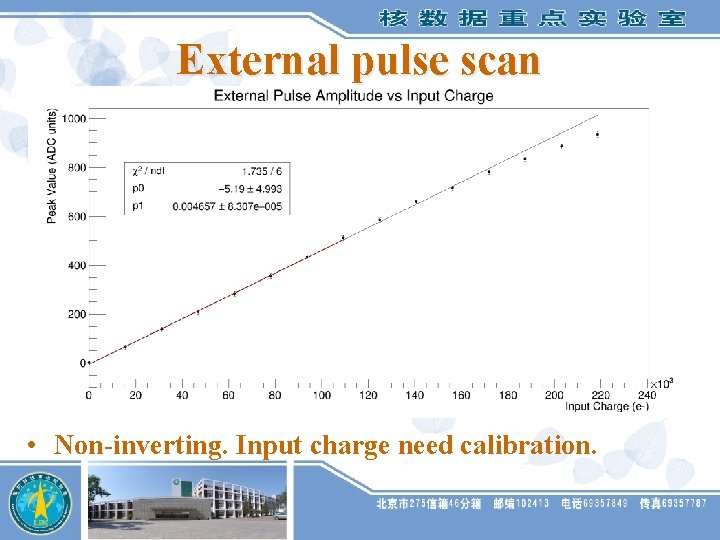

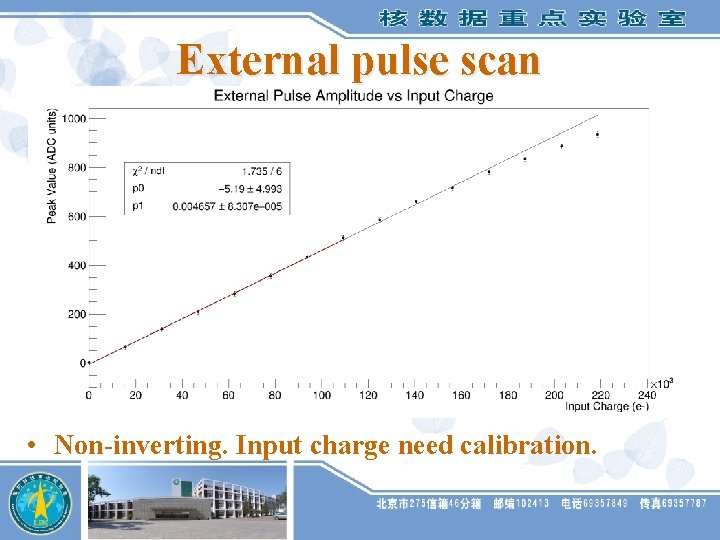

External pulse scan • Non-inverting. Input charge need calibration.