MP Core Algorithm and Design Techniques for Efficient

![Matching Pursuit Algorithm [KIM 04] n n Accurate and low complexity approximation to theoretical Matching Pursuit Algorithm [KIM 04] n n Accurate and low complexity approximation to theoretical](https://slidetodoc.com/presentation_image_h2/f0d03c9418c8d2882d2a8a88d2d12573/image-11.jpg)

- Slides: 26

MP Core ---- Algorithm and Design Techniques for Efficient Channel Estimation in Wireless Applications Yan Meng, Andrew P. Brown, Ronald A. Iltis, Timothy Sherwood, Hua Lee, and Ryan Kastner University of California, Santa Barbara Ex. PRESS Group: http: //express. ece. ucsb. edu

Outline n Background of wireless multipath fading and multipath channel estimation n Channel estimation problem formulation n Building an efficient channel estimator n n n Redesigning Matching Pursuit algorithm for efficient channel estimation Designing parameterized MP core on a RC device n Parameterization of the MP core n Data representation n Data distribution Conclusions

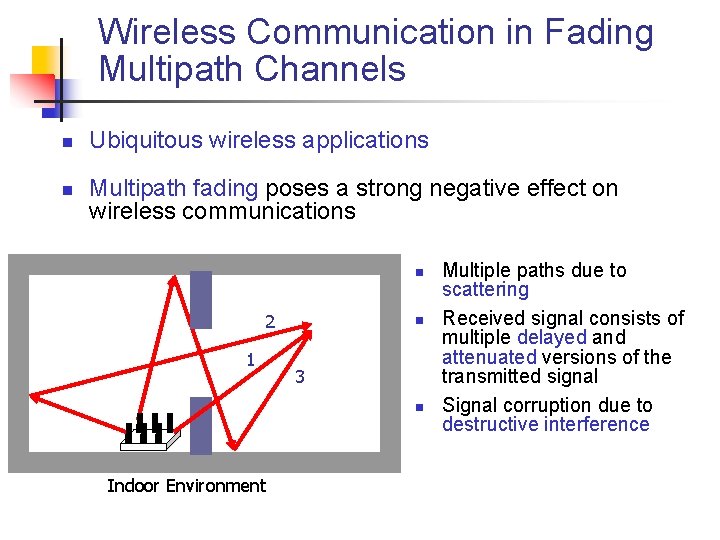

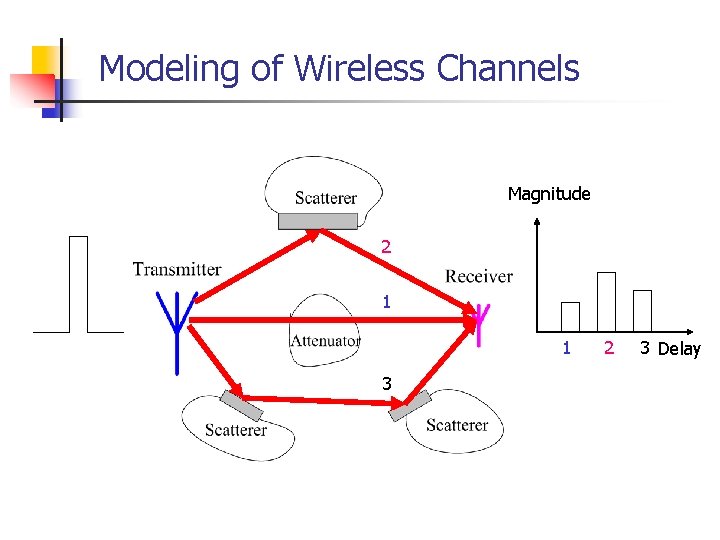

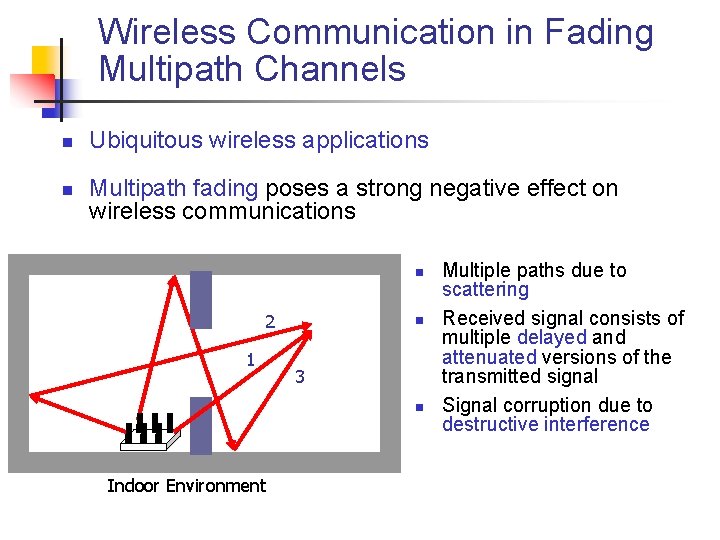

Wireless Communication in Fading Multipath Channels n n Ubiquitous wireless applications Multipath fading poses a strong negative effect on wireless communications n 2 1 n 3 n Indoor Environment Multiple paths due to scattering Received signal consists of multiple delayed and attenuated versions of the transmitted signal Signal corruption due to destructive interference

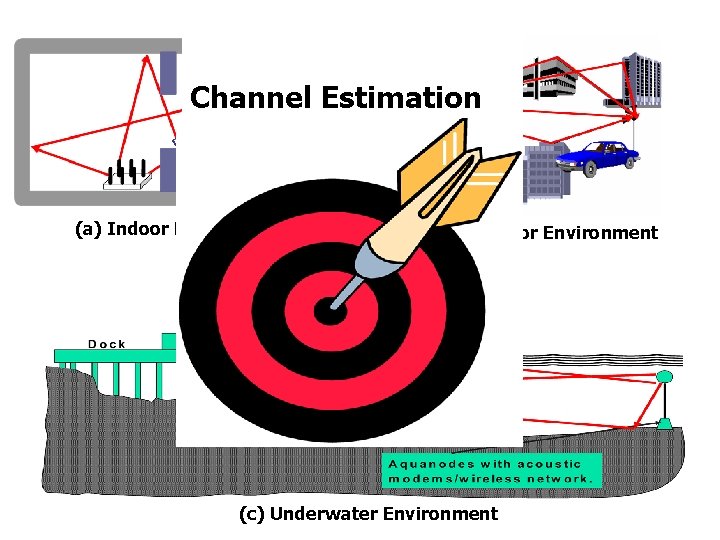

Channel Estimation h c re Di at p t (a) Indoor Environment (b) Outdoor Environment (c) Underwater Environment

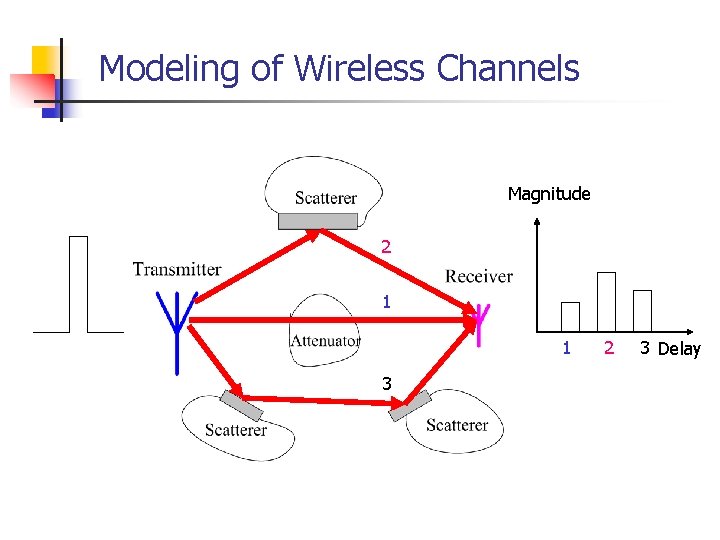

Modeling of Wireless Channels Magnitude 2 1 1 3 2 3 Delay

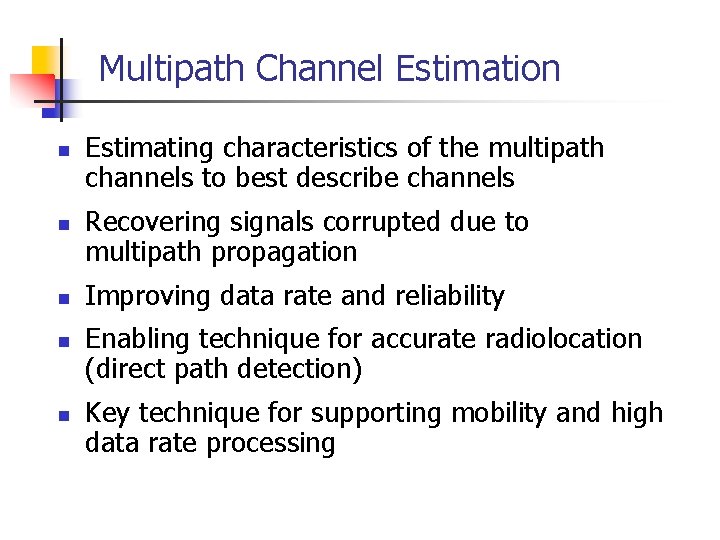

Multipath Channel Estimation n n Estimating characteristics of the multipath channels to best describe channels Recovering signals corrupted due to multipath propagation Improving data rate and reliability Enabling technique for accurate radiolocation (direct path detection) Key technique for supporting mobility and high data rate processing

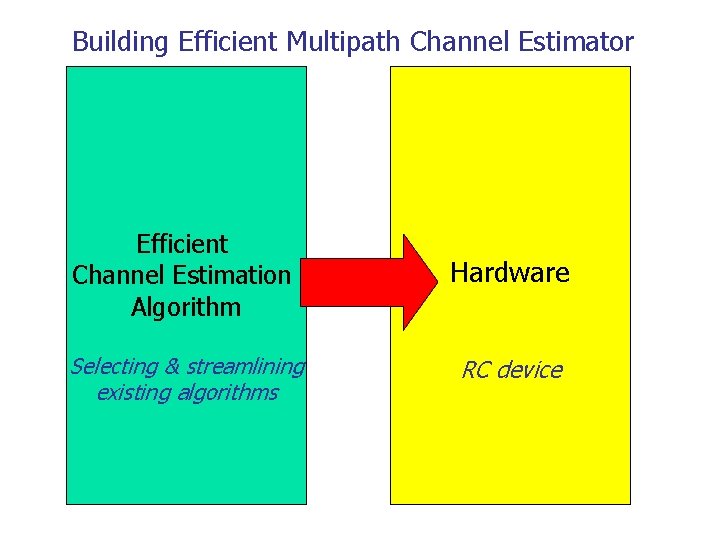

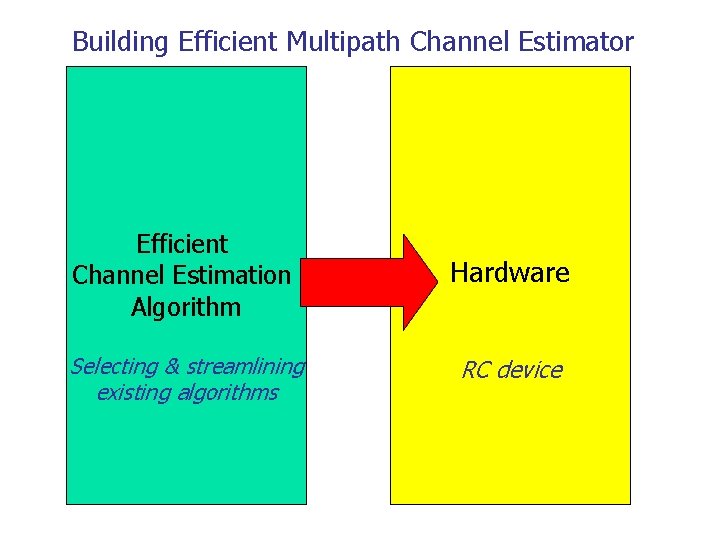

Building Efficient Multipath Channel Estimator Efficient Channel Estimation Algorithm Hardware Selecting & streamlining existing algorithms RC device

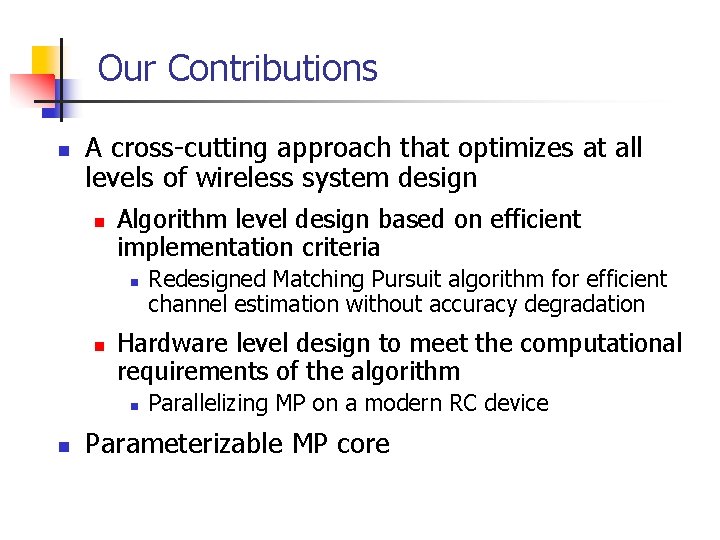

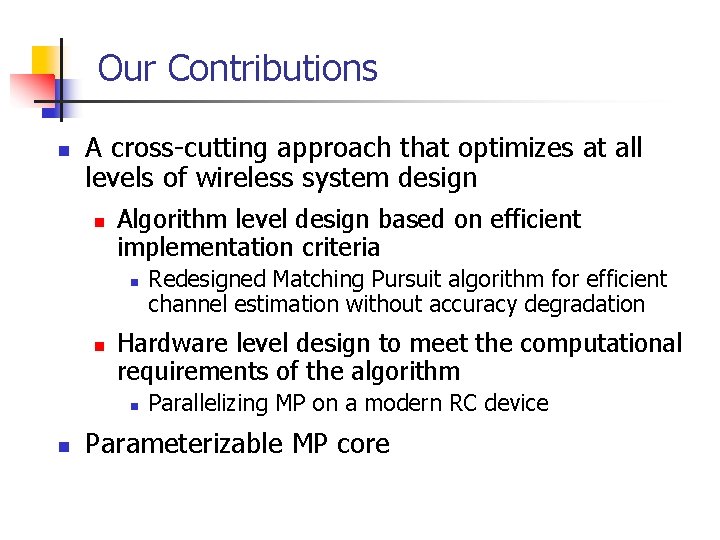

Our Contributions n A cross-cutting approach that optimizes at all levels of wireless system design n Algorithm level design based on efficient implementation criteria n n Hardware level design to meet the computational requirements of the algorithm n n Redesigned Matching Pursuit algorithm for efficient channel estimation without accuracy degradation Parallelizing MP on a modern RC device Parameterizable MP core

Efficient Channel Estimation Algorithm Hardware Selecting & streamlining existing algorithms RC device

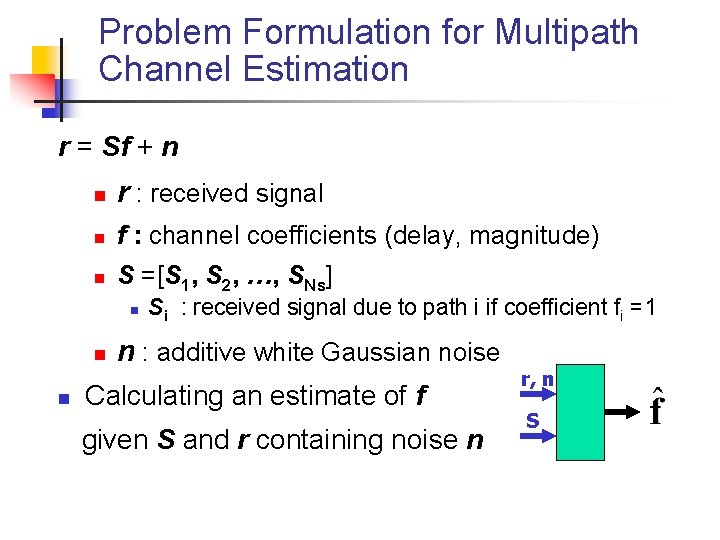

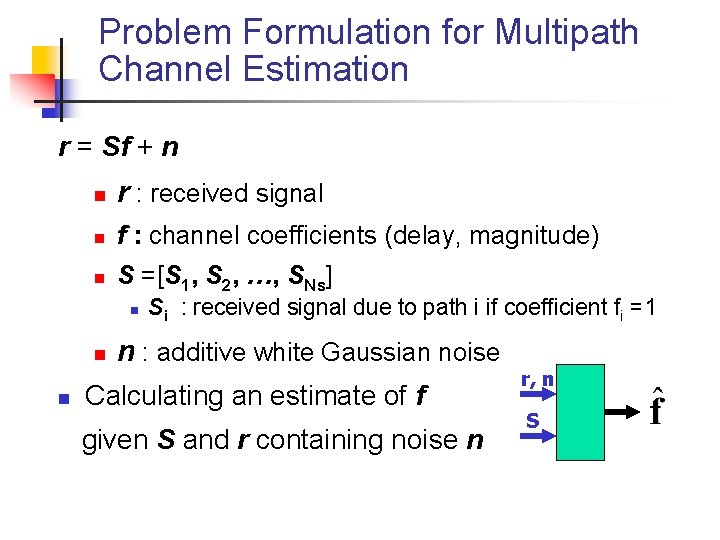

Problem Formulation for Multipath Channel Estimation r = Sf + n n r : received signal n f : channel coefficients (delay, magnitude) n S =[S 1, S 2, …, SNs] n n n Si : received signal due to path i if coefficient fi =1 n : additive white Gaussian noise Calculating an estimate of f given S and r containing noise n r, n S

![Matching Pursuit Algorithm KIM 04 n n Accurate and low complexity approximation to theoretical Matching Pursuit Algorithm [KIM 04] n n Accurate and low complexity approximation to theoretical](https://slidetodoc.com/presentation_image_h2/f0d03c9418c8d2882d2a8a88d2d12573/image-11.jpg)

Matching Pursuit Algorithm [KIM 04] n n Accurate and low complexity approximation to theoretical optimal -- ML solution for sparse channels A greedy algorithm to search for signal model parameters f to best explain measured data r Strongest path Direct path RMSE=0. 3%

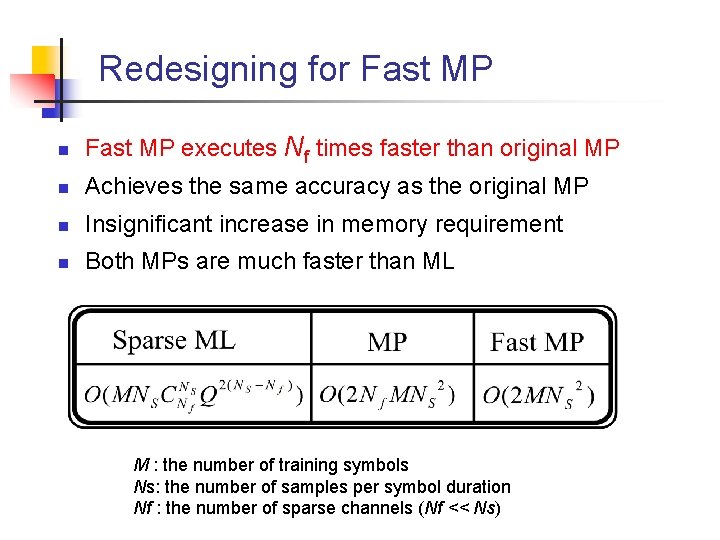

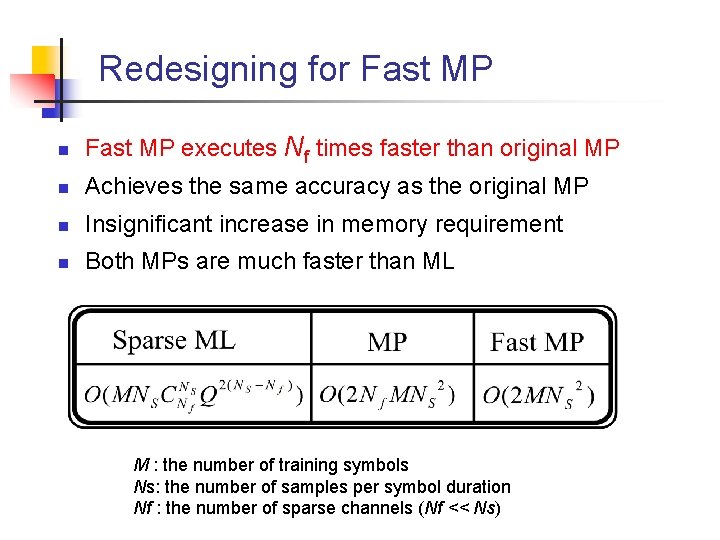

Redesigning for Fast MP n Fast MP executes Nf times faster than original MP n Achieves the same accuracy as the original MP n Insignificant increase in memory requirement n Both MPs are much faster than ML M : the number of training symbols Ns: the number of samples per symbol duration Nf : the number of sparse channels (Nf << Ns)

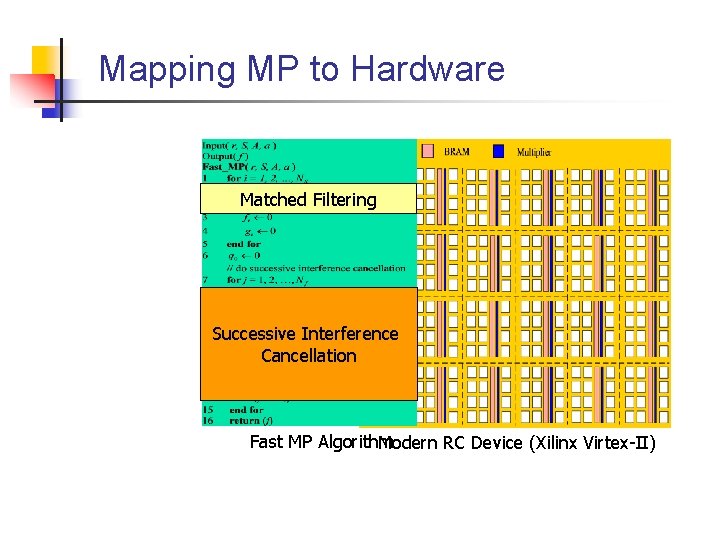

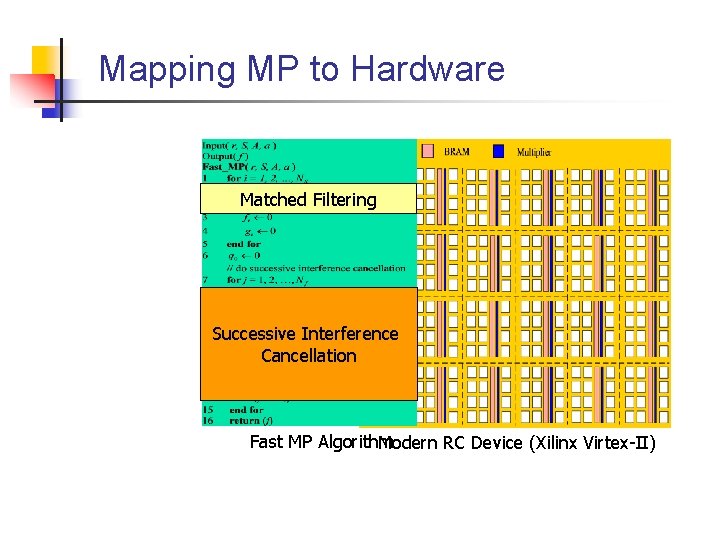

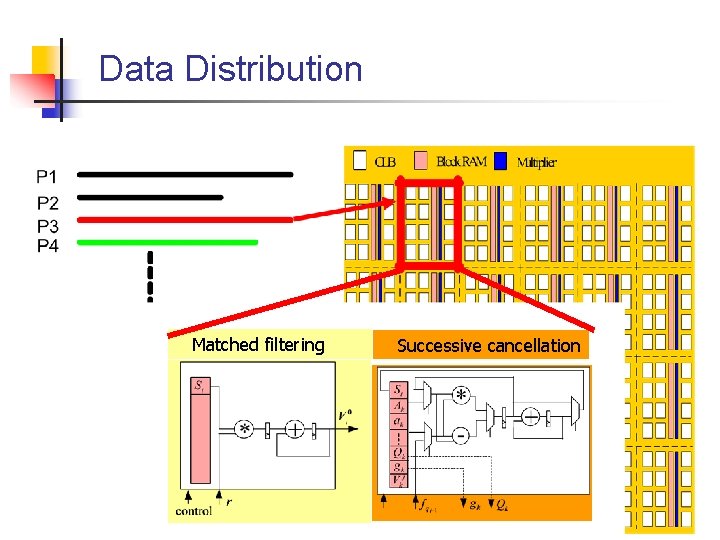

Mapping MP to Hardware Matched Filtering Successive Interference Cancellation Fast MP Algorithm Modern RC Device (Xilinx Virtex-II)

Design Space Exploration for the Parameterized MP Core n Parameterization of the MP core n Data representation n Data distribution

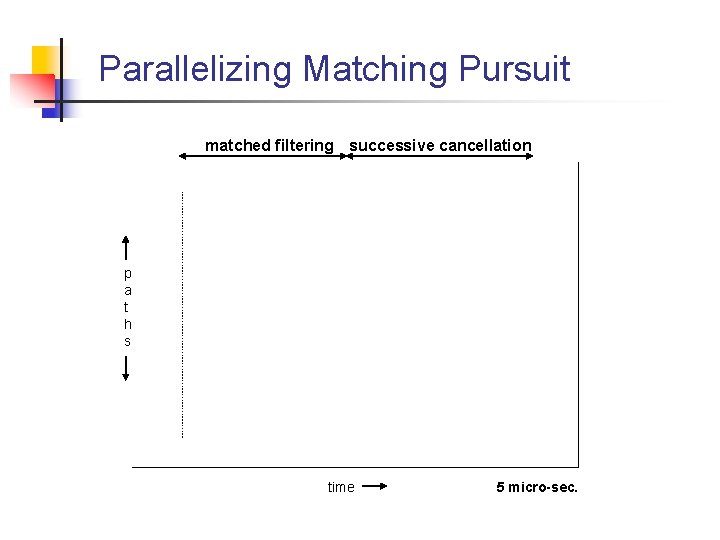

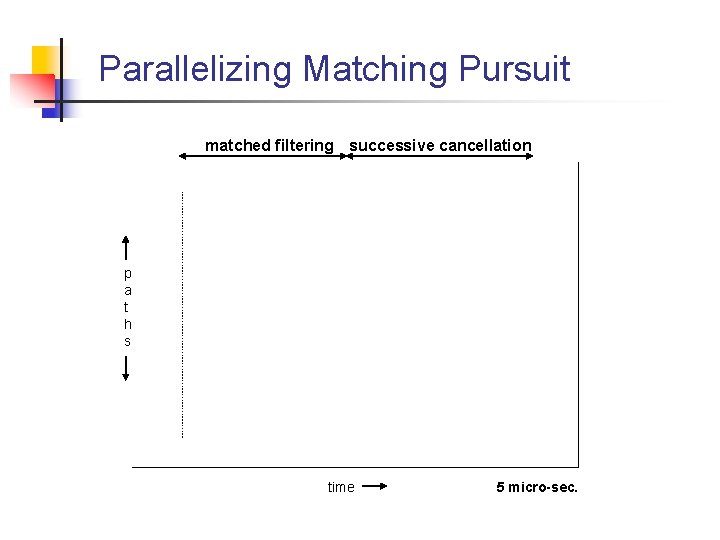

MP Core Parameterization n Tradeoff system parameters n Parameters in MP n n Number of training symbols (1) Number of sparse channels (15) Number of samples per symbol (88) The amount of hardware resources n n How much parallelism can be supported? Xilinx Virtex-II XC 2 V 3000 n n n 1728 KBits (96 BRAMs, 18 KBits/BRAM) 96 embedded multipliers (18 x 18 Bits) 3584 CLBs

Parallelizing Matching Pursuit matched filtering successive cancellation p a t h s time 5 micro-sec.

Data Representation n Floating point representation n Fixed point representation

Data Representation n Floating point representation n Large dynamic range and high precision n Costly in terms of area and performance 32 fixed point 3. 9 16 17. 9 584

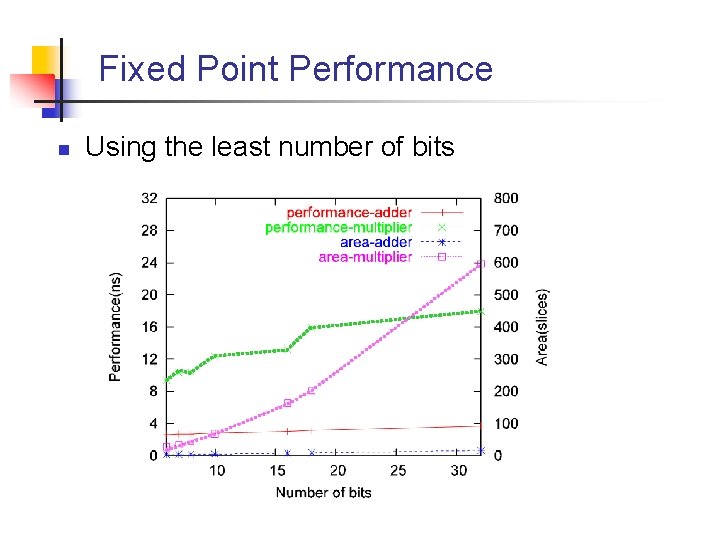

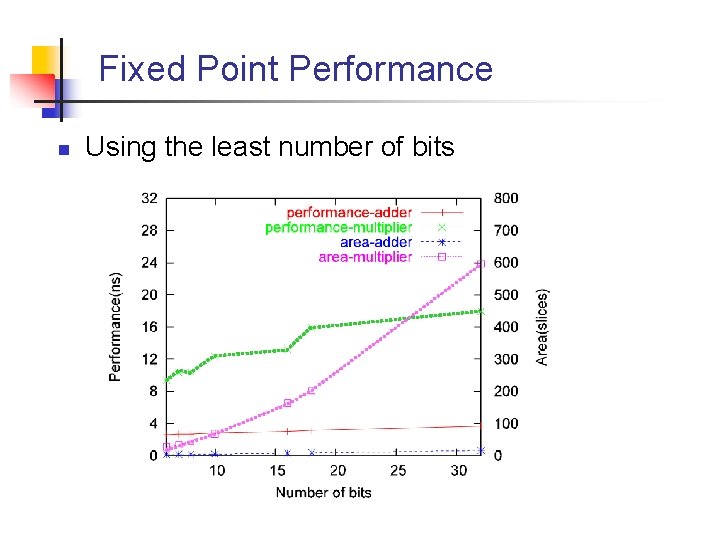

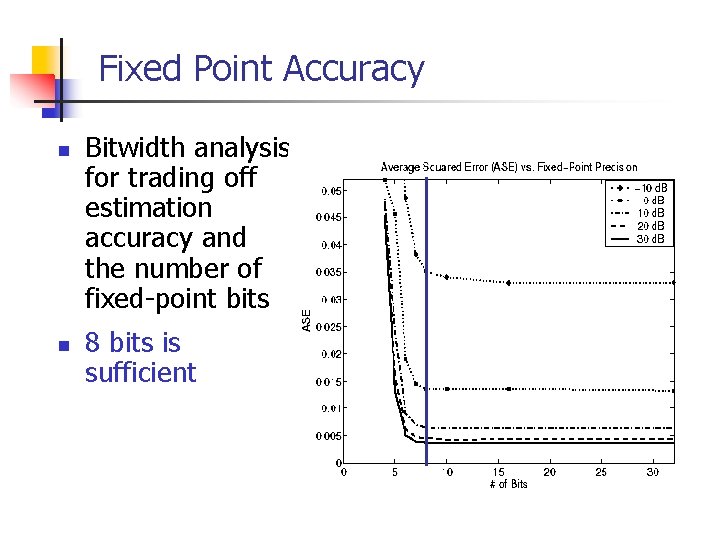

Fixed Point Performance n Using the least number of bits

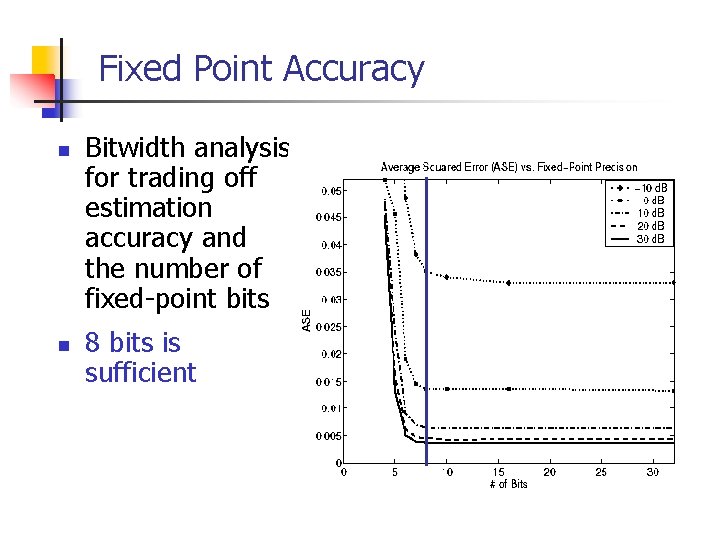

Fixed Point Accuracy n n Bitwidth analysis for trading off estimation accuracy and the number of fixed-point bits 8 bits is sufficient

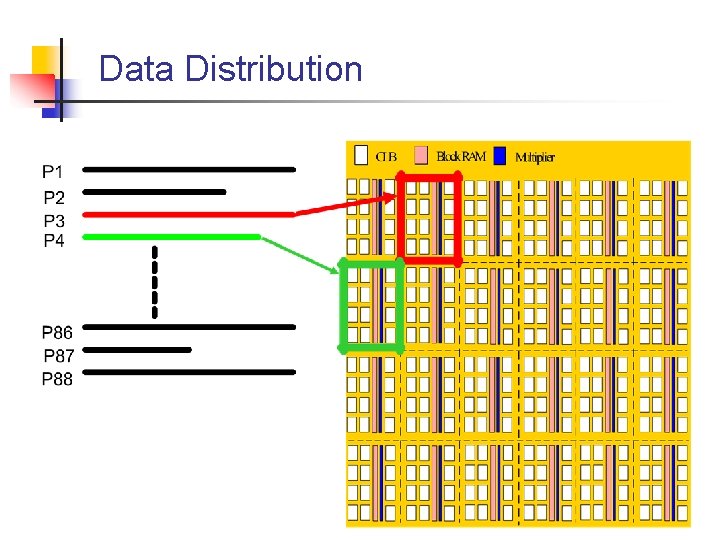

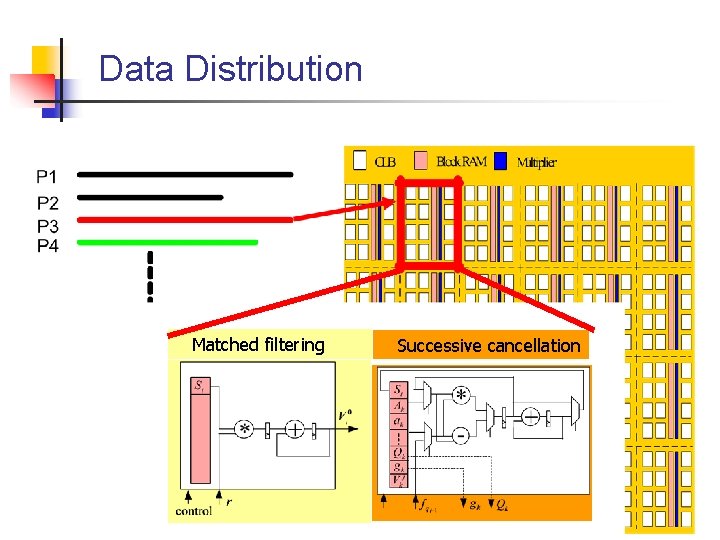

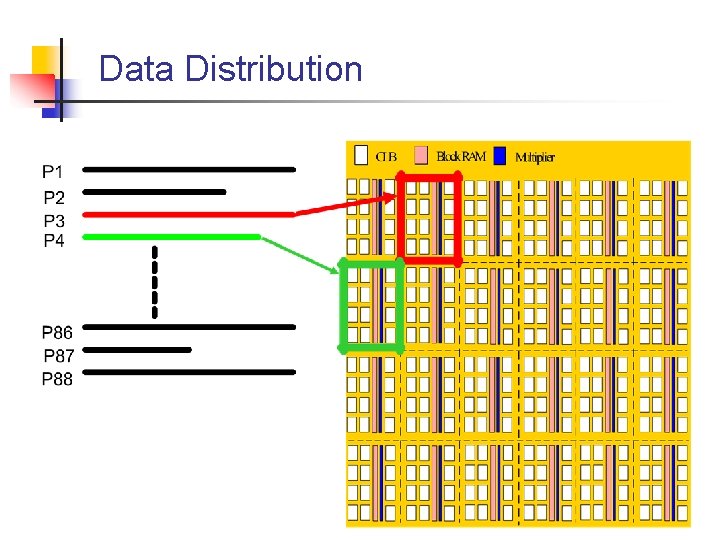

Data Distribution

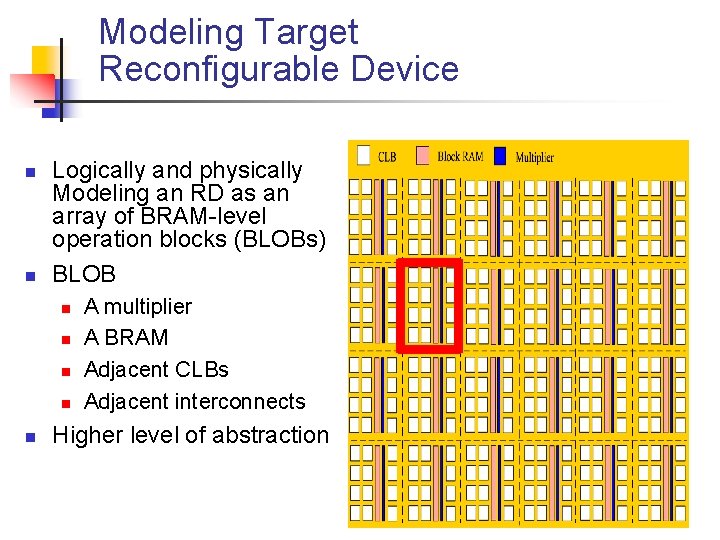

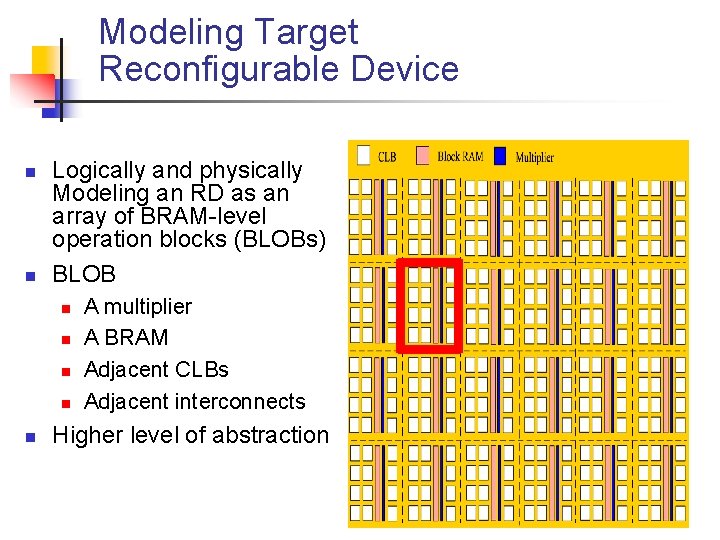

Modeling Target Reconfigurable Device n n Logically and physically Modeling an RD as an array of BRAM-level operation blocks (BLOBs) BLOB n n n A multiplier A BRAM Adjacent CLBs Adjacent interconnects Higher level of abstraction

Data Distribution Matched filtering Successive cancellation

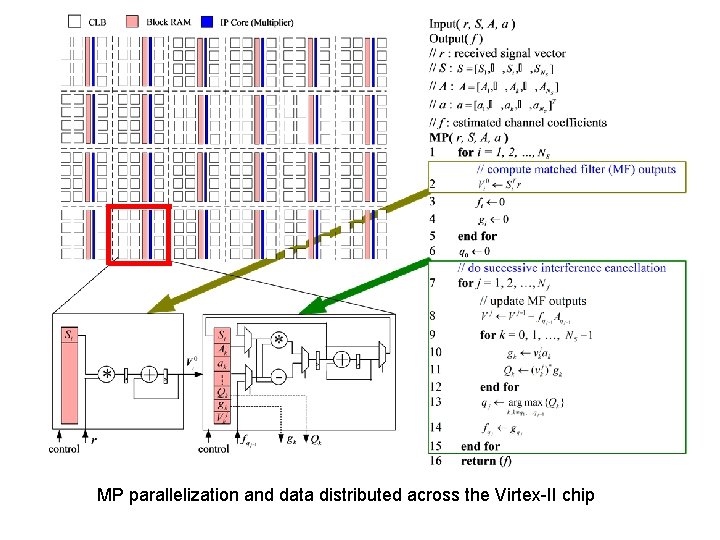

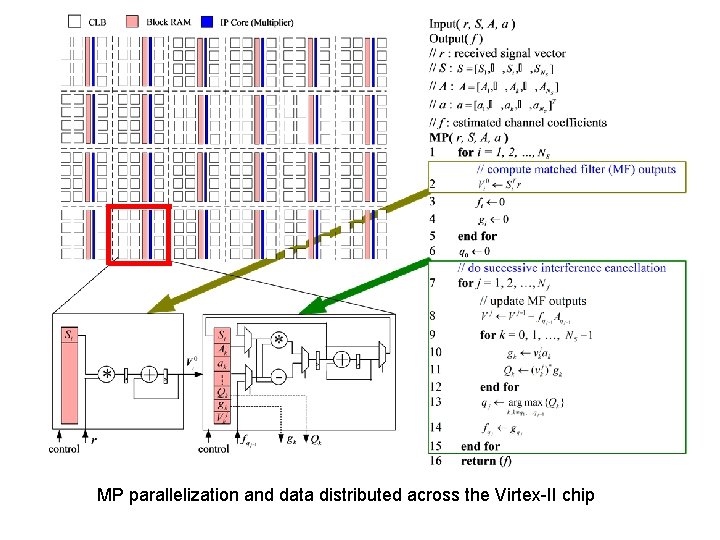

MP parallelization and data distributed across the Virtex-II chip

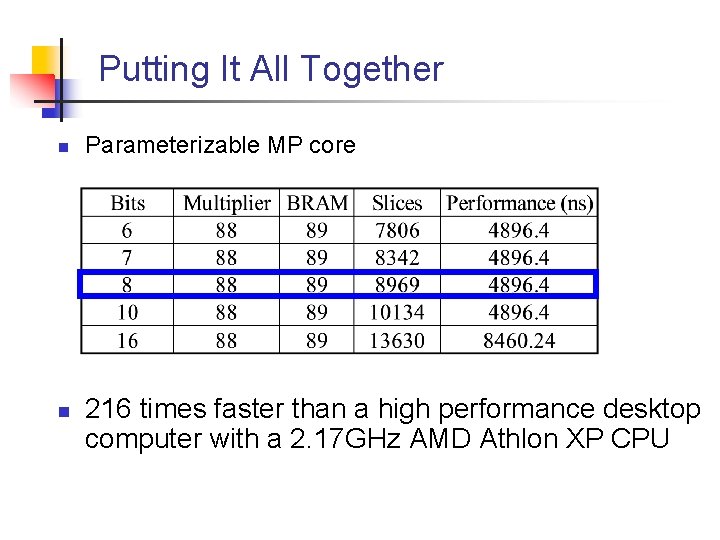

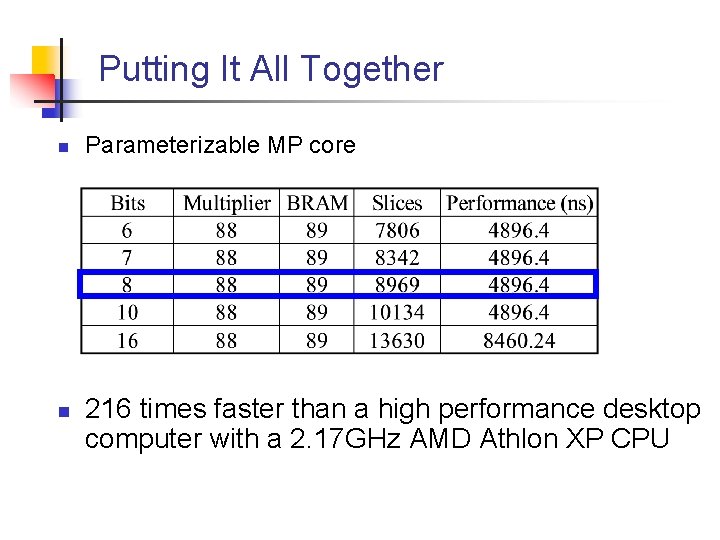

Putting It All Together n n Parameterizable MP core 216 times faster than a high performance desktop computer with a 2. 17 GHz AMD Athlon XP CPU

Conclusions n Channel estimation: key technique for high speed and reliable wireless communications n n n Redesigned Fast Matching Pursuit n Nf times faster n Same accuracy n Insignificant increase in memory requirement Designed parameterizable MP core n MP parameterization n Data representation n Data distribution MP core: 216 times faster than a high performance computer