Motivation for CDR Deserializer 1 1 2 DMUX

- Slides: 46

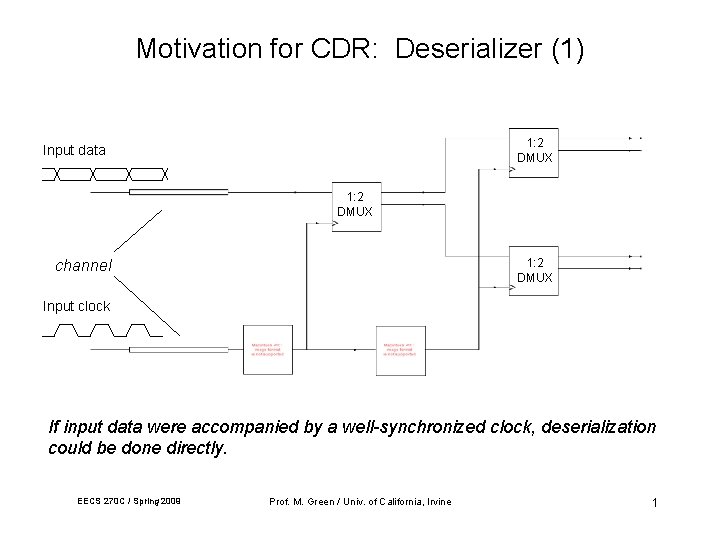

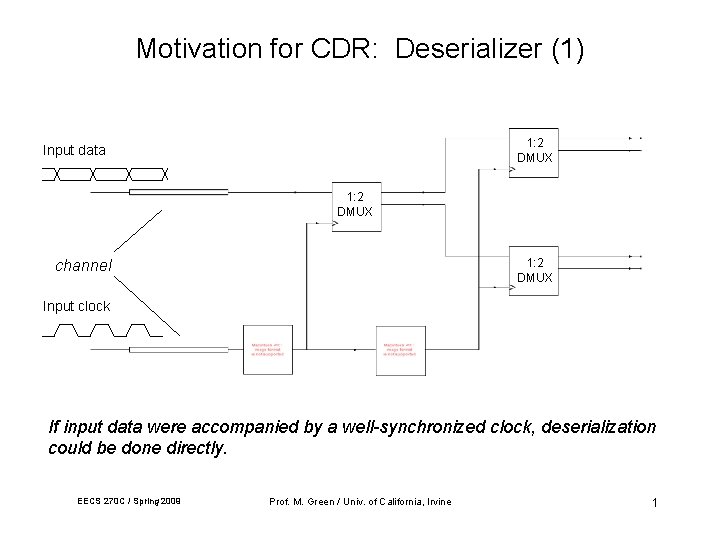

Motivation for CDR: Deserializer (1) 1: 2 DMUX Input data 1: 2 DMUX channel Input clock If input data were accompanied by a well-synchronized clock, deserialization could be done directly. EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 1

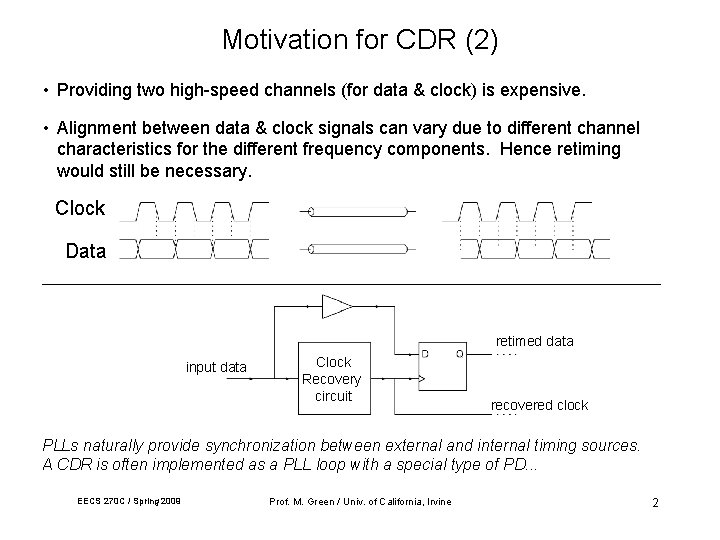

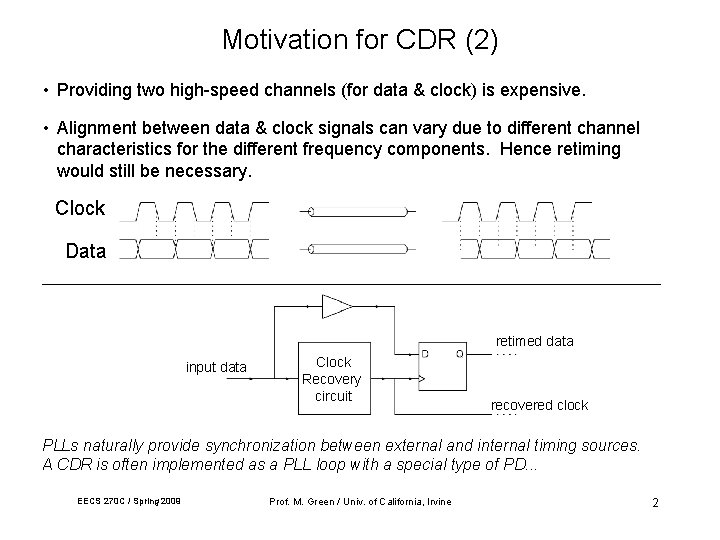

Motivation for CDR (2) • Providing two high-speed channels (for data & clock) is expensive. • Alignment between data & clock signals can vary due to different channel characteristics for the different frequency components. Hence retiming would still be necessary. Clock Data retimed data input data Clock Recovery circuit recovered clock PLLs naturally provide synchronization between external and internal timing sources. A CDR is often implemented as a PLL loop with a special type of PD. . . EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 2

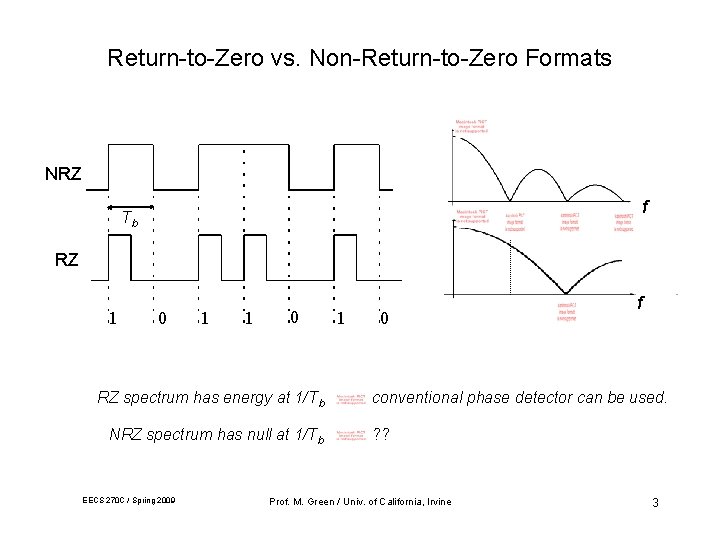

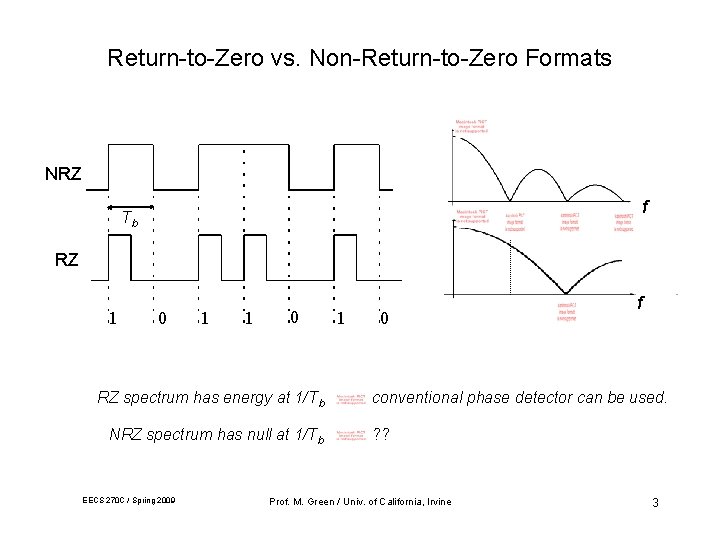

Return-to-Zero vs. Non-Return-to-Zero Formats NRZ f Tb RZ 1 0 1 1 0 RZ spectrum has energy at 1/Tb NRZ spectrum has null at 1/Tb EECS 270 C / Spring 2009 1 0 f conventional phase detector can be used. ? ? Prof. M. Green / Univ. of California, Irvine 3

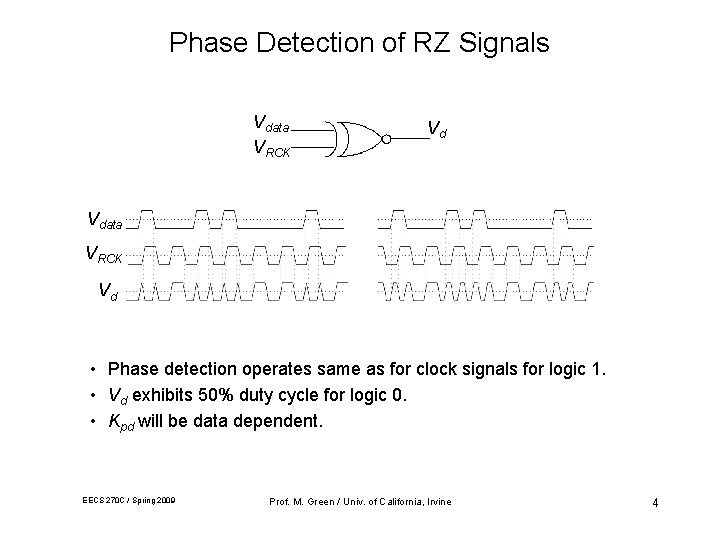

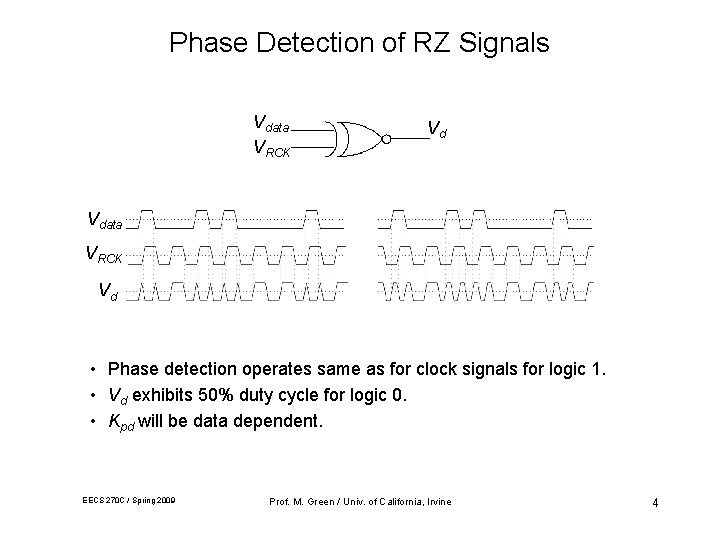

Phase Detection of RZ Signals Vdata VRCK Vd • Phase detection operates same as for clock signals for logic 1. • Vd exhibits 50% duty cycle for logic 0. • Kpd will be data dependent. EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 4

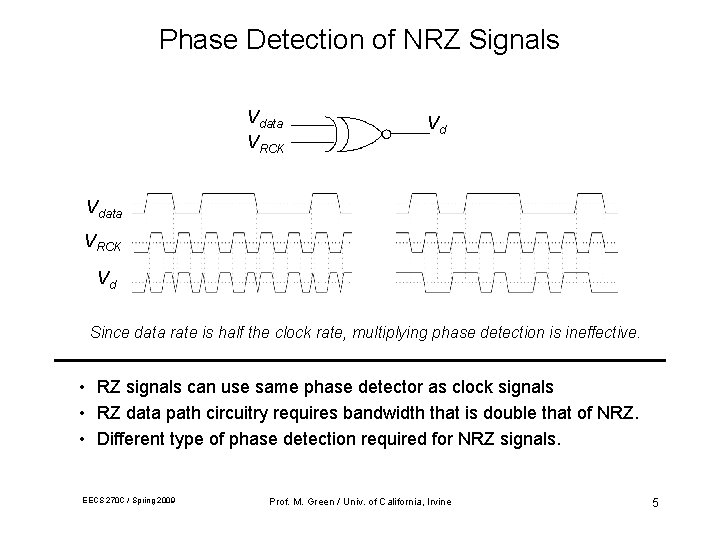

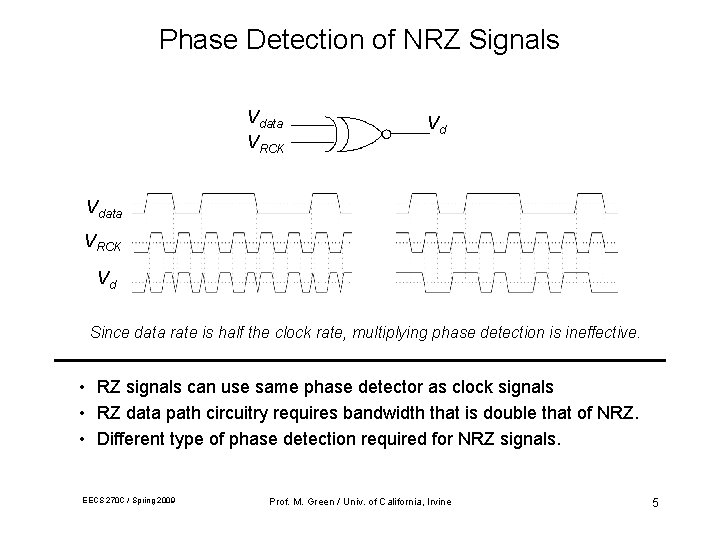

Phase Detection of NRZ Signals Vdata VRCK Vd Since data rate is half the clock rate, multiplying phase detection is ineffective. • RZ signals can use same phase detector as clock signals • RZ data path circuitry requires bandwidth that is double that of NRZ. • Different type of phase detection required for NRZ signals. EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 5

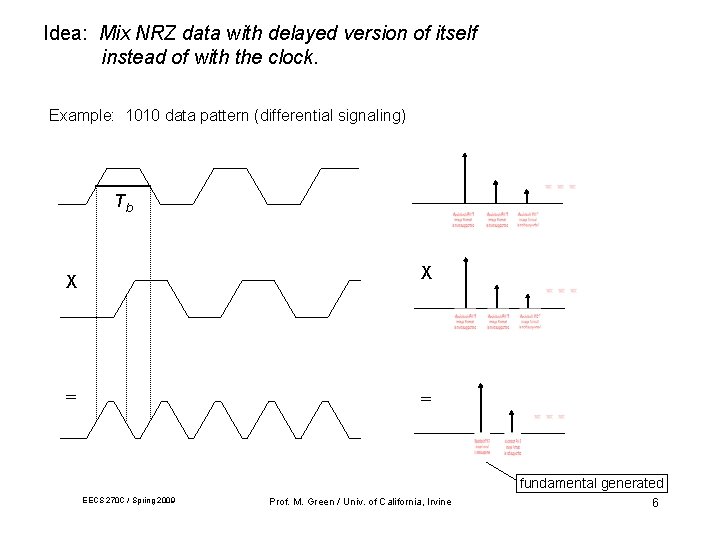

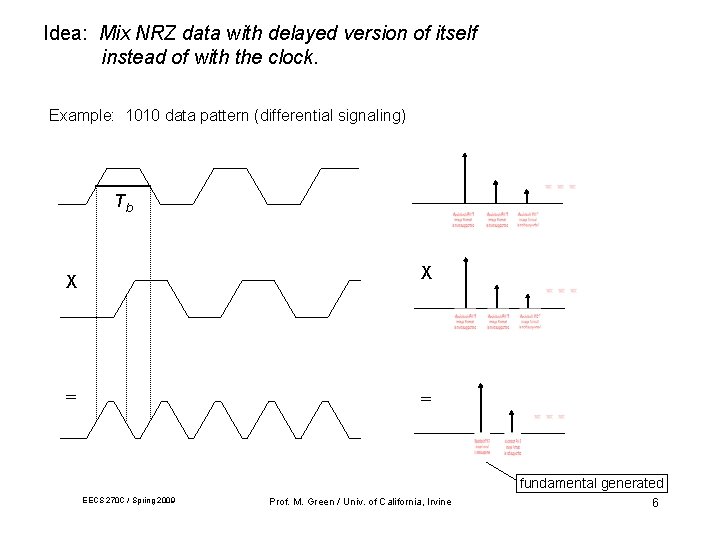

Idea: Mix NRZ data with delayed version of itself instead of with the clock. Example: 1010 data pattern (differential signaling) Tb X X = = fundamental generated EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 6

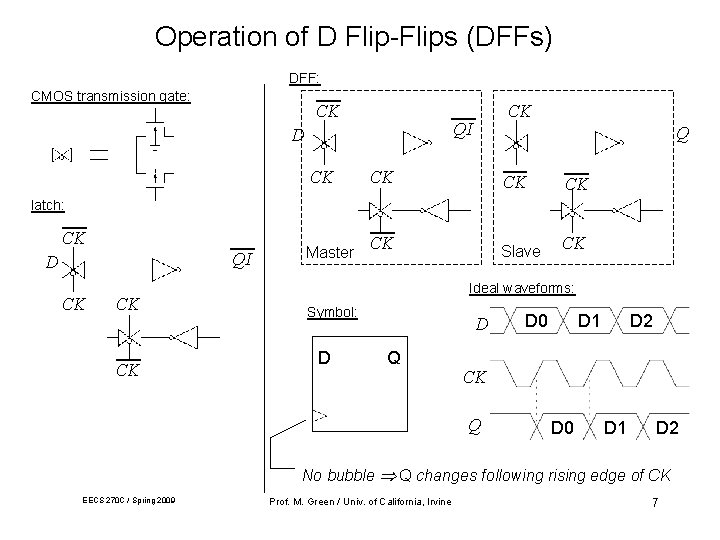

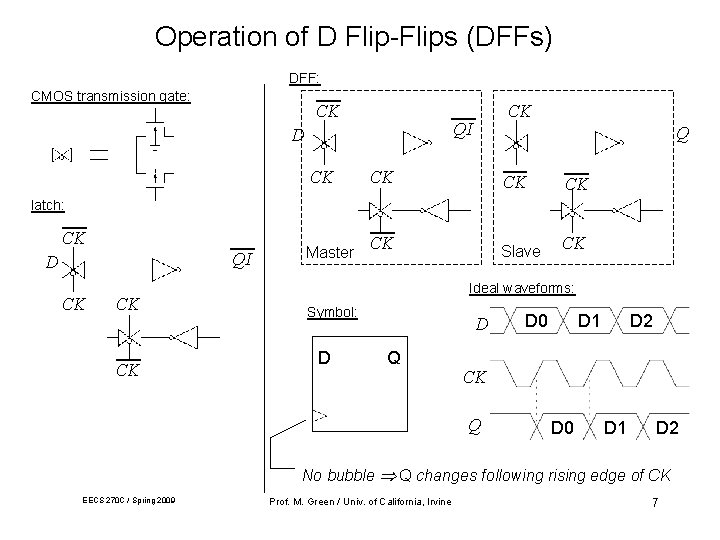

Operation of D Flip-Flips (DFFs) DFF: CMOS transmission gate: CK QI D CK CK Q CK CK Slave CK latch: CK QI D CK CK CK Master Ideal waveforms: Symbol: D D Q D 0 D 1 D 2 CK Q D 0 D 1 D 2 No bubble Q changes following rising edge of CK EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 7

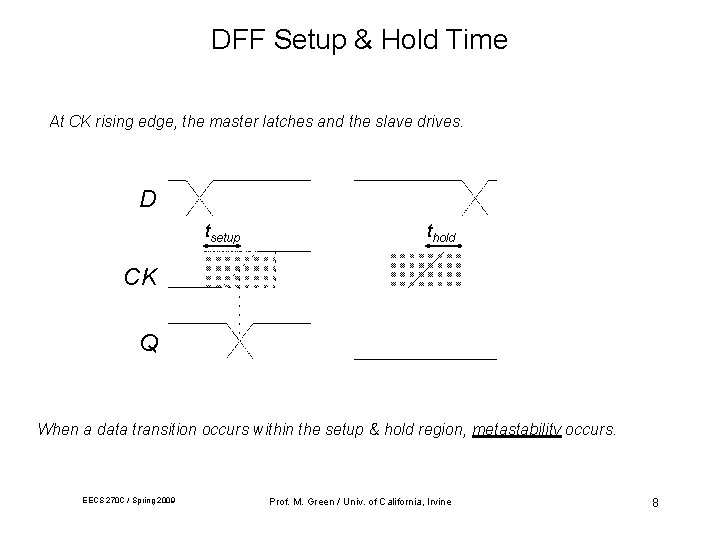

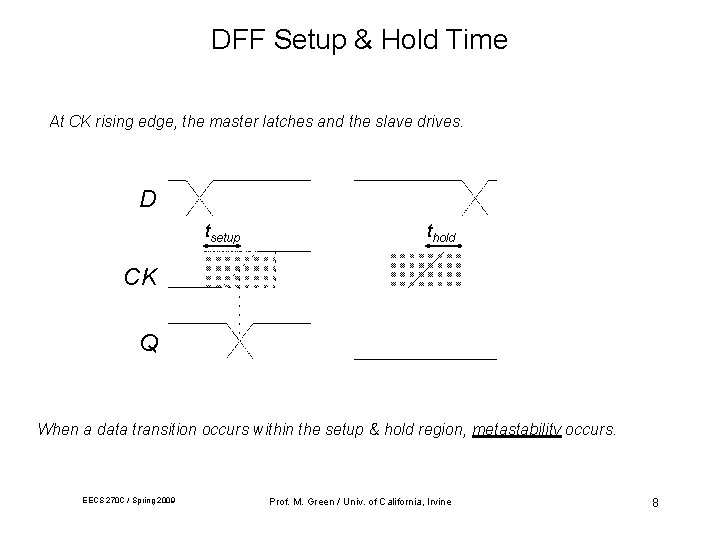

DFF Setup & Hold Time At CK rising edge, the master latches and the slave drives. D tsetup thold CK Q When a data transition occurs within the setup & hold region, metastability occurs. EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 8

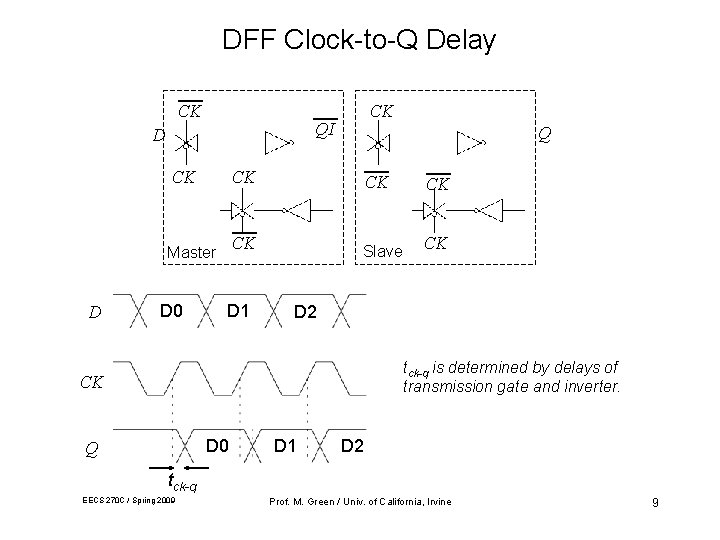

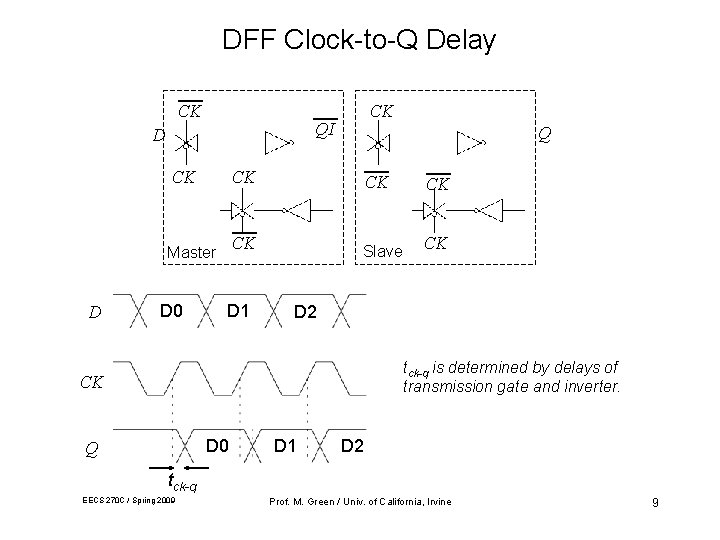

DFF Clock-to-Q Delay CK QI D CK Master D D 0 CK Q CK CK Slave CK D 1 D 2 tck-q is determined by delays of transmission gate and inverter. CK D 0 Q D 1 D 2 tck-q EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 9

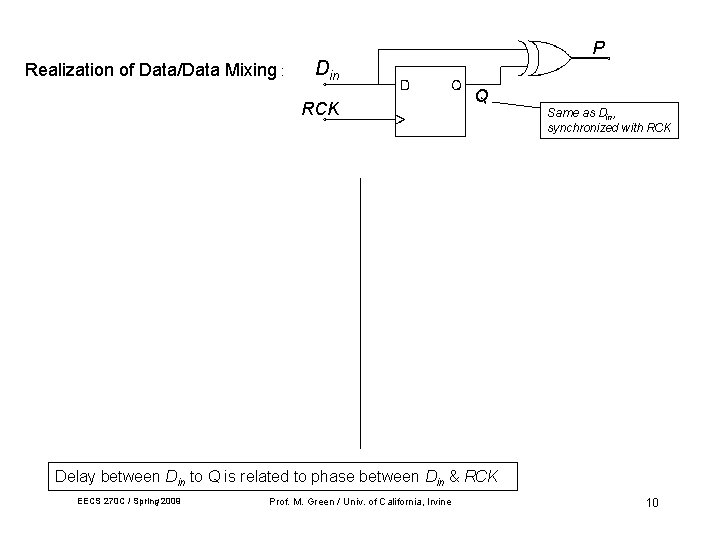

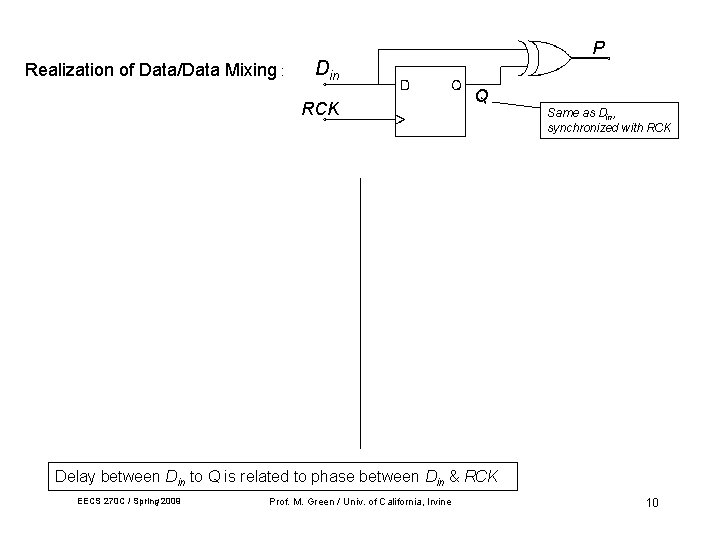

Realization of Data/Data Mixing : P Din Q RCK early: Din Same as Din, synchronized with RCK synchronized: D 1 D 0 D 2 D 0 D 3 D 1 D 2 D 3 RCK Q D 0 D 1 D 2 D 0 D 3 D 1 D 2 D 3 P D 0 D 1 D 2 D 3 D 4 Delay between Din to Q is related to phase between Din & RCK EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 10

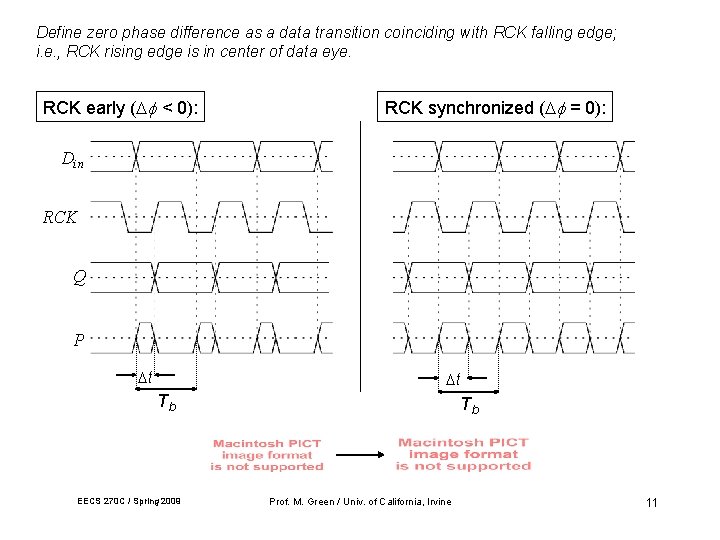

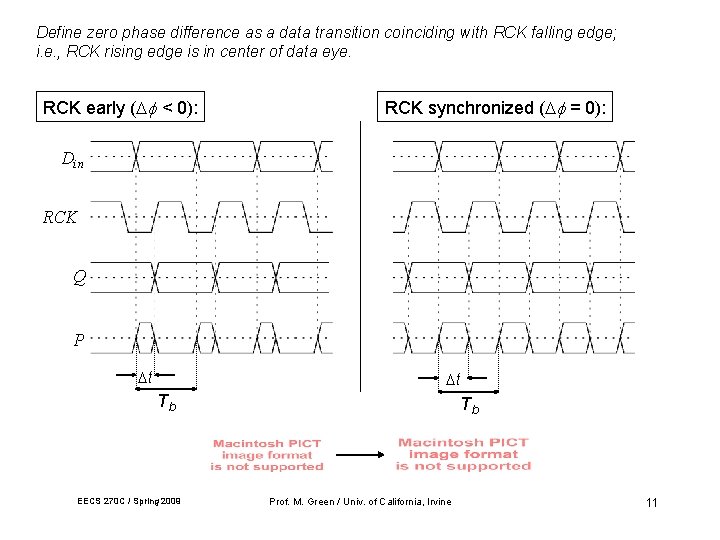

Define zero phase difference as a data transition coinciding with RCK falling edge; i. e. , RCK rising edge is in center of data eye. RCK early ( < 0): RCK synchronized ( = 0): Din RCK Q P t t Tb EECS 270 C / Spring 2009 Tb Prof. M. Green / Univ. of California, Irvine 11

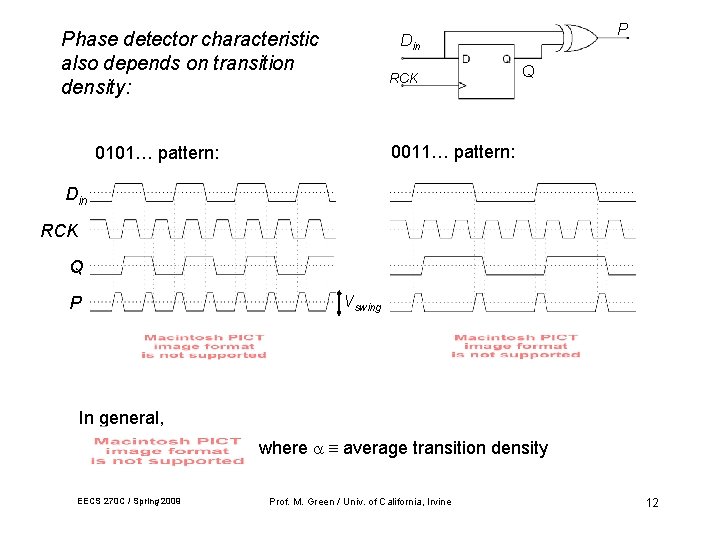

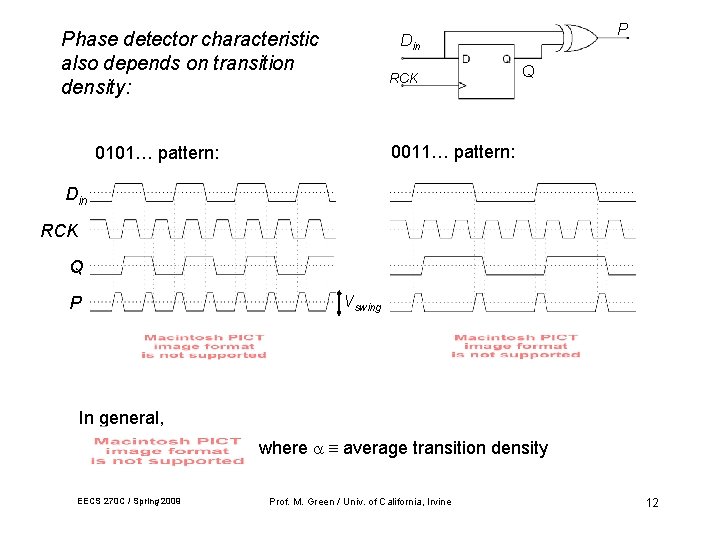

Phase detector characteristic also depends on transition density: P Din RCK Q 0011… pattern: 0101… pattern: Din RCK Q P Vswing In general, where average transition density EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 12

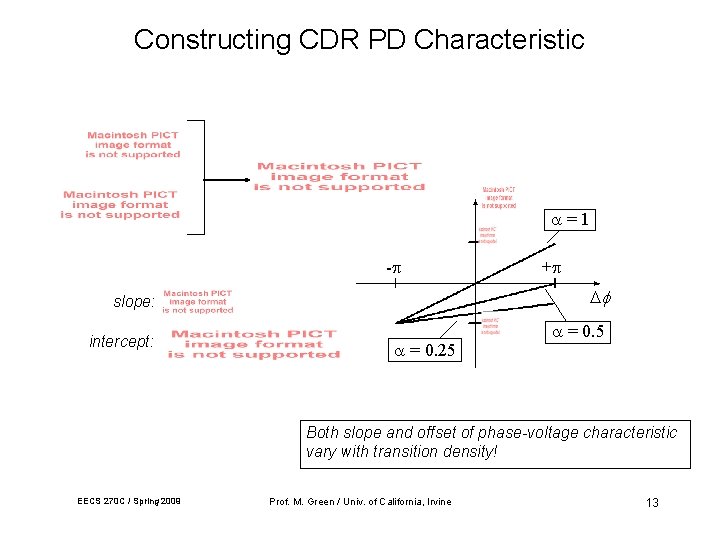

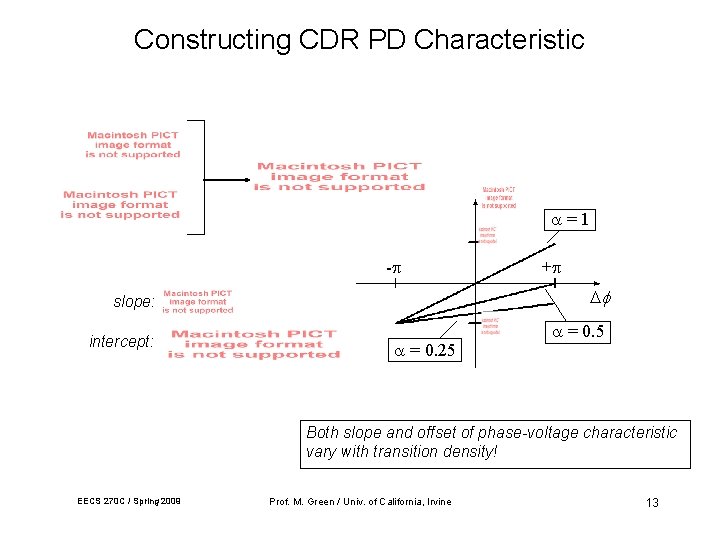

Constructing CDR PD Characteristic =1 -p slope: intercept: +p = 0. 25 = 0. 5 Both slope and offset of phase-voltage characteristic vary with transition density! EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 13

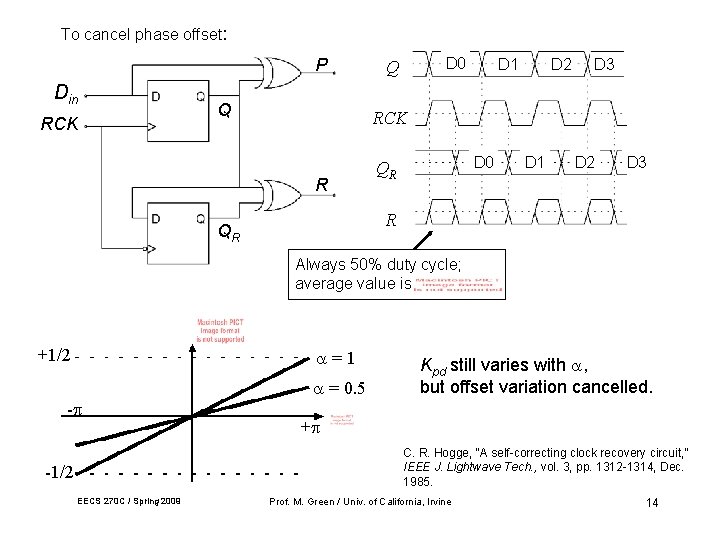

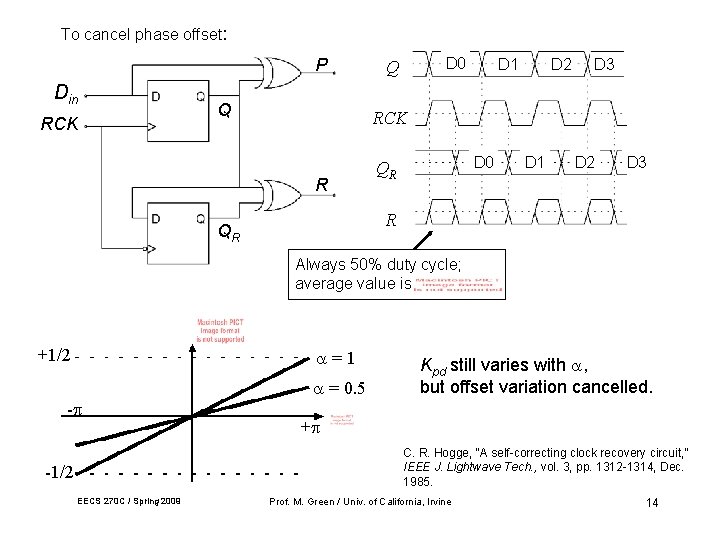

To cancel phase offset: P Din RCK Q D 0 Q D 1 D 2 D 3 RCK R D 0 QR D 1 D 2 D 3 R QR Always 50% duty cycle; average value is +1/2 =1 = 0. 5 -p Kpd still varies with , but offset variation cancelled. +p C. R. Hogge, “A self-correcting clock recovery circuit, ” IEEE J. Lightwave Tech. , vol. 3, pp. 1312 -1314, Dec. 1985. -1/2 EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 14

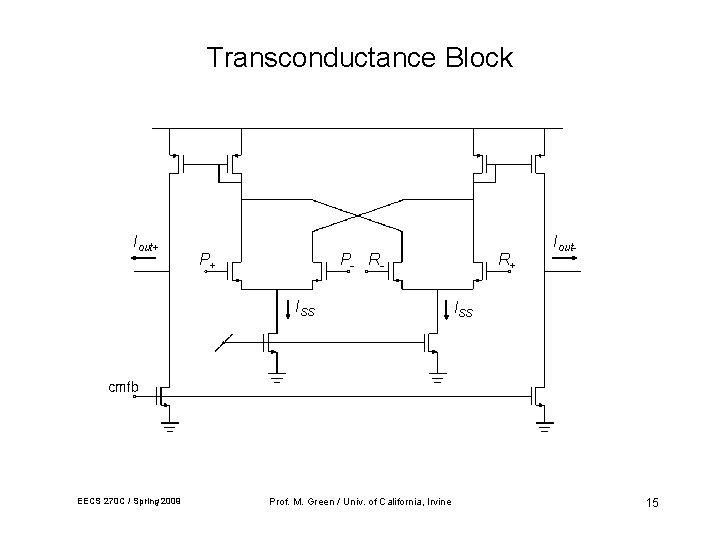

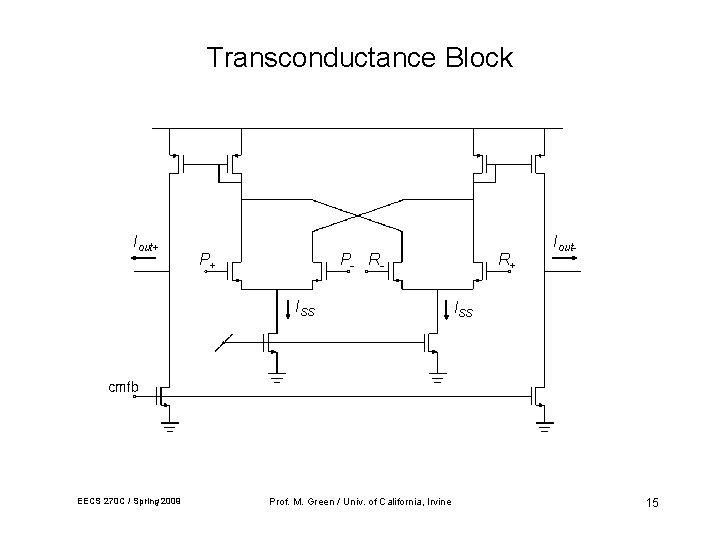

Transconductance Block Iout+ P+ P - RISS EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine R+ Iout- ISS 15

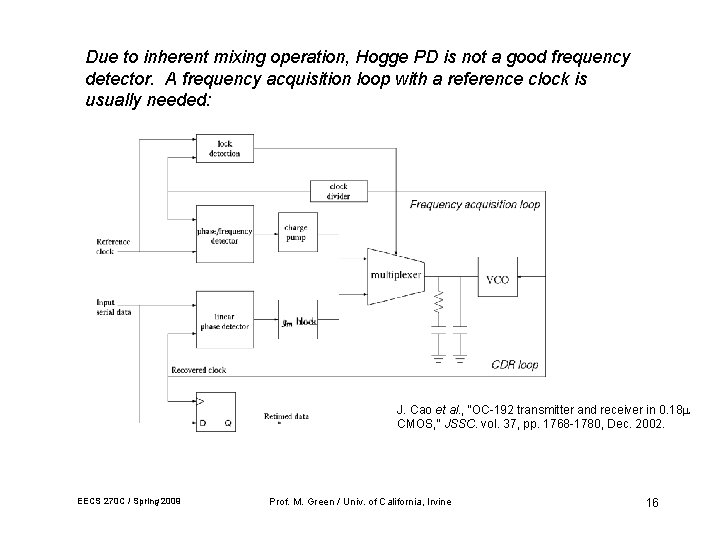

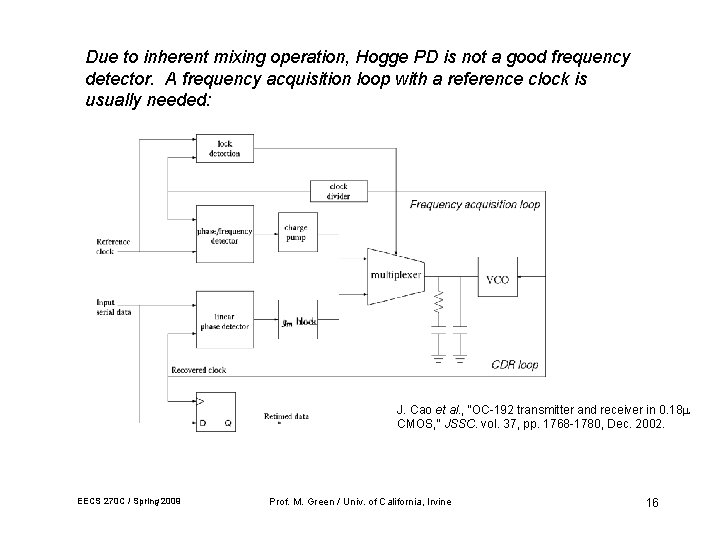

Due to inherent mixing operation, Hogge PD is not a good frequency detector. A frequency acquisition loop with a reference clock is usually needed: J. Cao et al. , “OC-192 transmitter and receiver in 0. 18 m CMOS, ” JSSC. vol. 37, pp. 1768 -1780, Dec. 2002. EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 16

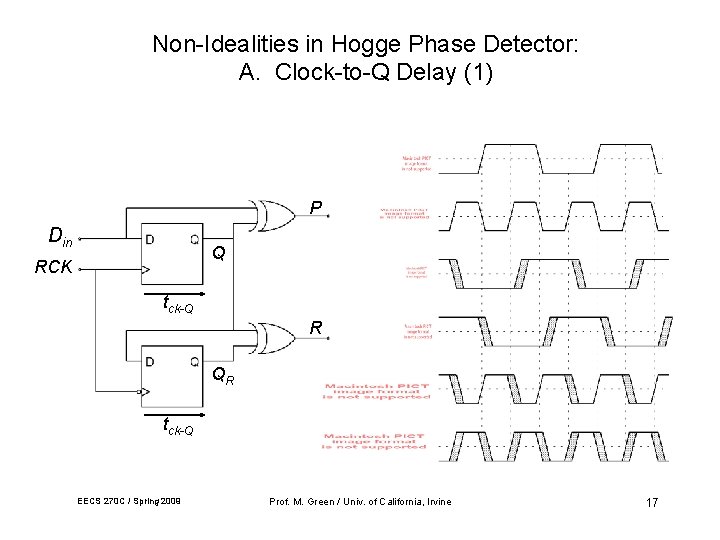

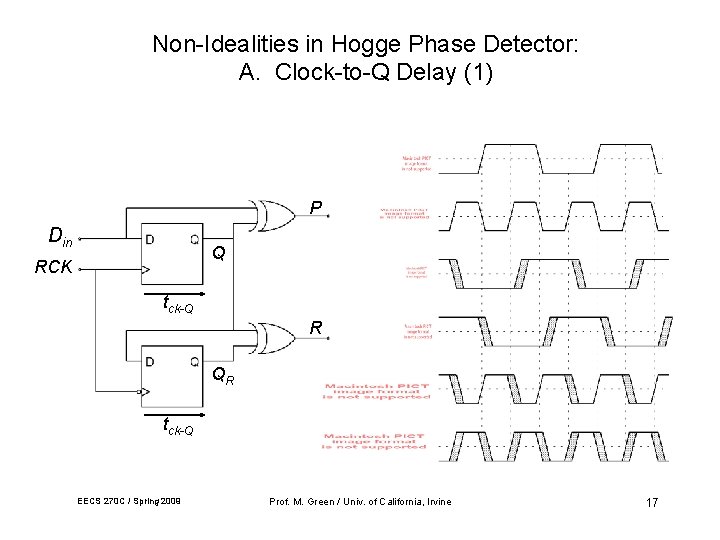

Non-Idealities in Hogge Phase Detector: A. Clock-to-Q Delay (1) P Din Q RCK tck-Q R QR tck-Q EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 17

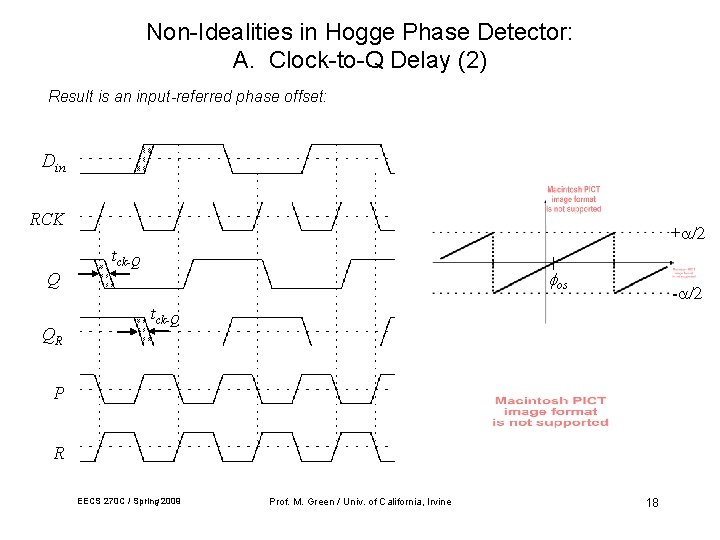

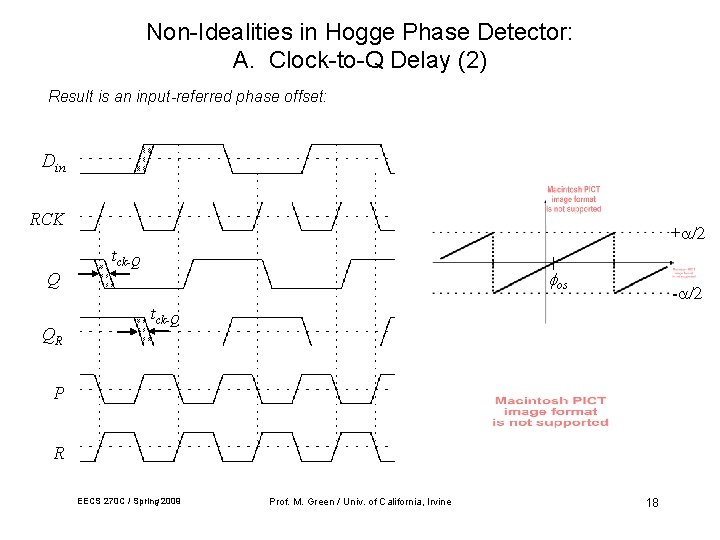

Non-Idealities in Hogge Phase Detector: A. Clock-to-Q Delay (2) Result is an input-referred phase offset: Din RCK + /2 tck-Q os Q QR - /2 tck-Q P R EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 18

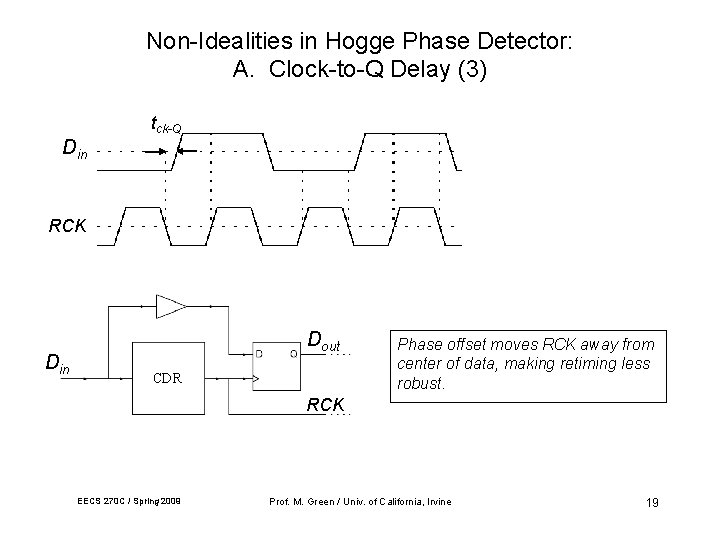

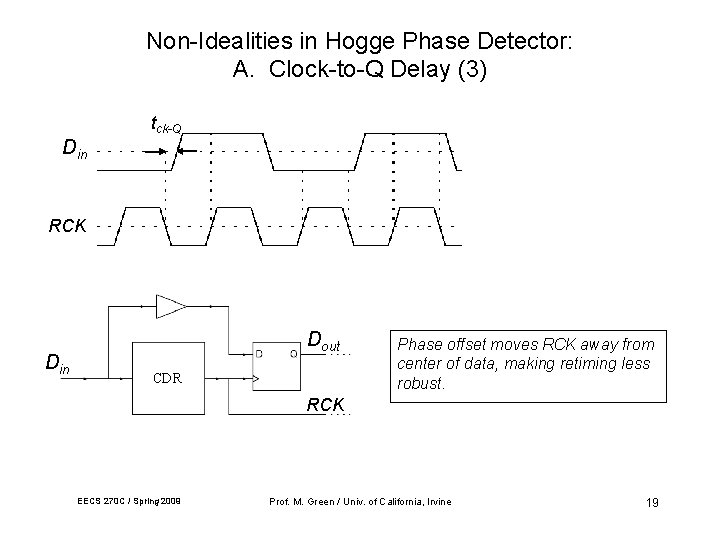

Non-Idealities in Hogge Phase Detector: A. Clock-to-Q Delay (3) tck-Q Din RCK Din Dout CDR Phase offset moves RCK away from center of data, making retiming less robust. RCK EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 19

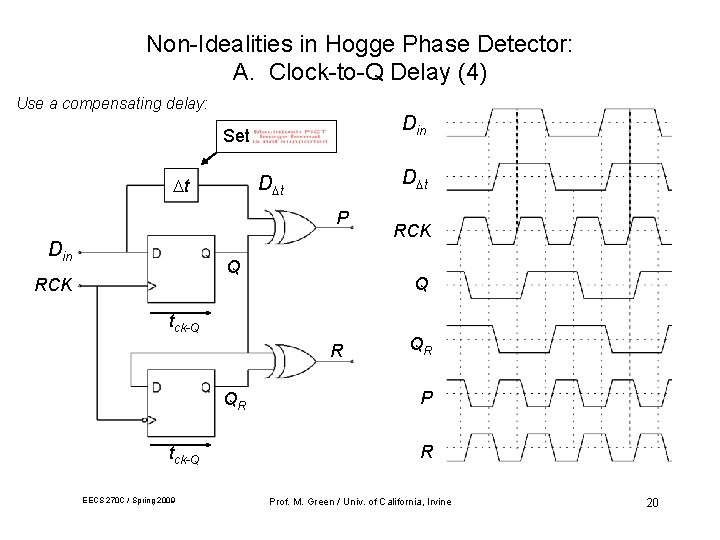

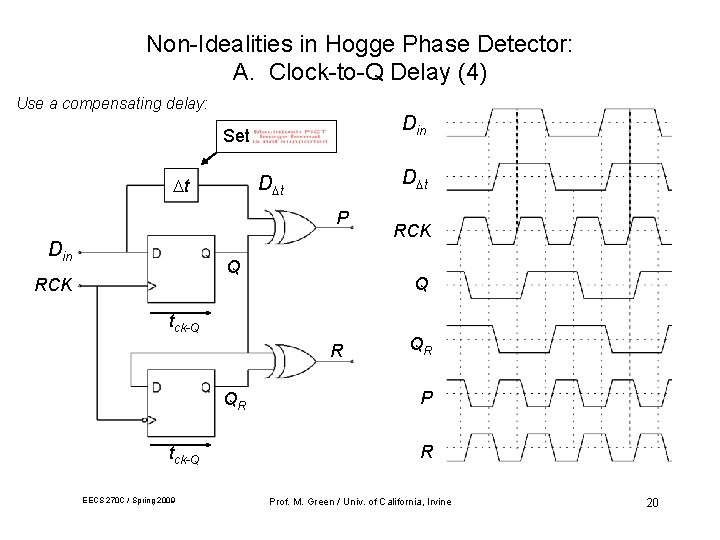

Non-Idealities in Hogge Phase Detector: A. Clock-to-Q Delay (4) Use a compensating delay: Din Set D t t P Din Q RCK Q tck-Q R QR tck-Q EECS 270 C / Spring 2009 RCK QR P R Prof. M. Green / Univ. of California, Irvine 20

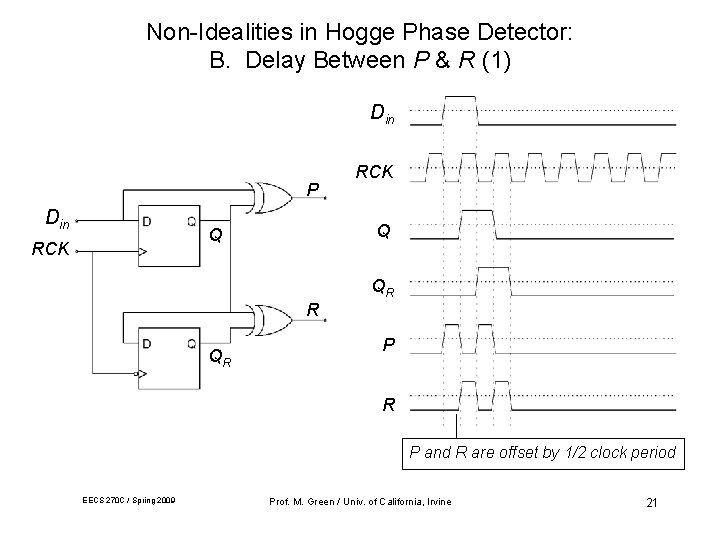

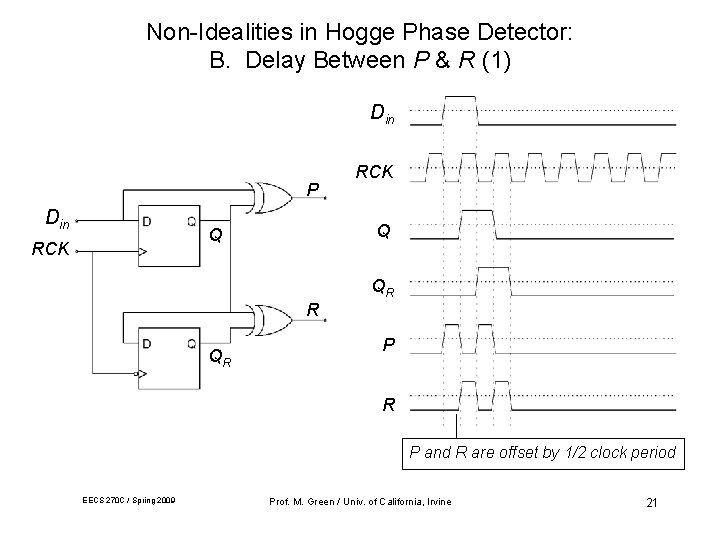

Non-Idealities in Hogge Phase Detector: B. Delay Between P & R (1) Din P Din Q Q RCK QR R QR P and R are offset by 1/2 clock period EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 21

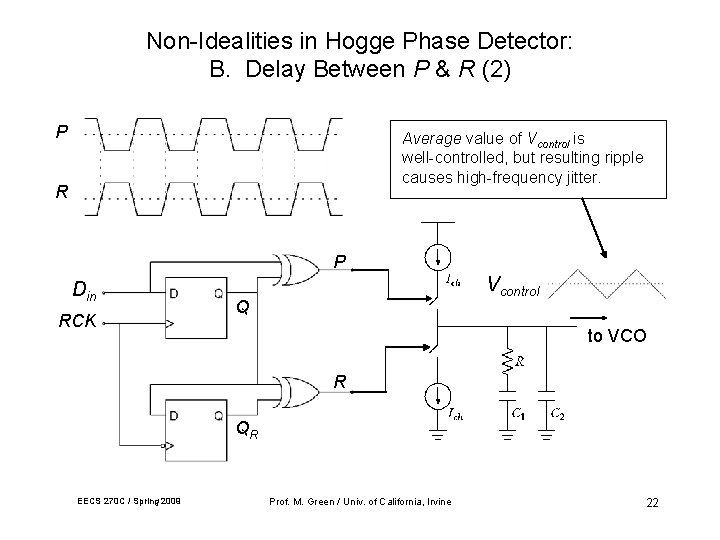

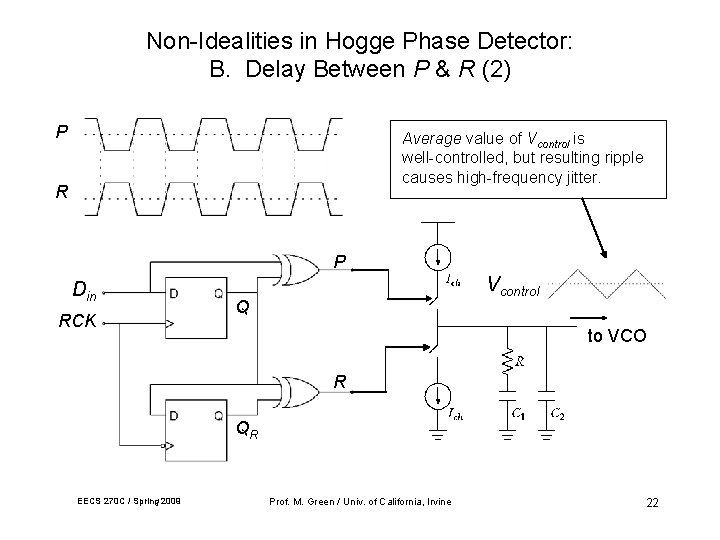

Non-Idealities in Hogge Phase Detector: B. Delay Between P & R (2) P Average value of Vcontrol is well-controlled, but resulting ripple causes high-frequency jitter. R P Din RCK Vcontrol Q to VCO R QR EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 22

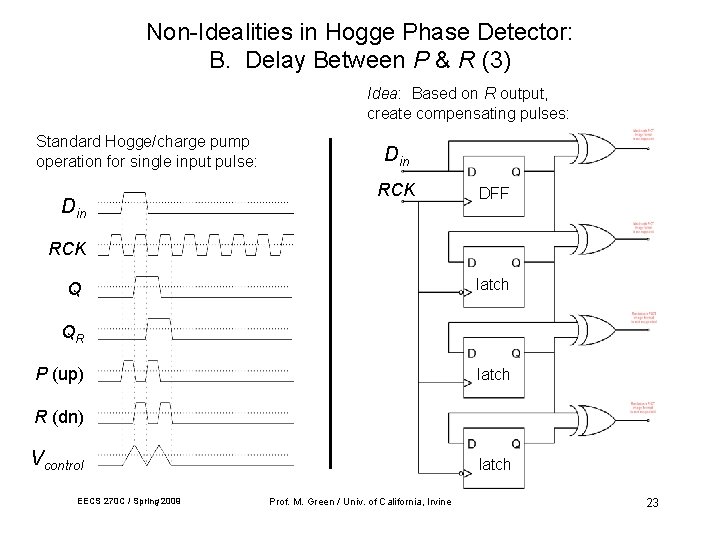

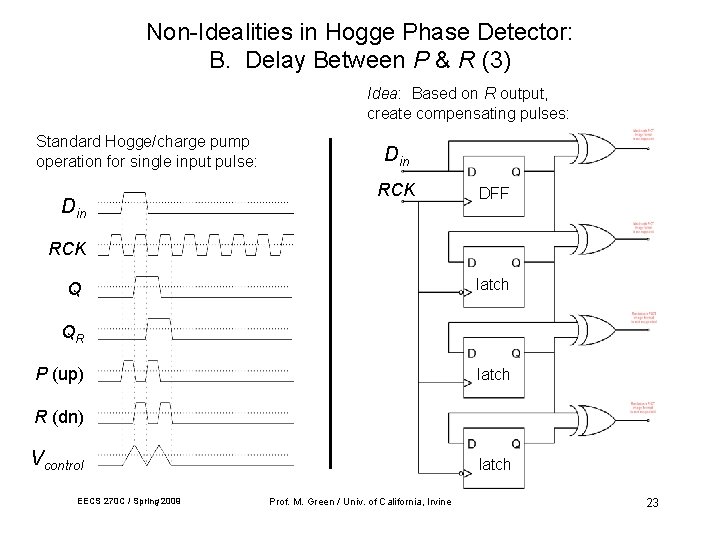

Non-Idealities in Hogge Phase Detector: B. Delay Between P & R (3) Idea: Based on R output, create compensating pulses: Standard Hogge/charge pump operation for single input pulse: Din RCK DFF RCK latch Q QR P (up) latch R (dn) Vcontrol EECS 270 C / Spring 2009 latch Prof. M. Green / Univ. of California, Irvine 23

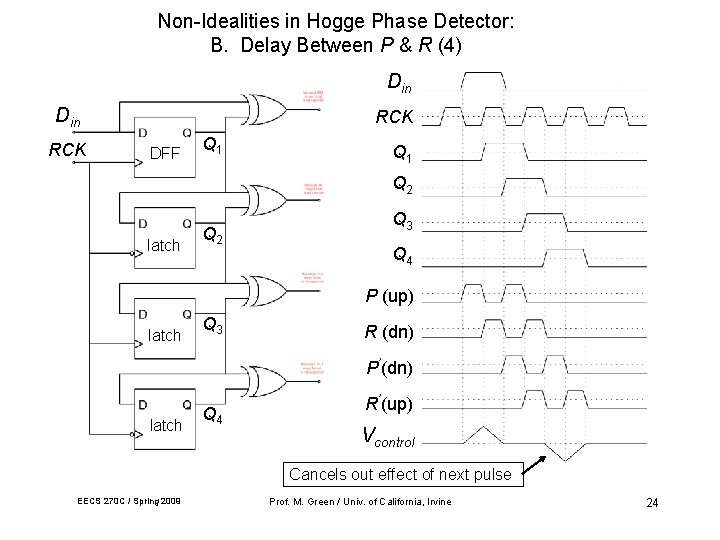

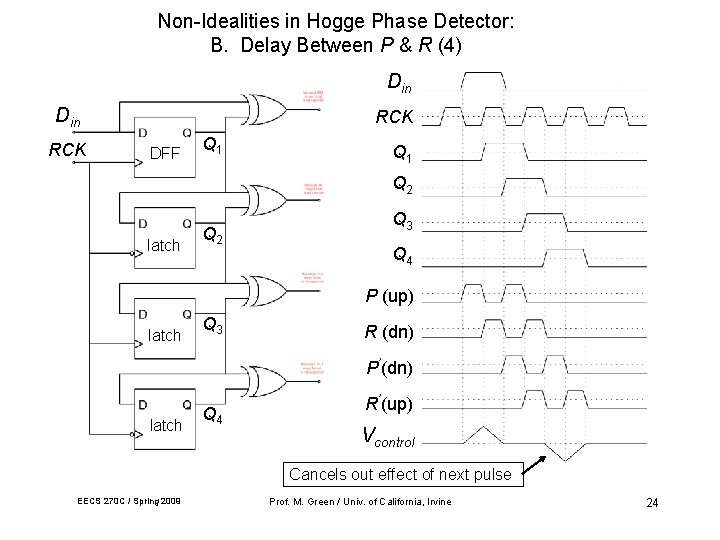

Non-Idealities in Hogge Phase Detector: B. Delay Between P & R (4) Din RCK DFF Q 1 Q 2 latch Q 2 Q 3 Q 4 P (up) latch Q 3 R (dn) P’(dn) latch Q 4 R’(up) Vcontrol Cancels out effect of next pulse EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 24

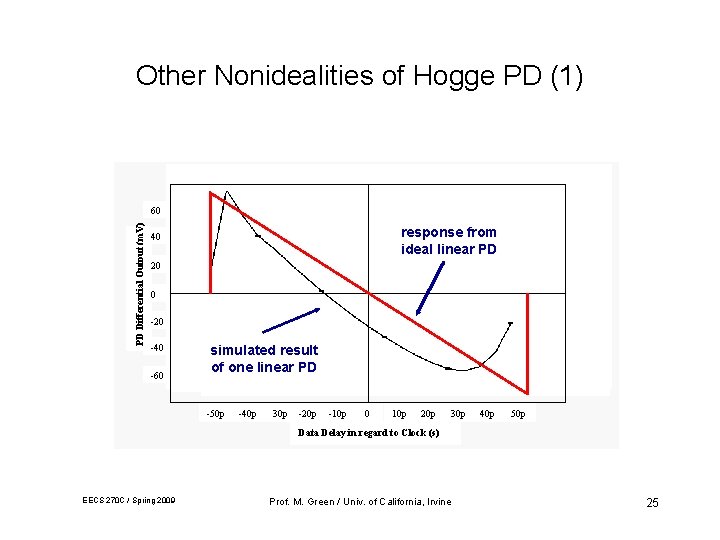

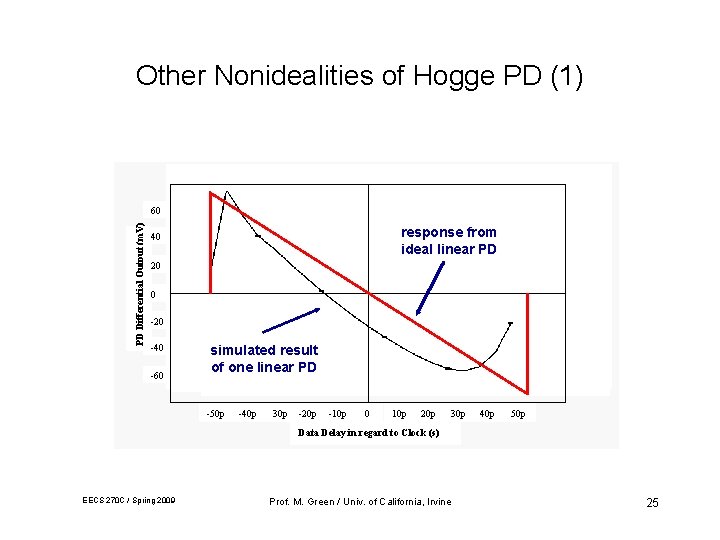

Other Nonidealities of Hogge PD (1) PD Differential Output (m. V) 60 response from ideal linear PD 40 20 0 -20 -40 -60 simulated result of one linear PD -50 p -40 p -30 p -20 p -10 p 0 10 p 20 p 30 p 40 p 50 p Data Delay in regard to Clock (s) EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 25

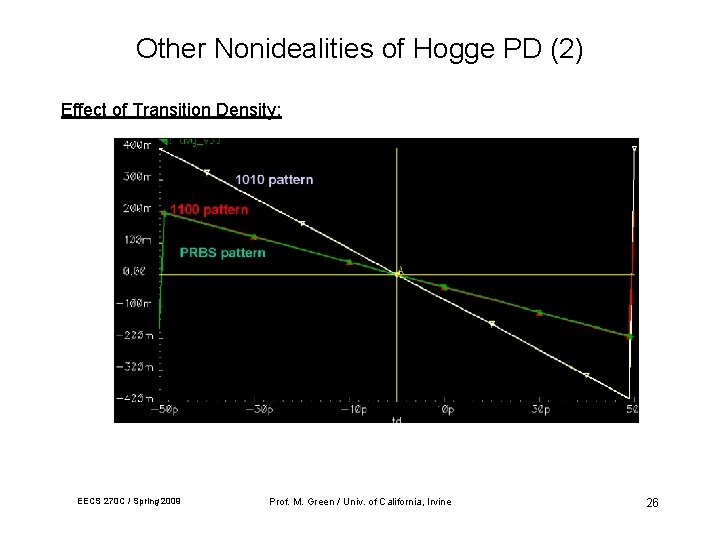

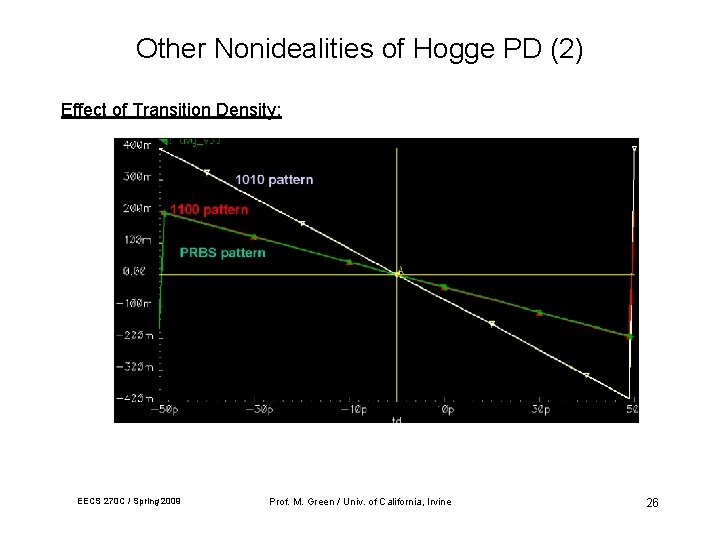

Other Nonidealities of Hogge PD (2) Effect of Transition Density: EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 26

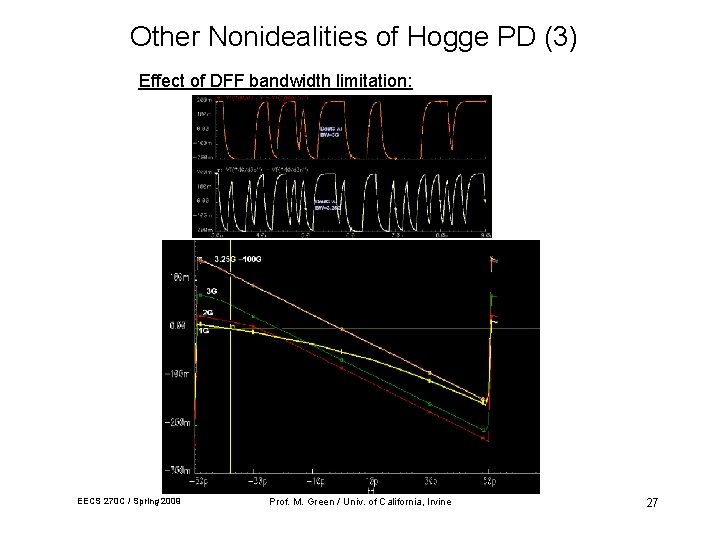

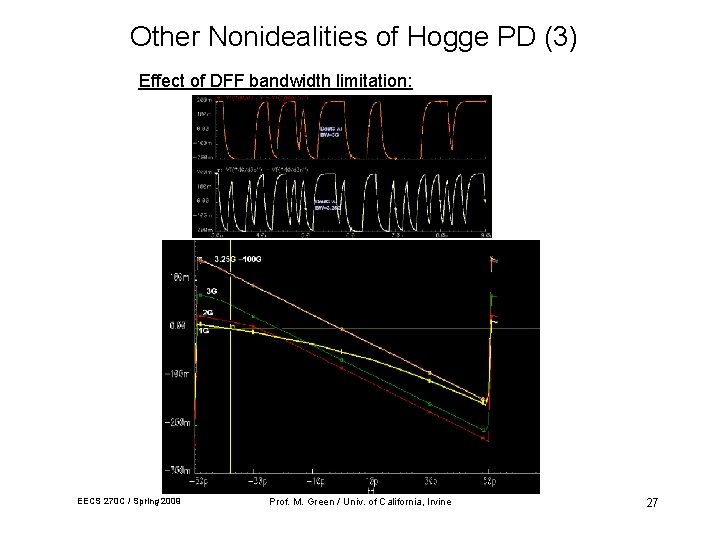

Other Nonidealities of Hogge PD (3) Effect of DFF bandwidth limitation: EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 27

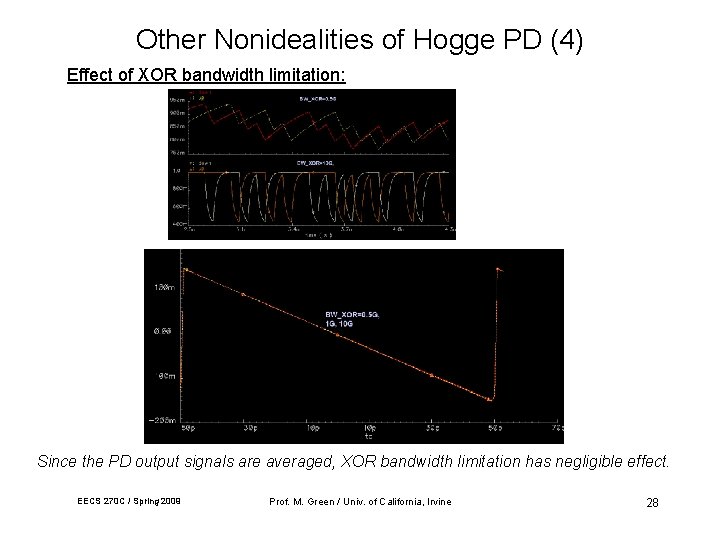

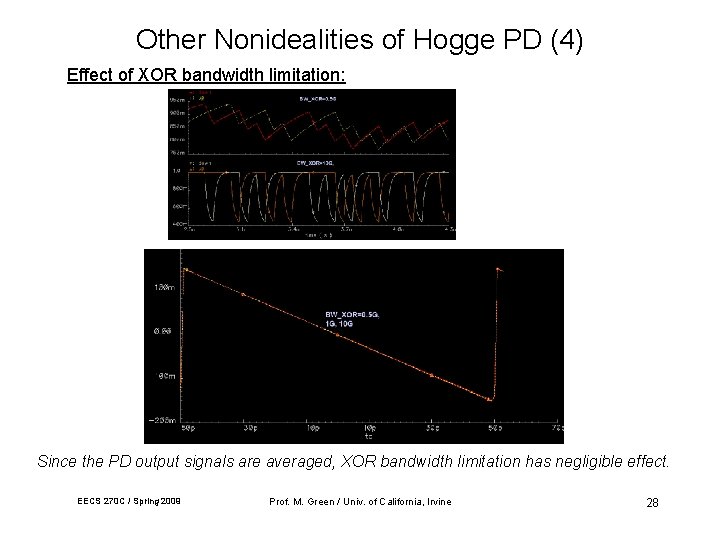

Other Nonidealities of Hogge PD (4) Effect of XOR bandwidth limitation: Since the PD output signals are averaged, XOR bandwidth limitation has negligible effect. EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 28

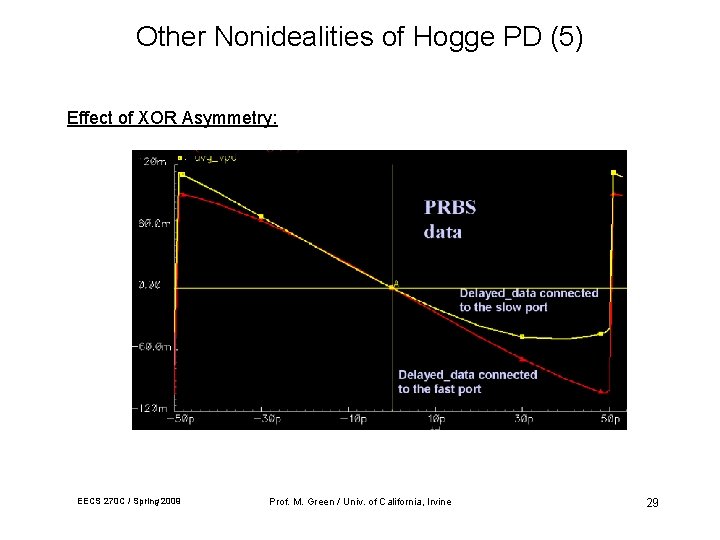

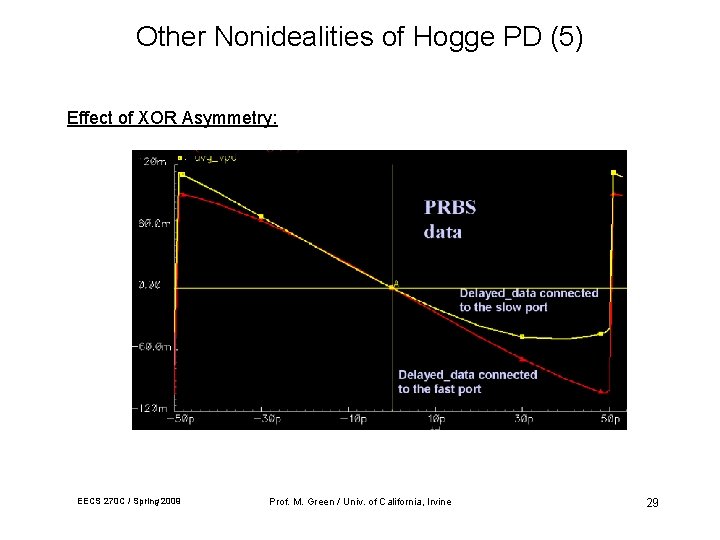

Other Nonidealities of Hogge PD (5) Effect of XOR Asymmetry: EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 29

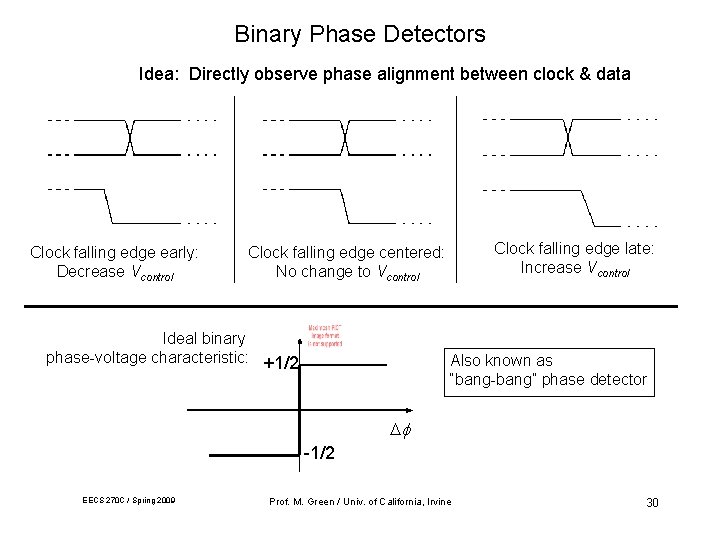

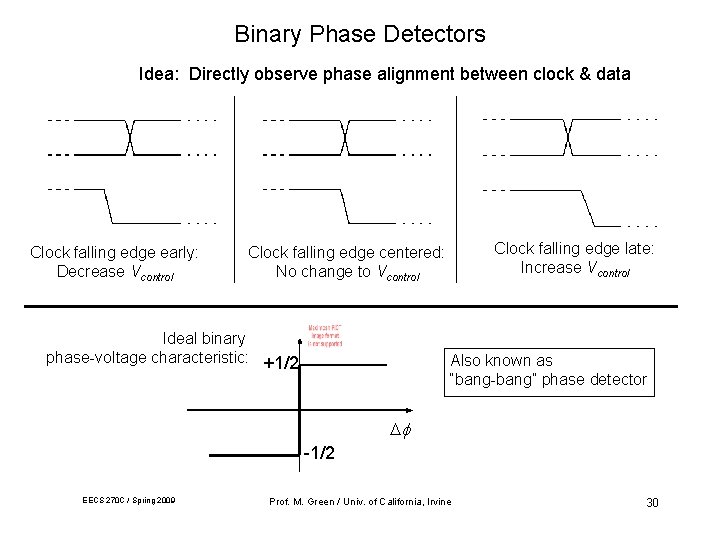

Binary Phase Detectors Idea: Directly observe phase alignment between clock & data Clock falling edge early: Decrease Vcontrol Clock falling edge late: Increase Vcontrol Clock falling edge centered: No change to Vcontrol Ideal binary phase-voltage characteristic: +1/2 Also known as “bang-bang” phase detector -1/2 EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 30

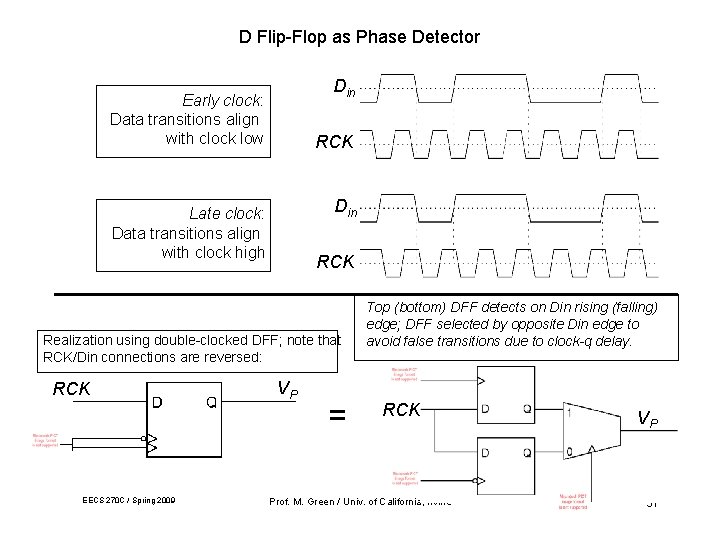

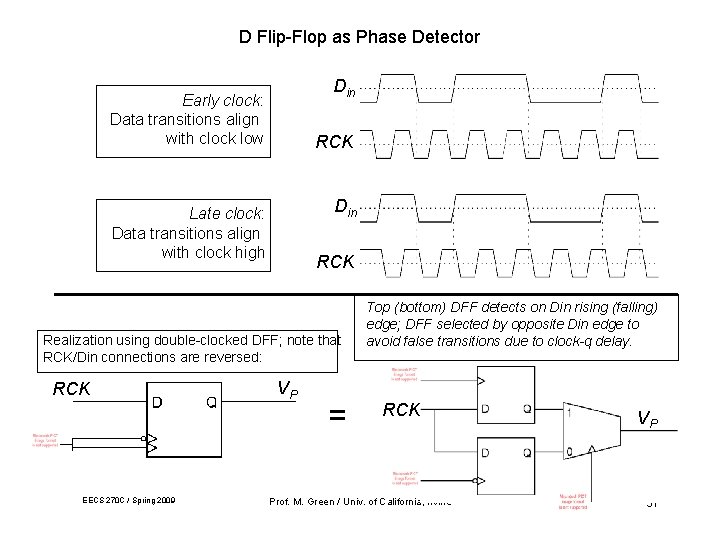

D Flip-Flop as Phase Detector Din Early clock: Data transitions align with clock low RCK Din Late clock: Data transitions align with clock high RCK Realization using double-clocked DFF; note that RCK/Din connections are reversed: RCK EECS 270 C / Spring 2009 VP = Top (bottom) DFF detects on Din rising (falling) edge; DFF selected by opposite Din edge to avoid false transitions due to clock-q delay. RCK Prof. M. Green / Univ. of California, Irvine VP 31

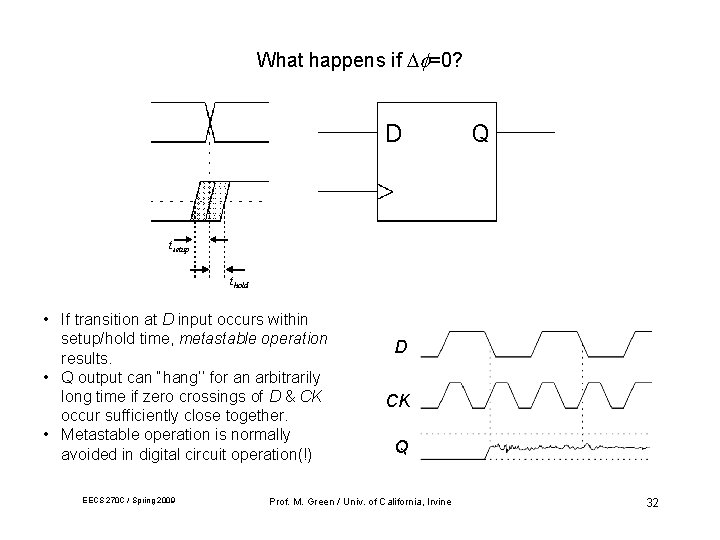

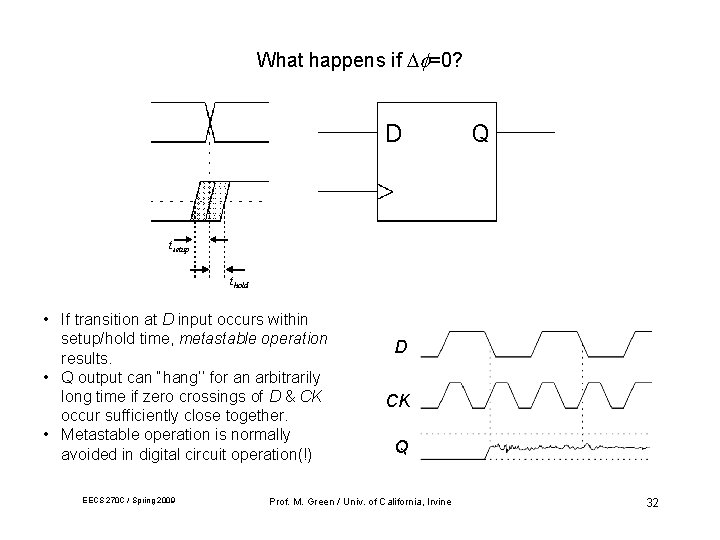

What happens if =0? tsetup thold • If transition at D input occurs within setup/hold time, metastable operation results. • Q output can “hang’’ for an arbitrarily long time if zero crossings of D & CK occur sufficiently close together. • Metastable operation is normally avoided in digital circuit operation(!) EECS 270 C / Spring 2009 D CK Q Prof. M. Green / Univ. of California, Irvine 32

Dog Dish Analogy ? ? ? A dog placed equidistant between two dog dishes will starve (in theory). EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 33

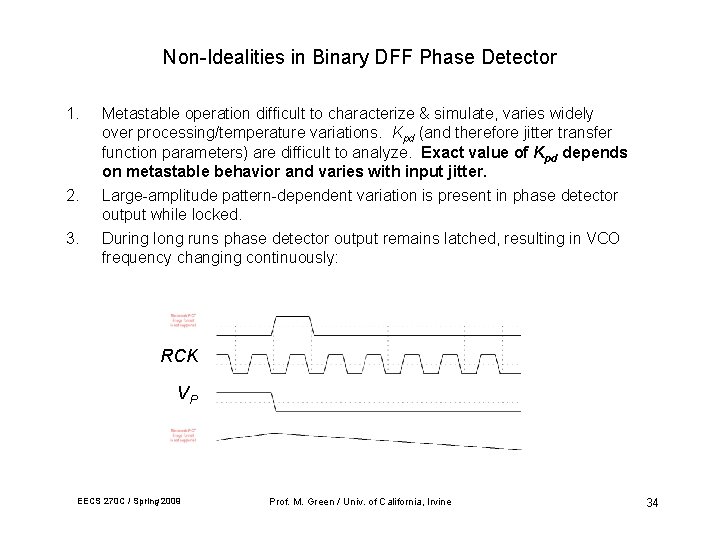

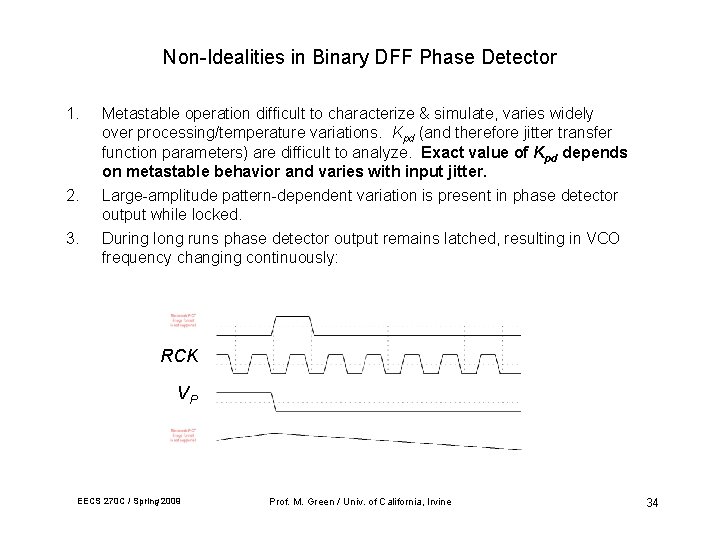

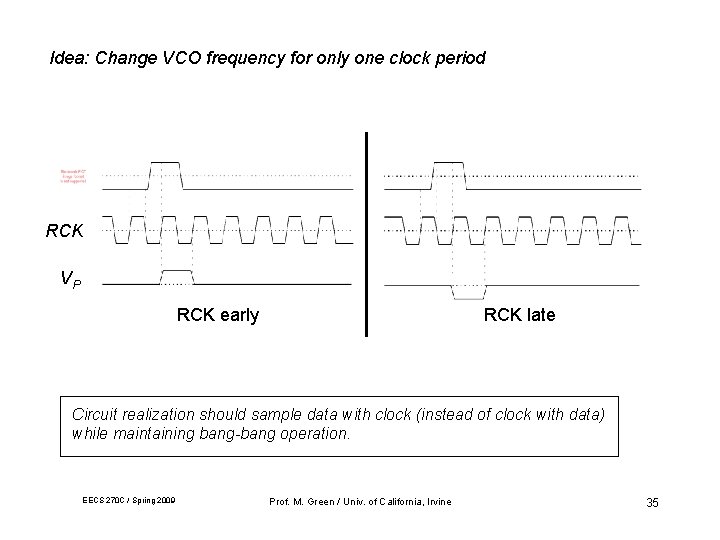

Non-Idealities in Binary DFF Phase Detector 1. Metastable operation difficult to characterize & simulate, varies widely over processing/temperature variations. Kpd (and therefore jitter transfer function parameters) are difficult to analyze. Exact value of Kpd depends on metastable behavior and varies with input jitter. 2. Large-amplitude pattern-dependent variation is present in phase detector output while locked. 3. During long runs phase detector output remains latched, resulting in VCO frequency changing continuously: RCK VP EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 34

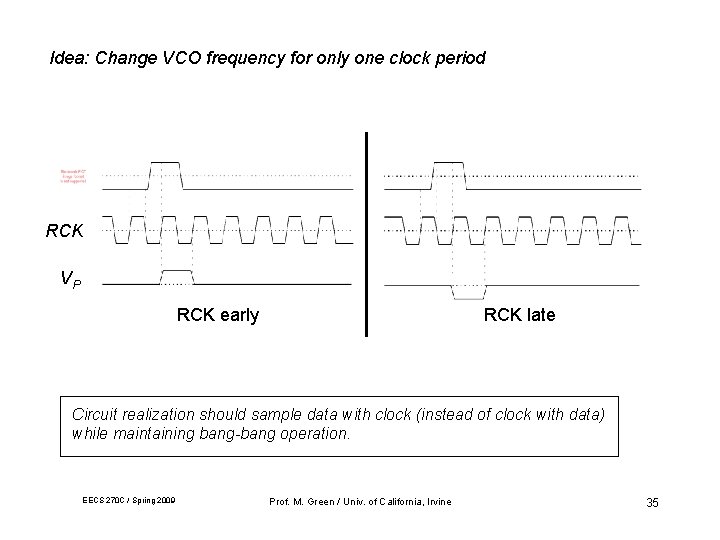

Idea: Change VCO frequency for only one clock period RCK VP RCK early RCK late Circuit realization should sample data with clock (instead of clock with data) while maintaining bang-bang operation. EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 35

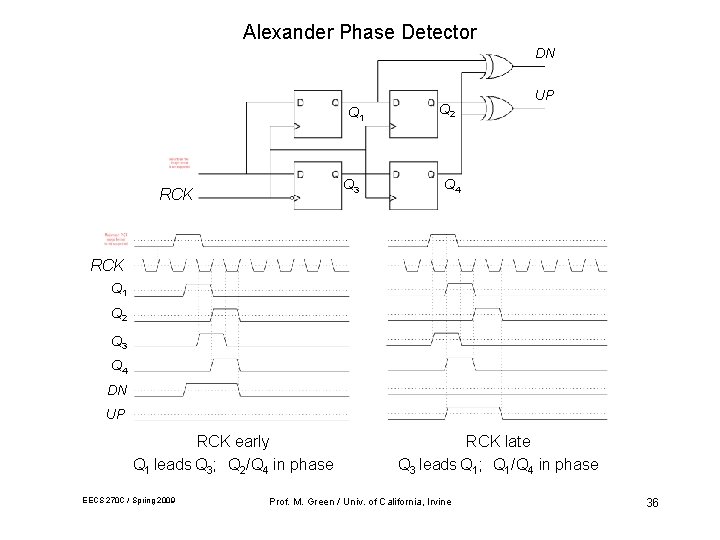

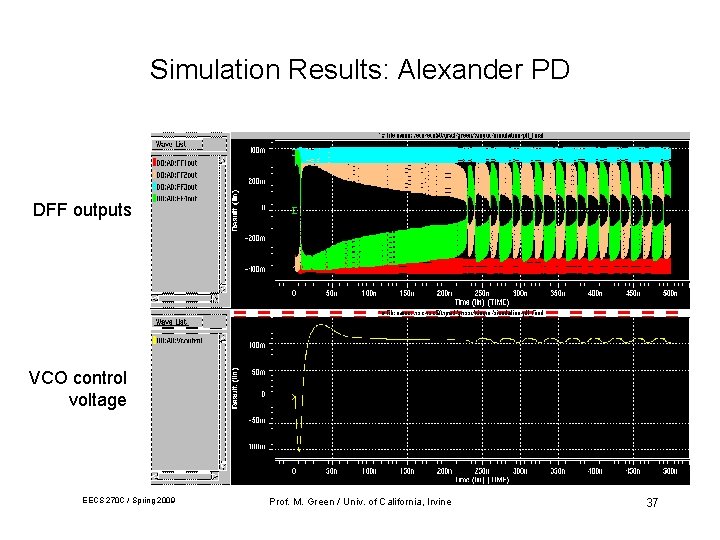

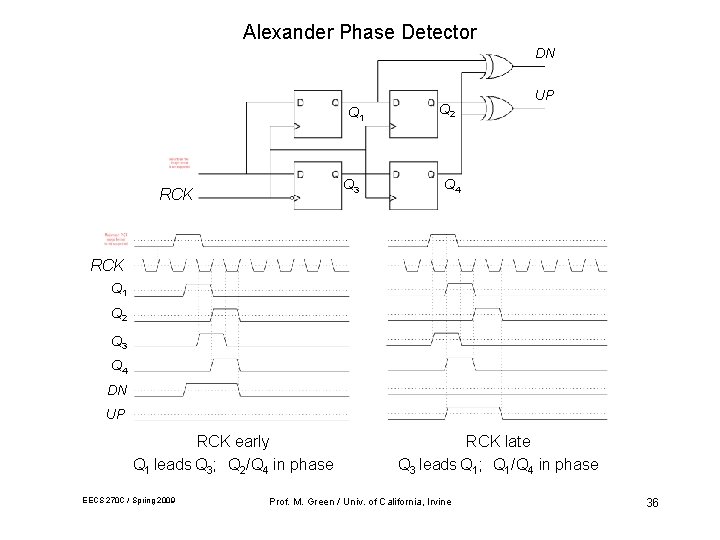

Alexander Phase Detector DN Q 1 Q 3 RCK Q 2 UP Q 4 RCK Q 1 Q 2 Q 3 Q 4 DN UP RCK early Q 1 leads Q 3; Q 2/Q 4 in phase EECS 270 C / Spring 2009 RCK late Q 3 leads Q 1; Q 1/Q 4 in phase Prof. M. Green / Univ. of California, Irvine 36

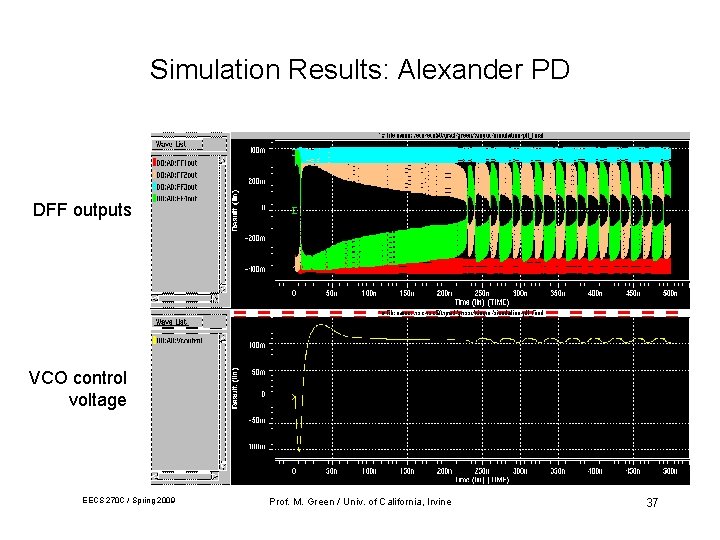

Simulation Results: Alexander PD DFF outputs VCO control voltage EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 37

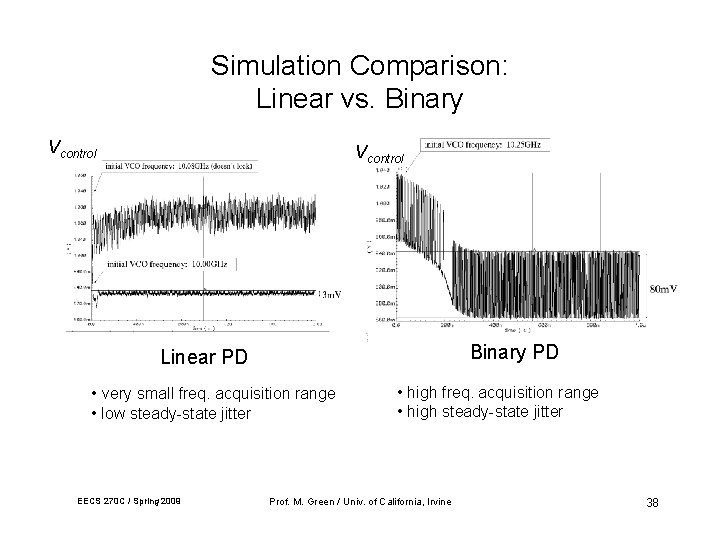

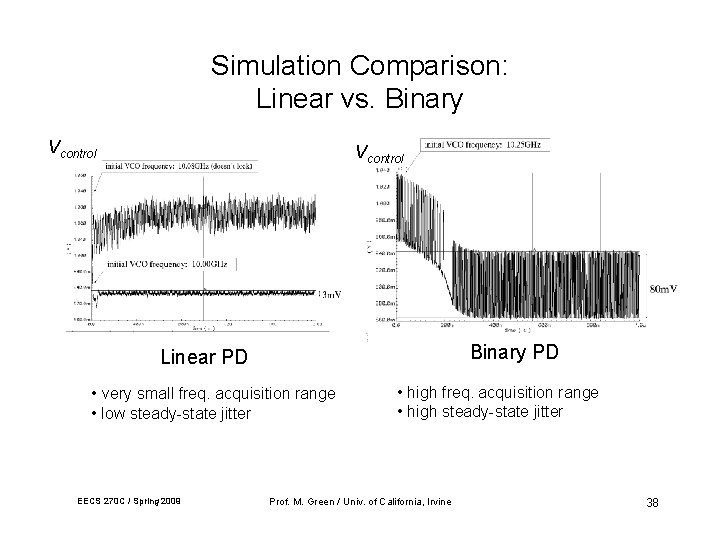

Simulation Comparison: Linear vs. Binary Vcontrol Binary PD Linear PD • very small freq. acquisition range • low steady-state jitter EECS 270 C / Spring 2009 • high freq. acquisition range • high steady-state jitter Prof. M. Green / Univ. of California, Irvine 38

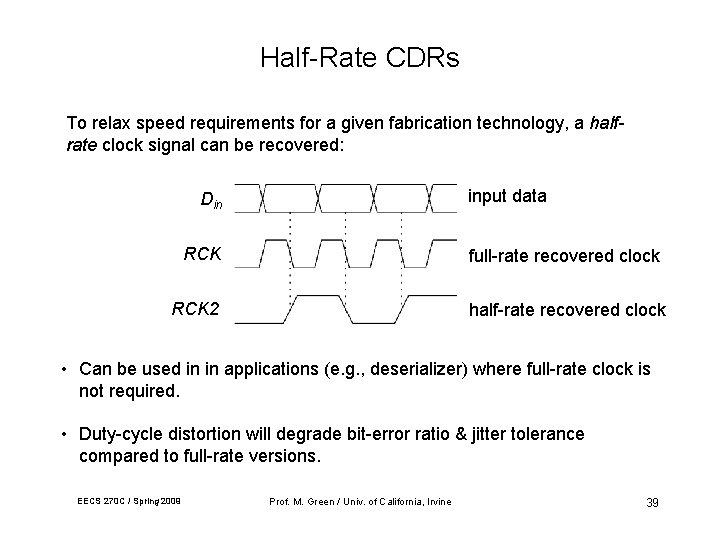

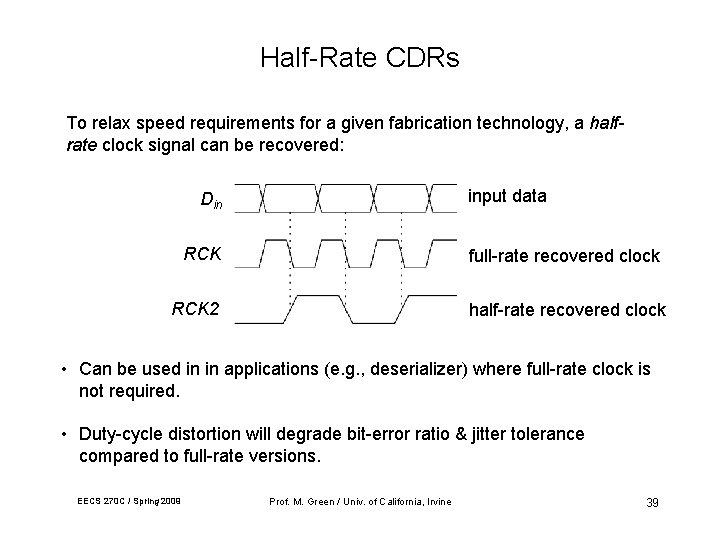

Half-Rate CDRs To relax speed requirements for a given fabrication technology, a halfrate clock signal can be recovered: input data Din RCK full-rate recovered clock RCK 2 half-rate recovered clock • Can be used in in applications (e. g. , deserializer) where full-rate clock is not required. • Duty-cycle distortion will degrade bit-error ratio & jitter tolerance compared to full-rate versions. EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 39

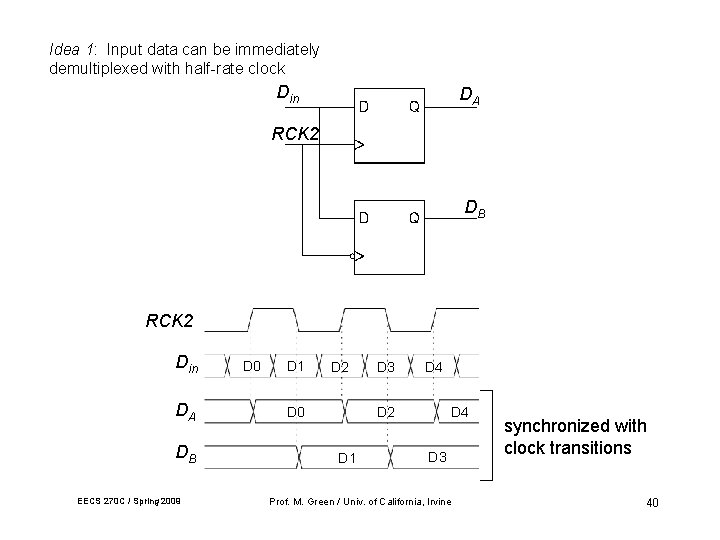

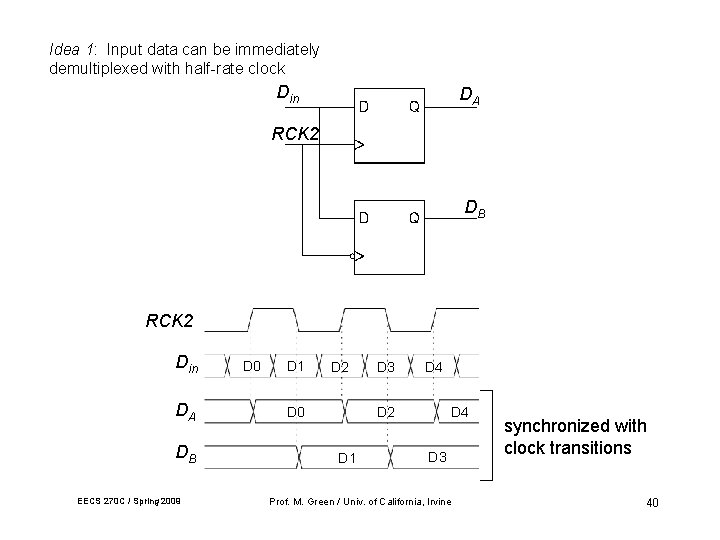

Idea 1: Input data can be immediately demultiplexed with half-rate clock Din DA RCK 2 DB RCK 2 Din DA DB EECS 270 C / Spring 2009 D 0 D 1 D 2 D 3 D 4 D 2 D 0 D 1 D 4 D 3 Prof. M. Green / Univ. of California, Irvine synchronized with clock transitions 40

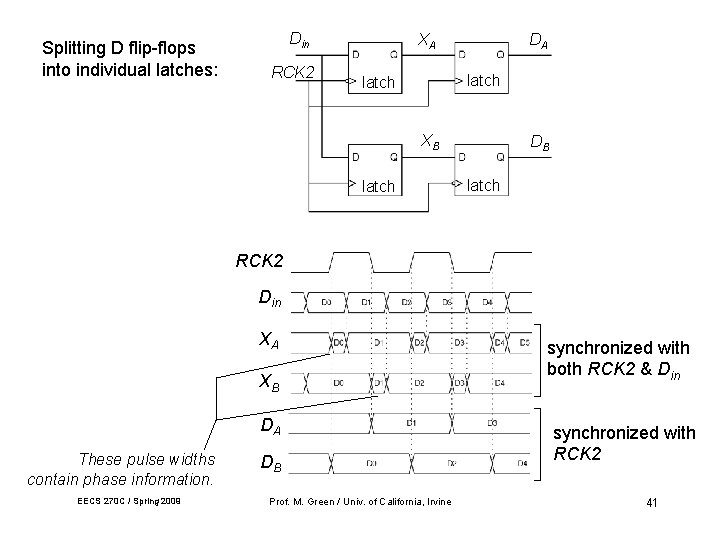

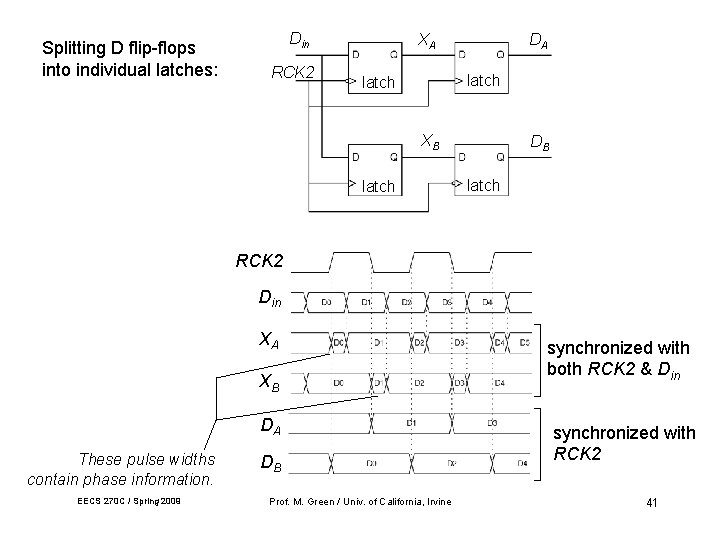

Splitting D flip-flops into individual latches: Din RCK 2 XA DA latch XB latch DB latch RCK 2 Din XA XB DA These pulse widths contain phase information. EECS 270 C / Spring 2009 DB Prof. M. Green / Univ. of California, Irvine synchronized with both RCK 2 & Din synchronized with RCK 2 41

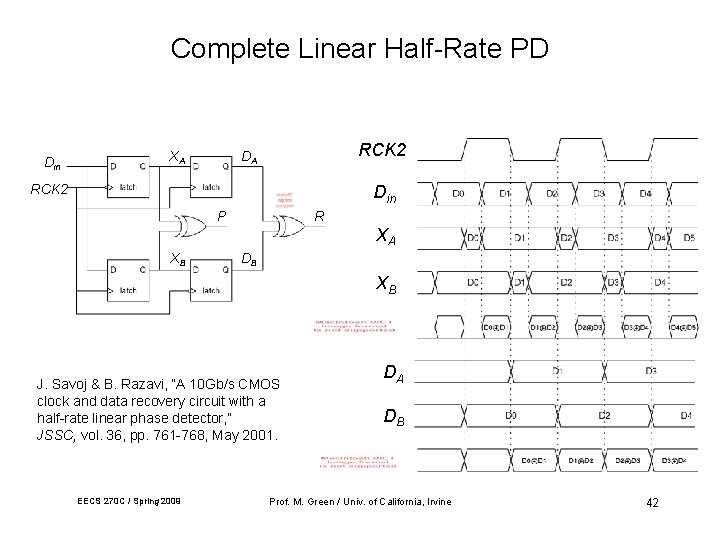

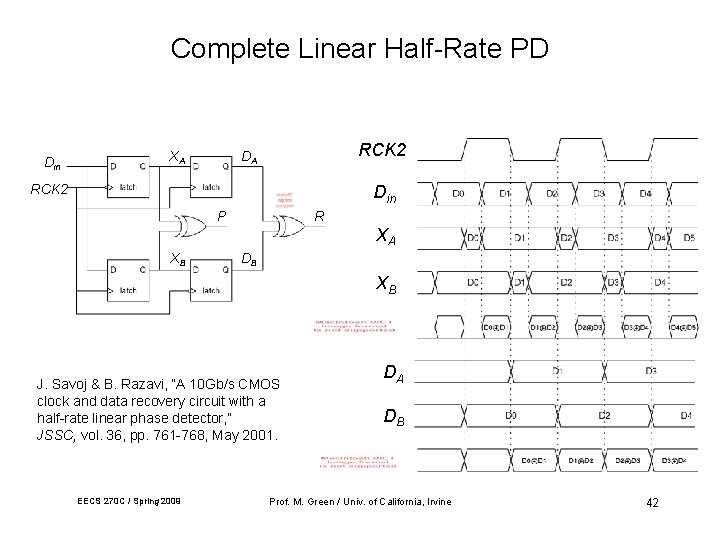

Complete Linear Half-Rate PD Din XA RCK 2 Din P R XA XB DB XB J. Savoj & B. Razavi, “A 10 Gb/s CMOS clock and data recovery circuit with a half-rate linear phase detector, ” JSSC, vol. 36, pp. 761 -768, May 2001. EECS 270 C / Spring 2009 DA DB Prof. M. Green / Univ. of California, Irvine 42

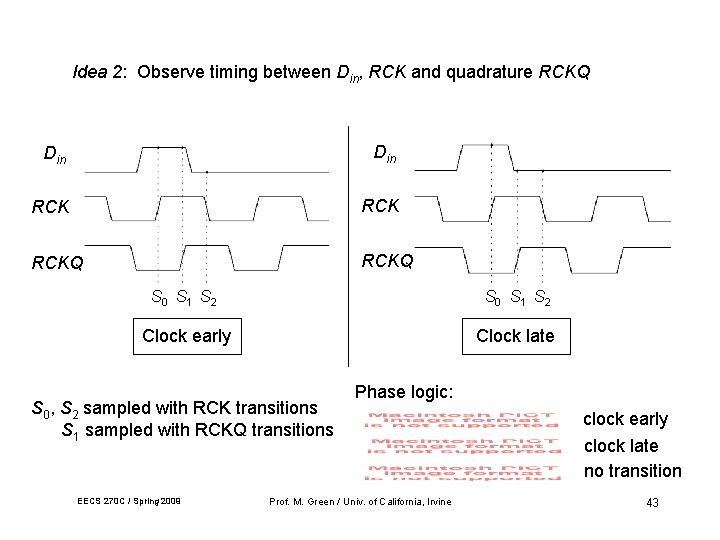

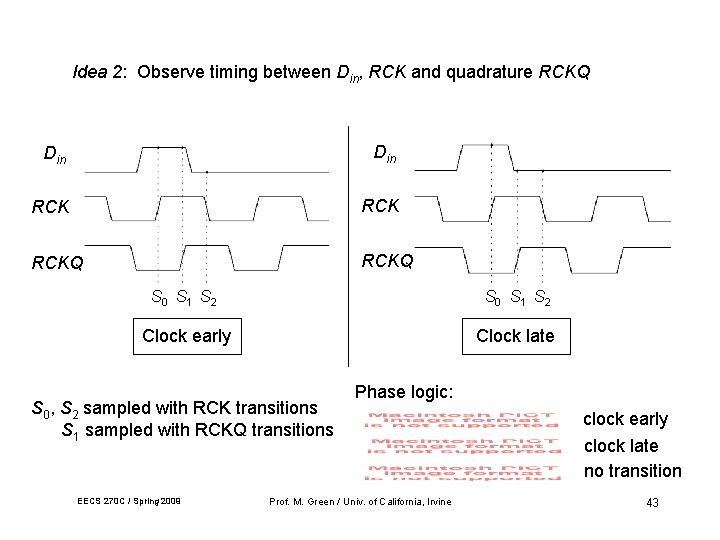

Idea 2: Observe timing between Din, RCK and quadrature RCKQ Din RCK RCKQ S 0 S 1 S 2 Clock early Clock late S 0, S 2 sampled with RCK transitions S 1 sampled with RCKQ transitions EECS 270 C / Spring 2009 Phase logic: Prof. M. Green / Univ. of California, Irvine clock early clock late no transition 43

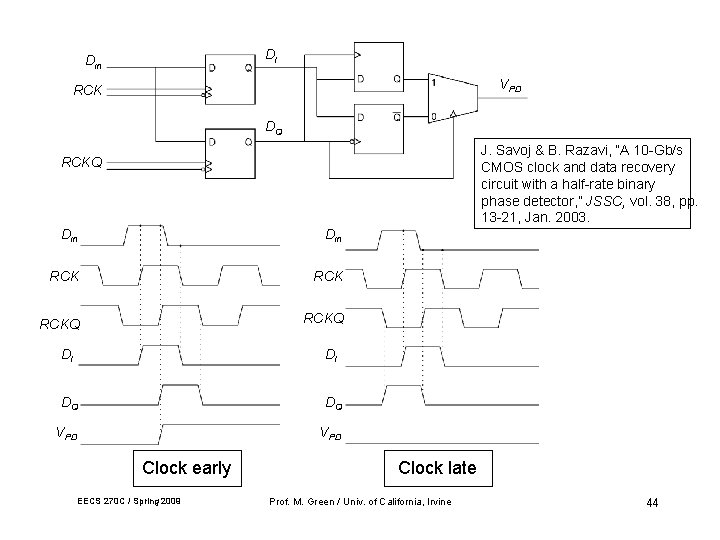

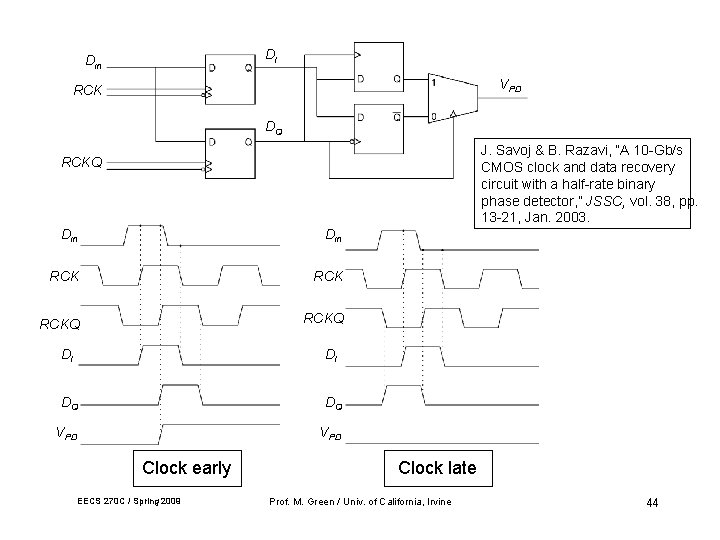

DI Din VPD RCK DQ J. Savoj & B. Razavi, “A 10 -Gb/s CMOS clock and data recovery circuit with a half-rate binary phase detector, ” JSSC, vol. 38, pp. 13 -21, Jan. 2003. RCKQ Din RCK RCKQ DI DI DQ DQ VPD Clock early EECS 270 C / Spring 2009 Clock late Prof. M. Green / Univ. of California, Irvine 44

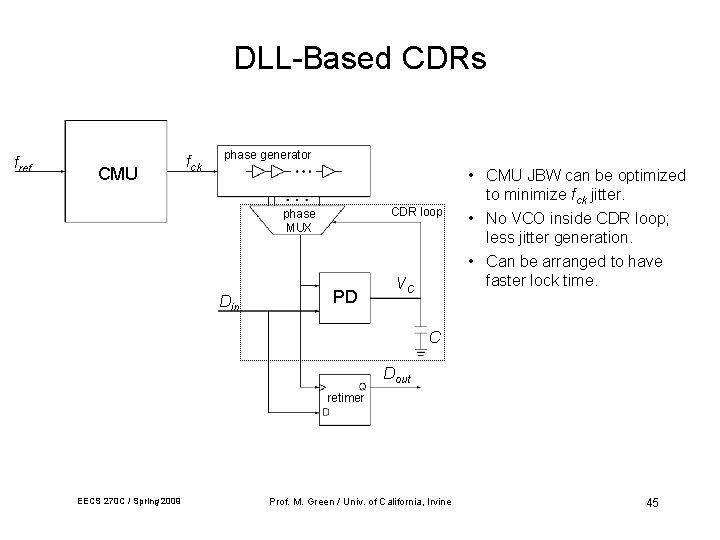

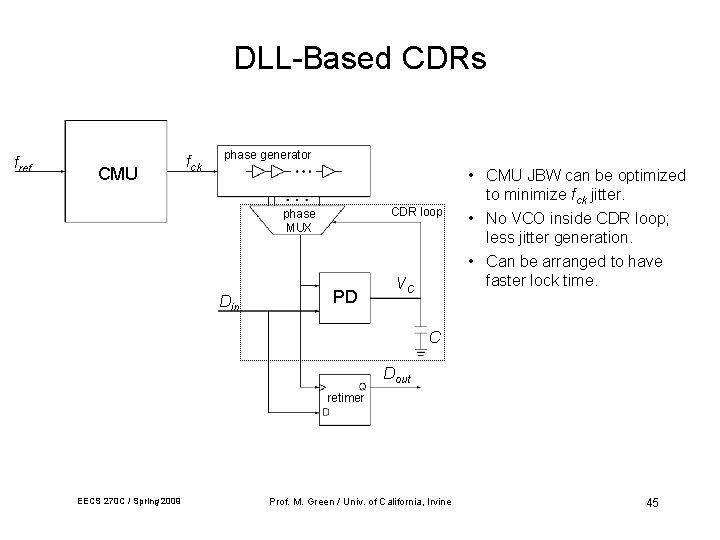

DLL-Based CDRs fref CMU fck phase generator CDR loop phase MUX Din PD VC • CMU JBW can be optimized to minimize fck jitter. • No VCO inside CDR loop; less jitter generation. • Can be arranged to have faster lock time. C Dout retimer EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine 45

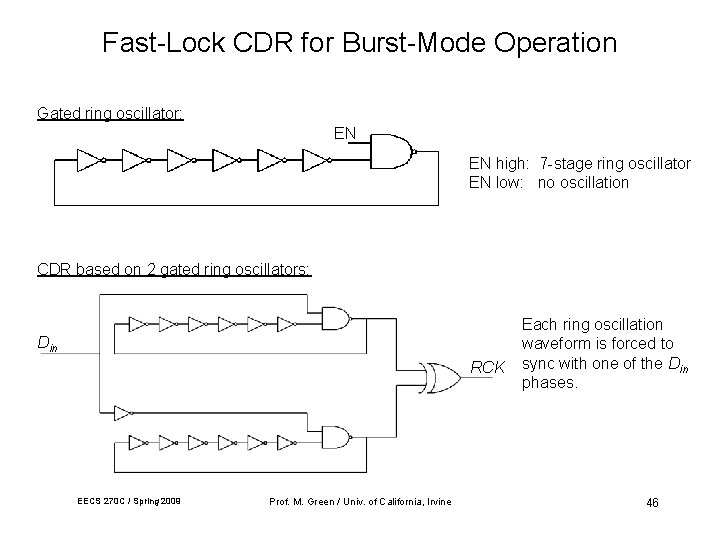

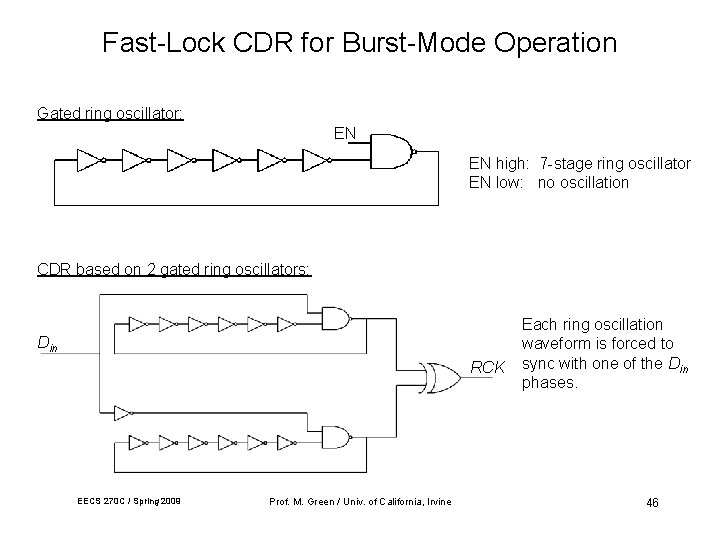

Fast-Lock CDR for Burst-Mode Operation Gated ring oscillator: EN EN high: 7 -stage ring oscillator EN low: no oscillation CDR based on 2 gated ring oscillators: Din RCK EECS 270 C / Spring 2009 Prof. M. Green / Univ. of California, Irvine Each ring oscillation waveform is forced to sync with one of the Din phases. 46