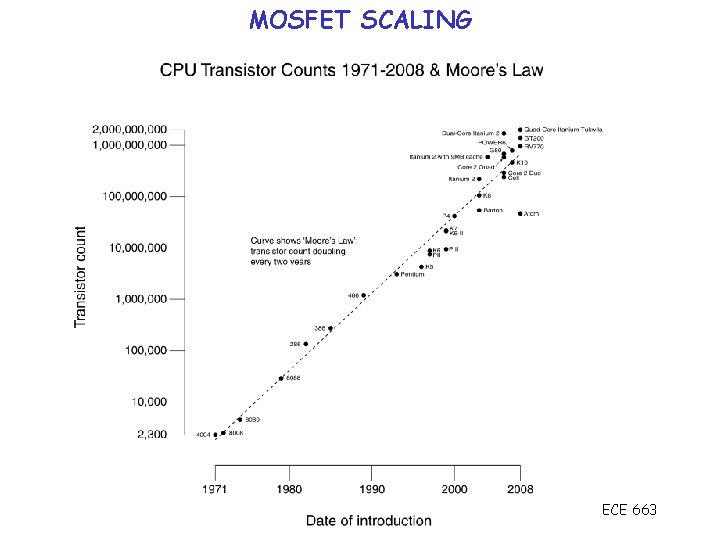

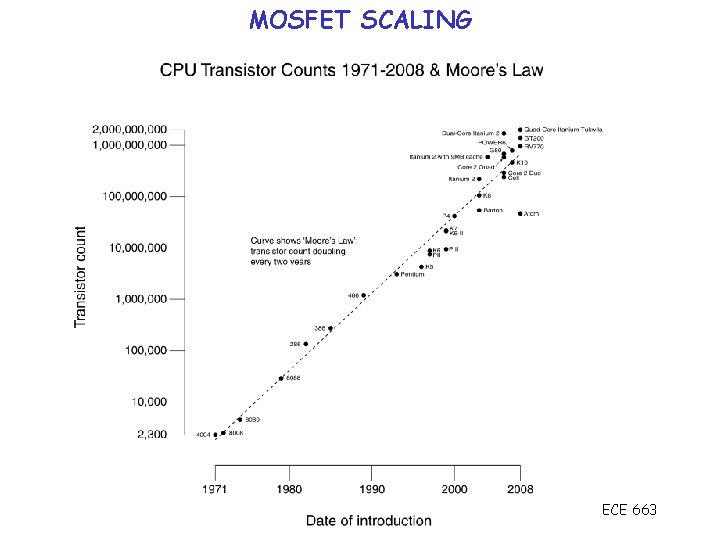

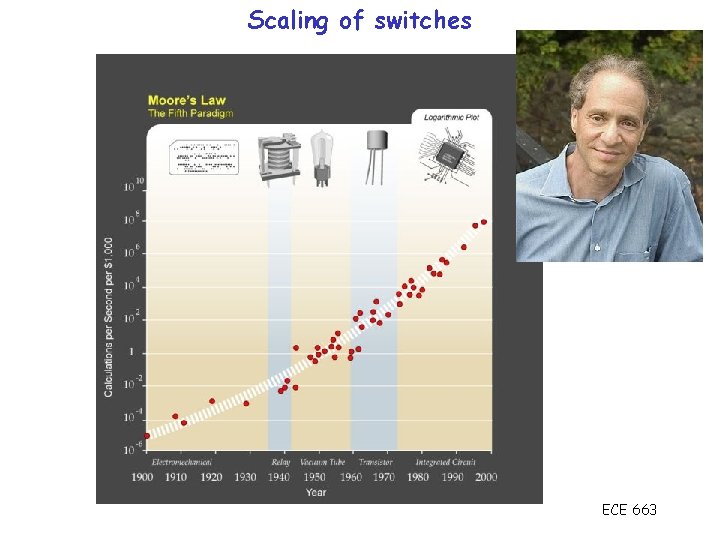

MOSFET SCALING ECE 663 Scaling of switches ECE

- Slides: 48

MOSFET SCALING ECE 663

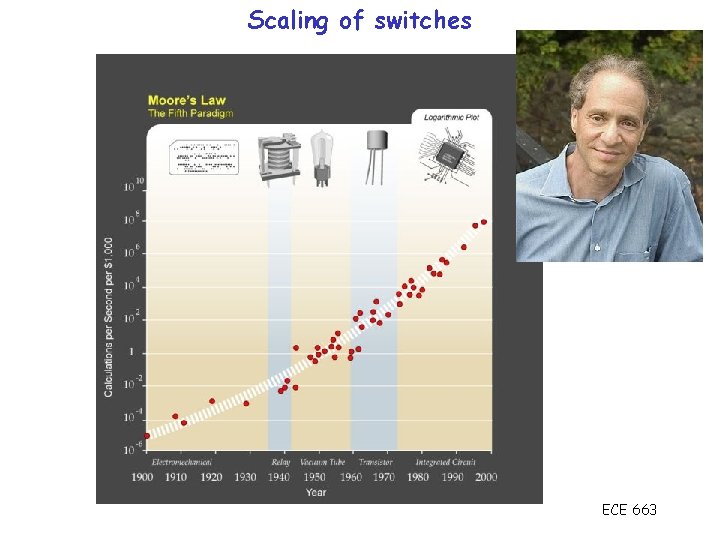

Scaling of switches ECE 663

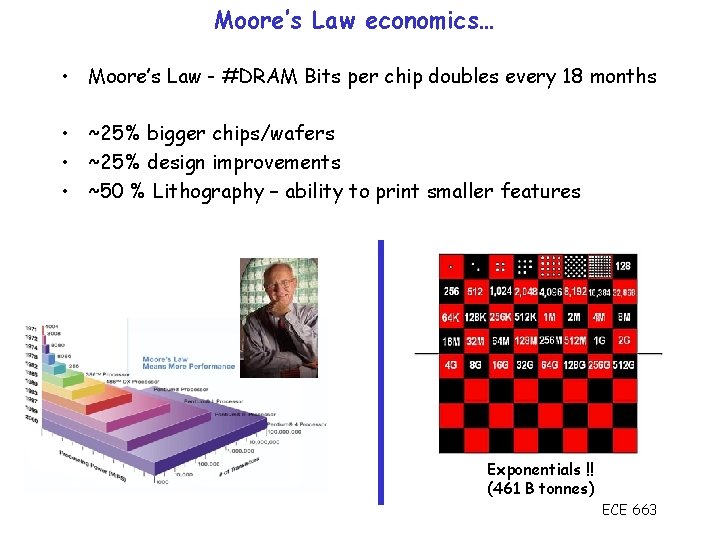

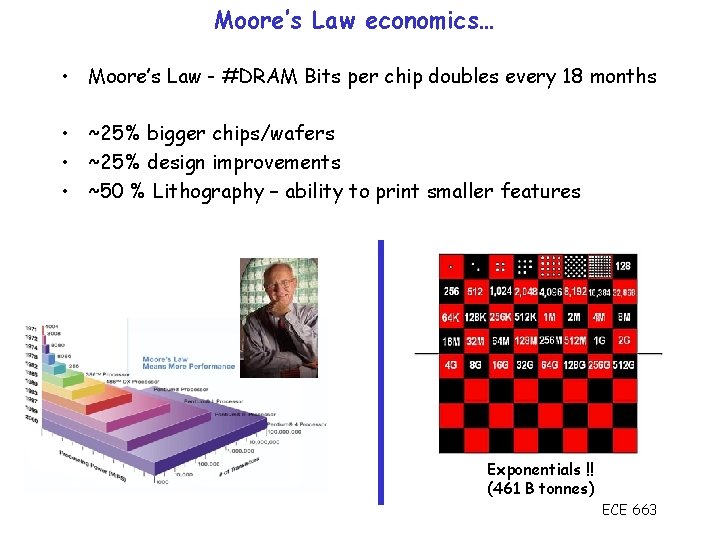

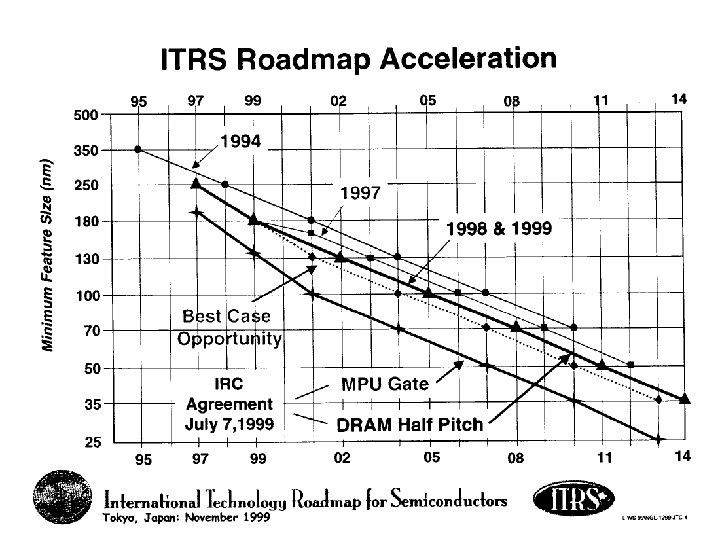

Moore’s Law economics… • Moore’s Law - #DRAM Bits per chip doubles every 18 months • ~25% bigger chips/wafers • ~25% design improvements • ~50 % Lithography – ability to print smaller features Exponentials !! (461 B tonnes) ECE 663

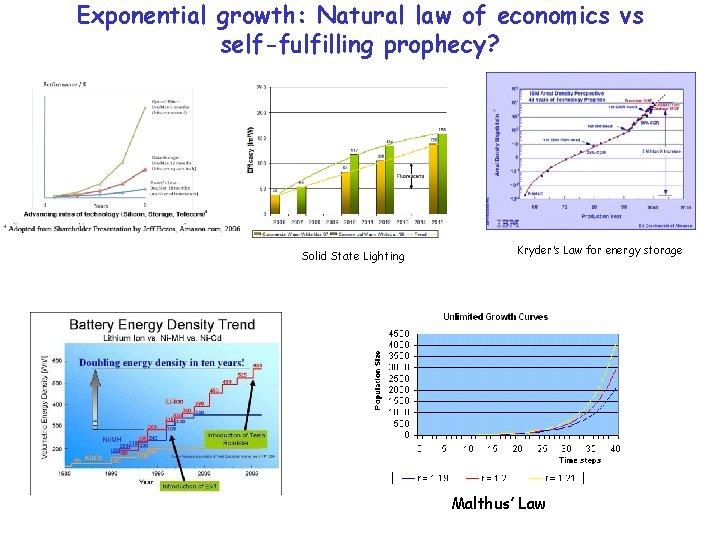

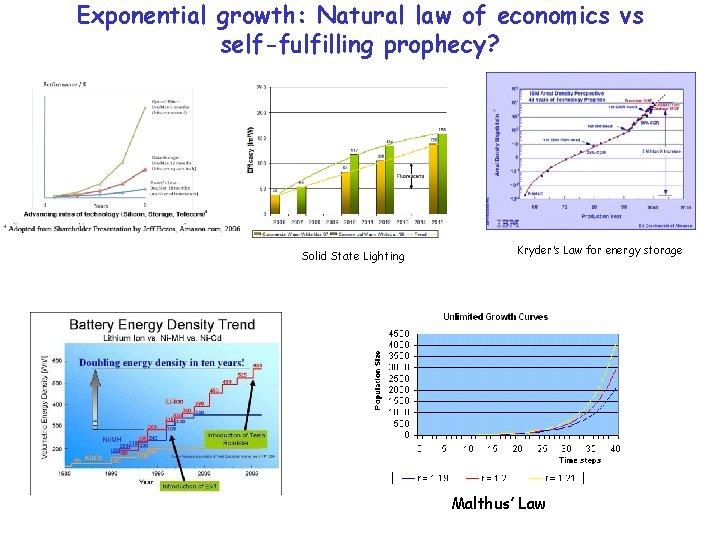

Exponential growth: Natural law of economics vs self-fulfilling prophecy? Solid State Lighting Kryder’s Law for energy storage Malthus’ Law

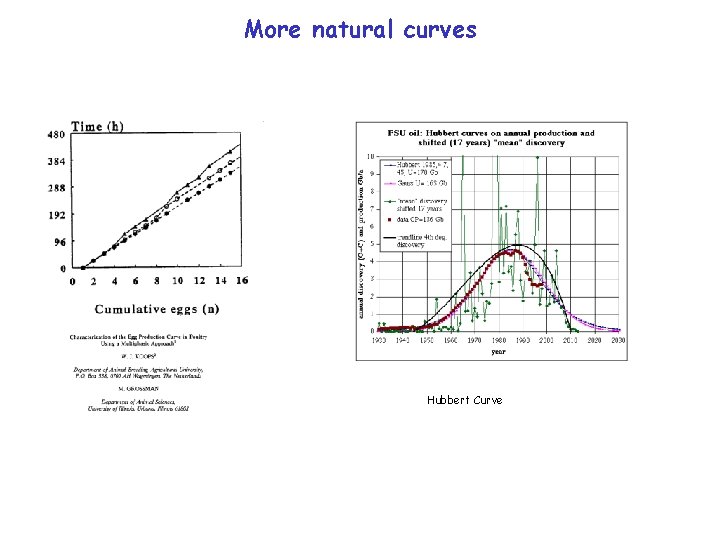

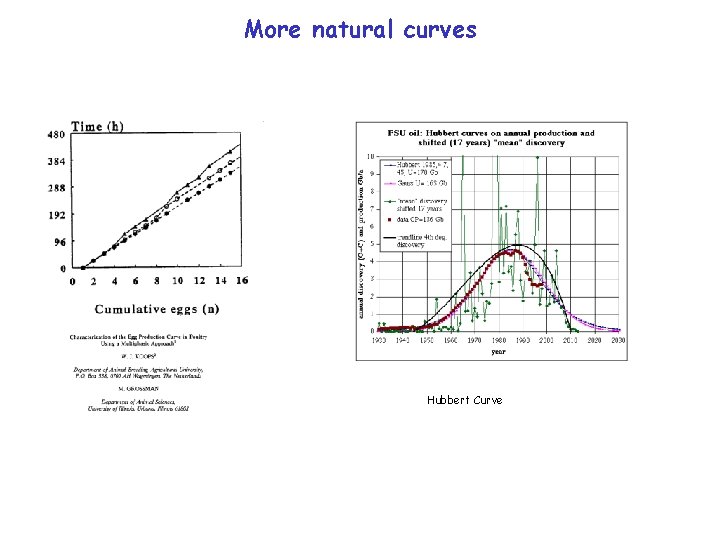

More natural curves Hubbert Curve

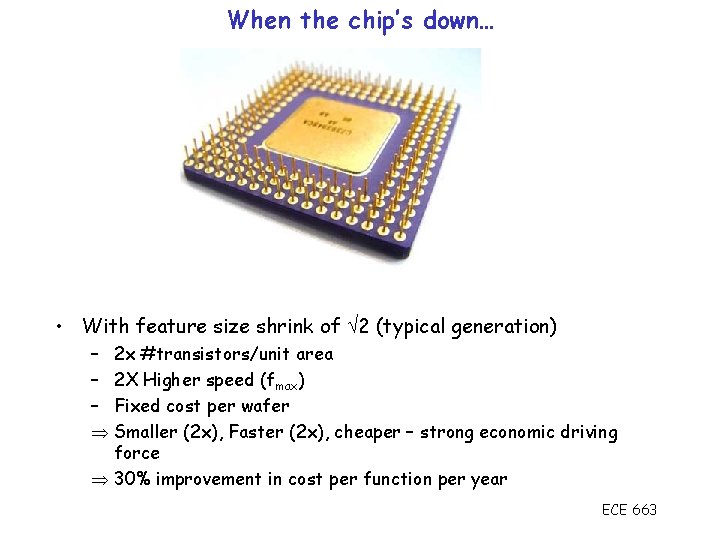

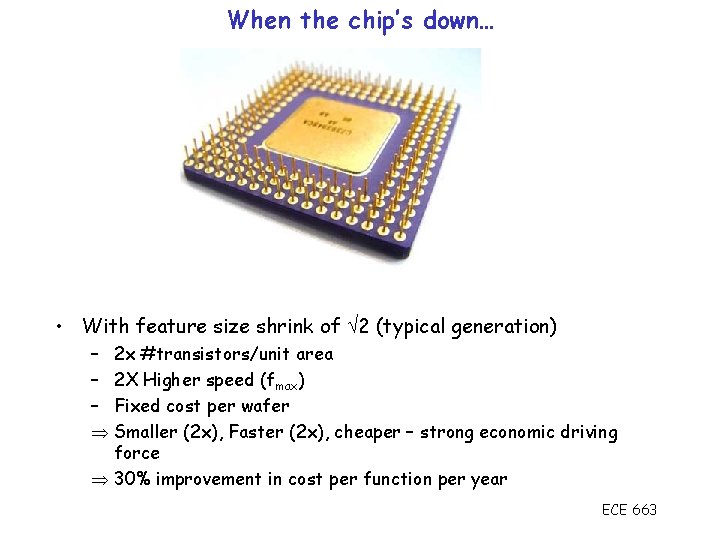

When the chip’s down… • With feature size shrink of 2 (typical generation) – 2 x #transistors/unit area – 2 X Higher speed (fmax) – Fixed cost per wafer Þ Smaller (2 x), Faster (2 x), cheaper – strong economic driving force Þ 30% improvement in cost per function per year ECE 663

ECE 663

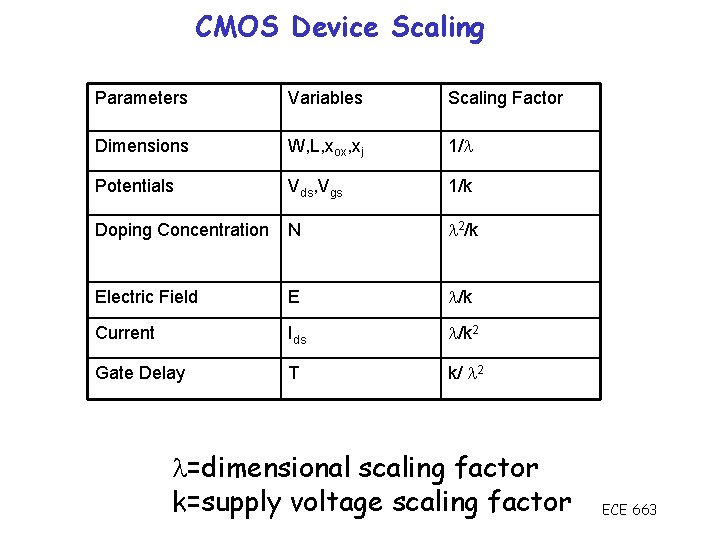

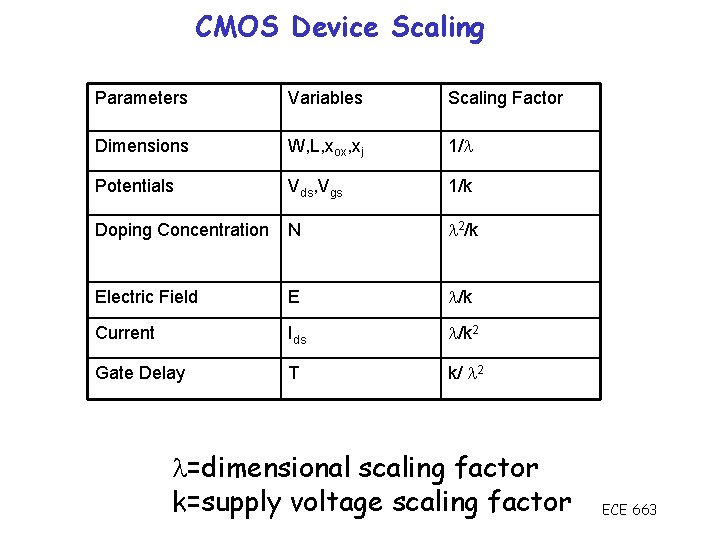

CMOS Device Scaling Parameters Variables Scaling Factor Dimensions W, L, xox, xj 1/ Potentials Vds, Vgs 1/k Doping Concentration N 2/k Electric Field E /k Current Ids /k 2 Gate Delay T k/ 2 =dimensional scaling factor k=supply voltage scaling factor ECE 663

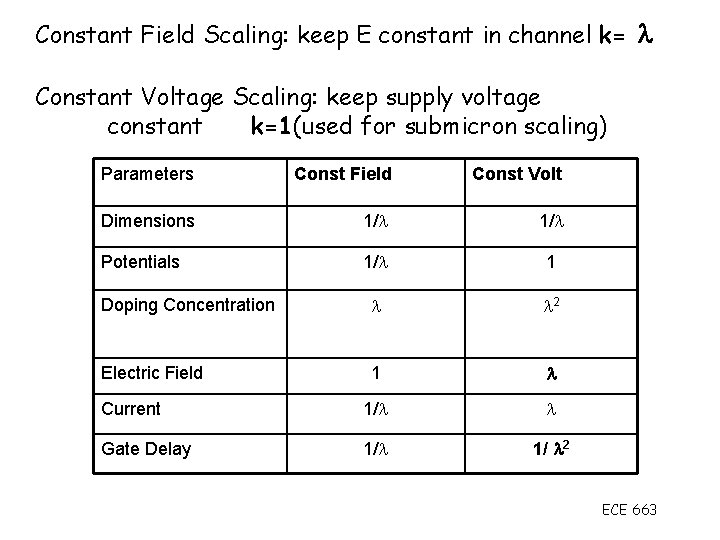

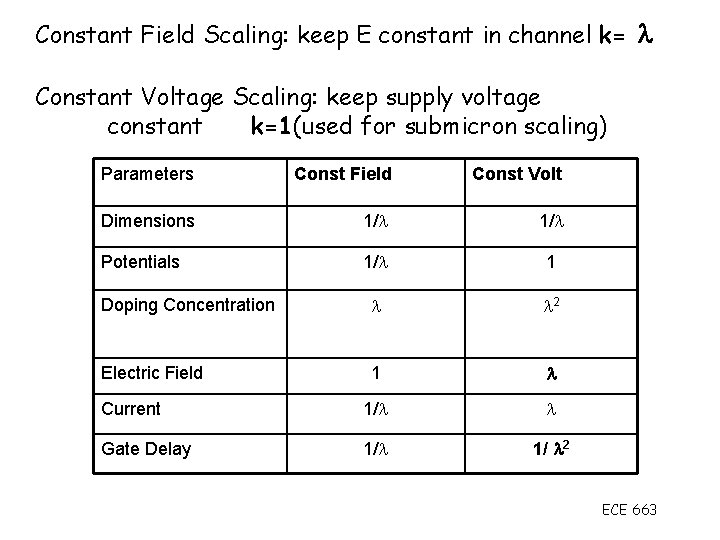

Constant Field Scaling: keep E constant in channel k= Constant Voltage Scaling: keep supply voltage constant k=1(used for submicron scaling) Parameters Const Field Const Volt Dimensions 1/ Potentials 1/ 1 Doping Concentration 2 Electric Field 1 Current 1/ Gate Delay 1/ 2 ECE 663

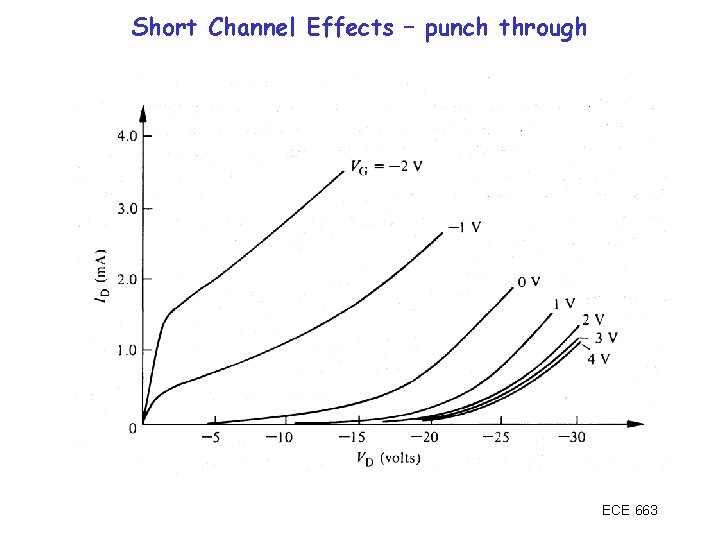

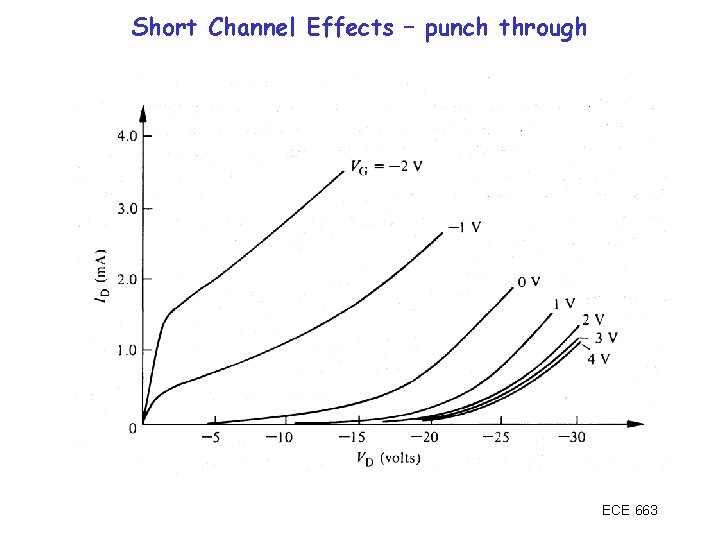

Short Channel Effects – punch through ECE 663

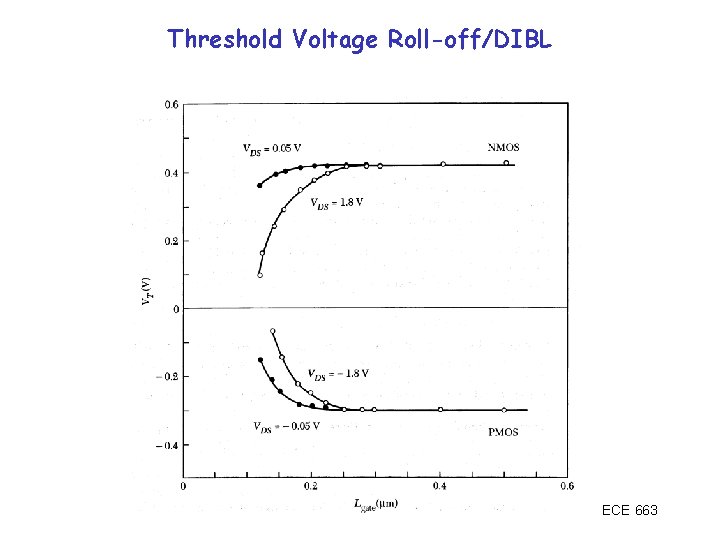

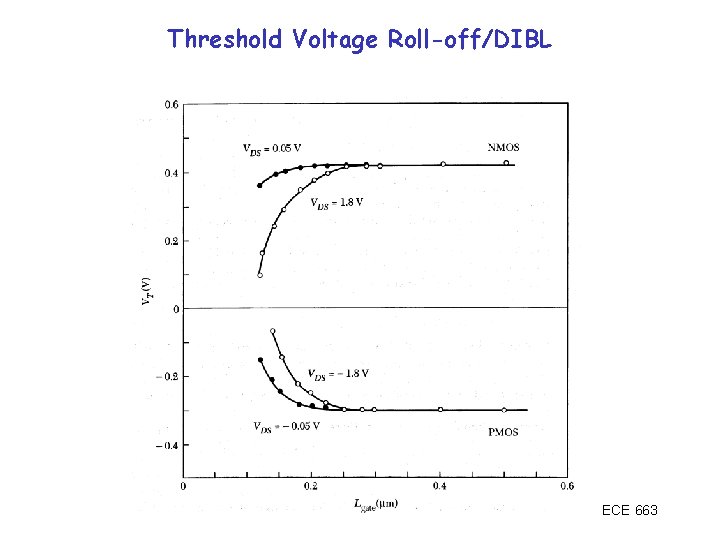

Threshold Voltage Roll-off/DIBL ECE 663

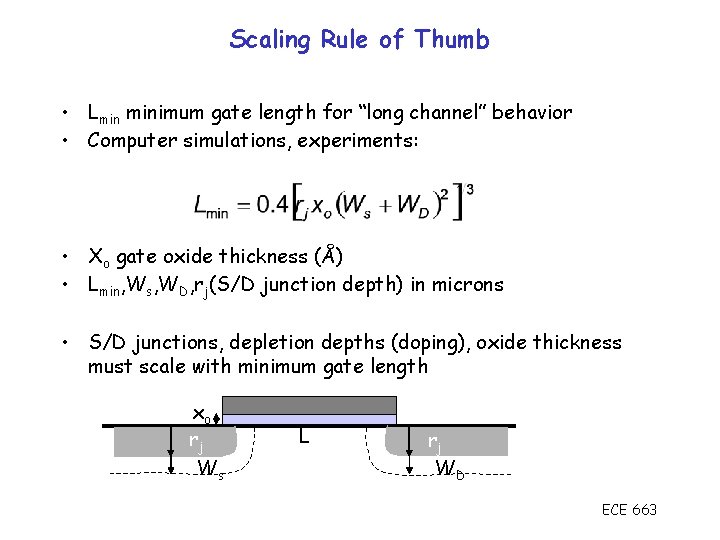

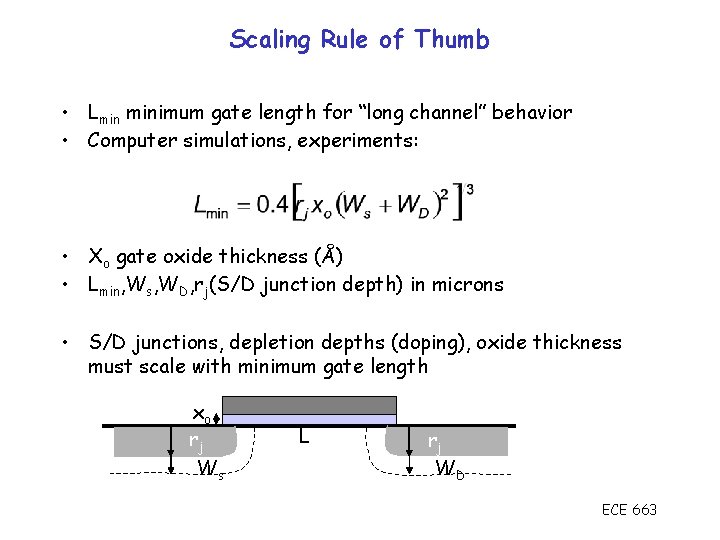

Scaling Rule of Thumb • Lmin minimum gate length for “long channel” behavior • Computer simulations, experiments: • Xo gate oxide thickness (Å) • Lmin, Ws, WD, rj(S/D junction depth) in microns • S/D junctions, depletion depths (doping), oxide thickness must scale with minimum gate length xo rj Ws L rj WD ECE 663

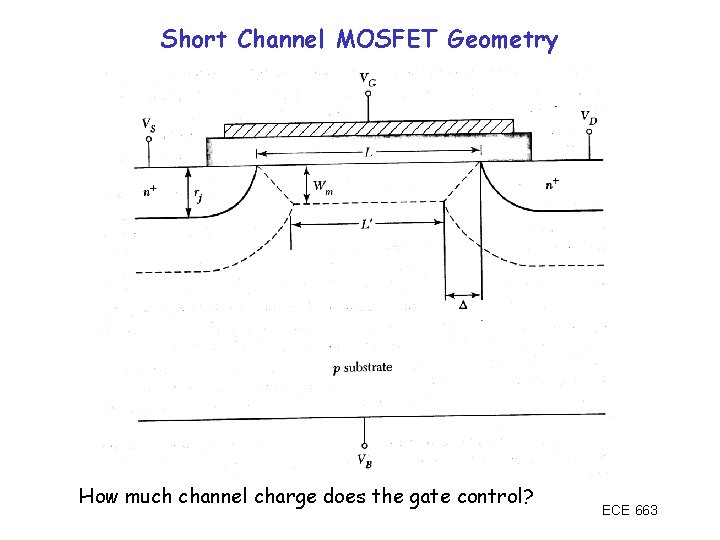

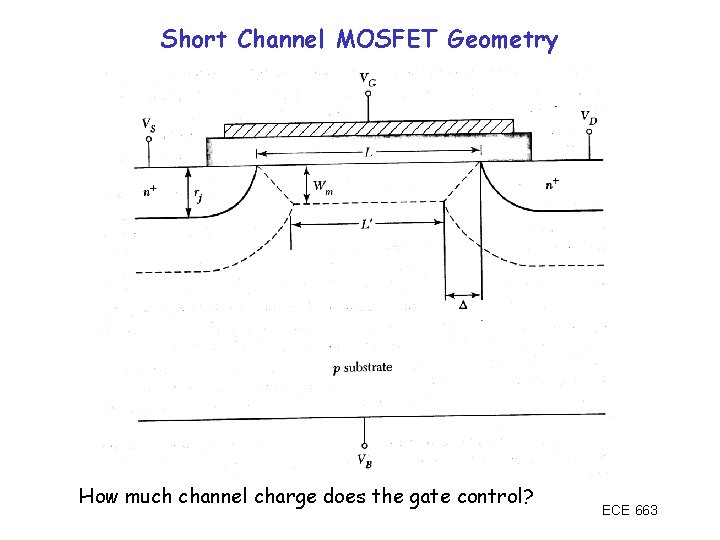

Short Channel MOSFET Geometry How much channel charge does the gate control? ECE 663

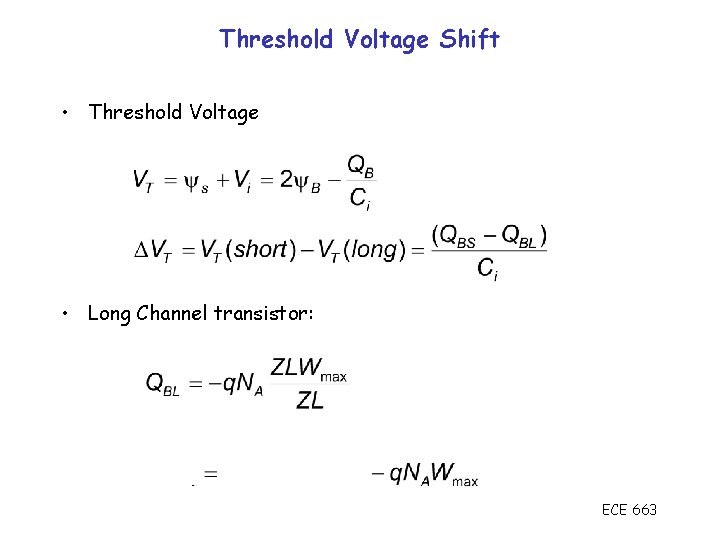

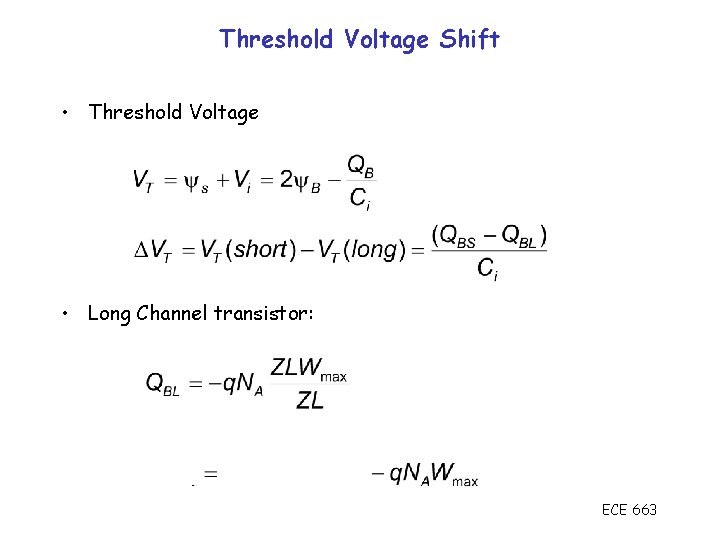

Threshold Voltage Shift • Threshold Voltage • Long Channel transistor: ECE 663

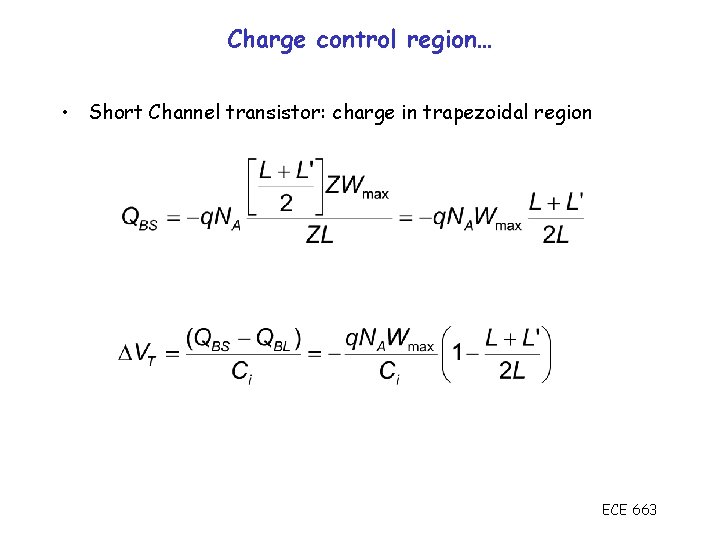

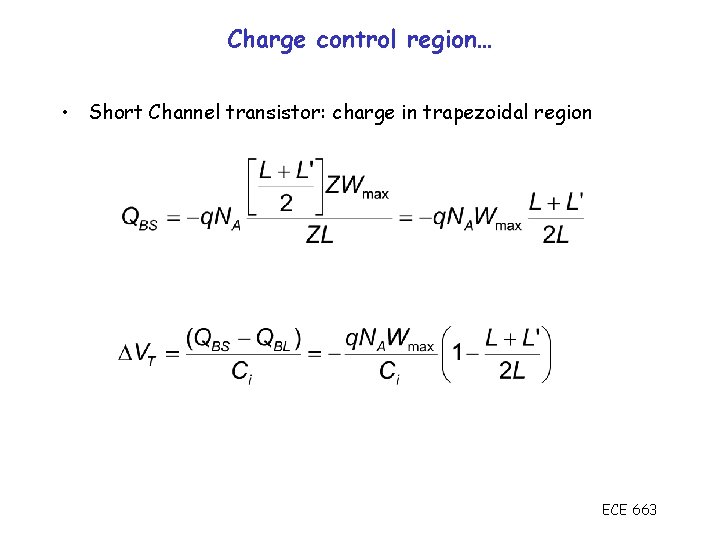

Charge control region… • Short Channel transistor: charge in trapezoidal region ECE 663

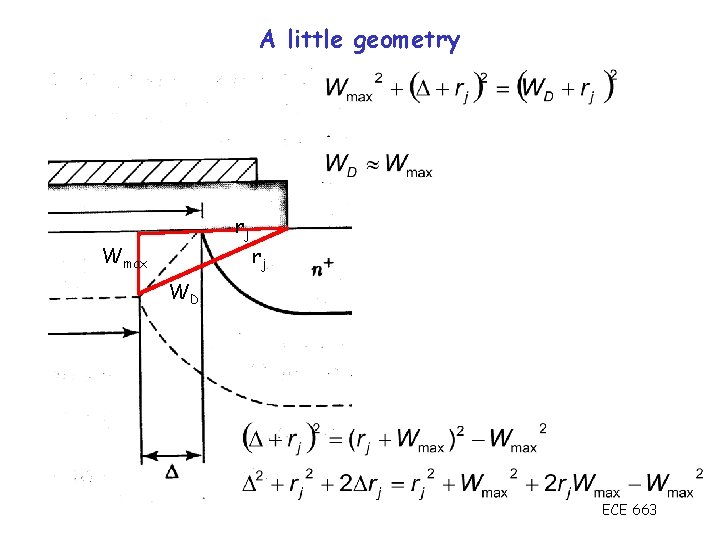

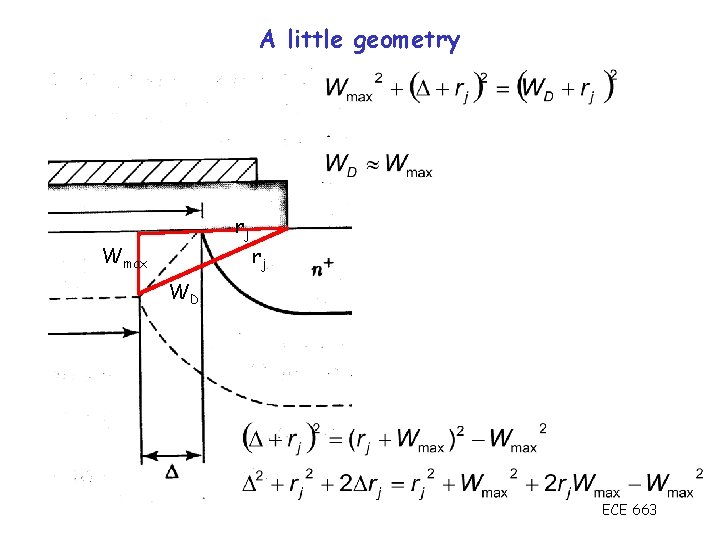

A little geometry rj Wmax rj WD ECE 663

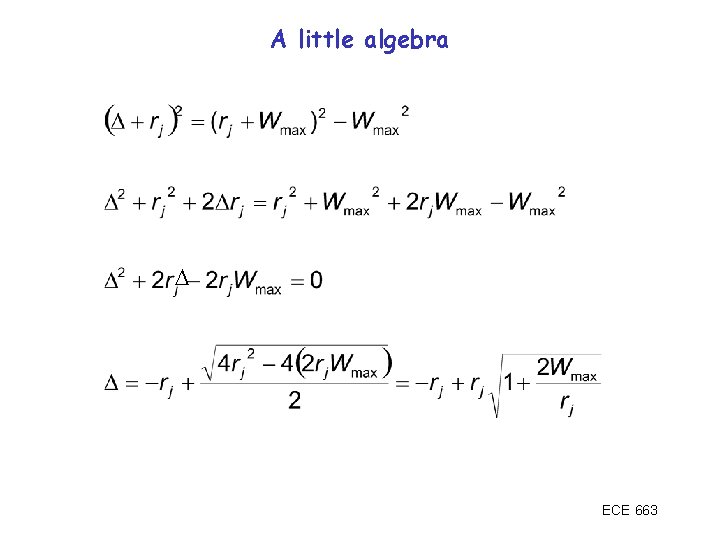

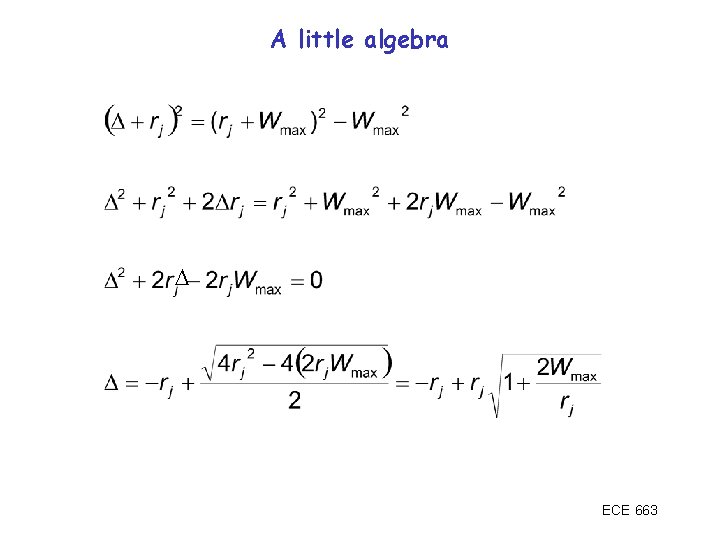

A little algebra D ECE 663

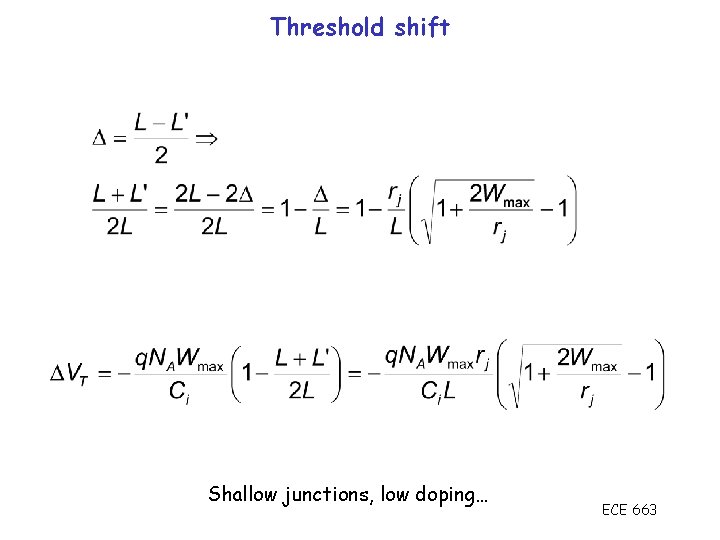

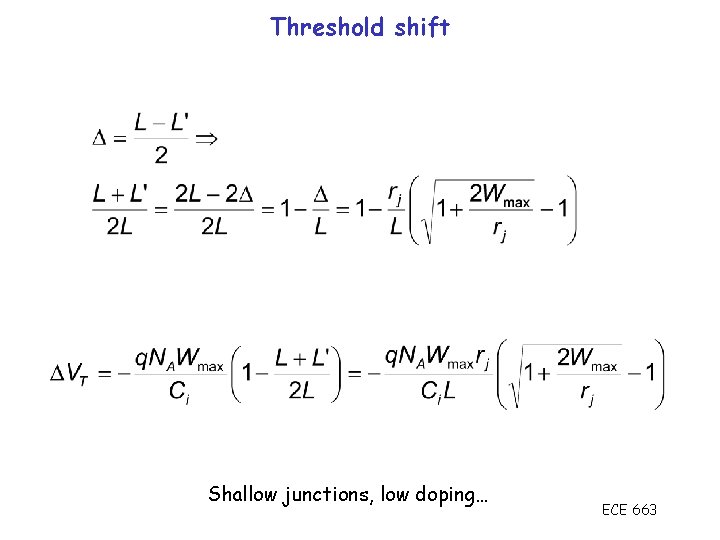

Threshold shift Shallow junctions, low doping… ECE 663

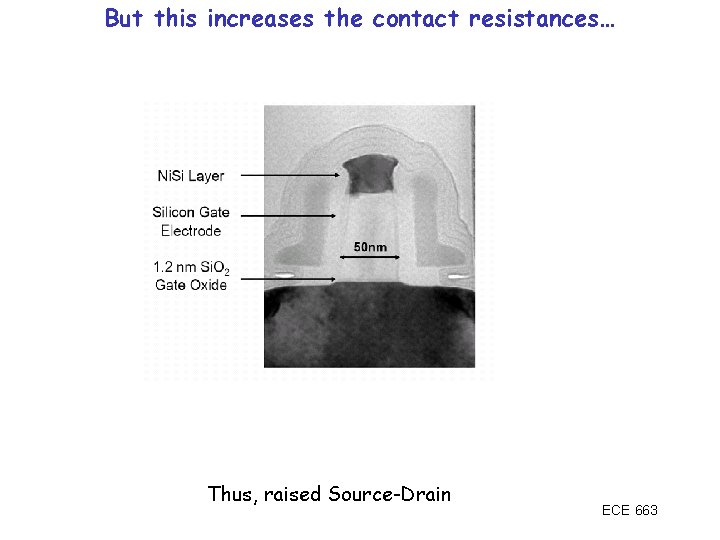

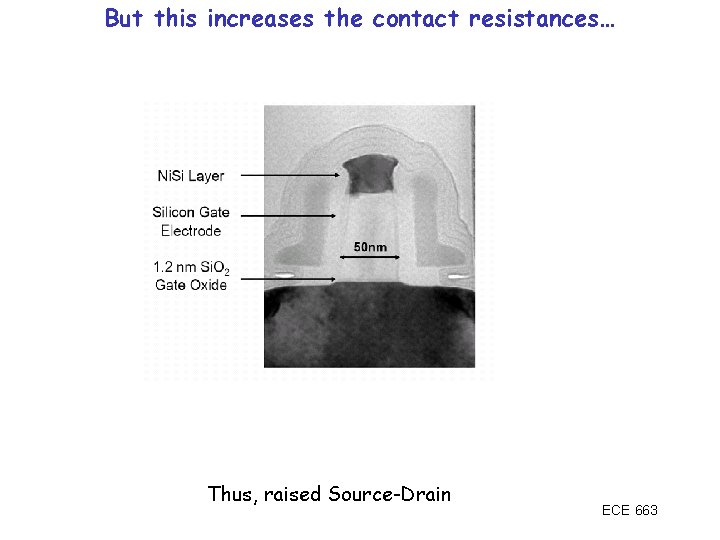

But this increases the contact resistances… Thus, raised Source-Drain ECE 663

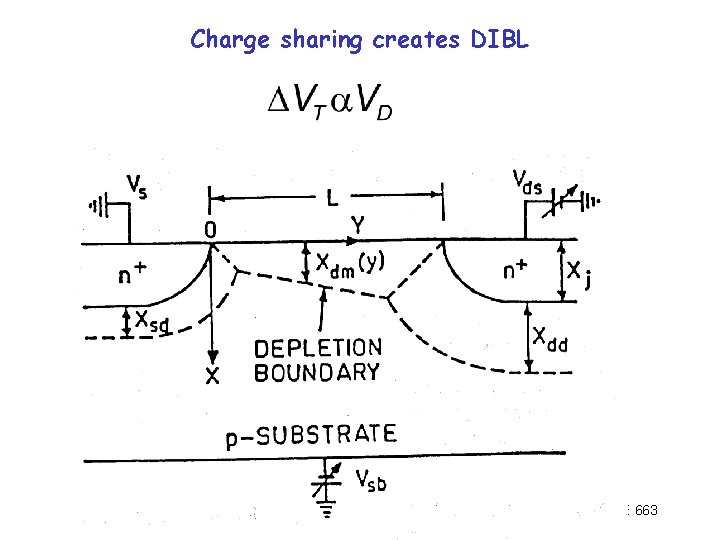

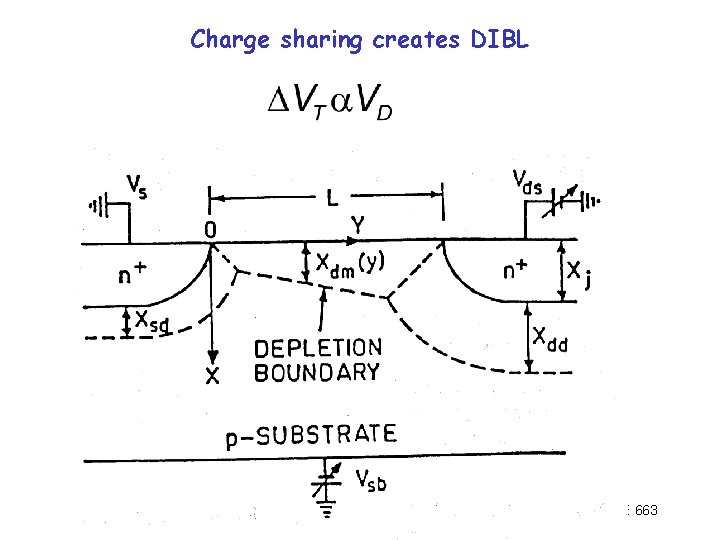

Charge sharing creates DIBL ECE 663

Charge sharing creates DIBL 3 D Simulation of Nanowire FETs using Quantum Models Vijay Sai Patnaik, Ankit Gheedia and M. Jagadesh Kumar The authors are with the Department of Electrical Engineering, Indian Institute of Technology, Huaz Khas, New Delhi 110 016, India (Email: vijaysai. patnaik@gmail. com) ECE 663

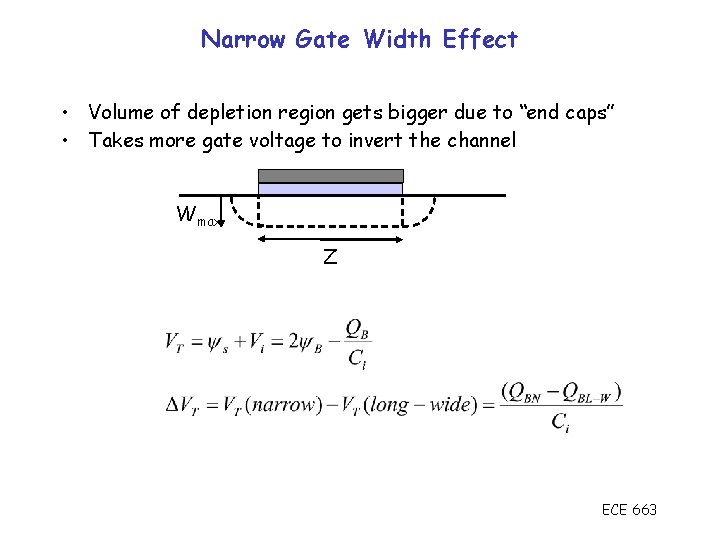

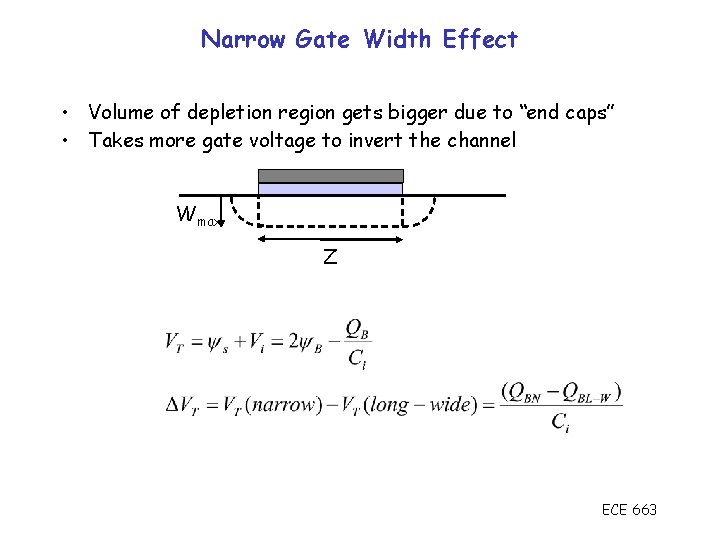

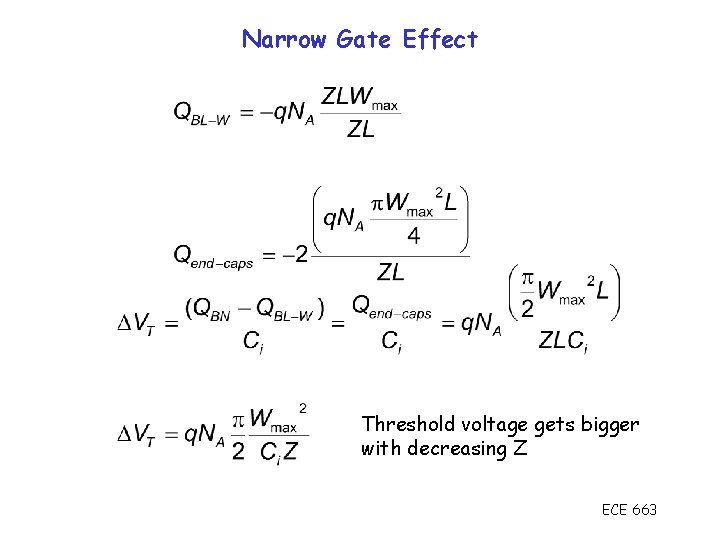

Narrow Gate Width Effect • Volume of depletion region gets bigger due to “end caps” • Takes more gate voltage to invert the channel Wmax Z ECE 663

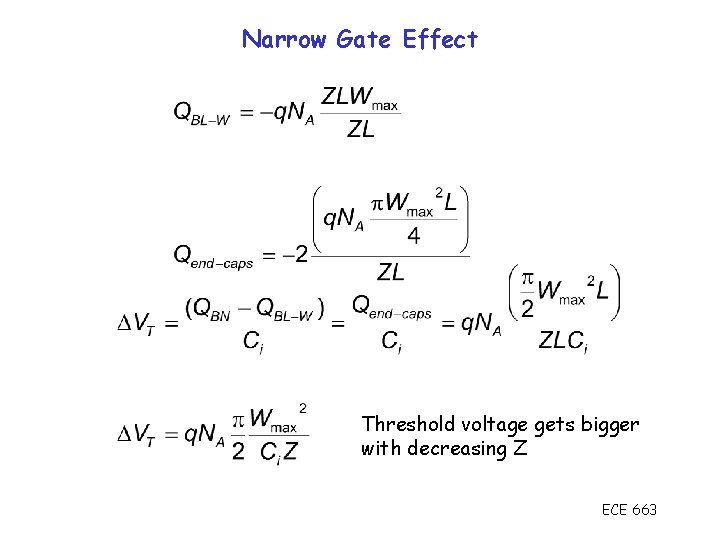

Narrow Gate Effect Threshold voltage gets bigger with decreasing Z ECE 663

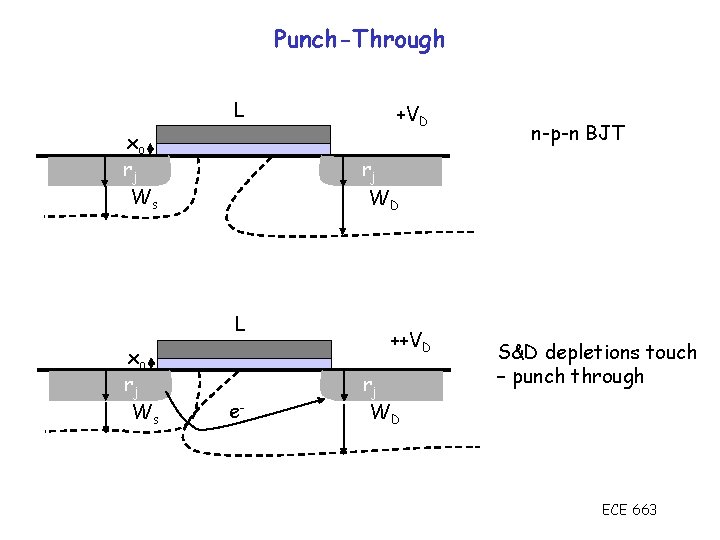

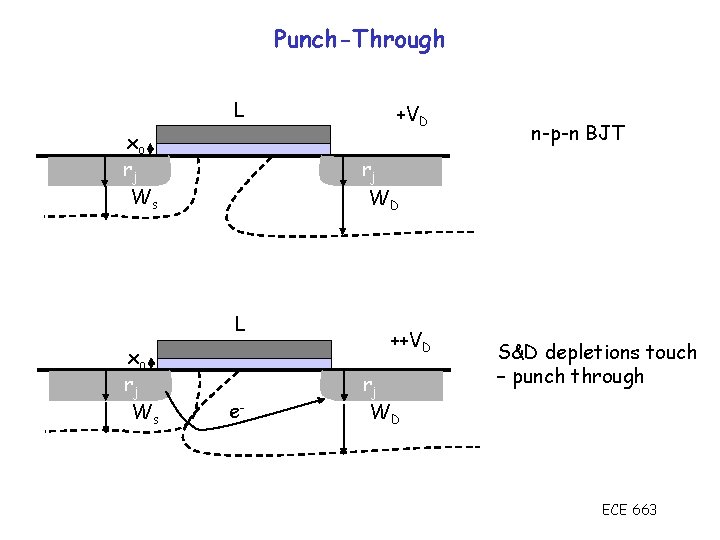

Punch-Through L xo rj Ws n-p-n BJT rj WD L xo rj Ws +VD e- ++VD rj WD S&D depletions touch – punch through ECE 663

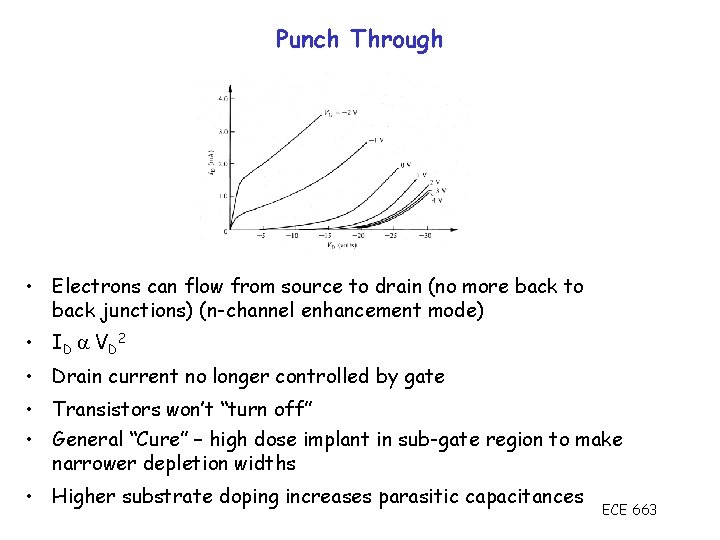

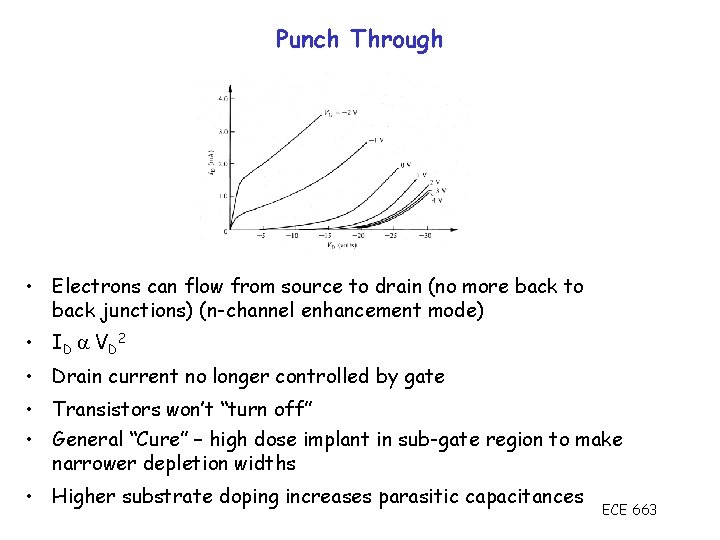

Punch Through • Electrons can flow from source to drain (no more back to back junctions) (n-channel enhancement mode) • ID VD 2 • Drain current no longer controlled by gate • Transistors won’t “turn off” • General “Cure” – high dose implant in sub-gate region to make narrower depletion widths • Higher substrate doping increases parasitic capacitances ECE 663

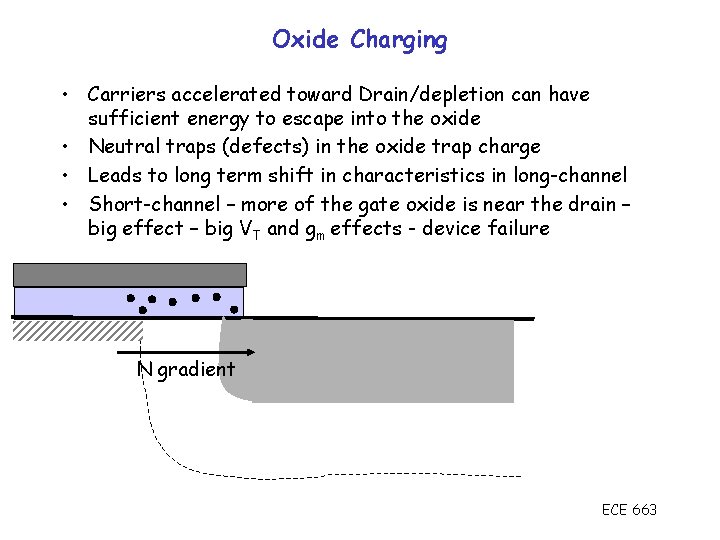

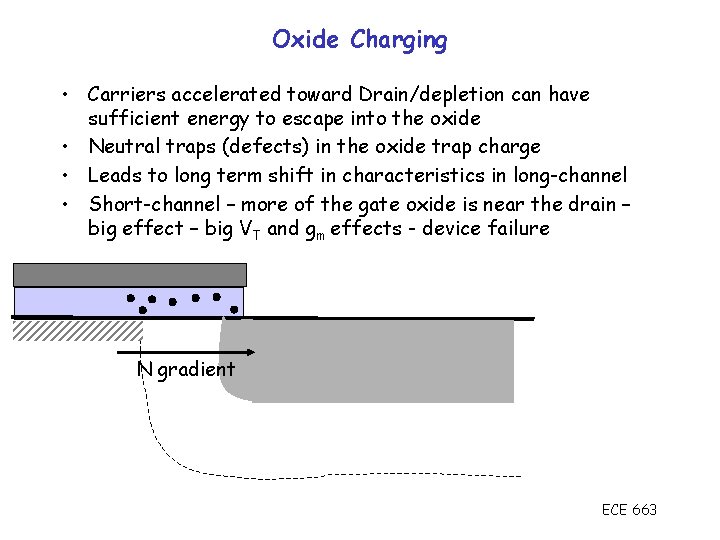

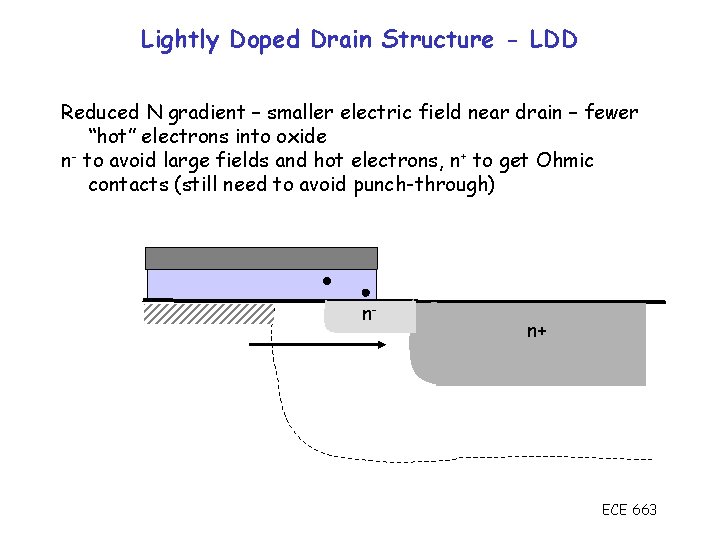

Oxide Charging • Carriers accelerated toward Drain/depletion can have sufficient energy to escape into the oxide • Neutral traps (defects) in the oxide trap charge • Leads to long term shift in characteristics in long-channel • Short-channel – more of the gate oxide is near the drain – big effect – big VT and gm effects - device failure N gradient ECE 663

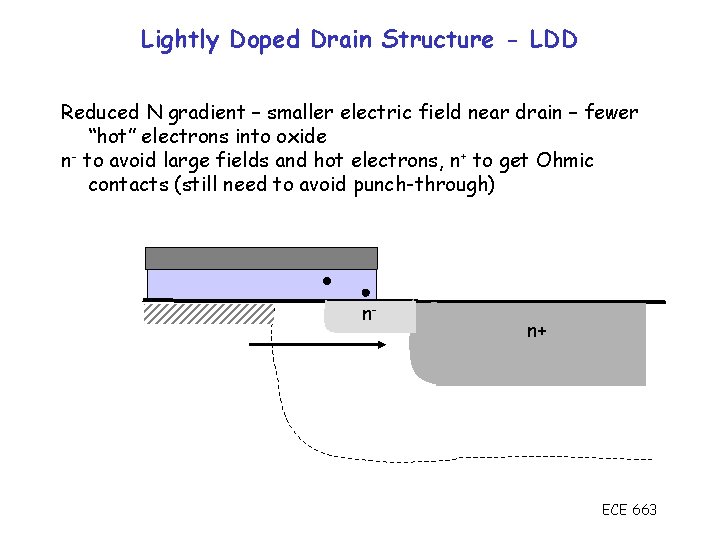

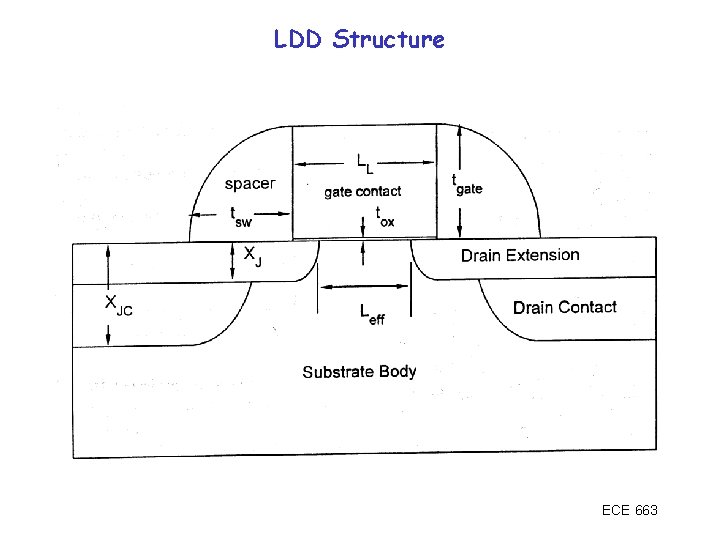

Lightly Doped Drain Structure - LDD Reduced N gradient – smaller electric field near drain – fewer “hot” electrons into oxide n- to avoid large fields and hot electrons, n+ to get Ohmic contacts (still need to avoid punch-through) n- n+ ECE 663

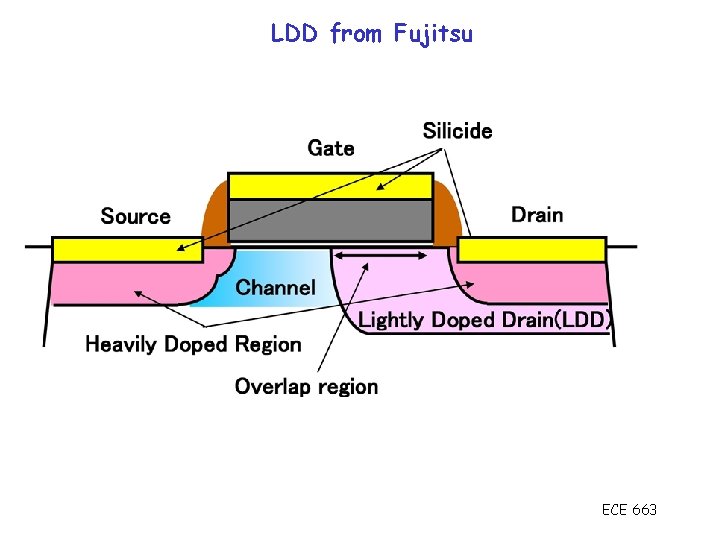

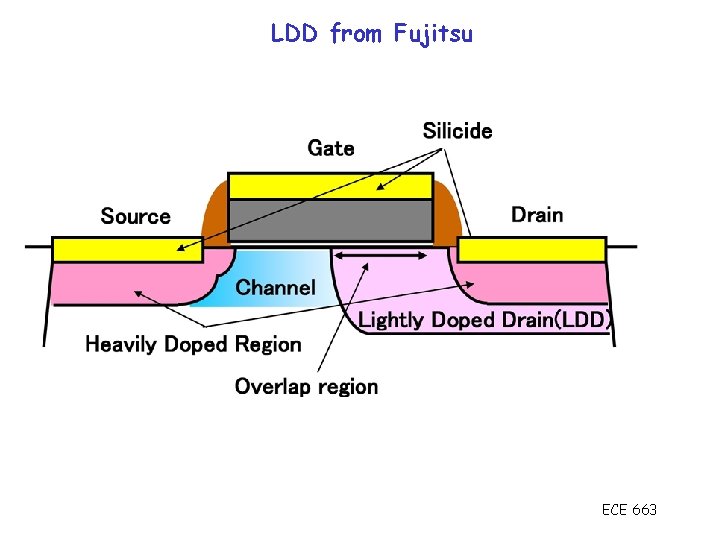

LDDDrain from. Structure Fujitsu - LDD Lightly Doped Reduced N gradient – smaller electric field near drain – fewer “hot” electrons into oxide n- to avoid large fields and hot electrons, n+ to get Ohmic contacts n- n+ ECE 663

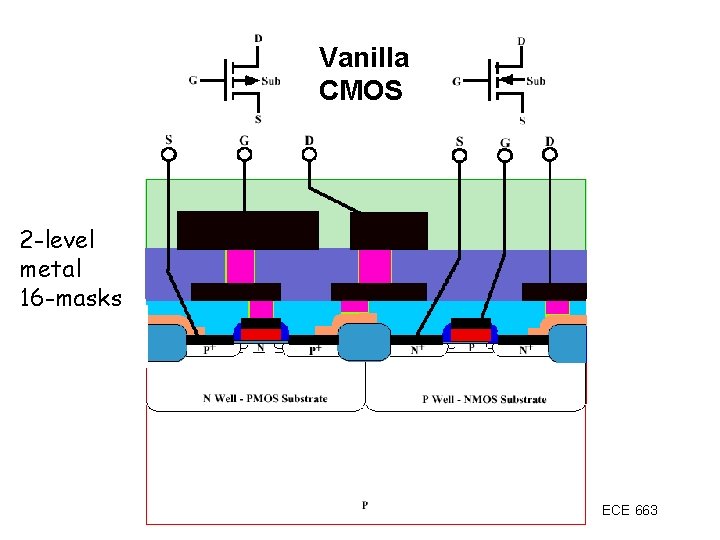

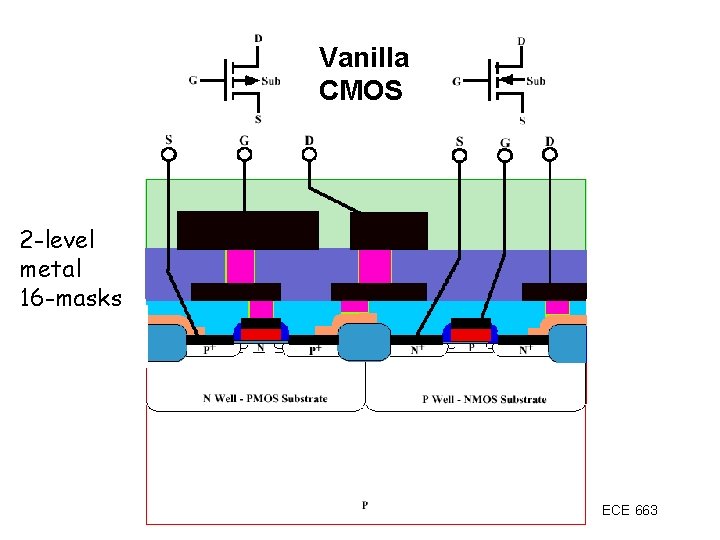

Vanilla CMOS 2 -level metal 16 -masks ECE 663

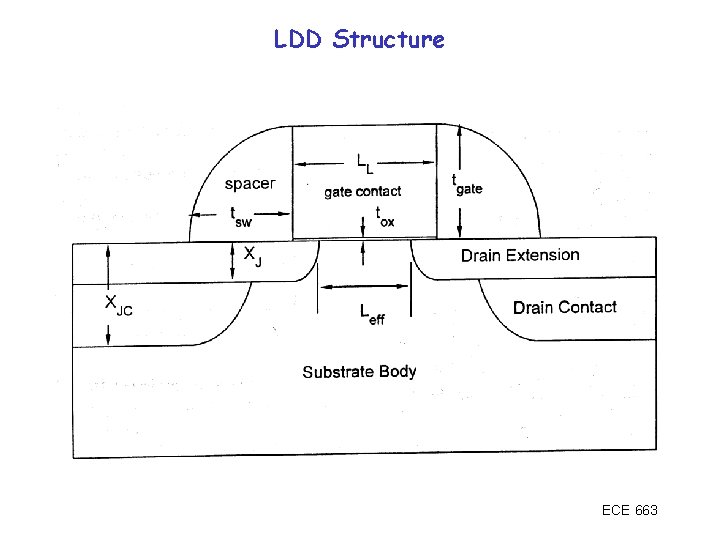

LDD Structure ECE 663

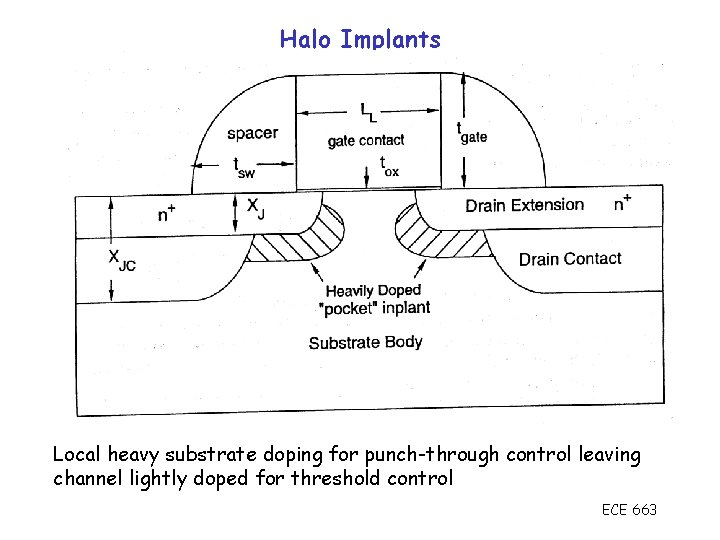

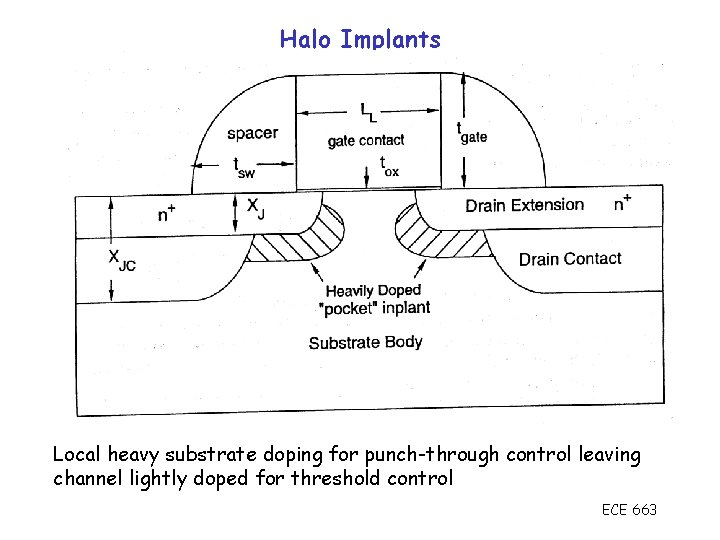

Halo Implants Local heavy substrate doping for punch-through control leaving channel lightly doped for threshold control ECE 663

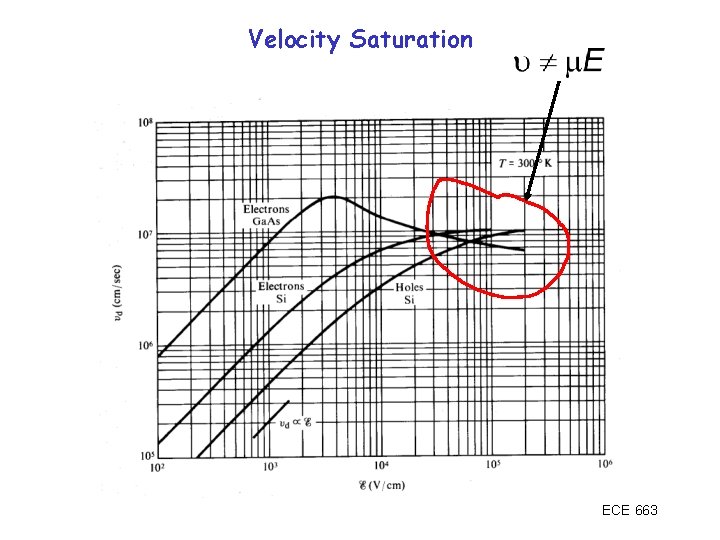

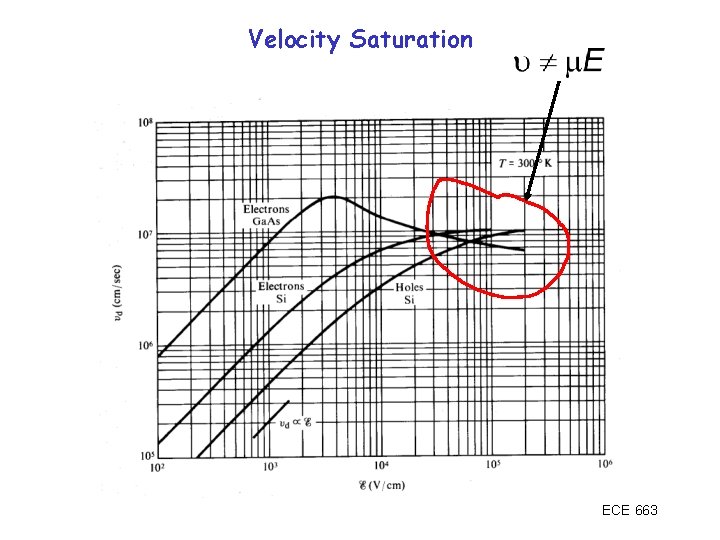

Velocity Saturation ECE 663

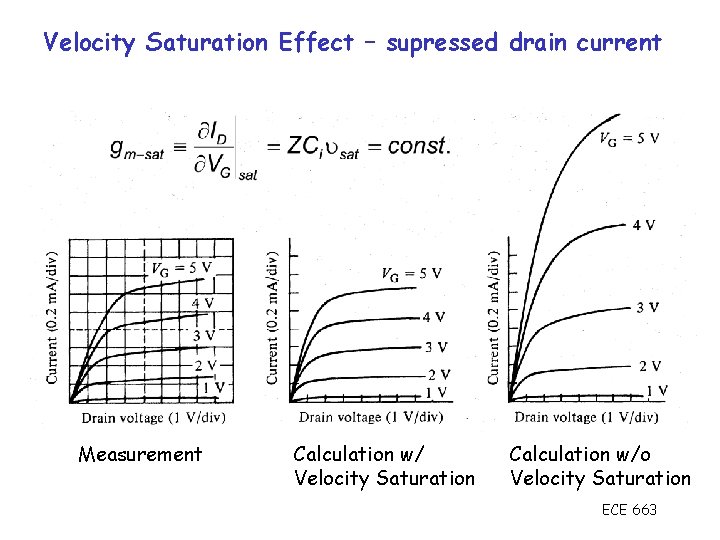

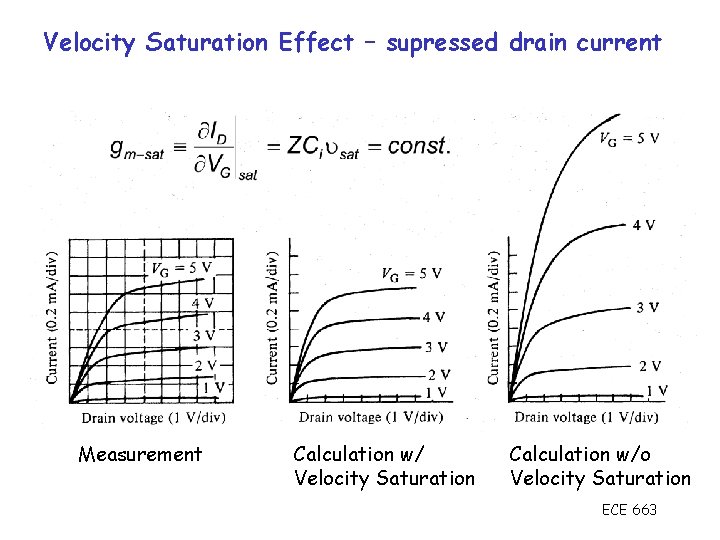

Velocity Saturation Effect – supressed drain current Measurement Calculation w/ Velocity Saturation Calculation w/o Velocity Saturation ECE 663

ECE 663

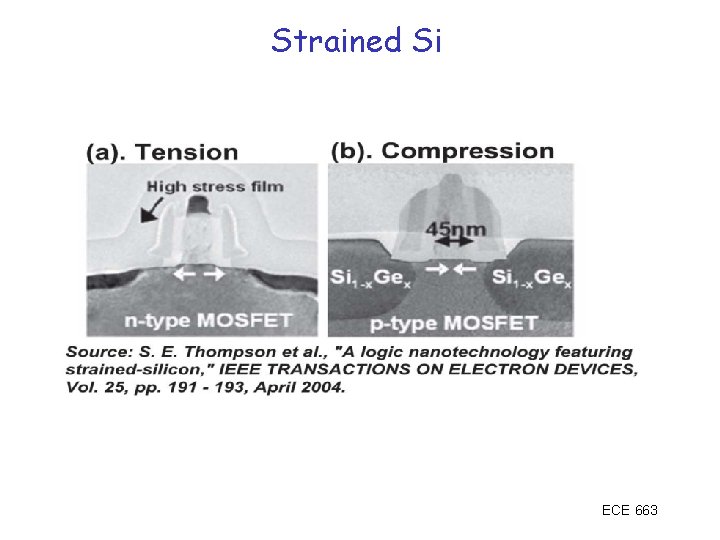

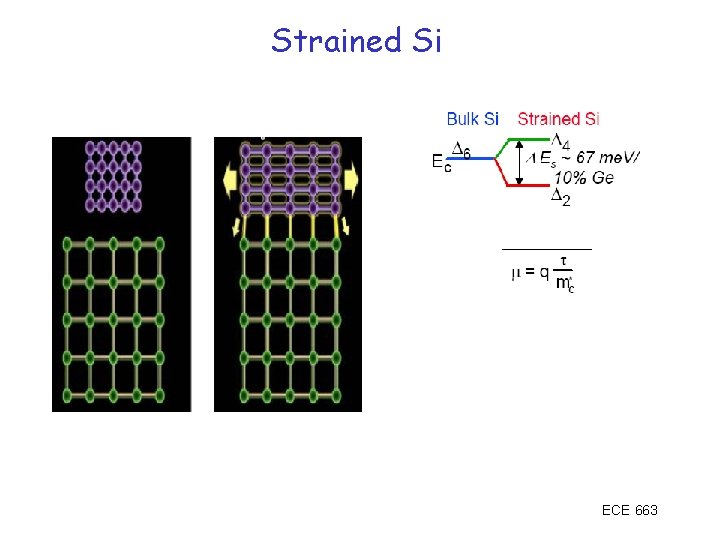

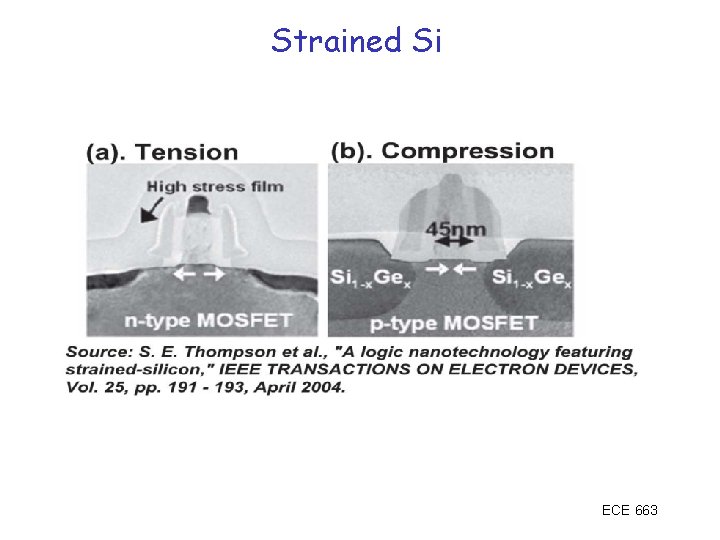

Strained Si ECE 663

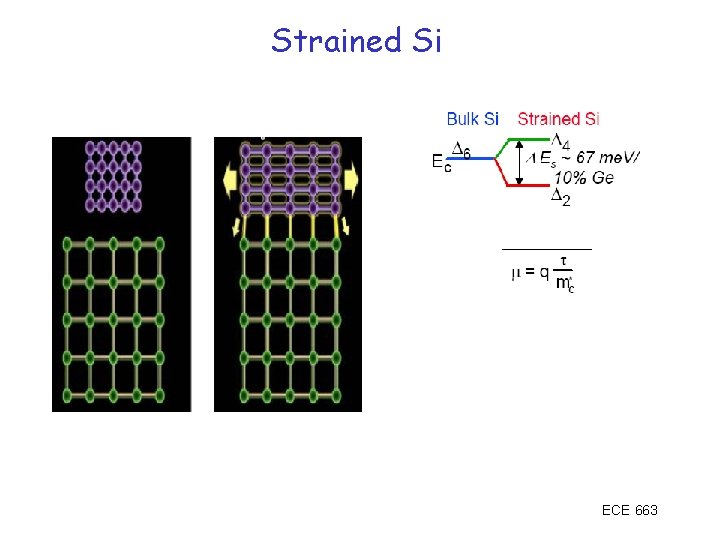

Strained Si ECE 663

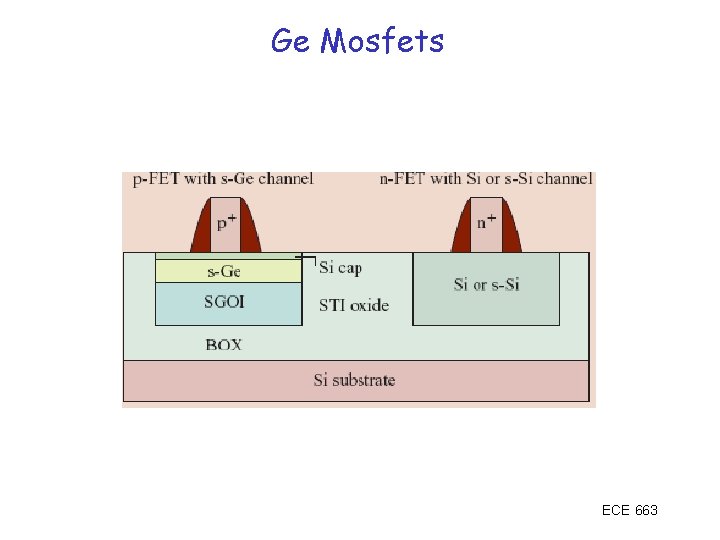

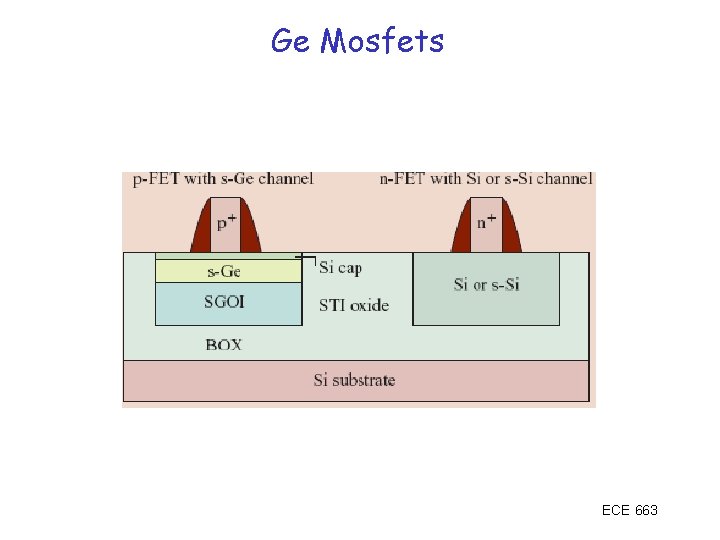

Ge Mosfets ECE 663

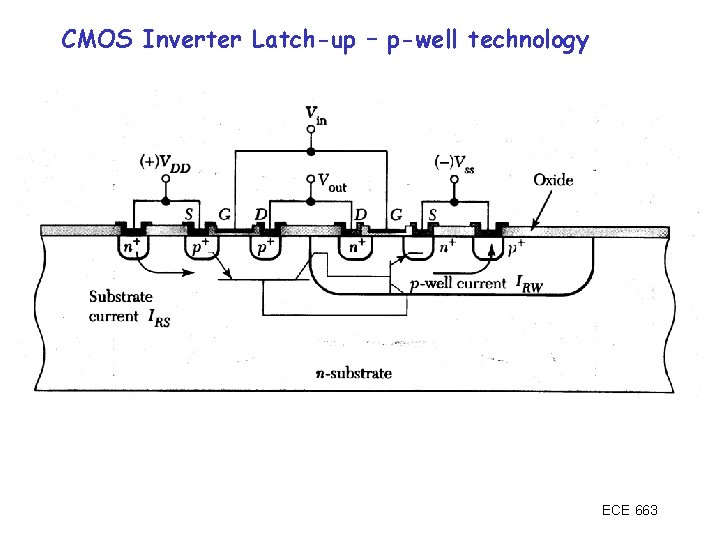

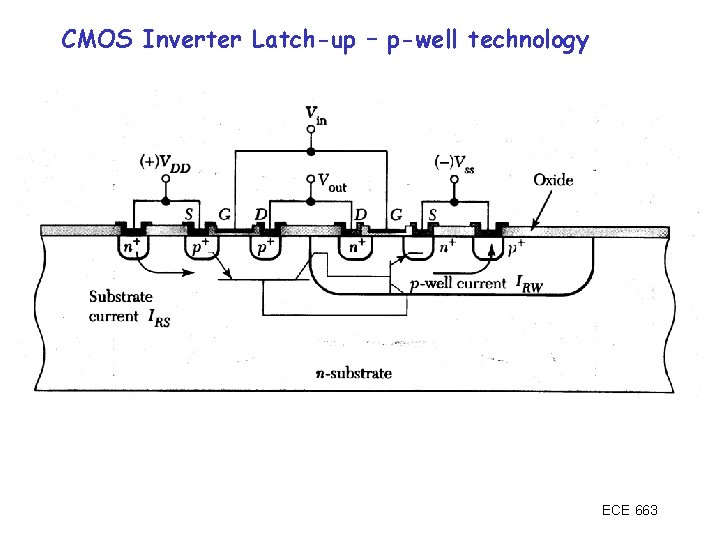

CMOS Inverter Latch-up – p-well technology ECE 663

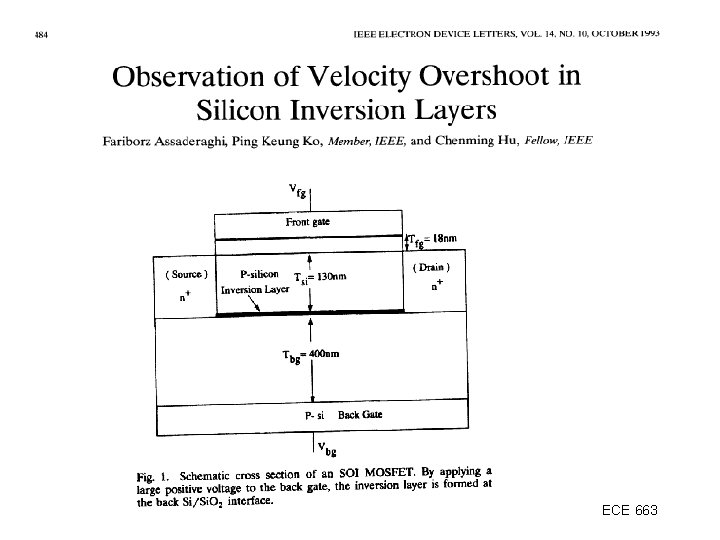

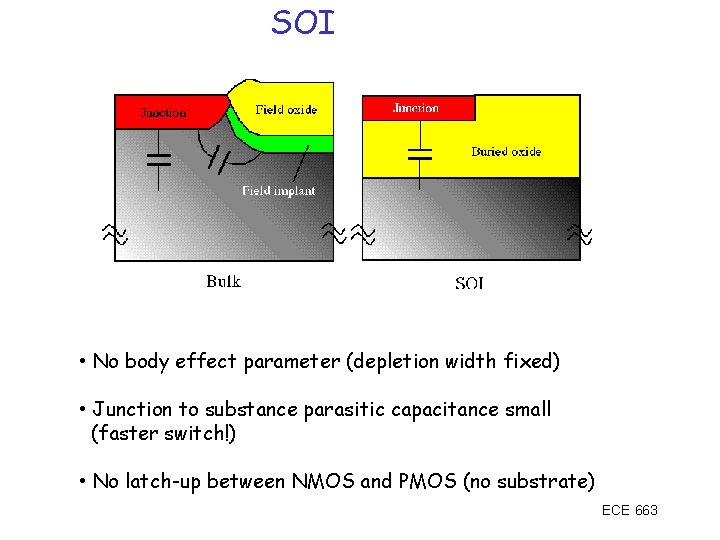

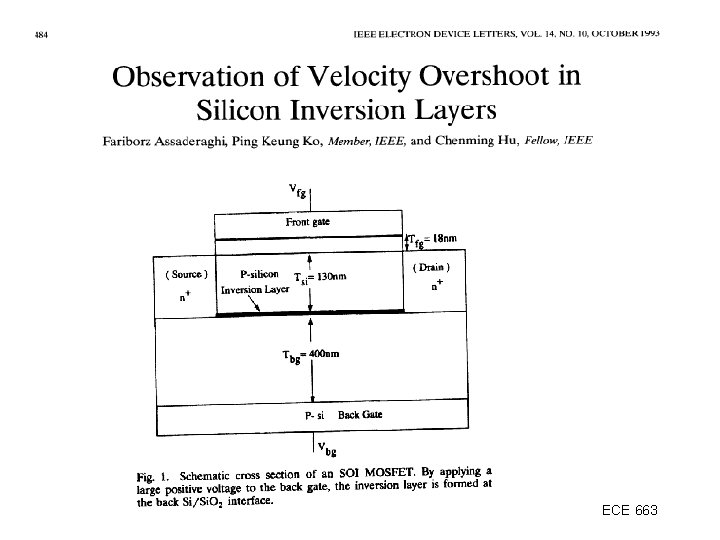

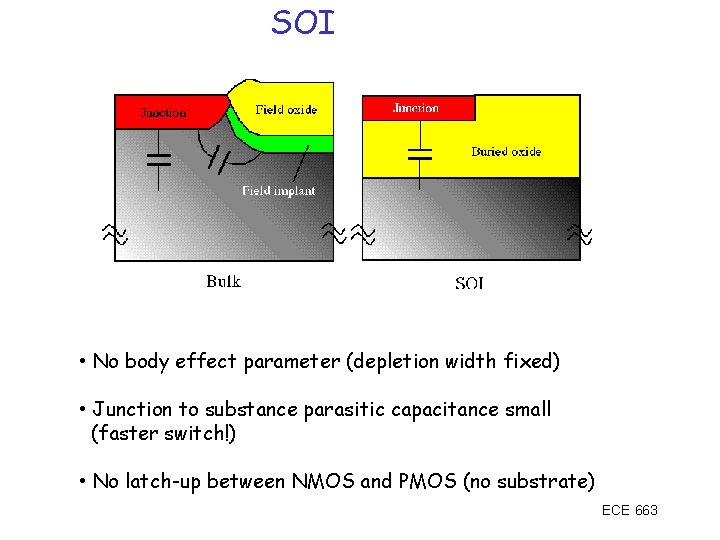

SOI • No body effect parameter (depletion width fixed) • Junction to substance parasitic capacitance small (faster switch!) • No latch-up between NMOS and PMOS (no substrate) ECE 663

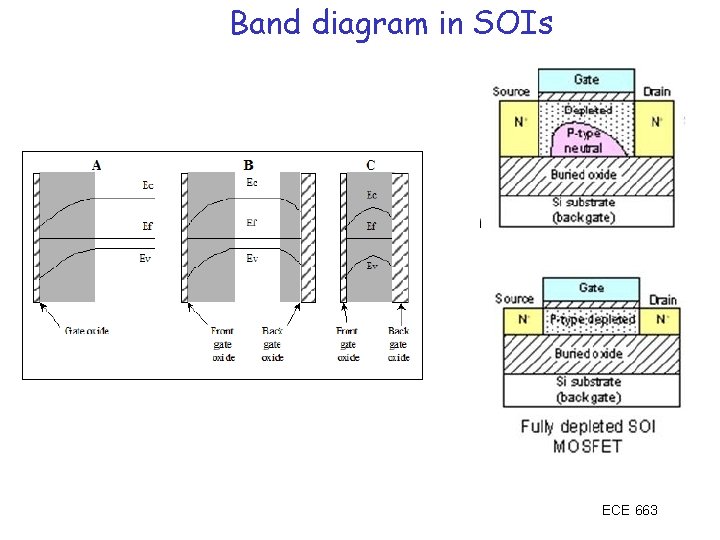

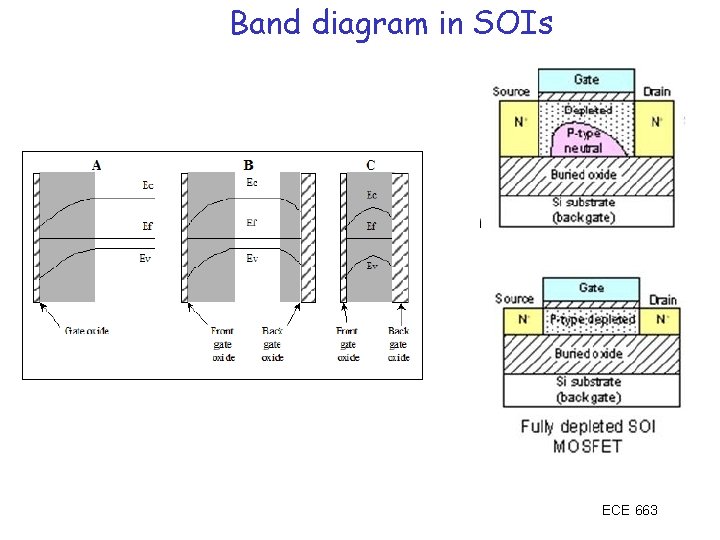

Band diagram in SOIs ECE 663

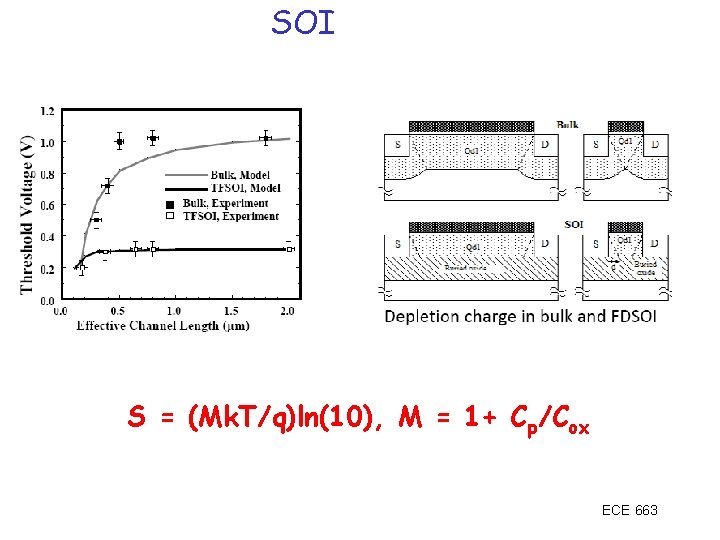

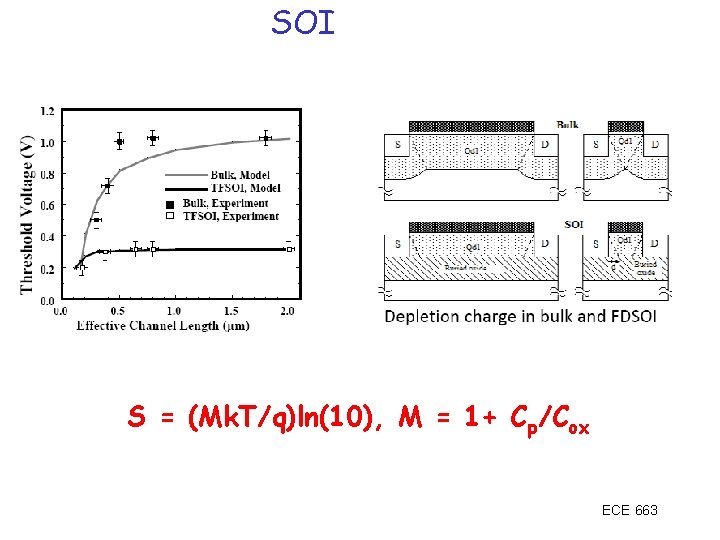

SOI S = (Mk. T/q)ln(10), M = 1+ Cp/Cox ECE 663

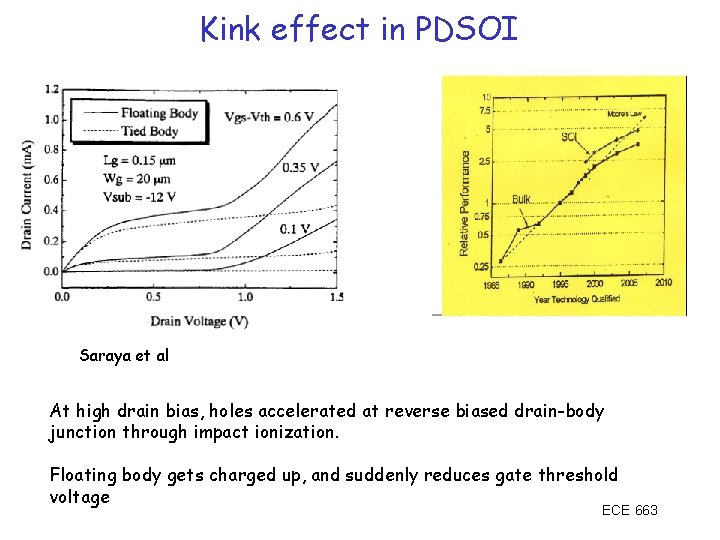

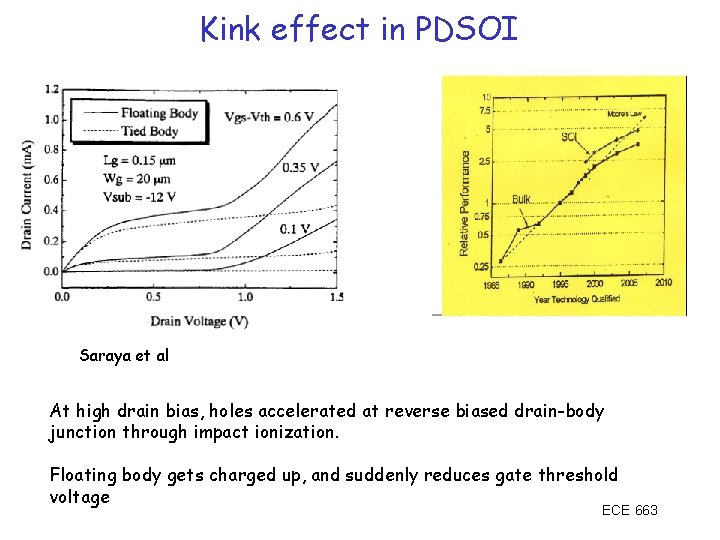

Kink effect in PDSOI Saraya et al At high drain bias, holes accelerated at reverse biased drain-body junction through impact ionization. Floating body gets charged up, and suddenly reduces gate threshold voltage ECE 663

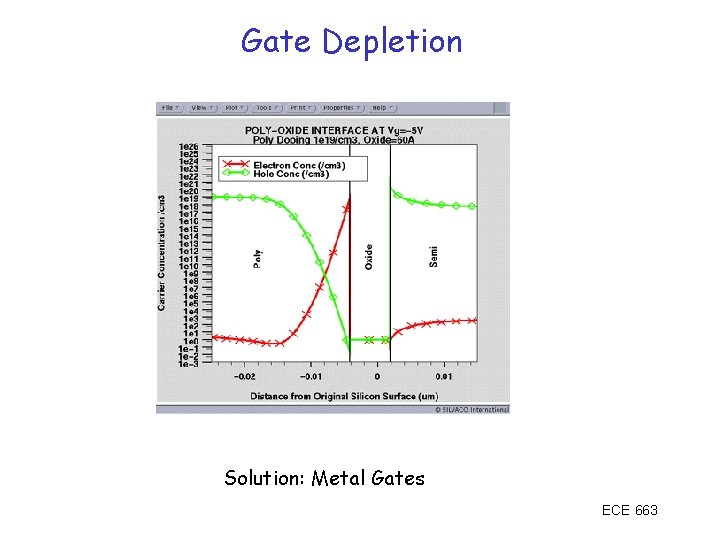

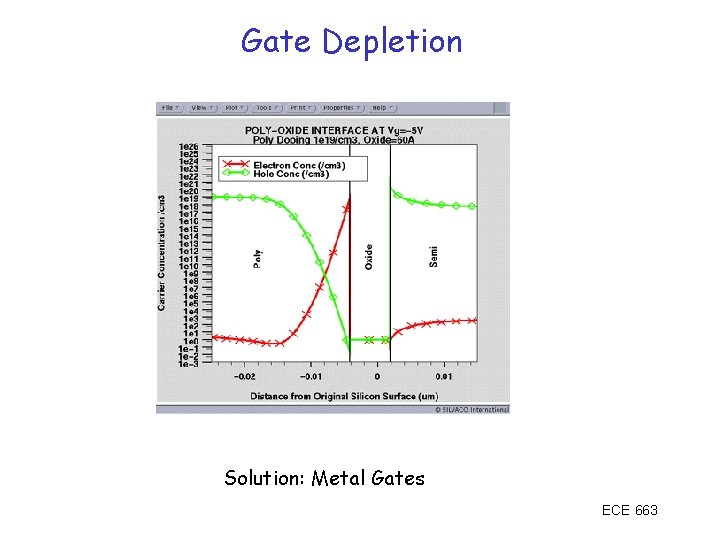

Gate Depletion Solution: Metal Gates ECE 663

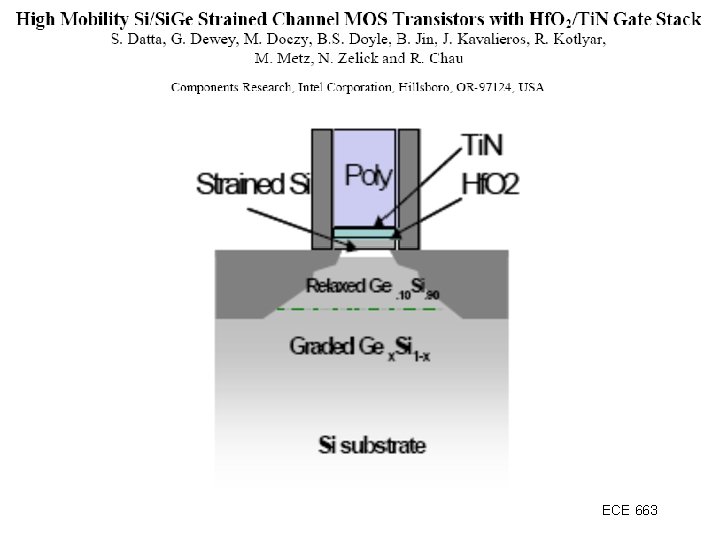

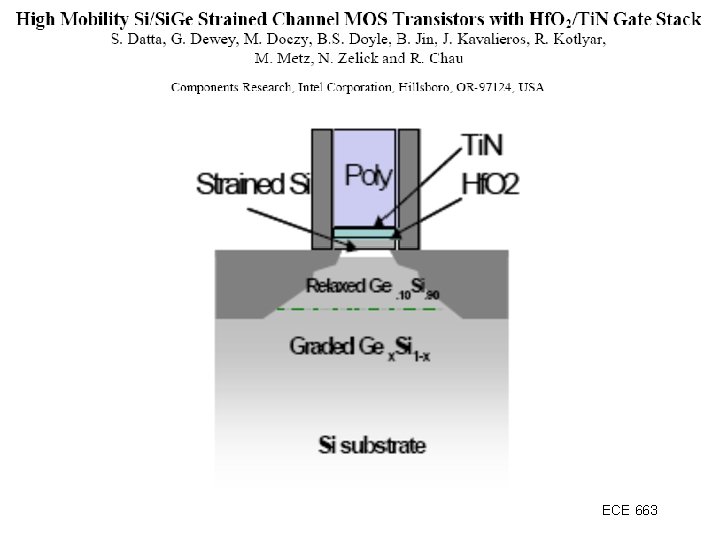

ECE 663

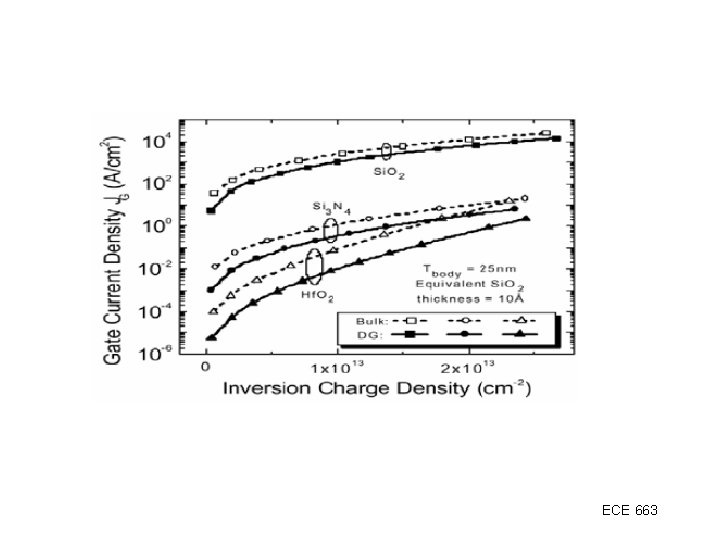

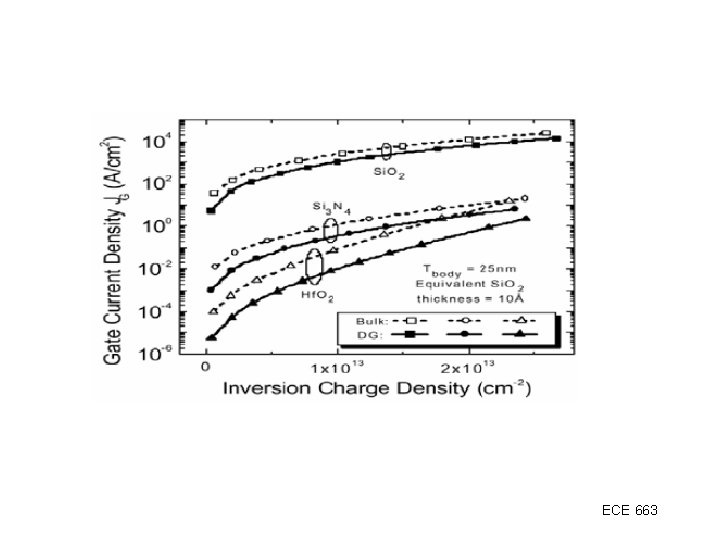

ECE 663

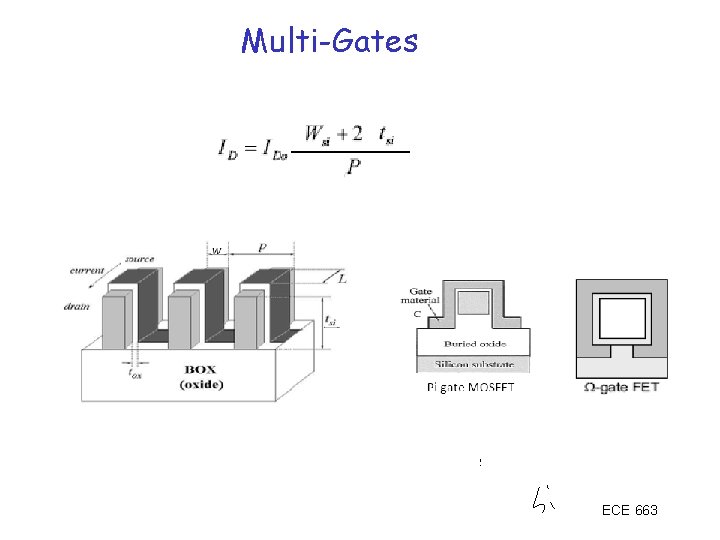

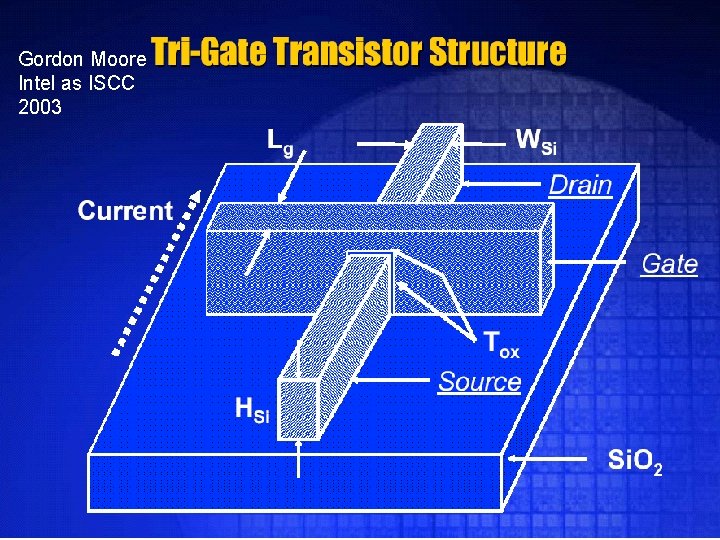

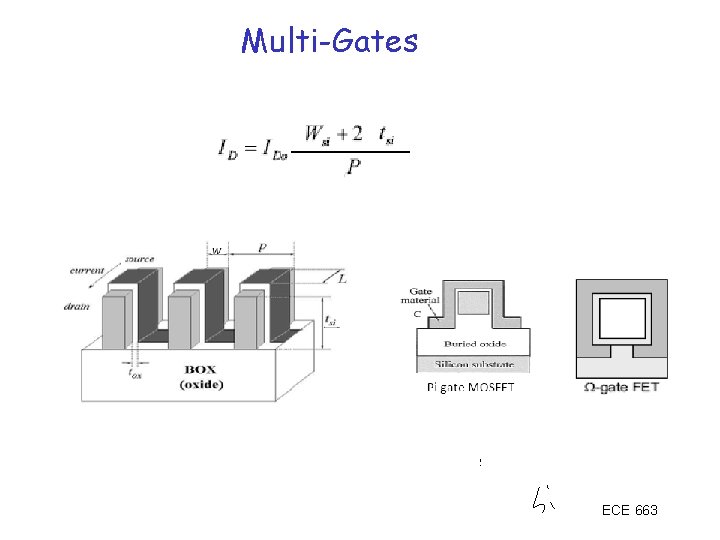

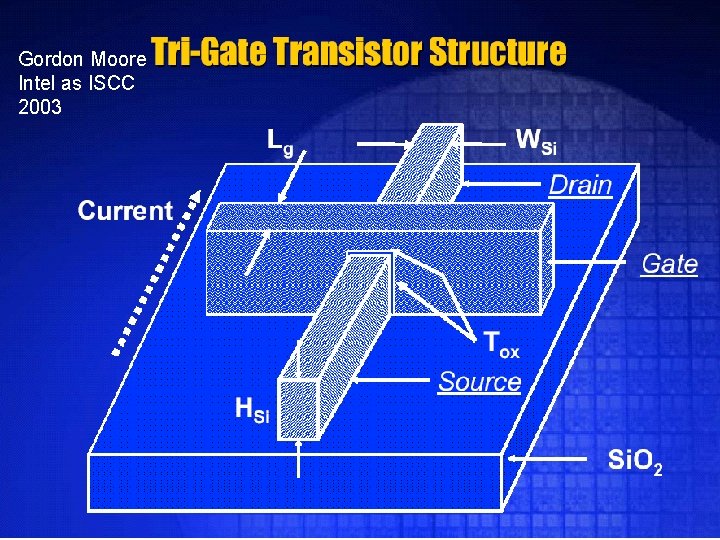

Gordon Moore Intel as ISCC 2003 Multi-Gates ECE 663

Gordon Moore Intel as ISCC 2003 ECE 663

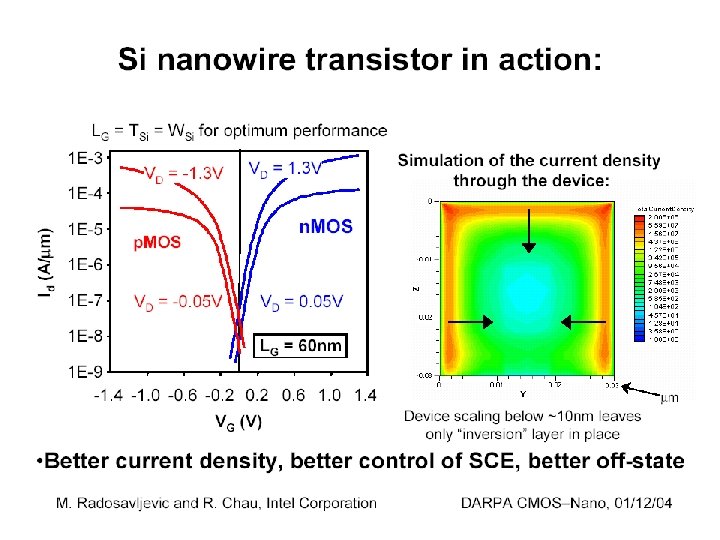

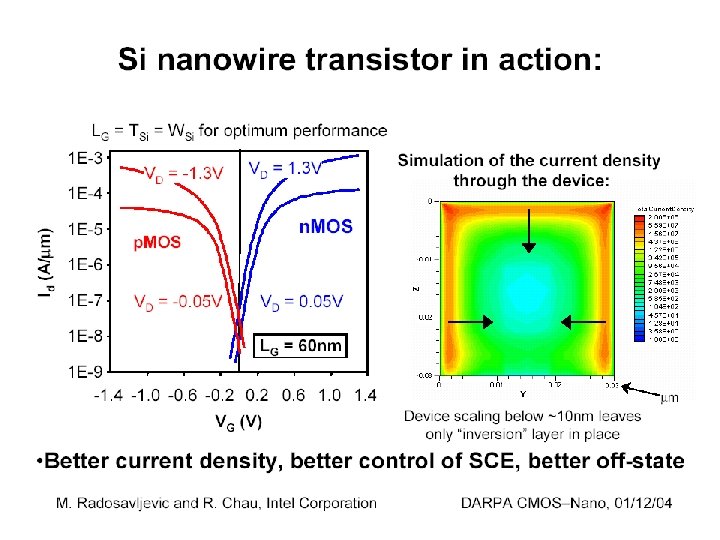

ECE 663