MOSFET Device Simulation MOSFET Device Structure Semiconductor Equations

- Slides: 17

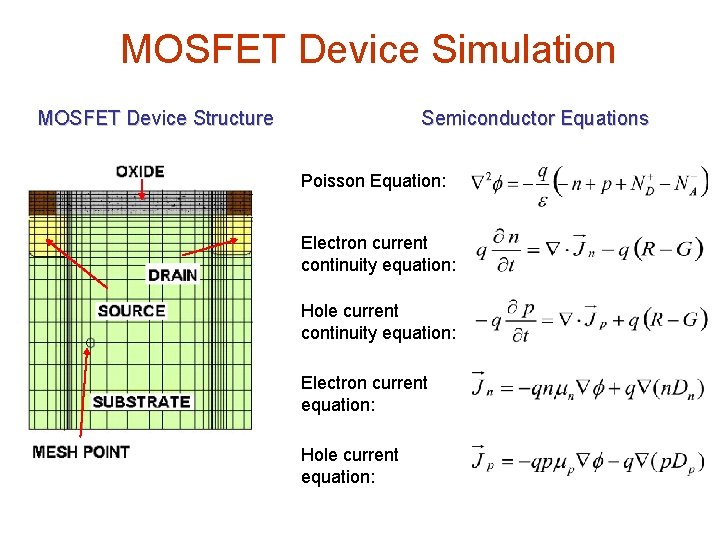

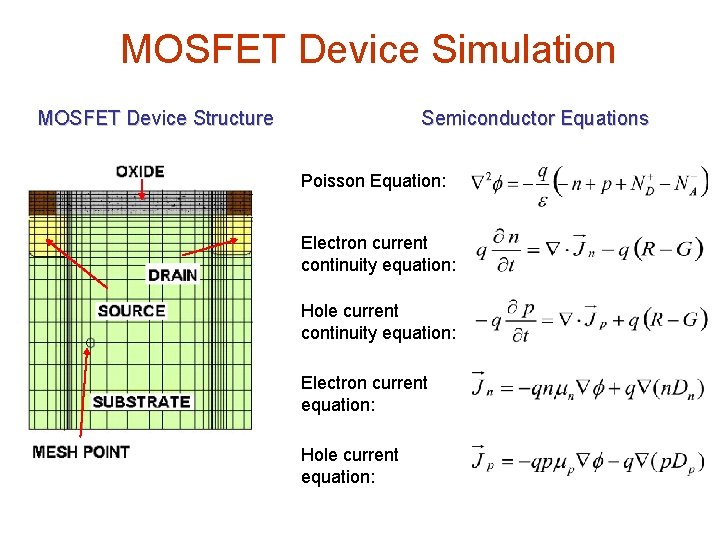

MOSFET Device Simulation MOSFET Device Structure Semiconductor Equations Poisson Equation: Electron current continuity equation: Hole current continuity equation: Electron current equation: Hole current equation:

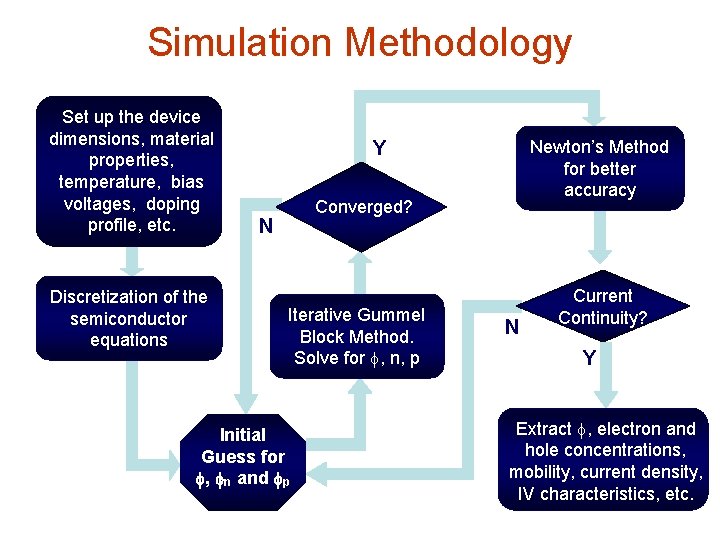

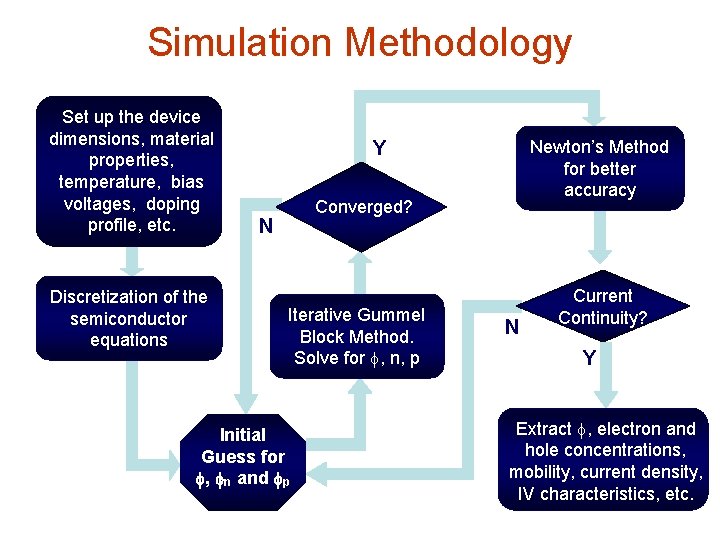

Simulation Methodology Set up the device dimensions, material properties, temperature, bias voltages, doping profile, etc. Discretization of the semiconductor equations Newton’s Method for better accuracy Y Converged? N Iterative Gummel Block Method. Solve for f, n, p Initial Guess for f, fn and fp N Current Continuity? Y Extract f, electron and hole concentrations, mobility, current density, IV characteristics, etc.

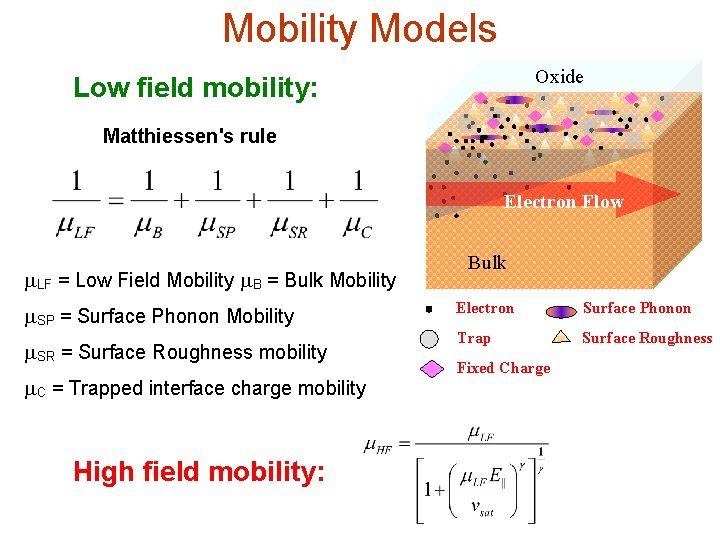

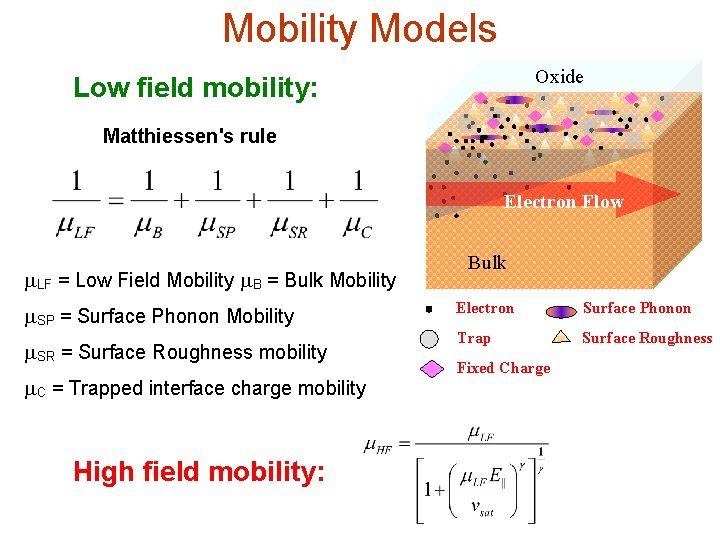

Mobility Models Oxide Low field mobility: Matthiessen's rule Electron Flow m. LF = Low Field Mobility m. B = Bulk Mobility m. SP = Surface Phonon Mobility m. SR = Surface Roughness mobility m. C = Trapped interface charge mobility High Field Mobility: High field mobility: Bulk Electron Surface Phonon Trap Surface Roughness Fixed Charge

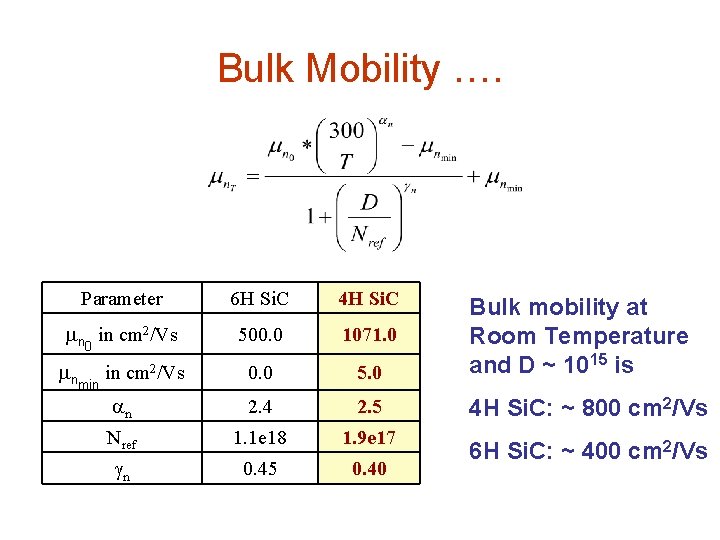

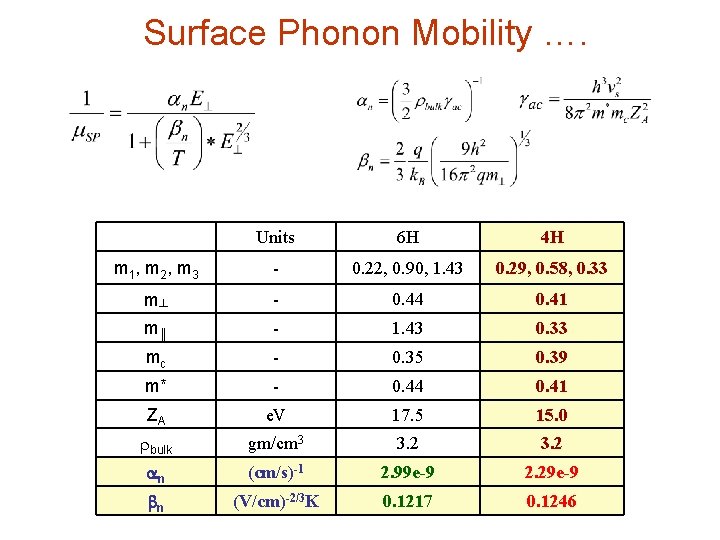

Caughey – Thomas Model for bulk mobility: Temperature dependence: Doping dependence: Surface Phonon Mobility: tac = Surface acoustic phonon relaxation time E┴ = Perpendicular E. Field an, bn = calculated from phonon scattering equation

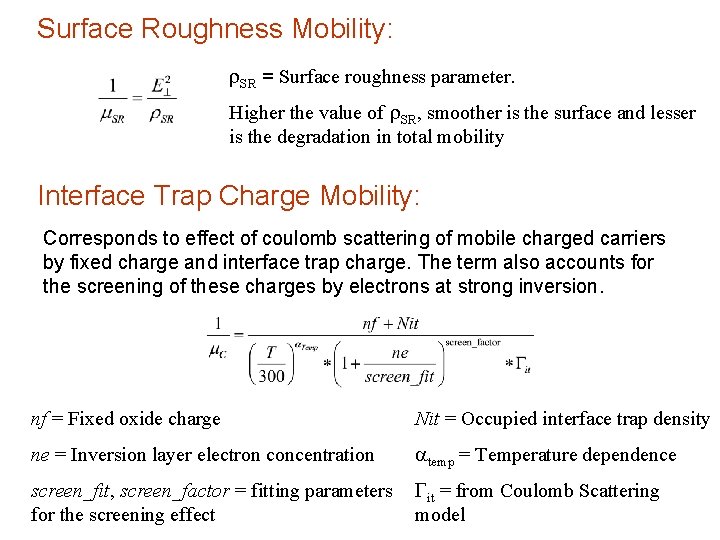

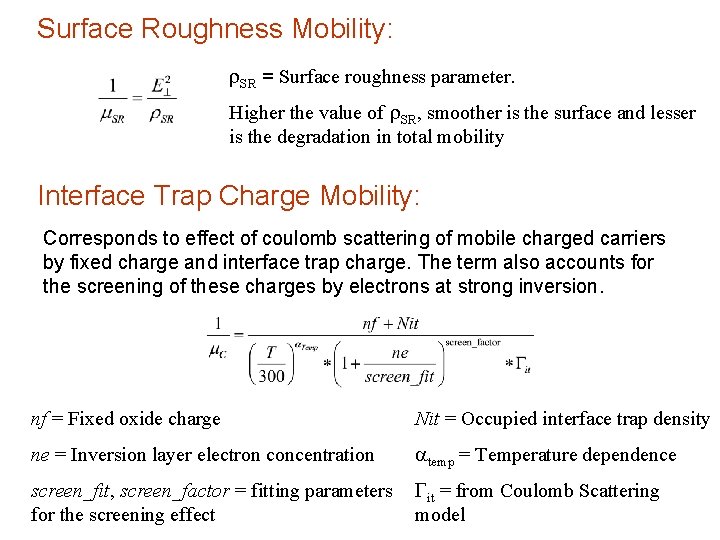

Surface Roughness Mobility: r. SR = Surface roughness parameter. Higher the value of r. SR, smoother is the surface and lesser is the degradation in total mobility Interface Trap Charge Mobility: Corresponds to effect of coulomb scattering of mobile charged carriers by fixed charge and interface trap charge. The term also accounts for the screening of these charges by electrons at strong inversion. nf = Fixed oxide charge Nit = Occupied interface trap density ne = Inversion layer electron concentration atemp = Temperature dependence screen_fit, screen_factor = fitting parameters for the screening effect Git = from Coulomb Scattering model

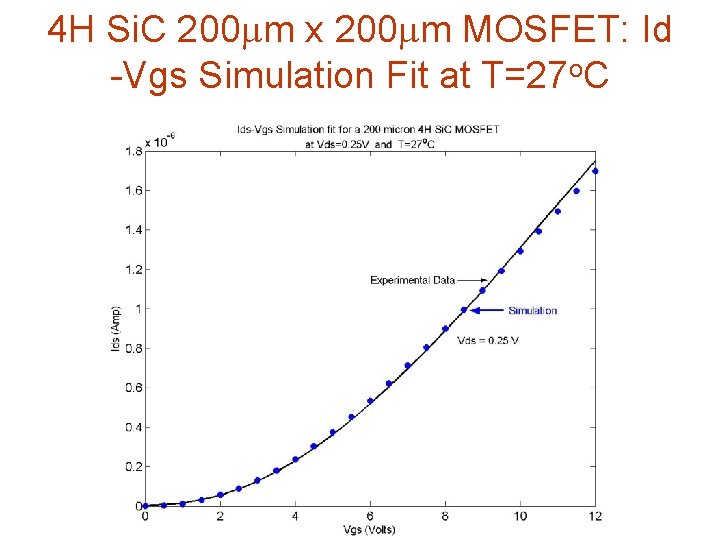

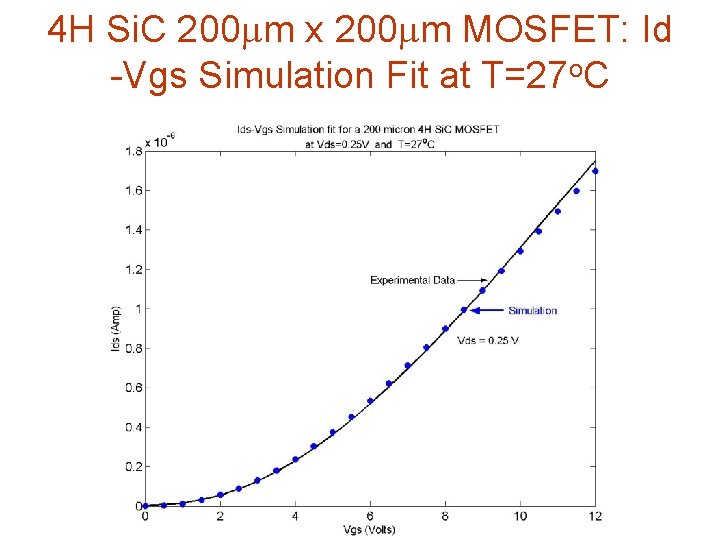

4 H Si. C 200 mm x 200 mm MOSFET: Id -Vgs Simulation Fit at T=27 o. C

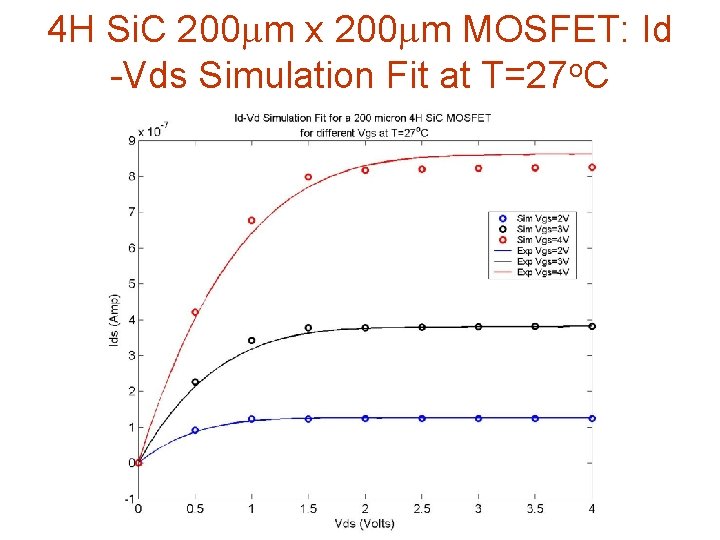

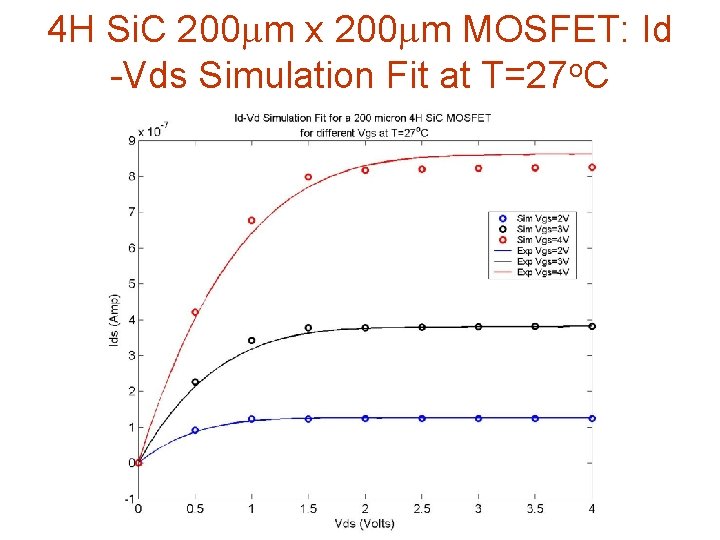

4 H Si. C 200 mm x 200 mm MOSFET: Id -Vds Simulation Fit at T=27 o. C

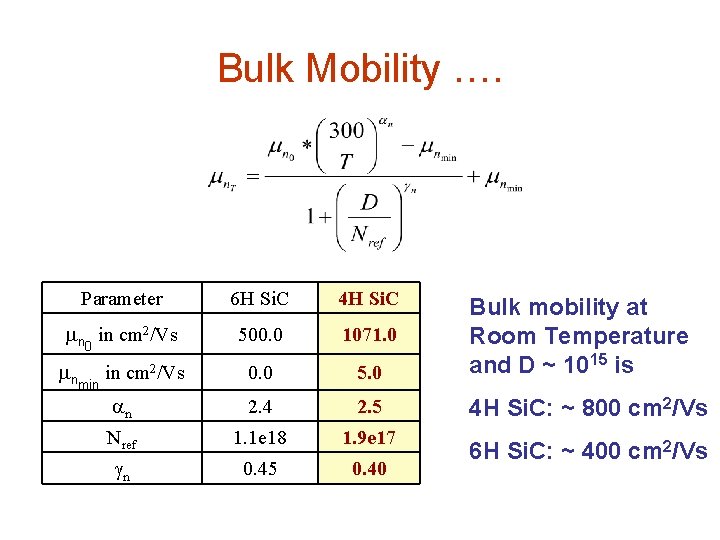

Bulk Mobility …. Parameter 6 H Si. C 4 H Si. C mn 0 in cm 2/Vs 500. 0 1071. 0 mnmin in cm 2/Vs 0. 0 5. 0 Bulk mobility at Room Temperature and D ~ 1015 is an 2. 4 2. 5 4 H Si. C: ~ 800 cm 2/Vs Nref 1. 1 e 18 1. 9 e 17 gn 0. 45 0. 40 6 H Si. C: ~ 400 cm 2/Vs

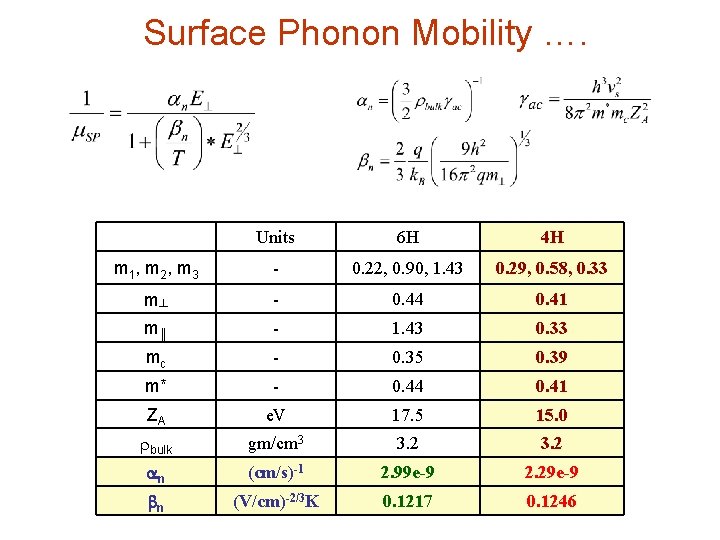

Surface Phonon Mobility …. Units 6 H 4 H m 1 , m 2 , m 3 - 0. 22, 0. 90, 1. 43 0. 29, 0. 58, 0. 33 m┴ - 0. 44 0. 41 m║ - 1. 43 0. 33 mc - 0. 35 0. 39 m* - 0. 44 0. 41 ZA e. V 17. 5 15. 0 rbulk gm/cm 3 3. 2 an (cm/s)-1 2. 99 e-9 2. 29 e-9 bn (V/cm)-2/3 K 0. 1217 0. 1246

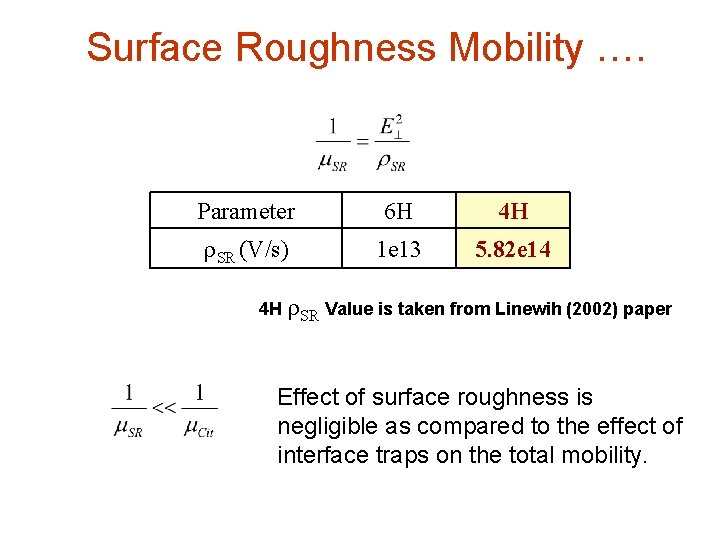

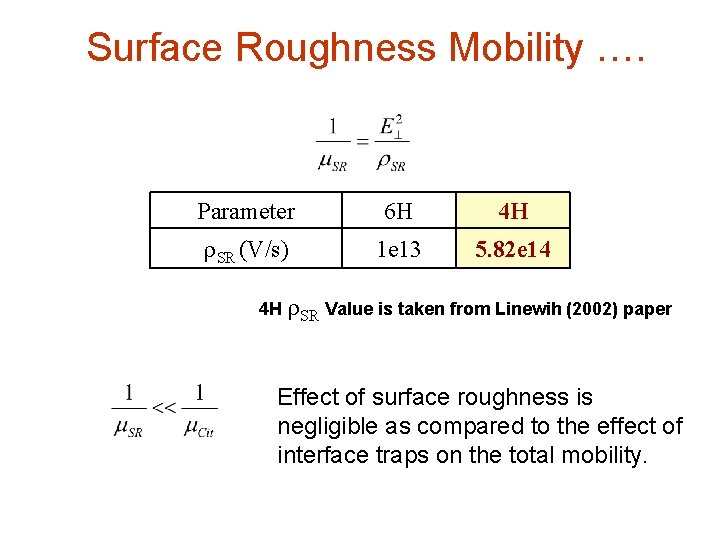

Surface Roughness Mobility …. Parameter 6 H 4 H r. SR (V/s) 1 e 13 5. 82 e 14 4 H r. SR Value is taken from Linewih (2002) paper Effect of surface roughness is negligible as compared to the effect of interface traps on the total mobility.

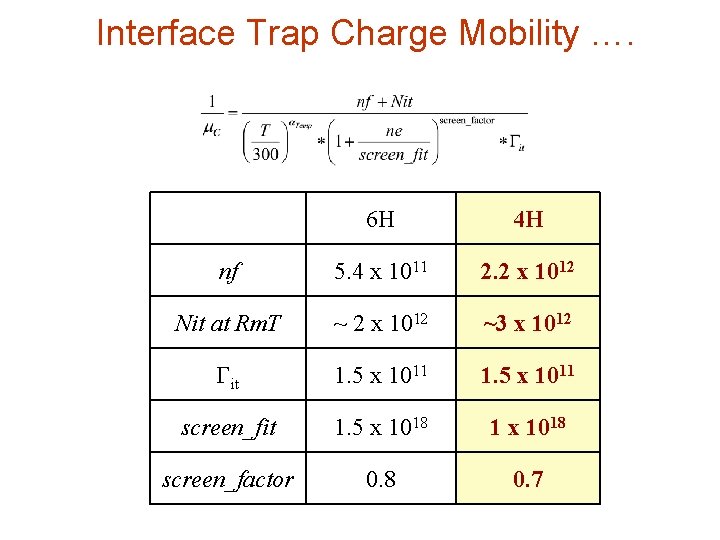

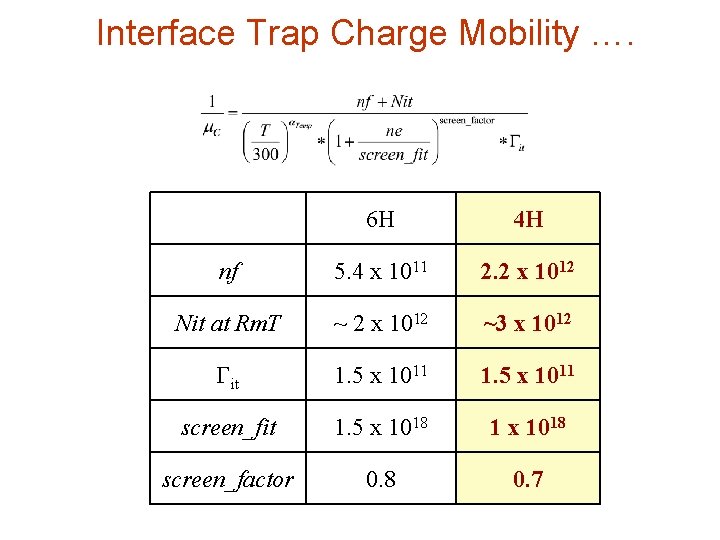

Interface Trap Charge Mobility …. 6 H 4 H nf 5. 4 x 1011 2. 2 x 1012 Nit at Rm. T ~ 2 x 1012 ~3 x 1012 Git 1. 5 x 1011 screen_fit 1. 5 x 1018 1 x 1018 screen_factor 0. 8 0. 7

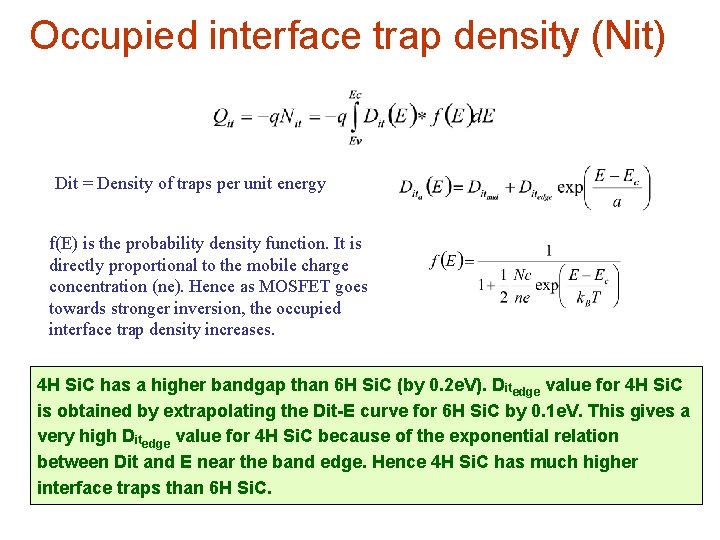

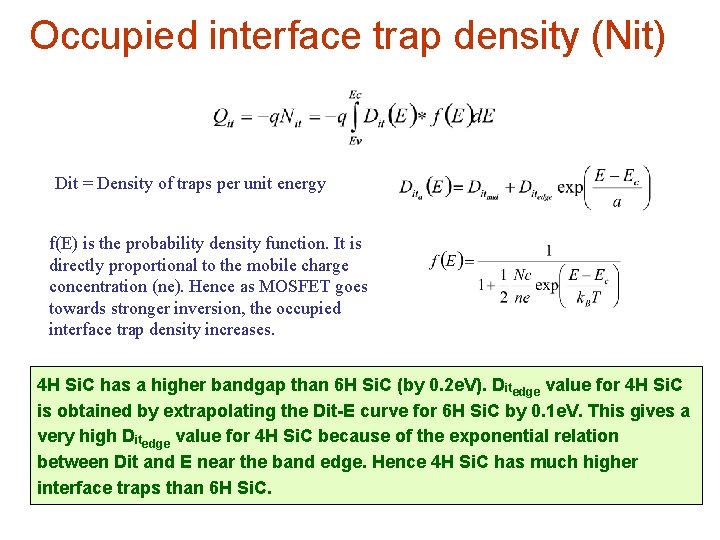

Occupied interface trap density (Nit) Dit = Density of traps per unit energy f(E) is the probability density function. It is directly proportional to the mobile charge concentration (ne). Hence as MOSFET goes towards stronger inversion, the occupied interface trap density increases. 4 H Si. C has a higher bandgap than 6 H Si. C (by 0. 2 e. V). Ditedge value for 4 H Si. C is obtained by extrapolating the Dit-E curve for 6 H Si. C by 0. 1 e. V. This gives a very high Ditedge value for 4 H Si. C because of the exponential relation between Dit and E near the band edge. Hence 4 H Si. C has much higher interface traps than 6 H Si. C.

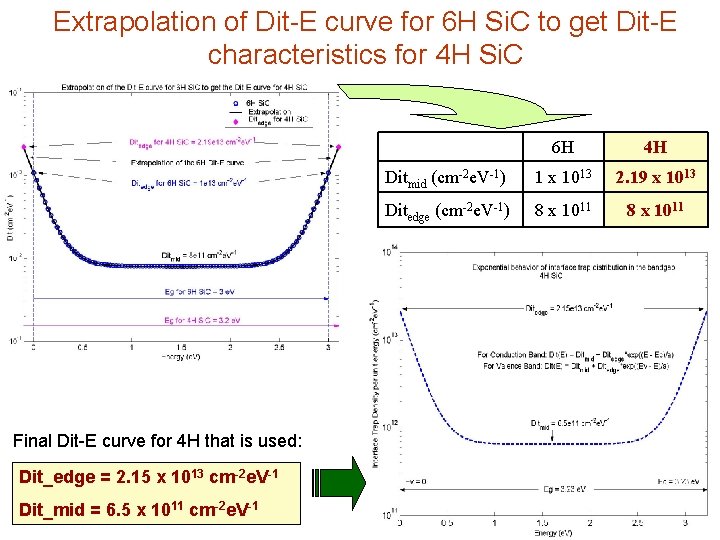

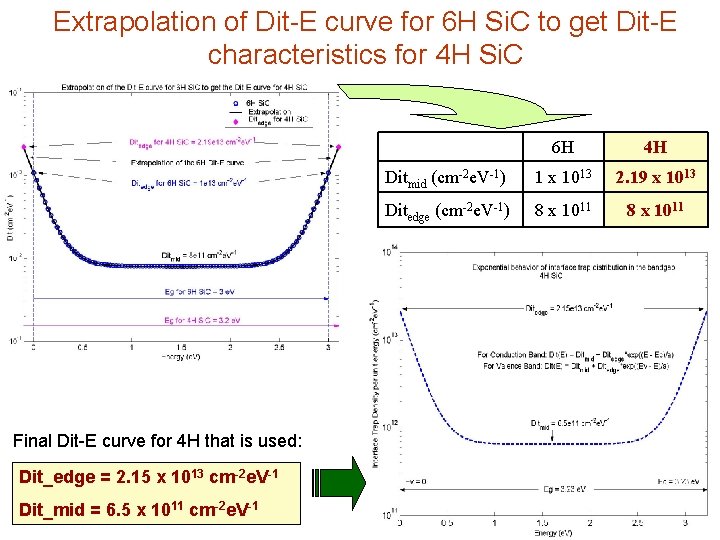

Extrapolation of Dit-E curve for 6 H Si. C to get Dit-E characteristics for 4 H Si. C Final Dit-E curve for 4 H that is used: Dit_edge = 2. 15 x 1013 cm-2 e. V-1 Dit_mid = 6. 5 x 1011 cm-2 e. V-1 6 H 4 H Ditmid (cm-2 e. V-1) 1 x 1013 2. 19 x 1013 Ditedge (cm-2 e. V-1) 8 x 1011

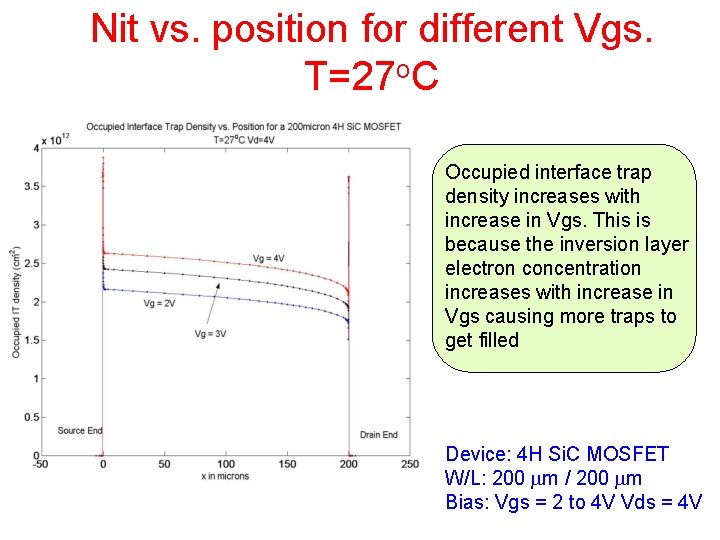

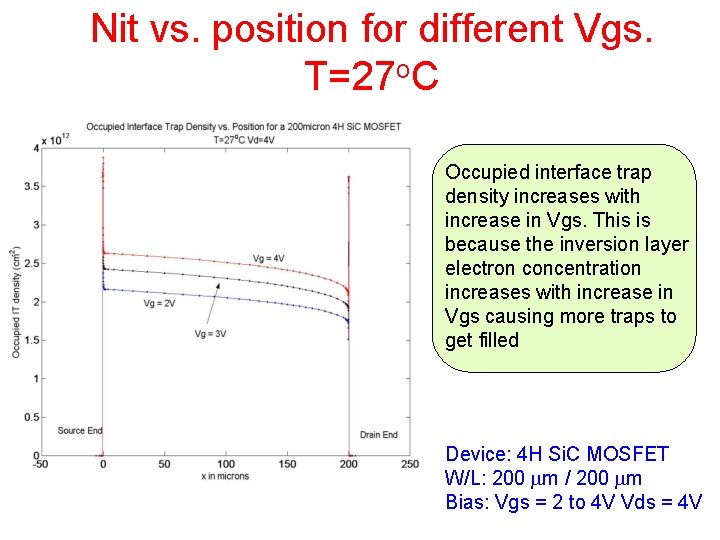

Nit vs. position for different Vgs. T=27 o. C Occupied interface trap density increases with increase in Vgs. This is because the inversion layer electron concentration increases with increase in Vgs causing more traps to get filled Device: 4 H Si. C MOSFET W/L: 200 mm / 200 mm Bias: Vgs = 2 to 4 V Vds = 4 V

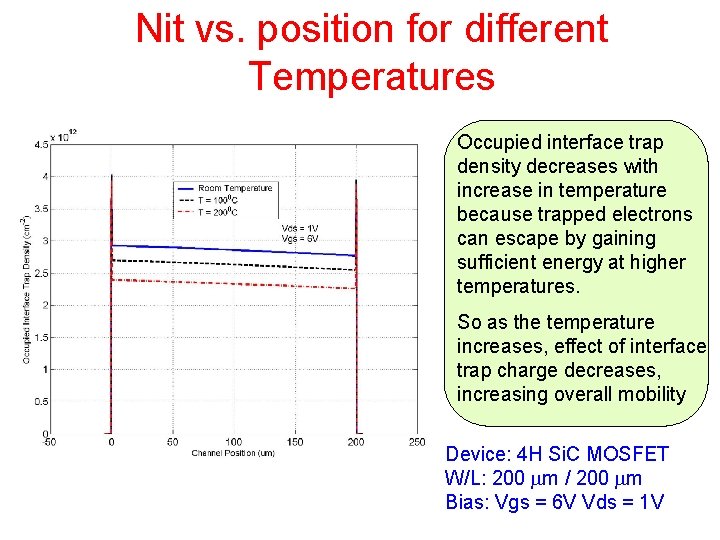

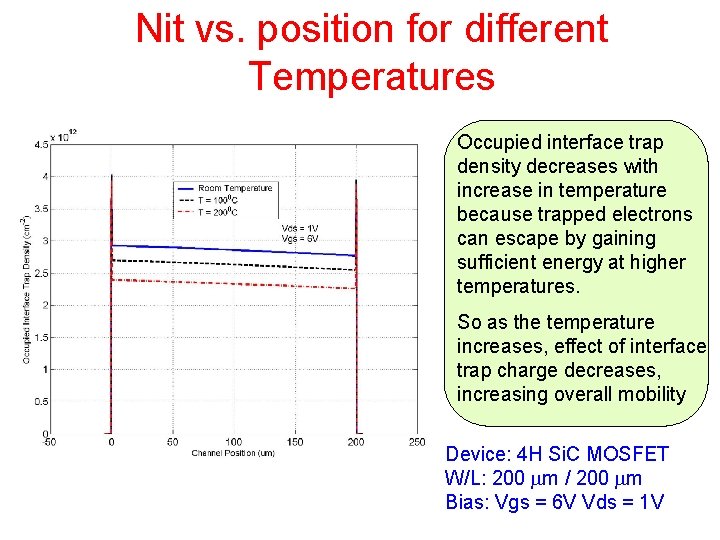

Nit vs. position for different Temperatures Occupied interface trap density decreases with increase in temperature because trapped electrons can escape by gaining sufficient energy at higher temperatures. So as the temperature increases, effect of interface trap charge decreases, increasing overall mobility Device: 4 H Si. C MOSFET W/L: 200 mm / 200 mm Bias: Vgs = 6 V Vds = 1 V

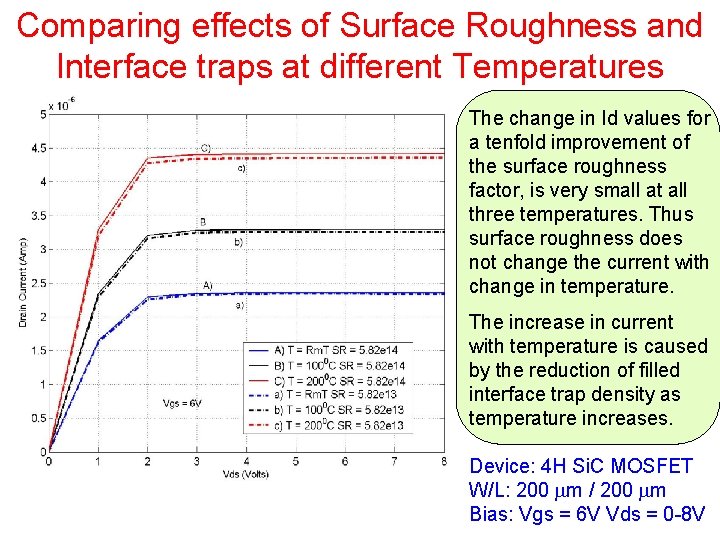

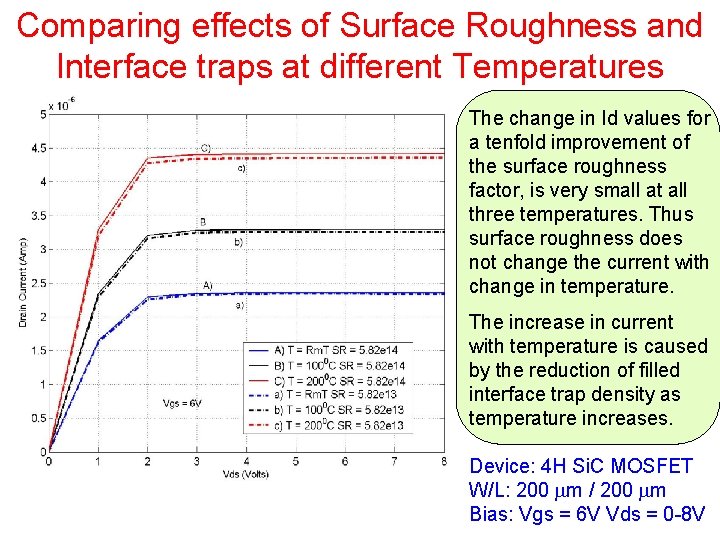

Comparing effects of Surface Roughness and Interface traps at different Temperatures The change in Id values for a tenfold improvement of the surface roughness factor, is very small at all three temperatures. Thus surface roughness does not change the current with change in temperature. The increase in current with temperature is caused by the reduction of filled interface trap density as temperature increases. Device: 4 H Si. C MOSFET W/L: 200 mm / 200 mm Bias: Vgs = 6 V Vds = 0 -8 V

Future Work… • Better screening model based on Brooks-Herring ionized impurity scattering model • Surface roughness calculation to get proper value for r. SR • Fitting data at higher temperatures • High power MOSFET simulation • Investigating gate leakage in Si. C MOSFETs • Building a Graphical User Interface for the simulator