Monolithic sensors in highvoltage deepsubmicron technology Ivan Peric

Monolithic sensors in high-voltage deep-submicron technology Ivan Peric University of Heidelberg, Germany FEE 2011, Ivan Peric 1

• • • Introduction to pixel sensors in high voltage CMOS technology Operation principle, advantages and disadvantages Summary of the project results Pixel types 1) Particle sensitive pixels with complex CMOS electronics – Test chip in 180 nm technology • 2) Integrating pixels with simple “ 4 T” electronics – 4 PMOST source follower pixels – 4 PMOST pixels with voltage amplification – >4 T CDS pixels • Test beam and lab measurements FEE 2011, Ivan Peric 2

Pixel detector in HV CMOS technology • • • Monolithic pixel sensor 100% fill-factor In-pixel CMOS signal processing Good timing properties (theoretically 40 ps signal collection time) Radiation hard (tested to 50 MRad (x-rays) and 1015 neq (protons)) Not expensive (monolithic sensor, no bumping, standard technology used) 350 nm technology: 8 inch wafer run: 90 k€ (350 nm) 180 nm technology: 120 k€ and 1. 5 k€/wafer (1 wafer ~ 200 cm 2) Allows thinning FEE 2011, Ivan Peric 3

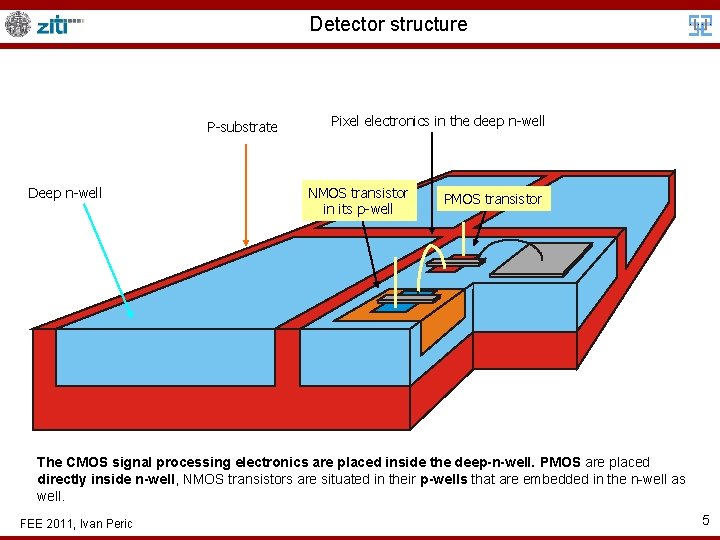

Detector structure • • The sensor is based on the “deep” n-well in a p-substrate Main properties: 1) Charge collection is based on drift 2) CMOS signal processing electronics FEE 2011, Ivan Peric 4

Detector structure P-substrate Deep n-well Pixel electronics in the deep n-well NMOS transistor in its p-well PMOS transistor The CMOS signal processing electronics are placed inside the deep-n-well. PMOS are placed directly inside n-well, NMOS transistors are situated in their p-wells that are embedded in the n-well as well. FEE 2011, Ivan Peric 5

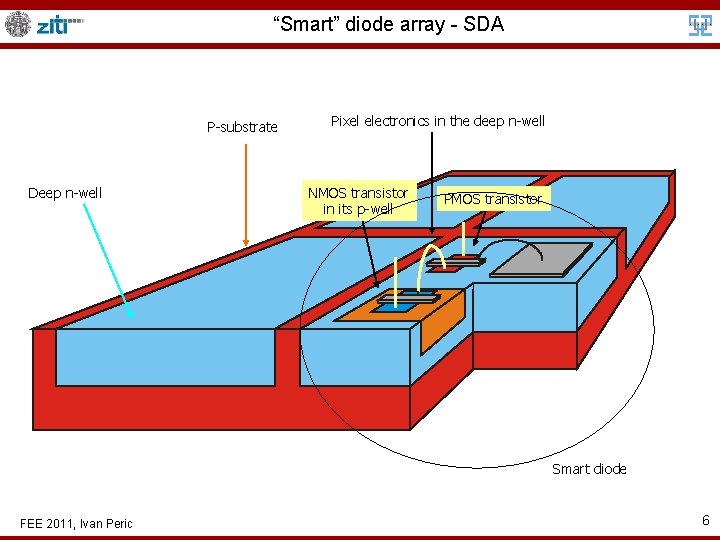

“Smart” diode array - SDA P-substrate Deep n-well Pixel electronics in the deep n-well NMOS transistor in its p-well PMOS transistor Smart diode FEE 2011, Ivan Peric 6

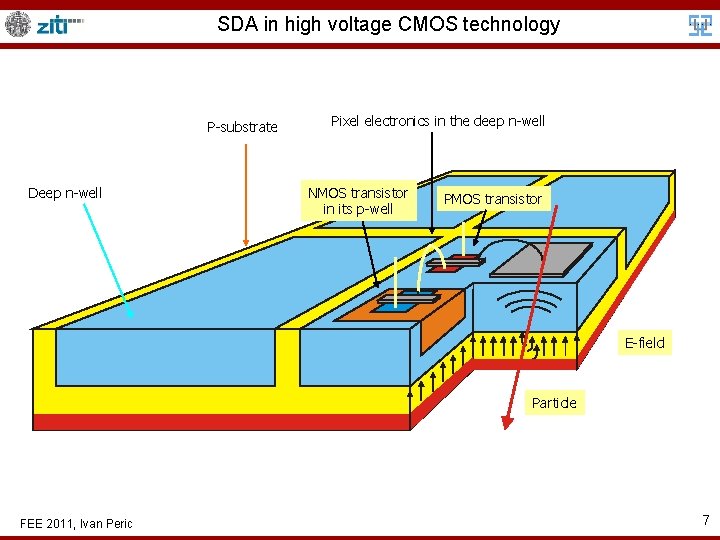

SDA in high voltage CMOS technology P-substrate Deep n-well Pixel electronics in the deep n-well NMOS transistor in its p-well PMOS transistor E-field Particle FEE 2011, Ivan Peric 7

SDA in high voltage CMOS technology • • • Although this structure can be implemented in any CMOS technology (see 65 nm pixel), the best results are achieved when a standard high voltage CMOS technology with twin well is used. A lowly-doped deep n-well can be then used. Such an n-well can be reversely biased with a high voltage. In the process we used, we expect a depleted area thickness of 14 μm (20 cm substrate resistance -> acceptor density ~ 1015 cm-3) We measure a MIP signal of ~ 2000 e, ~ 50% probably originates from undepleted bulk. The charge generated by ionizing particles in the depleted area is collected by drift. Due to high electric field and small drift path, charge collection is very fast. We estimate ~ 40 ps. Due to drift based charge collection we have high radiation tolerance FEE 2011, Ivan Peric 8

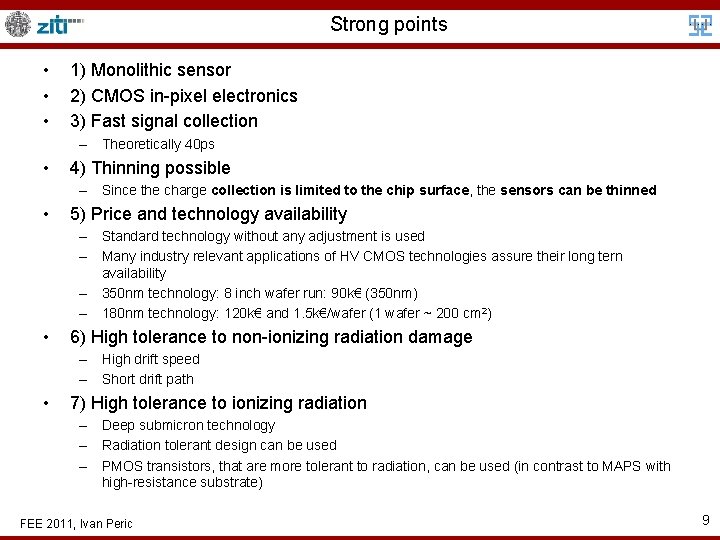

Strong points • • • 1) Monolithic sensor 2) CMOS in-pixel electronics 3) Fast signal collection – Theoretically 40 ps • 4) Thinning possible – Since the charge collection is limited to the chip surface, the sensors can be thinned • 5) Price and technology availability – Standard technology without any adjustment is used – Many industry relevant applications of HV CMOS technologies assure their long tern availability – 350 nm technology: 8 inch wafer run: 90 k€ (350 nm) – 180 nm technology: 120 k€ and 1. 5 k€/wafer (1 wafer ~ 200 cm 2) • 6) High tolerance to non-ionizing radiation damage – High drift speed – Short drift path • 7) High tolerance to ionizing radiation – Deep submicron technology – Radiation tolerant design can be used – PMOS transistors, that are more tolerant to radiation, can be used (in contrast to MAPS with high-resistance substrate) FEE 2011, Ivan Peric 9

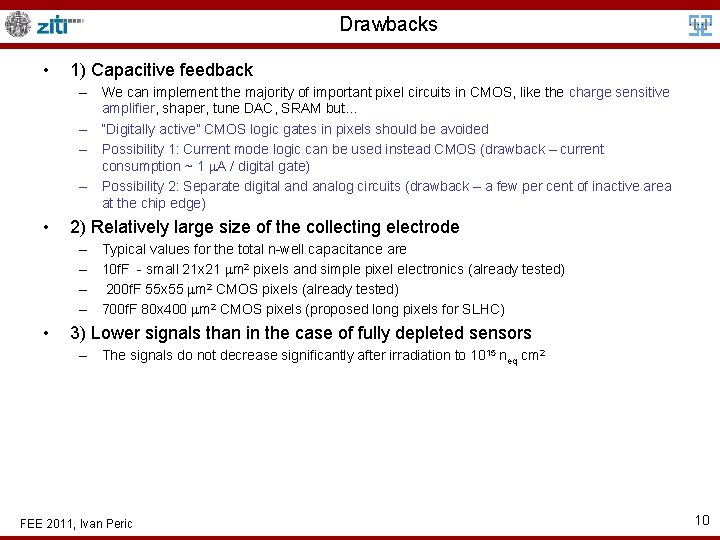

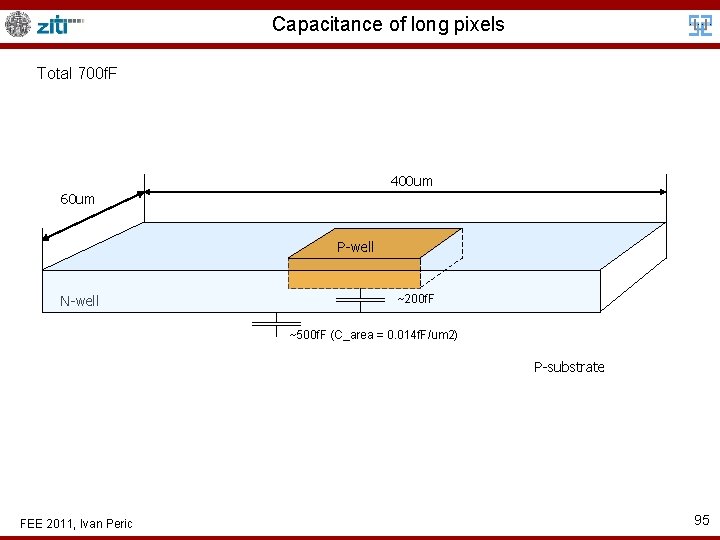

Drawbacks • 1) Capacitive feedback – We can implement the majority of important pixel circuits in CMOS, like the charge sensitive amplifier, shaper, tune DAC, SRAM but… – “Digitally active” CMOS logic gates in pixels should be avoided – Possibility 1: Current mode logic can be used instead CMOS (drawback – current consumption ~ 1 A / digital gate) – Possibility 2: Separate digital and analog circuits (drawback – a few per cent of inactive area at the chip edge) • 2) Relatively large size of the collecting electrode – Typical values for the total n-well capacitance are – 10 f. F - small 21 x 21 m 2 pixels and simple pixel electronics (already tested) – 200 f. F 55 x 55 m 2 CMOS pixels (already tested) – 700 f. F 80 x 400 m 2 CMOS pixels (proposed long pixels for SLHC) • 3) Lower signals than in the case of fully depleted sensors – The signals do not decrease significantly after irradiation to 1015 neq cm 2 FEE 2011, Ivan Peric 10

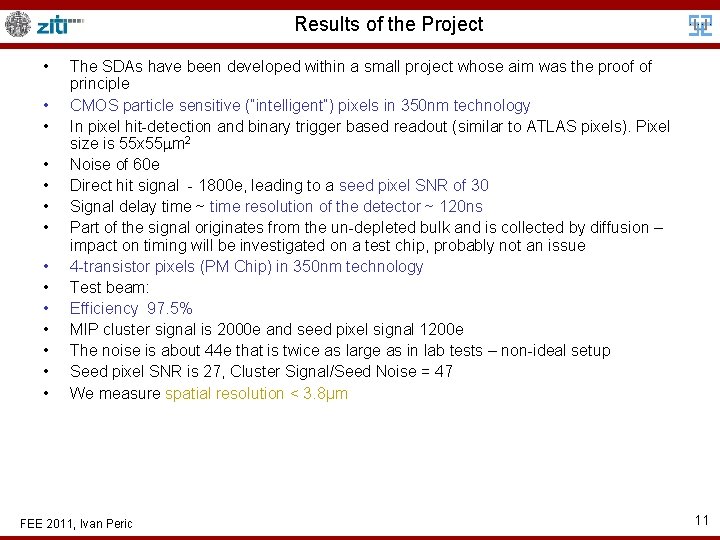

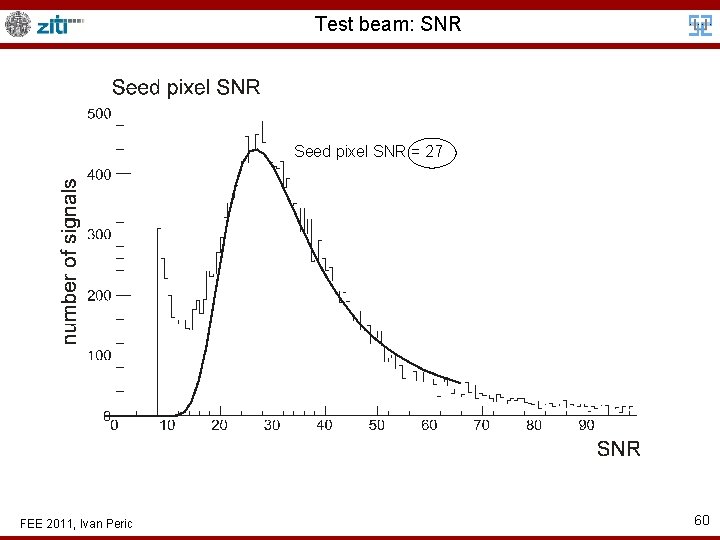

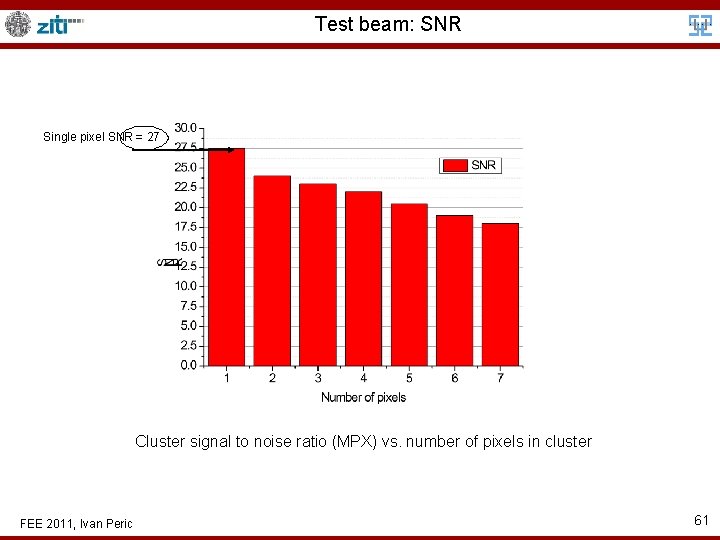

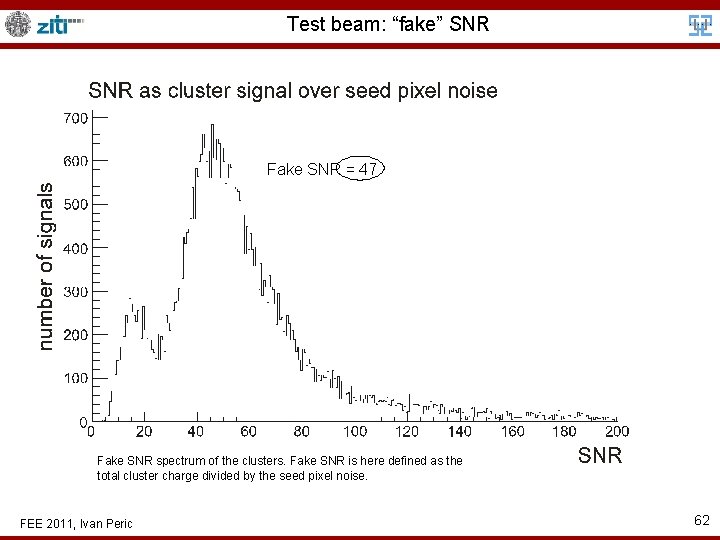

Results of the Project • • • • The SDAs have been developed within a small project whose aim was the proof of principle CMOS particle sensitive (“intelligent”) pixels in 350 nm technology In pixel hit-detection and binary trigger based readout (similar to ATLAS pixels). Pixel size is 55 x 55 m 2 Noise of 60 e Direct hit signal - 1800 e, leading to a seed pixel SNR of 30 Signal delay time ~ time resolution of the detector ~ 120 ns Part of the signal originates from the un-depleted bulk and is collected by diffusion – impact on timing will be investigated on a test chip, probably not an issue 4 -transistor pixels (PM Chip) in 350 nm technology Test beam: Efficiency 97. 5% MIP cluster signal is 2000 e and seed pixel signal 1200 e The noise is about 44 e that is twice as large as in lab tests – non-ideal setup Seed pixel SNR is 27, Cluster Signal/Seed Noise = 47 We measure spatial resolution < 3. 8μm FEE 2011, Ivan Peric 11

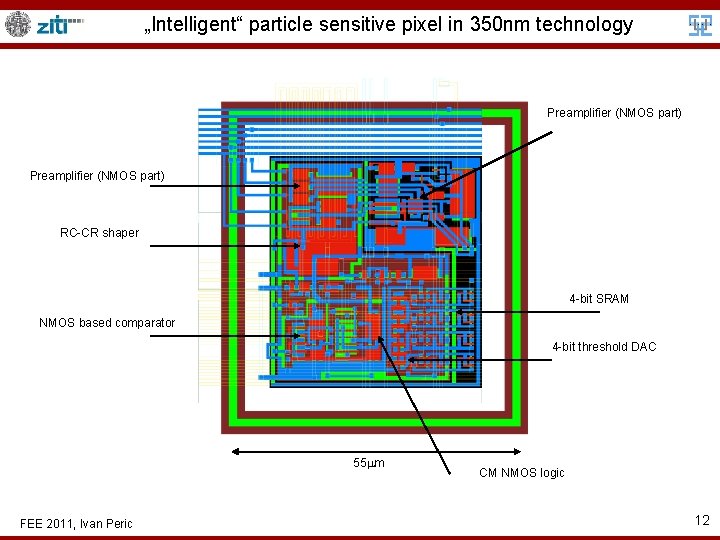

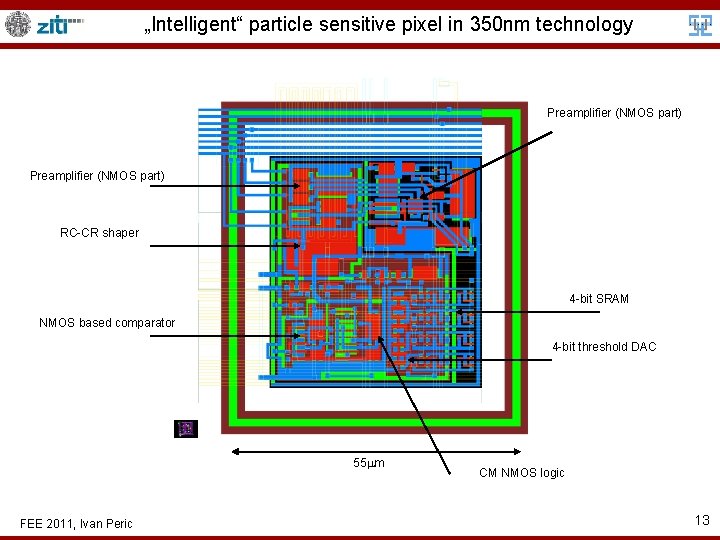

„Intelligent“ particle sensitive pixel in 350 nm technology Preamplifier (NMOS part) RC-CR shaper 4 -bit SRAM NMOS based comparator 4 -bit threshold DAC 55 m FEE 2011, Ivan Peric CM NMOS logic 12

„Intelligent“ particle sensitive pixel in 350 nm technology Preamplifier (NMOS part) RC-CR shaper 4 -bit SRAM NMOS based comparator 4 -bit threshold DAC 55 m FEE 2011, Ivan Peric CM NMOS logic 13

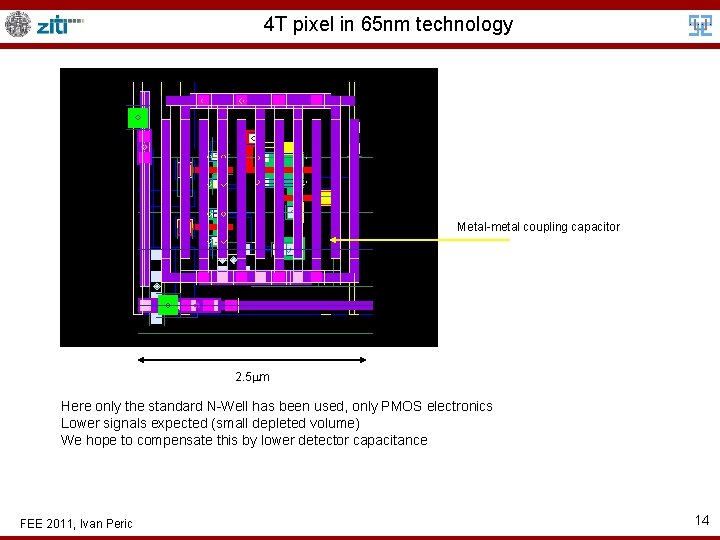

4 T pixel in 65 nm technology Metal-metal coupling capacitor 2. 5 m Here only the standard N-Well has been used, only PMOS electronics Lower signals expected (small depleted volume) We hope to compensate this by lower detector capacitance FEE 2011, Ivan Peric 14

Radiation tolerance • In order to test the radiation tolerance we have performed a few irradiations FEE 2011, Ivan Peric 15

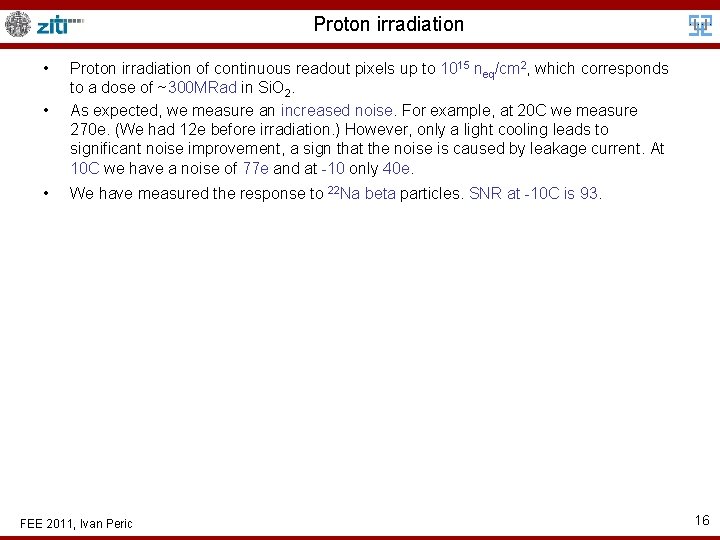

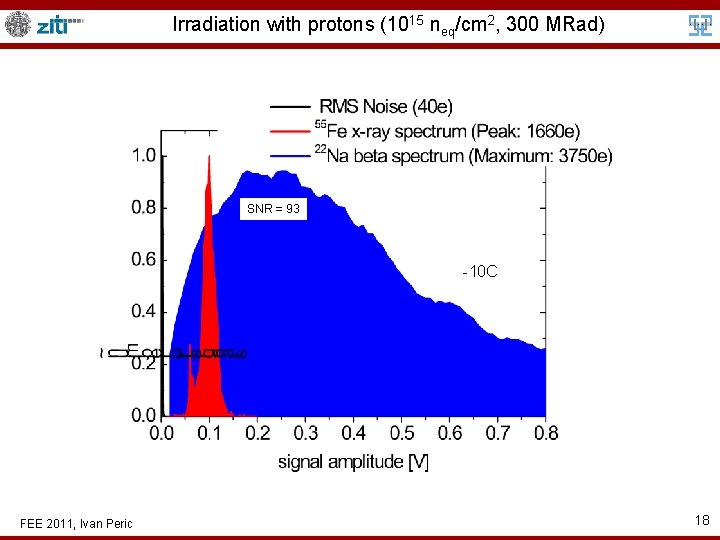

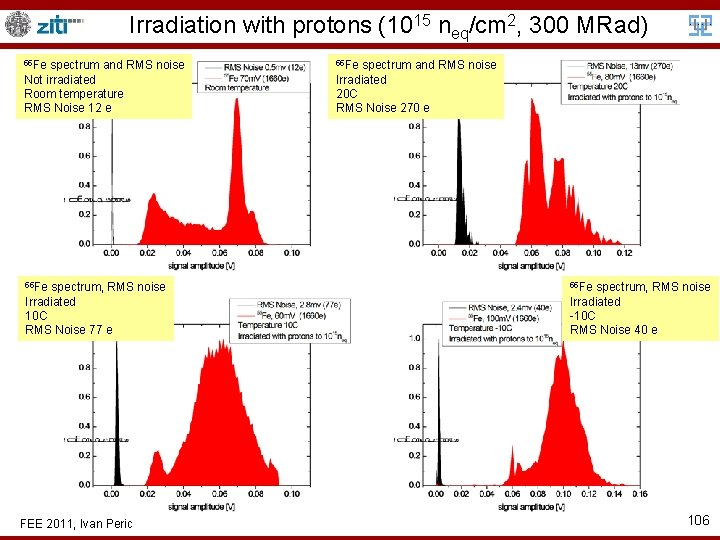

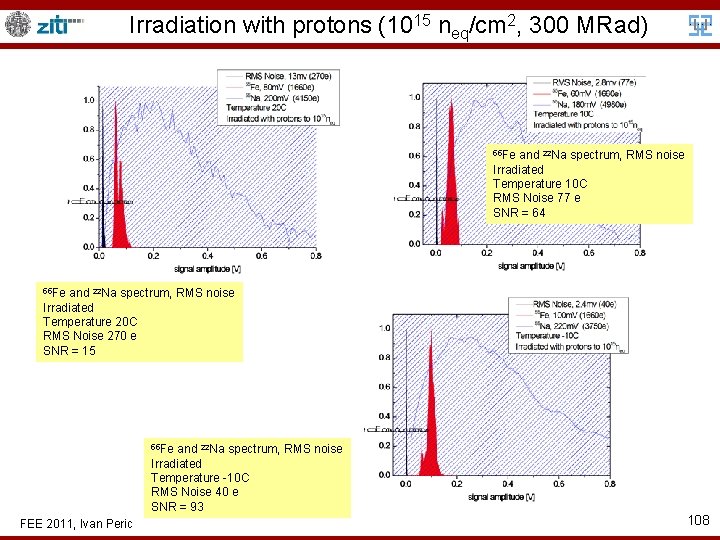

Proton irradiation • • Proton irradiation of continuous readout pixels up to 1015 neq/cm 2, which corresponds to a dose of ~300 MRad in Si. O 2. As expected, we measure an increased noise. For example, at 20 C we measure 270 e. (We had 12 e before irradiation. ) However, only a light cooling leads to significant noise improvement, a sign that the noise is caused by leakage current. At 10 C we have a noise of 77 e and at -10 only 40 e. • We have measured the response to 22 Na beta particles. SNR at -10 C is 93. FEE 2011, Ivan Peric 16

Irradiation with protons (1015 neq/cm 2, 300 MRad) 55 Fe spectrum and RMS noise Not irradiated Room temperature RMS Noise 12 e FEE 2011, Ivan Peric spectrum, RMS noise Irradiated 10 C RMS Noise 77 e 17

Irradiation with protons (1015 neq/cm 2, 300 MRad) SNR = 93 -10 C FEE 2011, Ivan Peric 18

Particle sensitive pixels with CMOS electronics and continuous readout FEE 2011, Ivan Peric 19

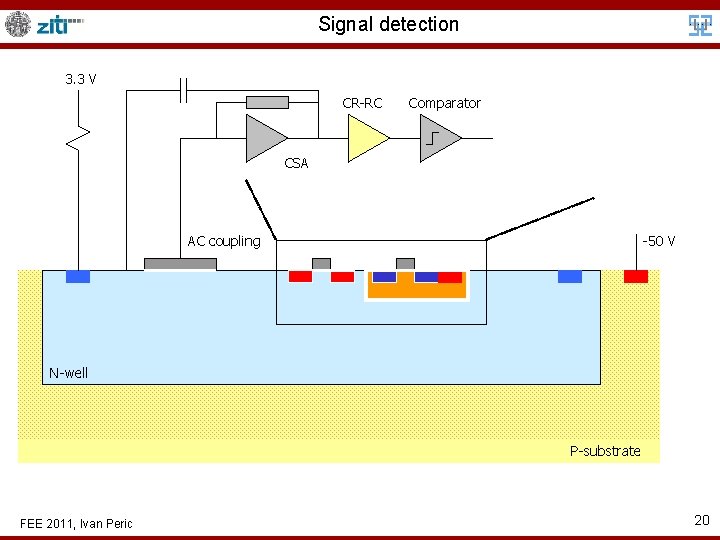

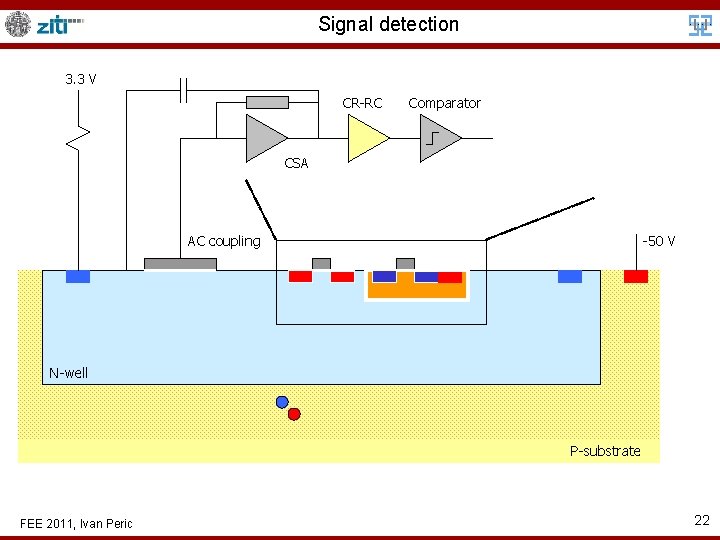

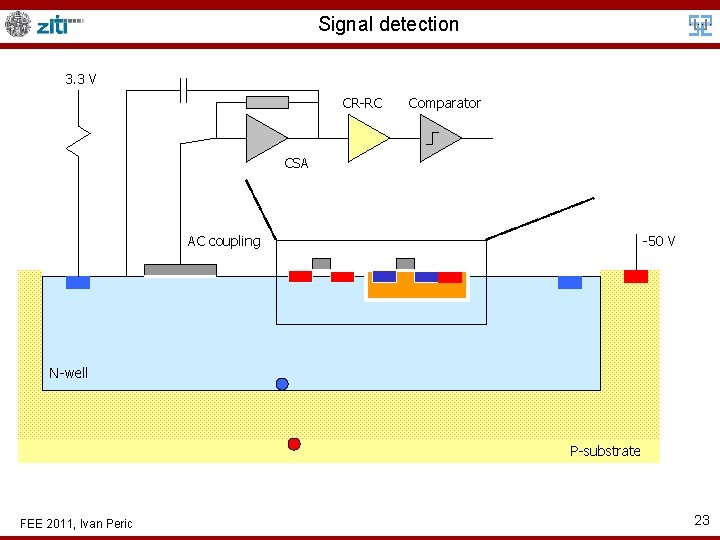

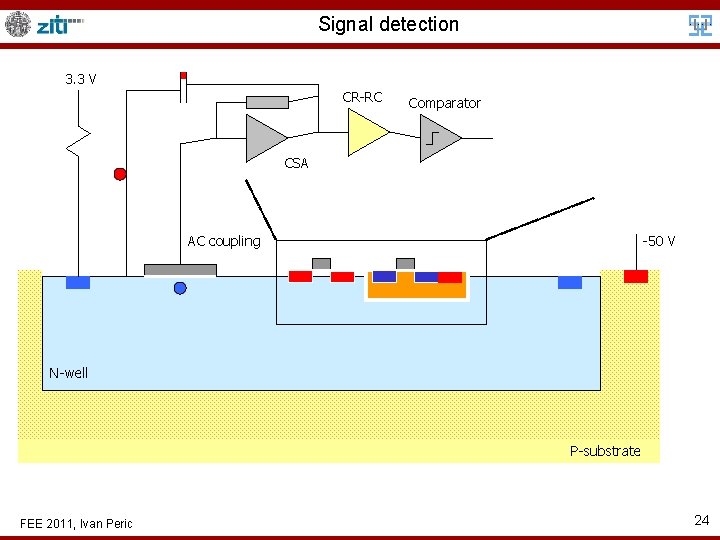

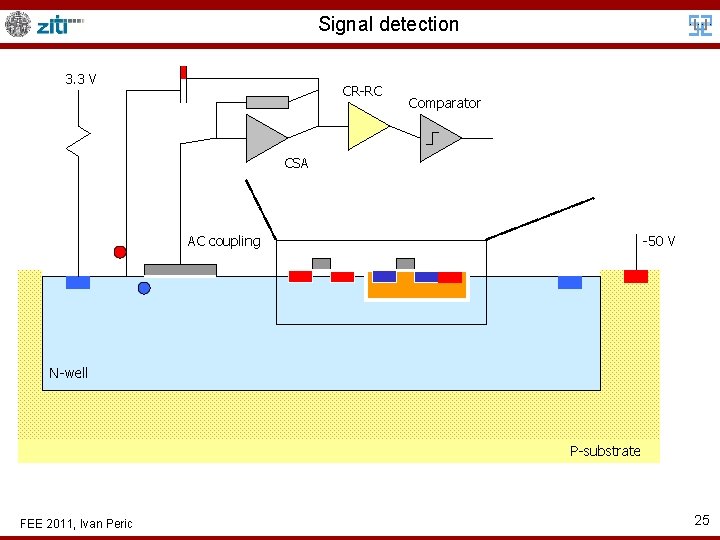

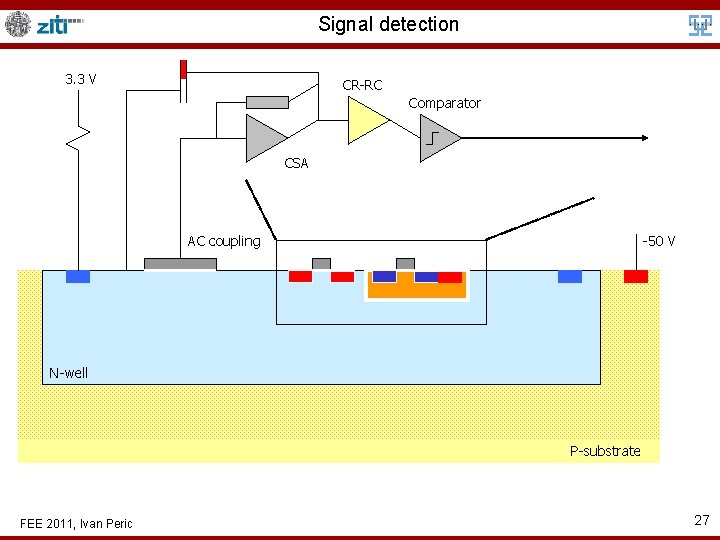

Signal detection 3. 3 V CR-RC Comparator CSA AC coupling -50 V N-well P-substrate FEE 2011, Ivan Peric 20

Signal detection 3. 3 V CR-RC Comparator CSA AC coupling -50 V N-well P-substrate FEE 2011, Ivan Peric 21

Signal detection 3. 3 V CR-RC Comparator CSA AC coupling -50 V N-well P-substrate FEE 2011, Ivan Peric 22

Signal detection 3. 3 V CR-RC Comparator CSA AC coupling -50 V N-well P-substrate FEE 2011, Ivan Peric 23

Signal detection 3. 3 V CR-RC Comparator CSA AC coupling -50 V N-well P-substrate FEE 2011, Ivan Peric 24

Signal detection 3. 3 V CR-RC Comparator CSA AC coupling -50 V N-well P-substrate FEE 2011, Ivan Peric 25

Signal detection 3. 3 V CR-RC Comparator CSA AC coupling -50 V N-well P-substrate FEE 2011, Ivan Peric 26

Signal detection 3. 3 V CR-RC Comparator CSA AC coupling -50 V N-well P-substrate FEE 2011, Ivan Peric 27

Intelligent particle sensitive pixels – possible application • • Vertex detector for the novel experiment. Goal: search for lepton flavor violating decay -> eee Four layers of pixels ~ 80 x 80 m 2 size Continuous muon beam stopped at target – 109 muon stops/s –> requires time stamping with ~ 100 ns resolution Energy range of interest: 15 -50 Me. V –> multiple scattering dominates momentum measurement –> ~50 m thin detector FEE 2011, Ivan Peric 28

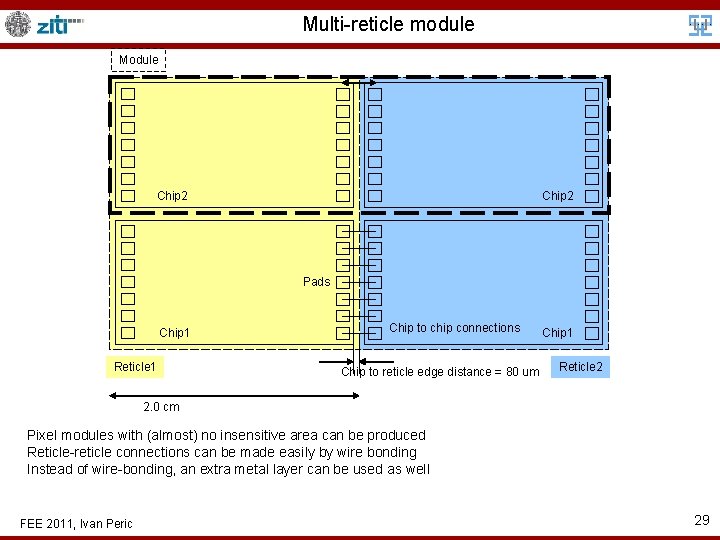

Multi-reticle module Module Chip 2 Pads Chip 1 Reticle 1 Chip to chip connections Chip to reticle edge distance = 80 um Chip 1 Reticle 2 2. 0 cm Pixel modules with (almost) no insensitive area can be produced Reticle-reticle connections can be made easily by wire bonding Instead of wire-bonding, an extra metal layer can be used as well FEE 2011, Ivan Peric 29

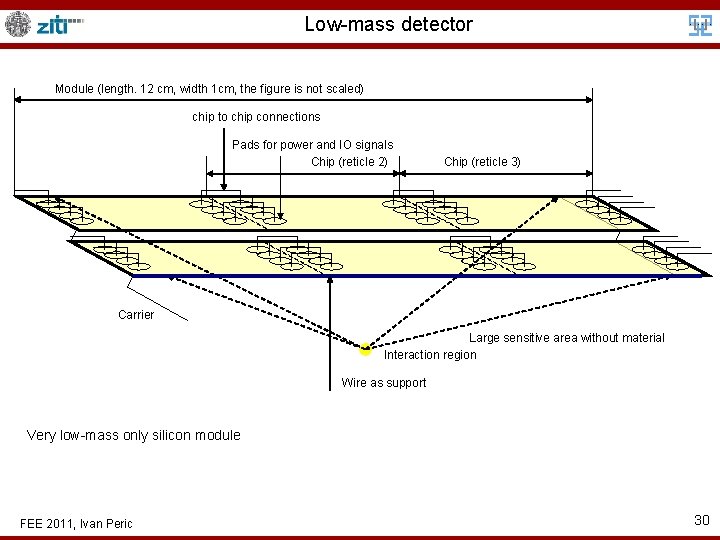

Low-mass detector Module (length. 12 cm, width 1 cm, the figure is not scaled) chip to chip connections Pads for power and IO signals Chip (reticle 2) Chip (reticle 3) Carrier Large sensitive area without material Interaction region Wire as support Very low-mass only silicon module FEE 2011, Ivan Peric 30

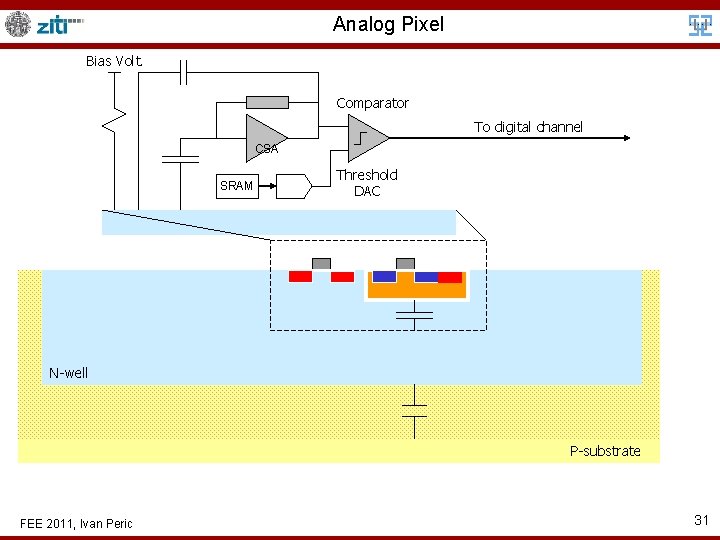

Analog Pixel Bias Volt. Comparator To digital channel CSA SRAM Threshold DAC N-well P-substrate FEE 2011, Ivan Peric 31

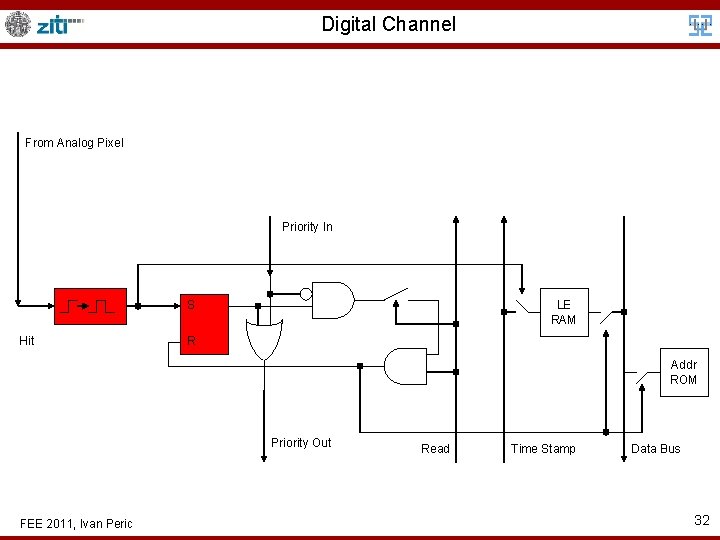

Digital Channel From Analog Pixel Priority In S Hit LE RAM R Addr ROM Priority Out FEE 2011, Ivan Peric Read Time Stamp Data Bus 32

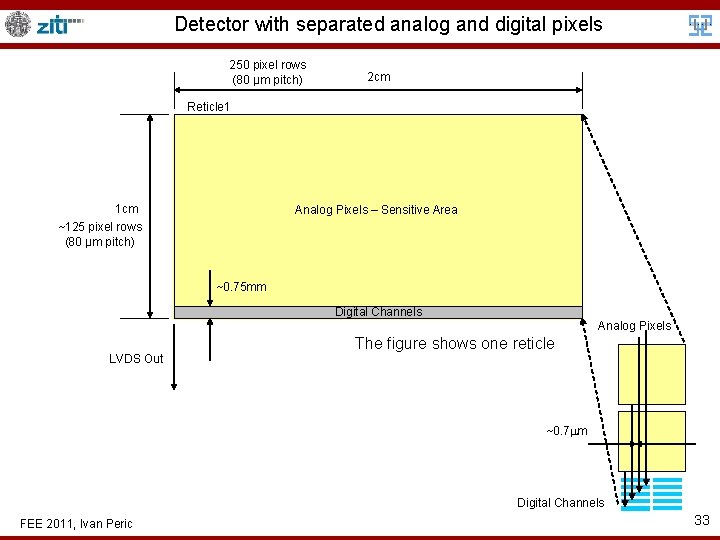

Detector with separated analog and digital pixels 250 pixel rows (80 μm pitch) 2 cm Reticle 1 1 cm ~125 pixel rows (80 μm pitch) Analog Pixels – Sensitive Area ~0. 75 mm Digital Channels LVDS Out Analog Pixels The figure shows one reticle ~0. 7 m Digital Channels FEE 2011, Ivan Peric 33

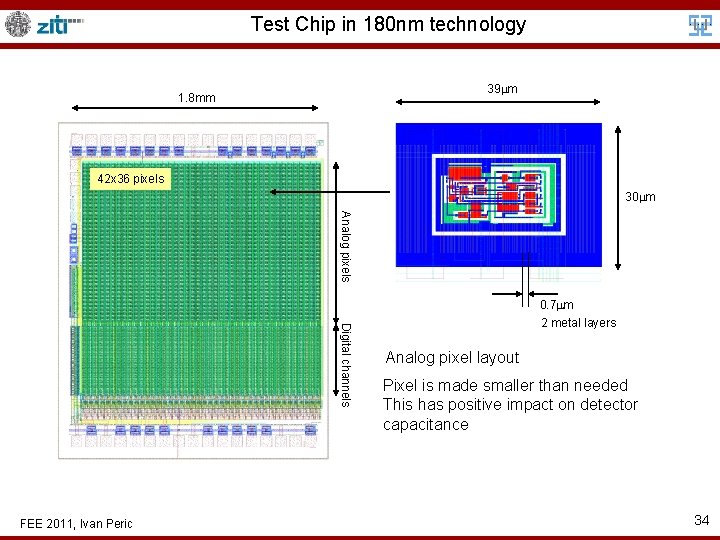

Test Chip in 180 nm technology 39 m 1. 8 mm 42 x 36 pixels 30 m Analog pixels Digital channels FEE 2011, Ivan Peric 0. 7 m 2 metal layers Analog pixel layout Pixel is made smaller than needed This has positive impact on detector capacitance 34

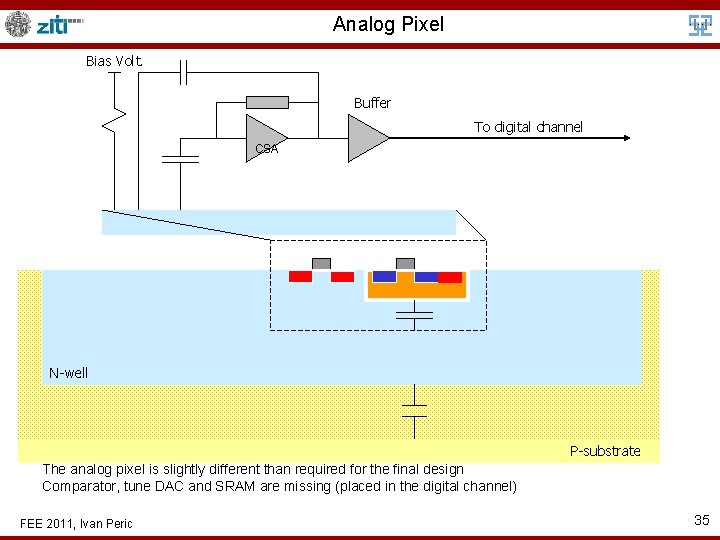

Analog Pixel Bias Volt. Buffer To digital channel CSA N-well P-substrate The analog pixel is slightly different than required for the final design Comparator, tune DAC and SRAM are missing (placed in the digital channel) FEE 2011, Ivan Peric 35

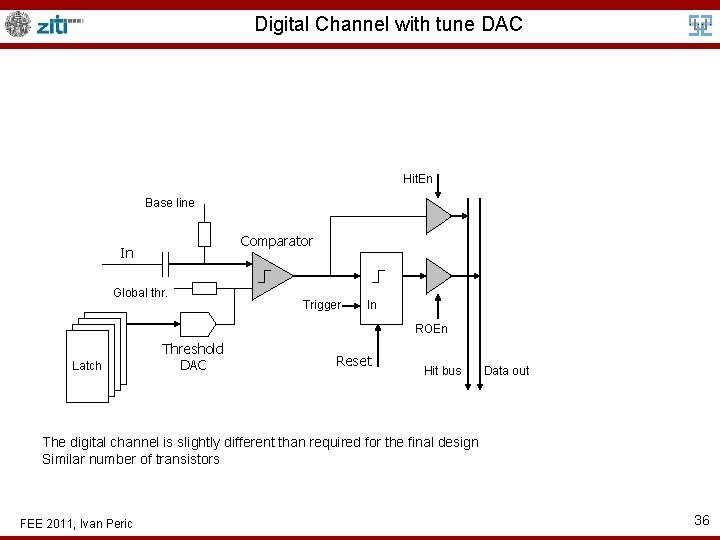

Digital Channel with tune DAC Hit. En Base line Comparator In Global thr. Trigger In ROEn Latch Threshold DAC Reset Hit bus Data out The digital channel is slightly different than required for the final design Similar number of transistors FEE 2011, Ivan Peric 36

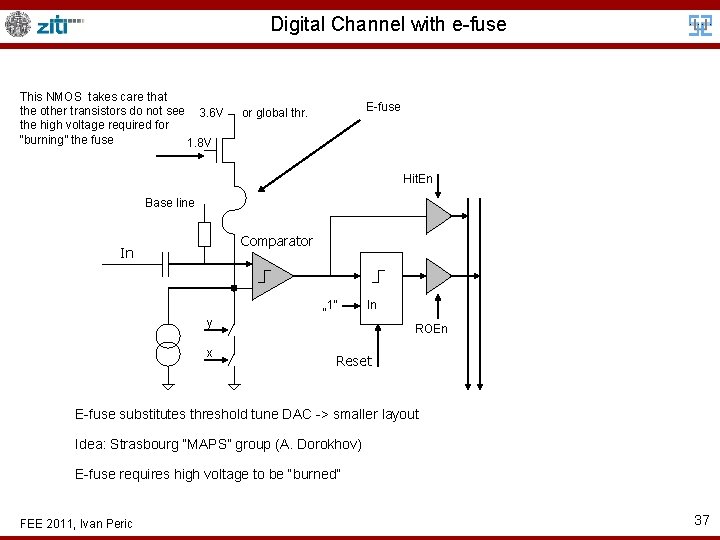

Digital Channel with e-fuse This NMOS takes care that the other transistors do not see 3. 6 V the high voltage required for “burning” the fuse 1. 8 V E-fuse or global thr. Hit. En Base line Comparator In „ 1“ In y x ROEn Reset E-fuse substitutes threshold tune DAC -> smaller layout Idea: Strasbourg “MAPS” group (A. Dorokhov) E-fuse requires high voltage to be “burned” FEE 2011, Ivan Peric 37

Digital Channels Fuse-“addressing“ transistors 39 m DAC 12 m Latches FEE 2011, Ivan Peric 38

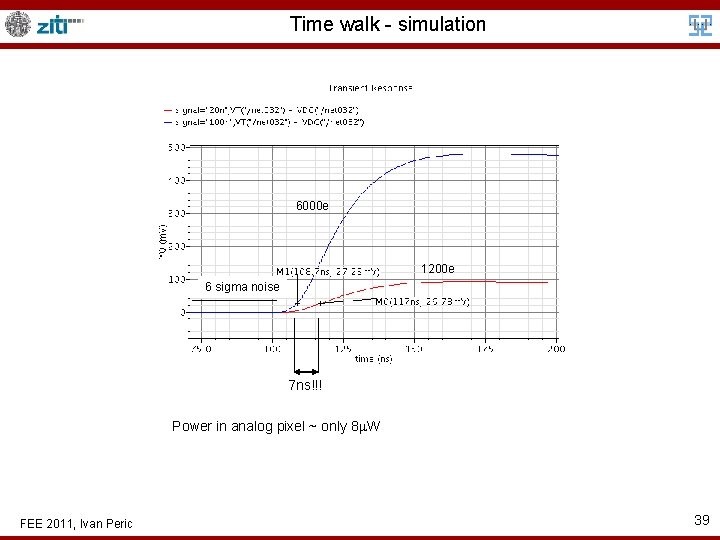

Time walk - simulation 6000 e 1200 e 6 sigma noise 7 ns!!! Power in analog pixel ~ only 8 W FEE 2011, Ivan Peric 39

Integrating pixels FEE 2011, Ivan Peric 40

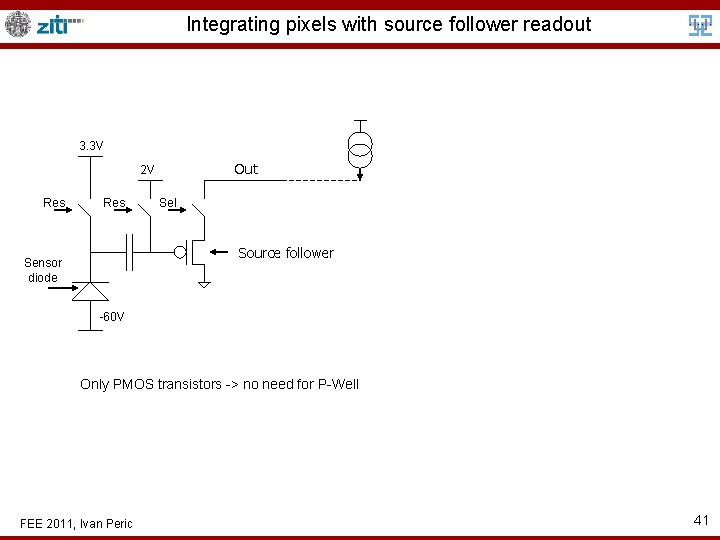

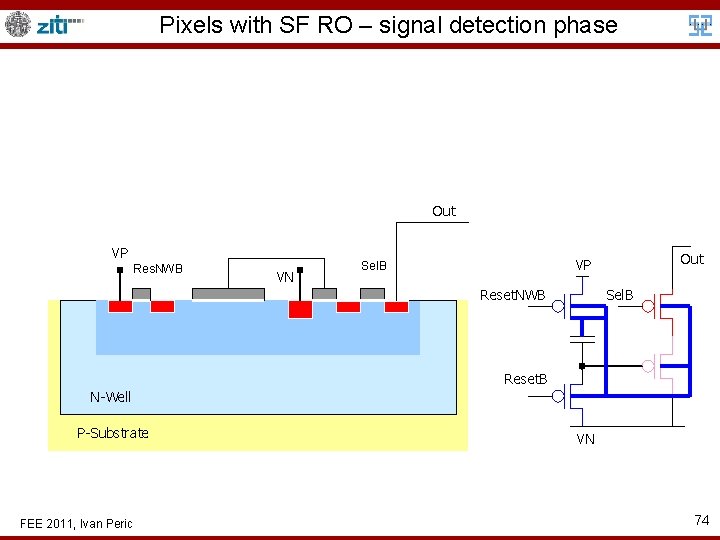

Integrating pixels with source follower readout 3. 3 V Out 2 V Res Sel Source follower Sensor diode -60 V Only PMOS transistors -> no need for P-Well FEE 2011, Ivan Peric 41

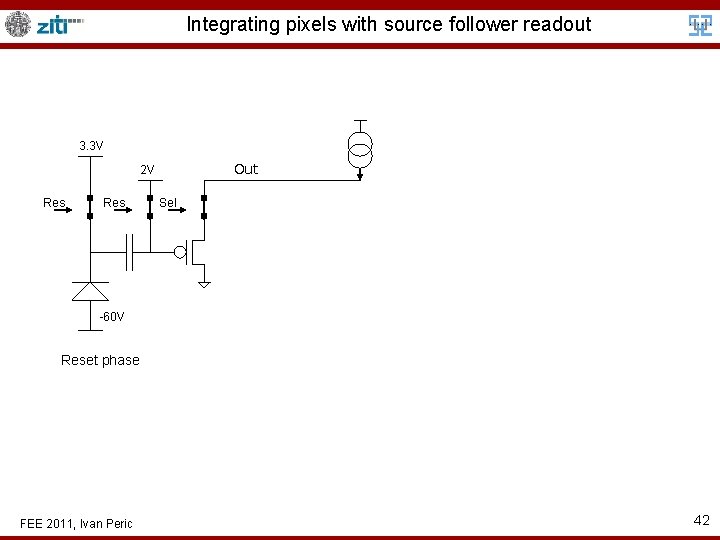

Integrating pixels with source follower readout 3. 3 V Out 2 V Res Sel -60 V Reset phase FEE 2011, Ivan Peric 42

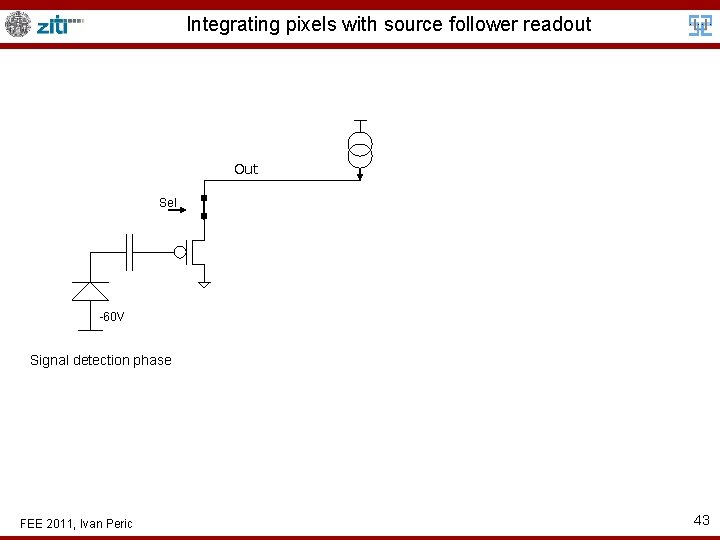

Integrating pixels with source follower readout Out Sel -60 V Signal detection phase FEE 2011, Ivan Peric 43

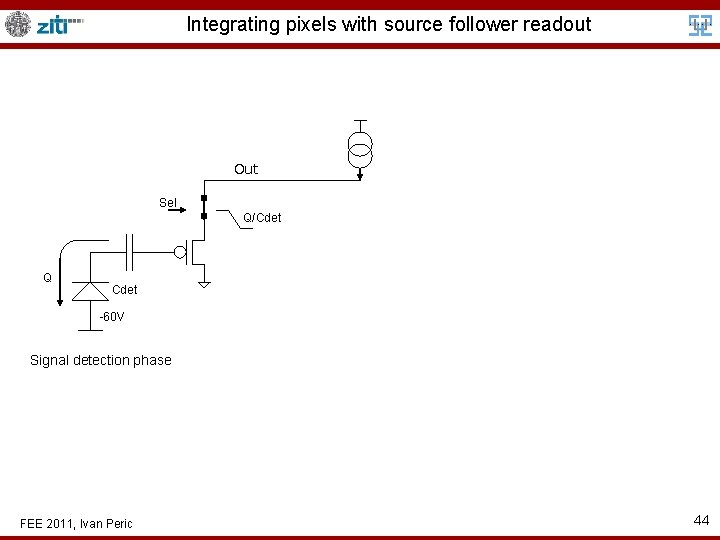

Integrating pixels with source follower readout Out Sel Q/Cdet Q Cdet -60 V Signal detection phase FEE 2011, Ivan Peric 44

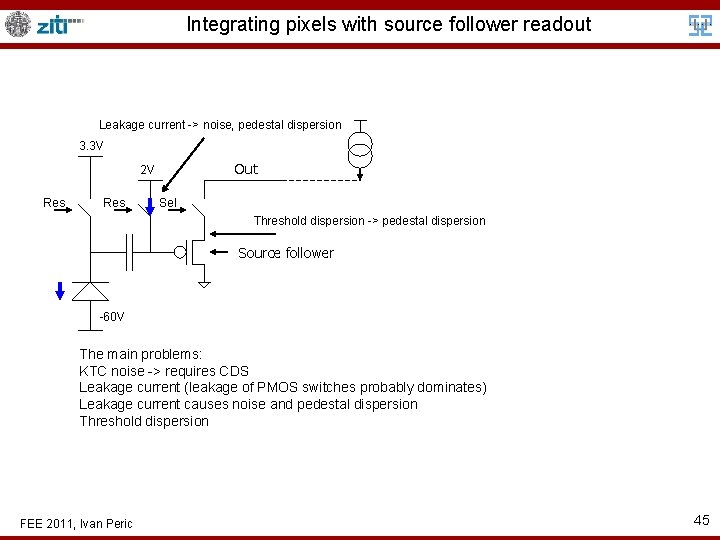

Integrating pixels with source follower readout Leakage current -> noise, pedestal dispersion 3. 3 V Out 2 V Res Sel Threshold dispersion -> pedestal dispersion Source follower -60 V The main problems: KTC noise -> requires CDS Leakage current (leakage of PMOS switches probably dominates) Leakage current causes noise and pedestal dispersion Threshold dispersion FEE 2011, Ivan Peric 45

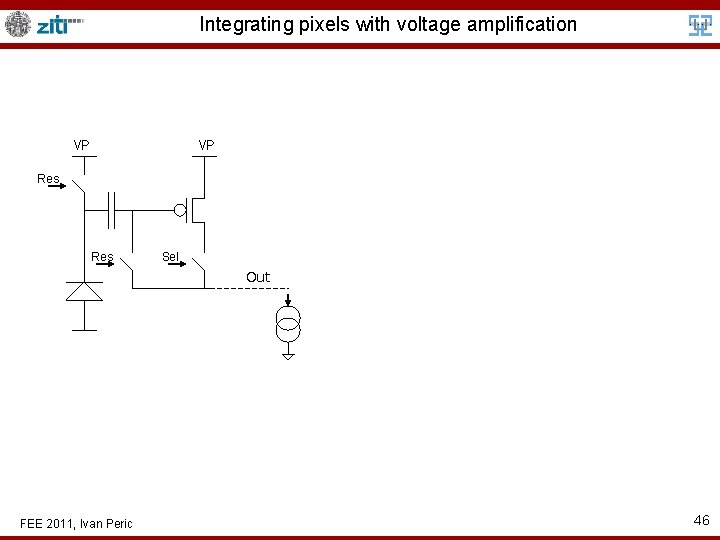

Integrating pixels with voltage amplification VP VP Res Sel Out FEE 2011, Ivan Peric 46

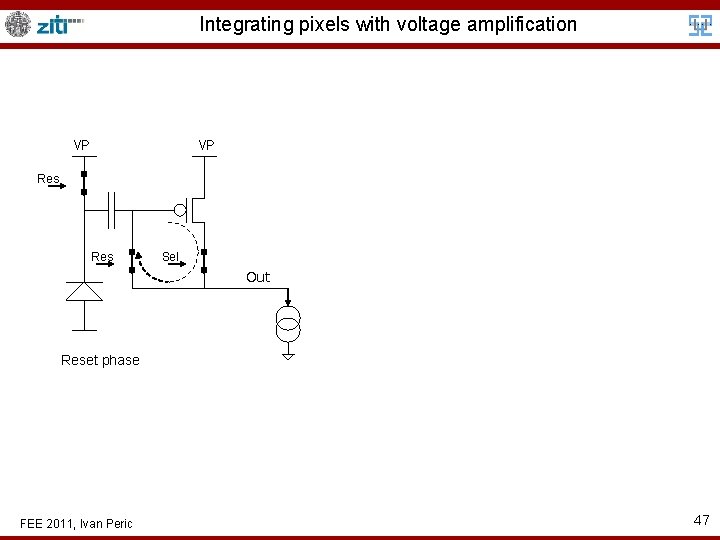

Integrating pixels with voltage amplification VP VP Res Sel Out Reset phase FEE 2011, Ivan Peric 47

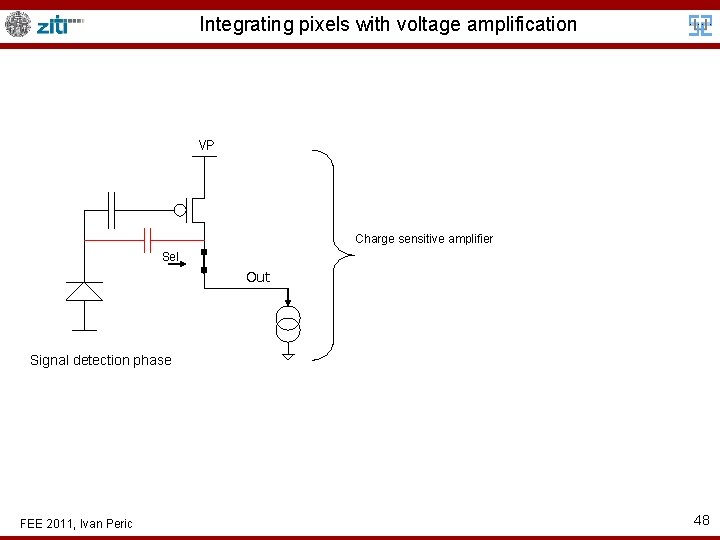

Integrating pixels with voltage amplification VP Charge sensitive amplifier Sel Out Signal detection phase FEE 2011, Ivan Peric 48

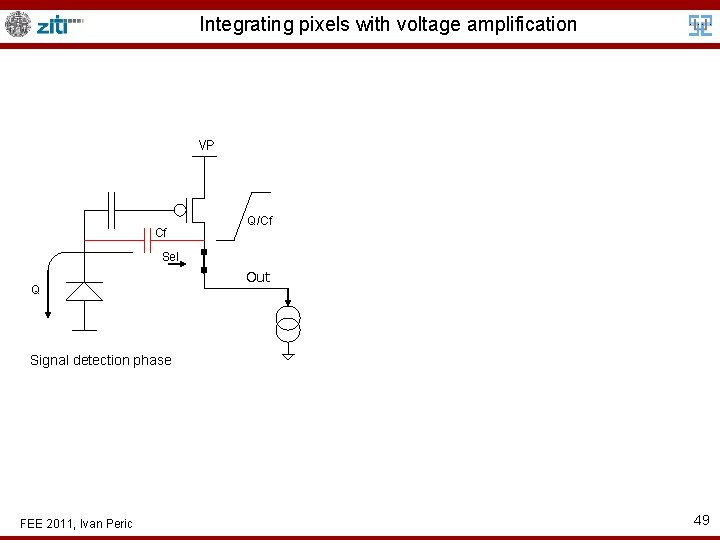

Integrating pixels with voltage amplification VP Cf Q/Cf Sel Q Out Signal detection phase FEE 2011, Ivan Peric 49

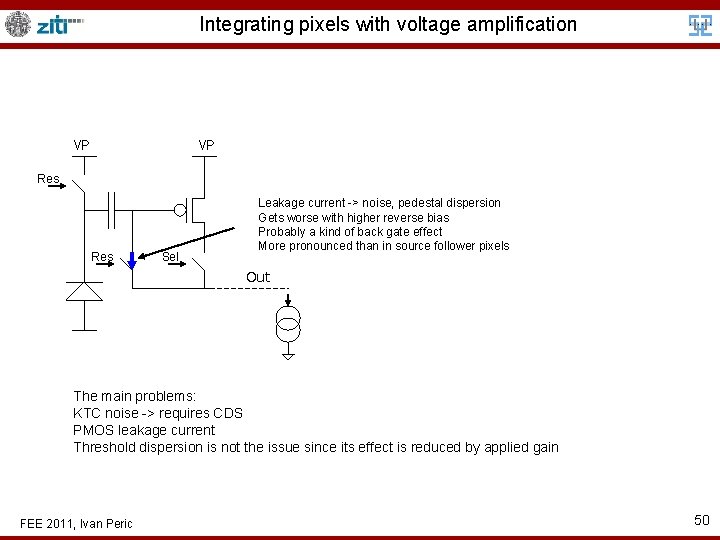

Integrating pixels with voltage amplification VP VP Res Sel Leakage current -> noise, pedestal dispersion Gets worse with higher reverse bias Probably a kind of back gate effect More pronounced than in source follower pixels Out The main problems: KTC noise -> requires CDS PMOS leakage current Threshold dispersion is not the issue since its effect is reduced by applied gain FEE 2011, Ivan Peric 50

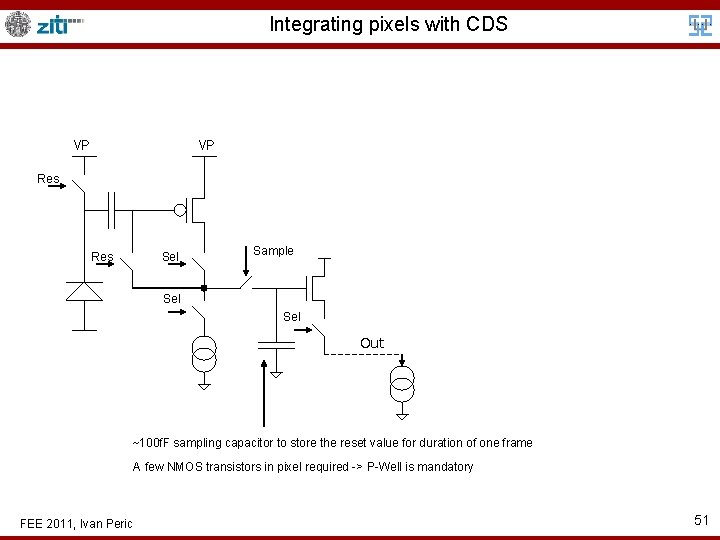

Integrating pixels with CDS VP VP Res Sel Sample Sel Out ~100 f. F sampling capacitor to store the reset value for duration of one frame A few NMOS transistors in pixel required -> P-Well is mandatory FEE 2011, Ivan Peric 51

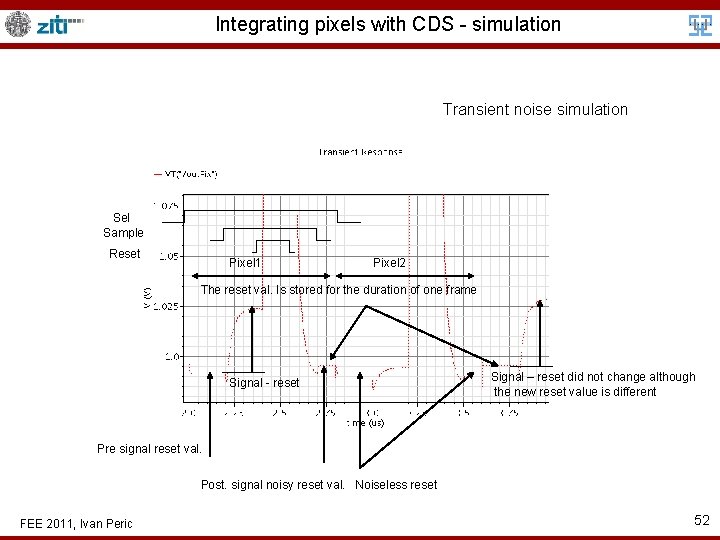

Integrating pixels with CDS - simulation Transient noise simulation Sel Sample Reset Pixel 1 Pixel 2 The reset val. Is stored for the duration of one frame Signal - reset Signal – reset did not change although the new reset value is different Pre signal reset val. Post. signal noisy reset val. Noiseless reset FEE 2011, Ivan Peric 52

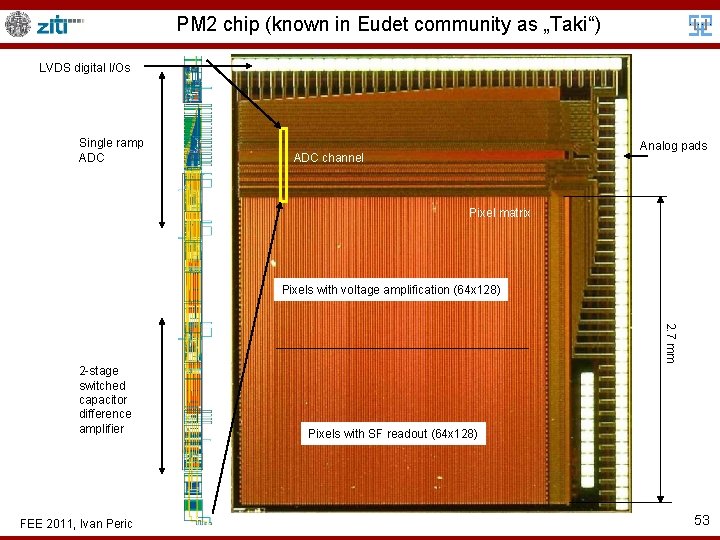

PM 2 chip (known in Eudet community as „Taki“) LVDS digital I/Os Single ramp ADC Analog pads ADC channel Pixel matrix Pixels with voltage amplification (64 x 128) 2. 7 mm 2 -stage switched capacitor difference amplifier FEE 2011, Ivan Peric Pixels with SF readout (64 x 128) 53

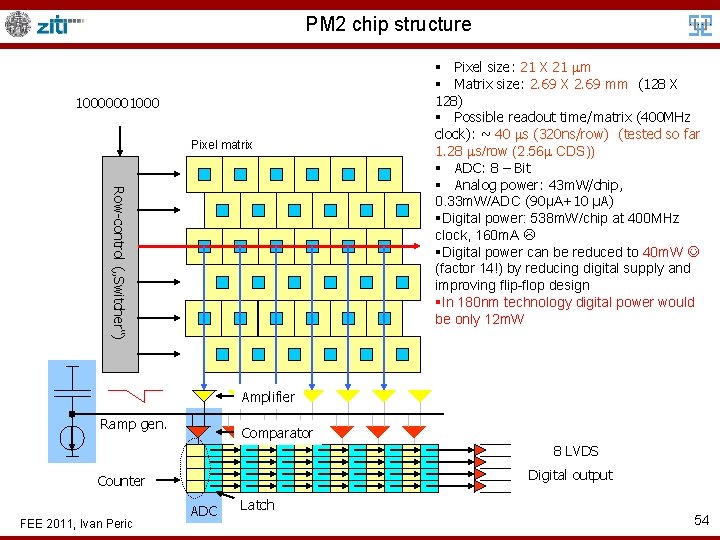

PM 2 chip structure 10000001000 Pixel matrix Row-control („Switcher“) § Pixel size: 21 X 21 m § Matrix size: 2. 69 X 2. 69 mm (128 X 128) § Possible readout time/matrix (400 MHz clock): ~ 40 s (320 ns/row) (tested so far 1. 28 s/row (2. 56 CDS)) § ADC: 8 – Bit § Analog power: 43 m. W/chip, 0. 33 m. W/ADC (90μA+10 μA) §Digital power: 538 m. W/chip at 400 MHz clock, 160 m. A §Digital power can be reduced to 40 m. W (factor 14!) by reducing digital supply and improving flip-flop design §In 180 nm technology digital power would be only 12 m. W Amplifier Ramp gen. Comparator 8 LVDS Digital output Counter FEE 2011, Ivan Peric ADC Latch 54

Integrating pixels with SF readout – experimental results FEE 2011, Ivan Peric 55

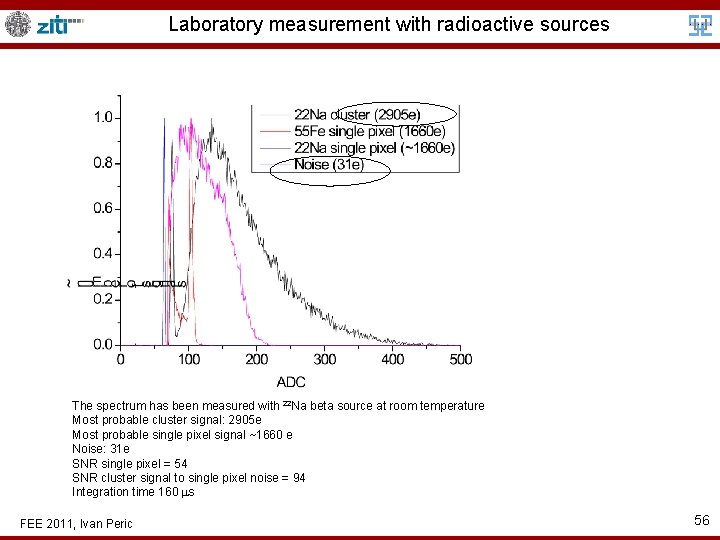

Laboratory measurement with radioactive sources The spectrum has been measured with 22 Na beta source at room temperature Most probable cluster signal: 2905 e Most probable single pixel signal ~1660 e Noise: 31 e SNR single pixel = 54 SNR cluster signal to single pixel noise = 94 Integration time 160 s FEE 2011, Ivan Peric 56

Test beam at CERN (SPS) with Eudet Mimosa 26 telescope Noise measurement Base line noise – the pixel signals corrected for pedestal distribution, all pixel in one frame are shown FEE 2011, Ivan Peric Common mode noise – common mode correction values for all frames and rows 57

Test beam: Signal spectra in AD units depending on number of pixels in a cluster FEE 2011, Ivan Peric 58

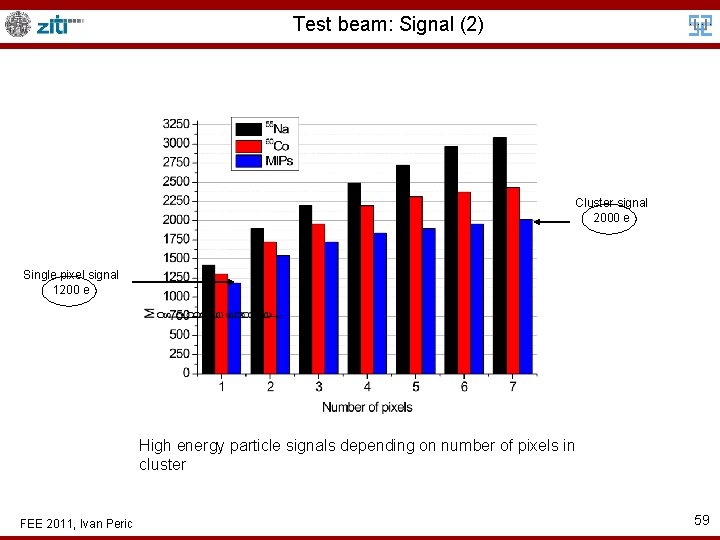

Test beam: Signal (2) Cluster signal 2000 e Single pixel signal 1200 e High energy particle signals depending on number of pixels in cluster FEE 2011, Ivan Peric 59

Test beam: SNR Seed pixel SNR = 27 FEE 2011, Ivan Peric 60

Test beam: SNR Single pixel SNR = 27 Cluster signal to noise ratio (MPX) vs. number of pixels in cluster FEE 2011, Ivan Peric 61

Test beam: “fake” SNR Fake SNR = 47 Fake SNR spectrum of the clusters. Fake SNR is here defined as the total cluster charge divided by the seed pixel noise. FEE 2011, Ivan Peric 62

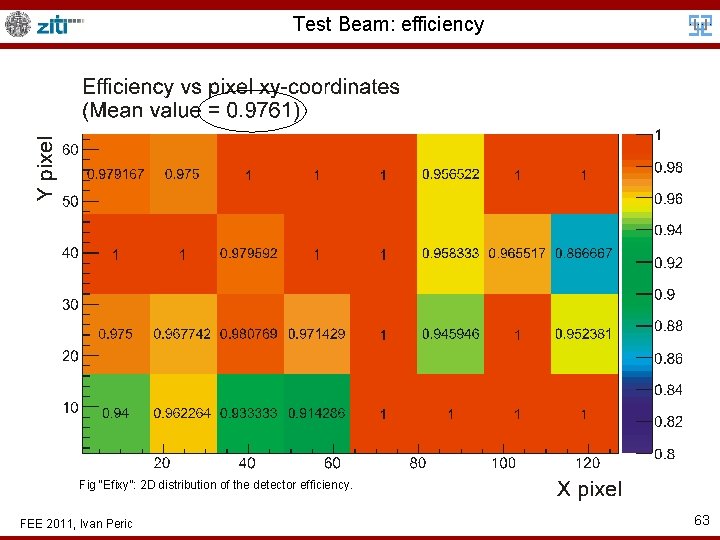

Test Beam: efficiency Fig “Efixy”: 2 D distribution of the detector efficiency. FEE 2011, Ivan Peric 63

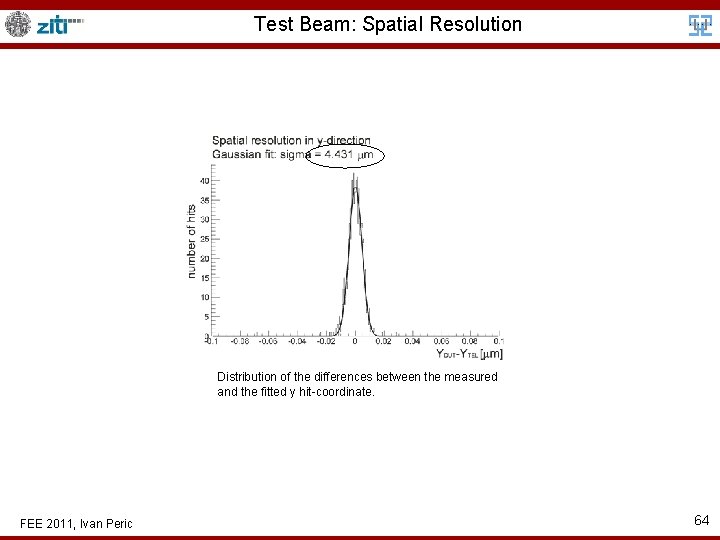

Test Beam: Spatial Resolution Distribution of the differences between the measured and the fitted y hit-coordinate. FEE 2011, Ivan Peric 64

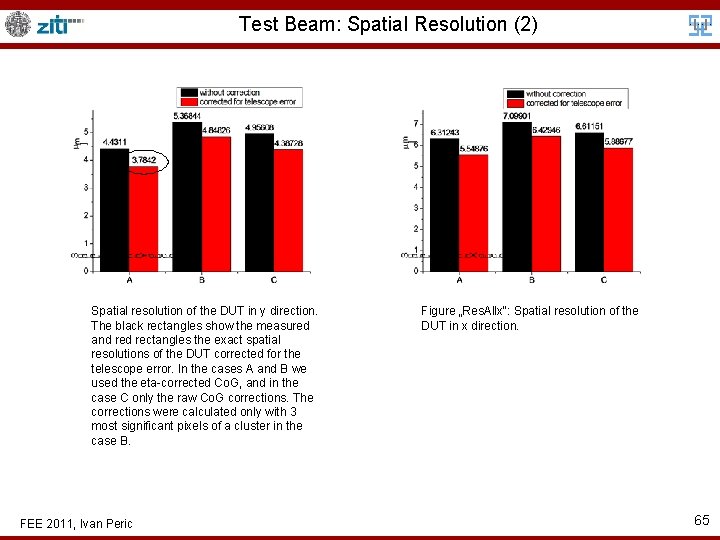

Test Beam: Spatial Resolution (2) Spatial resolution of the DUT in y direction. The black rectangles show the measured and rectangles the exact spatial resolutions of the DUT corrected for the telescope error. In the cases A and B we used the eta-corrected Co. G, and in the case C only the raw Co. G corrections. The corrections were calculated only with 3 most significant pixels of a cluster in the case B. FEE 2011, Ivan Peric Figure „Res. Allx“: Spatial resolution of the DUT in x direction. 65

Integrating pixels with voltage amplification – experimental results FEE 2011, Ivan Peric 66

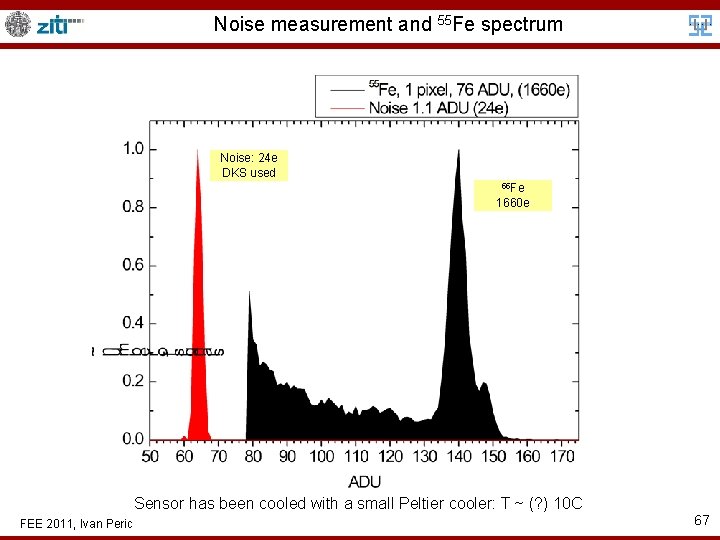

Noise measurement and 55 Fe spectrum Noise: 24 e DKS used 55 Fe 1660 e Sensor has been cooled with a small Peltier cooler: T ~ (? ) 10 C FEE 2011, Ivan Peric 67

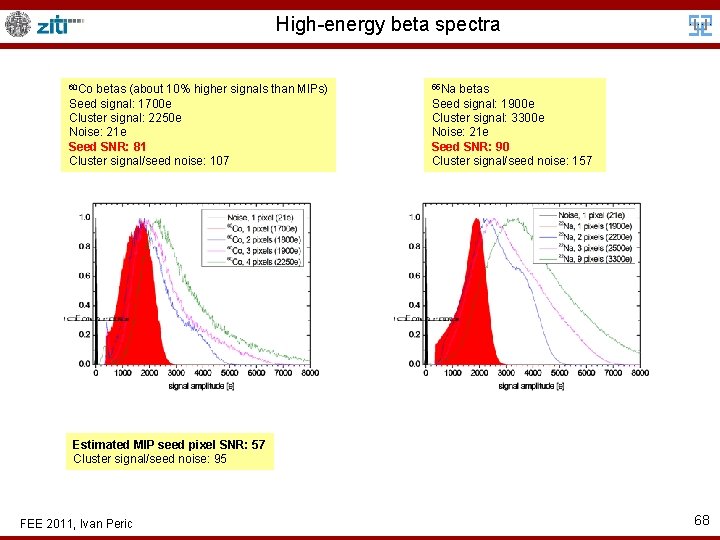

High-energy beta spectra 60 Co betas (about 10% higher signals than MIPs) Seed signal: 1700 e Cluster signal: 2250 e Noise: 21 e Seed SNR: 81 Cluster signal/seed noise: 107 55 Na betas Seed signal: 1900 e Cluster signal: 3300 e Noise: 21 e Seed SNR: 90 Cluster signal/seed noise: 157 Estimated MIP seed pixel SNR: 57 Cluster signal/seed noise: 95 FEE 2011, Ivan Peric 68

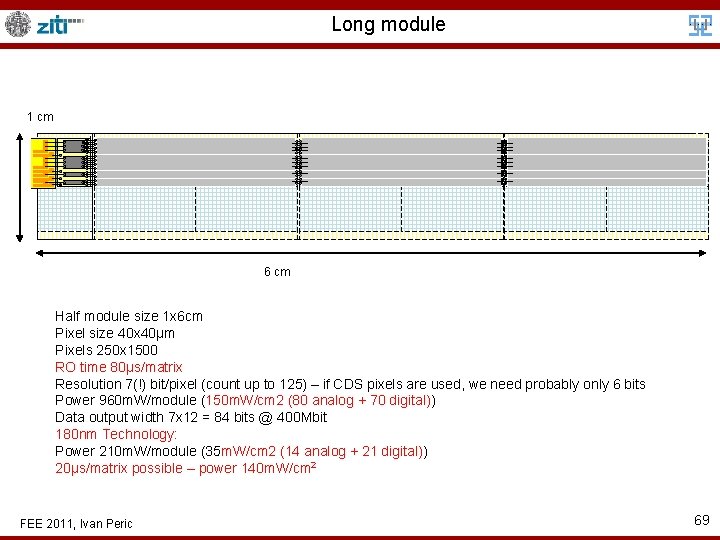

Long module 1 cm 6 cm Half module size 1 x 6 cm Pixel size 40 x 40μm Pixels 250 x 1500 RO time 80μs/matrix Resolution 7(!) bit/pixel (count up to 125) – if CDS pixels are used, we need probably only 6 bits Power 960 m. W/module (150 m. W/cm 2 (80 analog + 70 digital)) Data output width 7 x 12 = 84 bits @ 400 Mbit 180 nm Technology: Power 210 m. W/module (35 m. W/cm 2 (14 analog + 21 digital)) 20μs/matrix possible – power 140 m. W/cm 2 FEE 2011, Ivan Peric 69

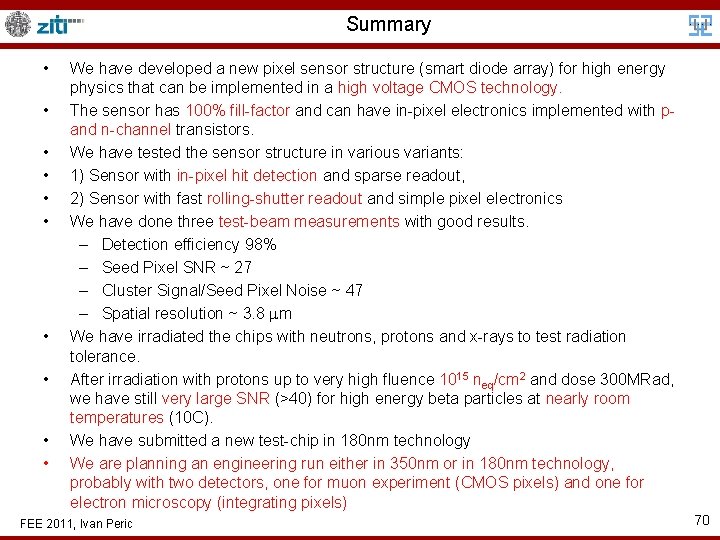

Summary • • • We have developed a new pixel sensor structure (smart diode array) for high energy physics that can be implemented in a high voltage CMOS technology. The sensor has 100% fill-factor and can have in-pixel electronics implemented with pand n-channel transistors. We have tested the sensor structure in various variants: 1) Sensor with in-pixel hit detection and sparse readout, 2) Sensor with fast rolling-shutter readout and simple pixel electronics We have done three test-beam measurements with good results. – Detection efficiency 98% – Seed Pixel SNR ~ 27 – Cluster Signal/Seed Pixel Noise ~ 47 – Spatial resolution ~ 3. 8 m We have irradiated the chips with neutrons, protons and x-rays to test radiation tolerance. After irradiation with protons up to very high fluence 1015 neq/cm 2 and dose 300 MRad, we have still very large SNR (>40) for high energy beta particles at nearly room temperatures (10 C). We have submitted a new test-chip in 180 nm technology We are planning an engineering run either in 350 nm or in 180 nm technology, probably with two detectors, one for muon experiment (CMOS pixels) and one for electron microscopy (integrating pixels) FEE 2011, Ivan Peric 70

• Thank you! FEE 2011, Ivan Peric 71

• Backup slides FEE 2011, Ivan Peric 72

Integrating pixels with source follower readout FEE 2011, Ivan Peric 73

Pixels with SF RO – signal detection phase Out VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B N-Well P-Substrate FEE 2011, Ivan Peric VN 74

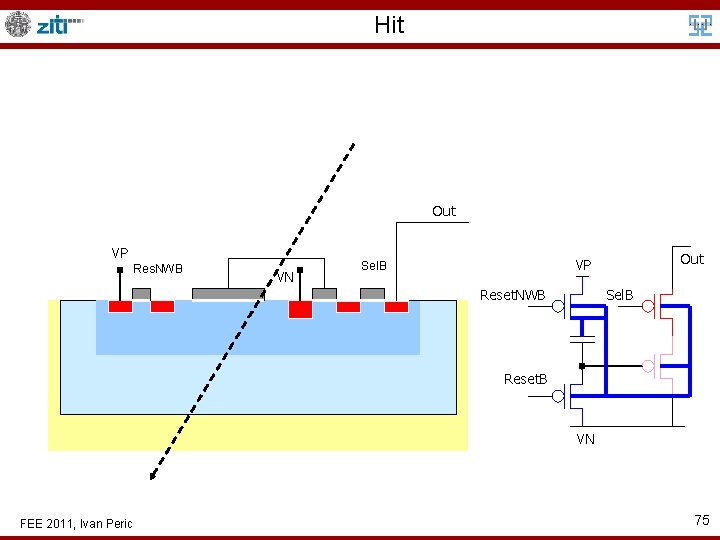

Hit Out VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B VN FEE 2011, Ivan Peric 75

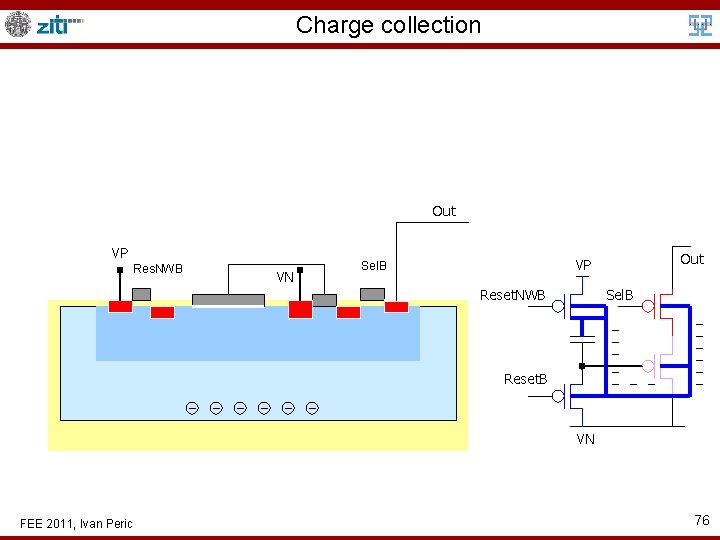

Charge collection Out VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B VN FEE 2011, Ivan Peric 76

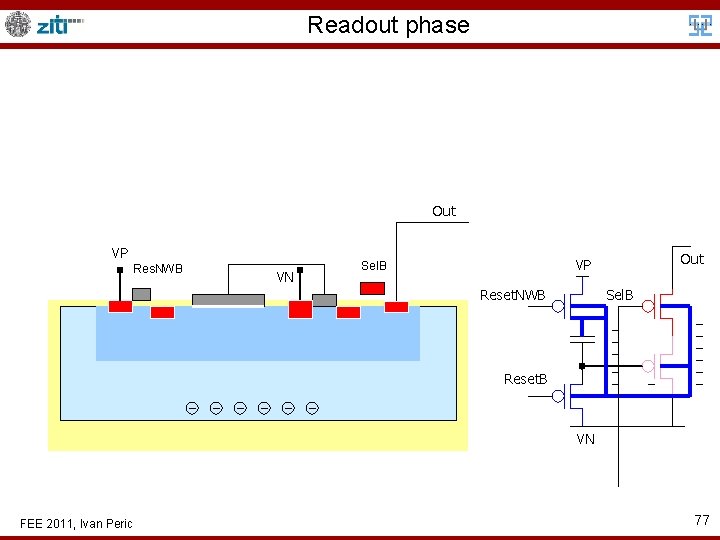

Readout phase Out VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B VN FEE 2011, Ivan Peric 77

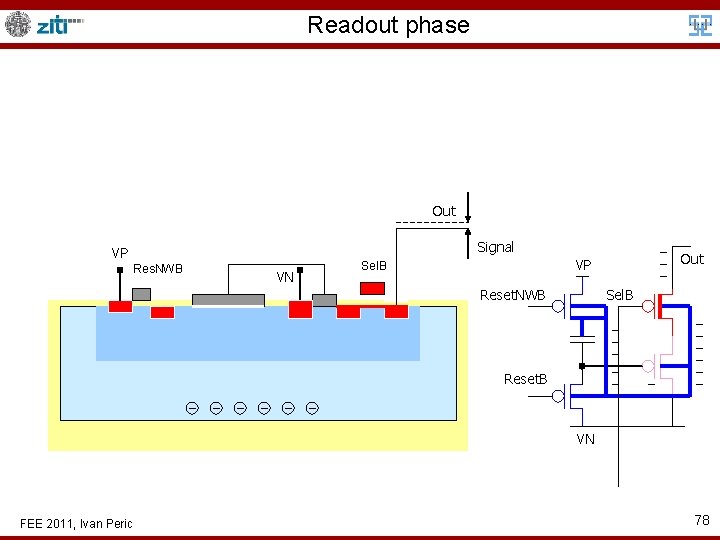

Readout phase Out Signal VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B VN FEE 2011, Ivan Peric 78

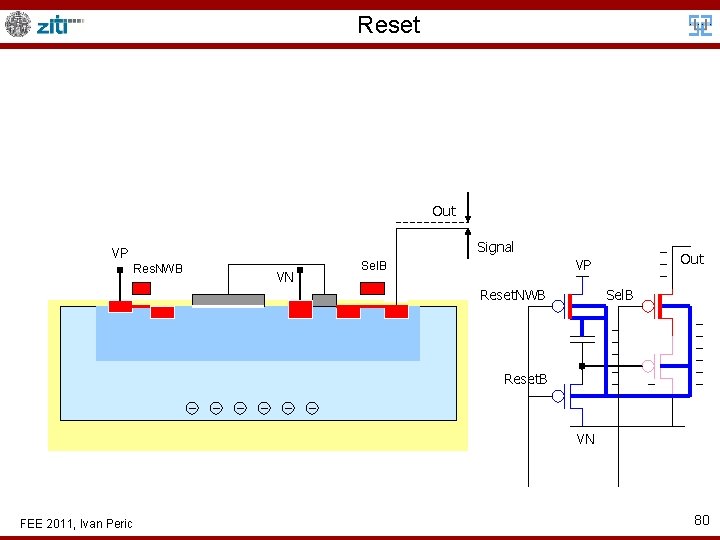

Reset Out Signal VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B VN FEE 2011, Ivan Peric 79

Reset Out Signal VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B VN FEE 2011, Ivan Peric 80

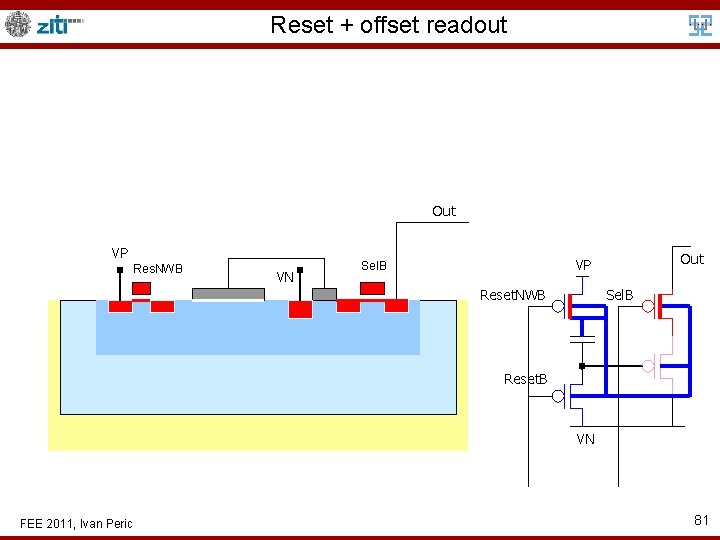

Reset + offset readout Out VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B VN FEE 2011, Ivan Peric 81

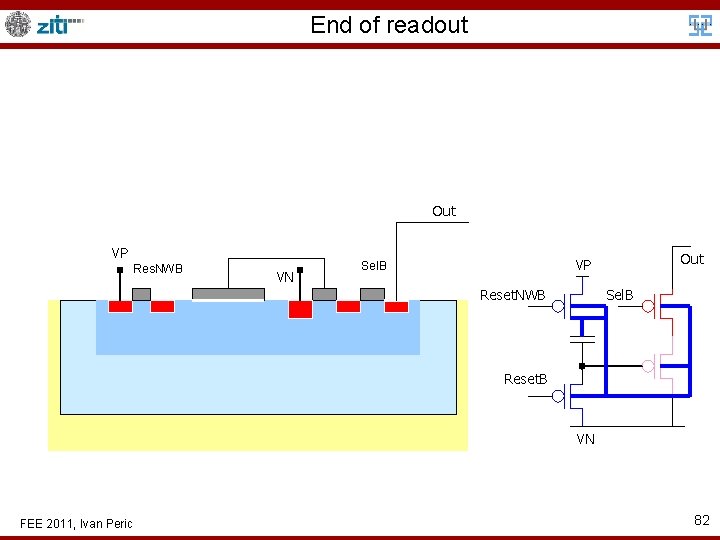

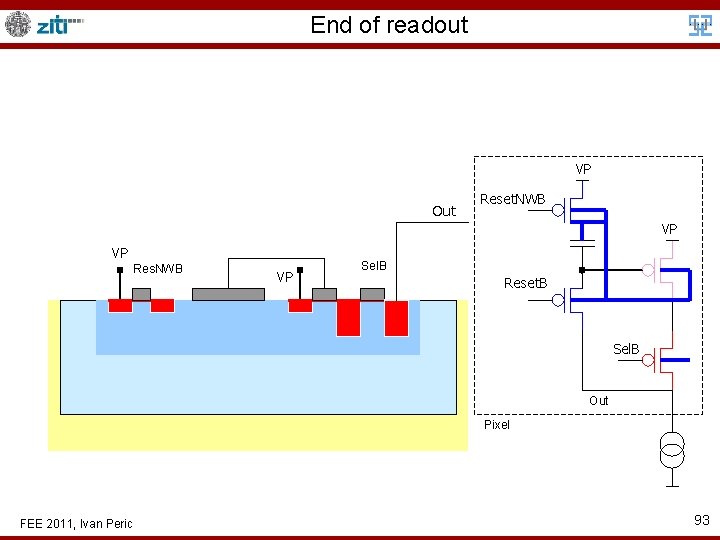

End of readout Out VP Res. NWB VN Out VP Sel. B Reset. NWB Sel. B Reset. B VN FEE 2011, Ivan Peric 82

Integrating pixels with voltage amplification FEE 2011, Ivan Peric 83

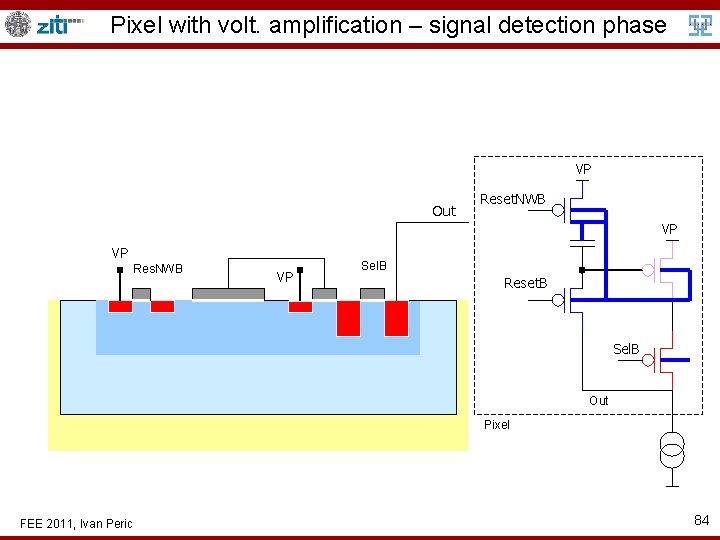

Pixel with volt. amplification – signal detection phase VP Out Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Sel. B Out Pixel FEE 2011, Ivan Peric 84

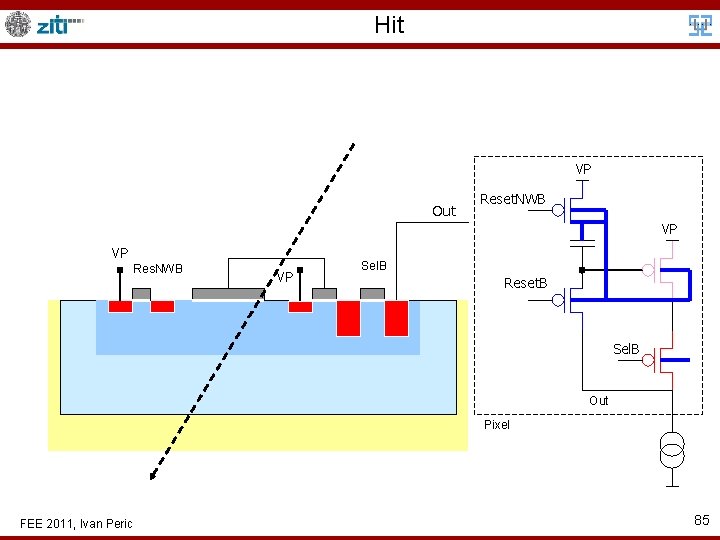

Hit VP Out Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Sel. B Out Pixel FEE 2011, Ivan Peric 85

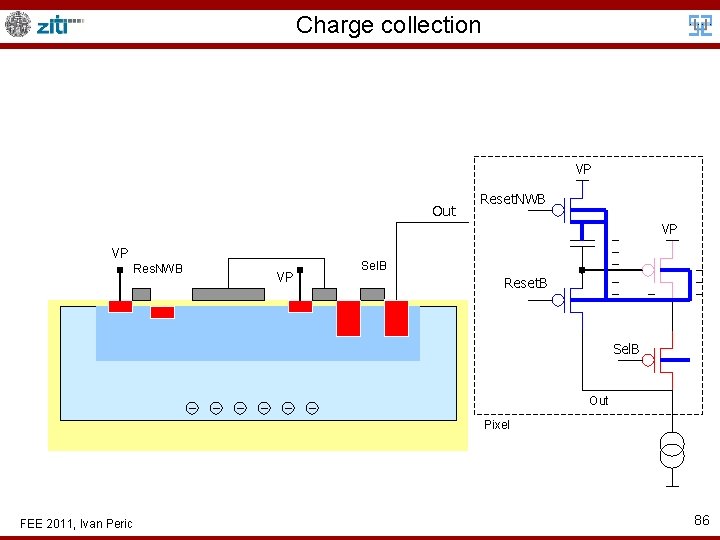

Charge collection VP Out Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Sel. B Out Pixel FEE 2011, Ivan Peric 86

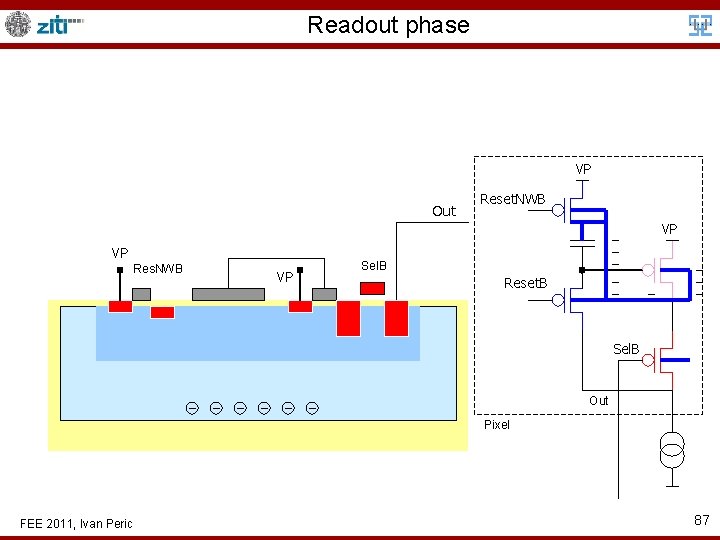

Readout phase VP Out Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Sel. B Out Pixel FEE 2011, Ivan Peric 87

Readout phase VP Out Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Sel. B Out Pixel FEE 2011, Ivan Peric 88

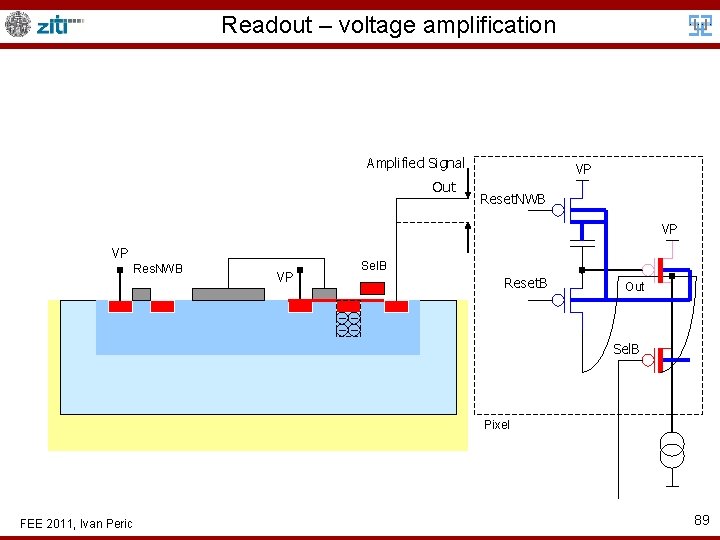

Readout – voltage amplification Amplified Signal Out VP Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Out Sel. B Pixel FEE 2011, Ivan Peric 89

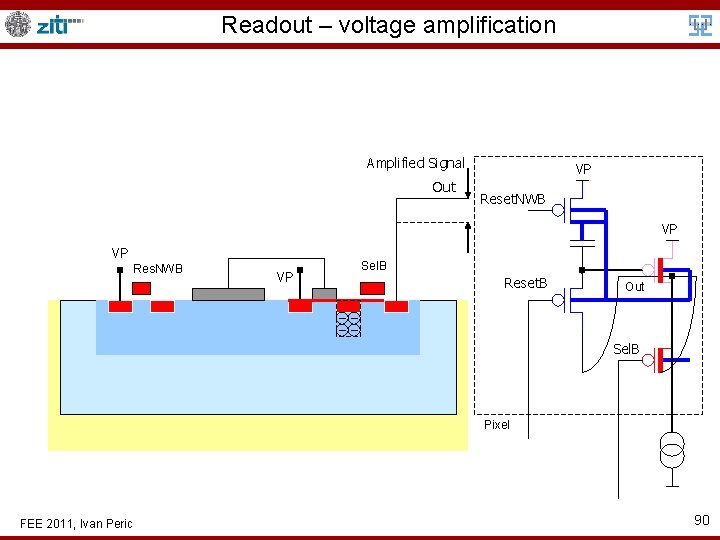

Readout – voltage amplification Amplified Signal Out VP Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Out Sel. B Pixel FEE 2011, Ivan Peric 90

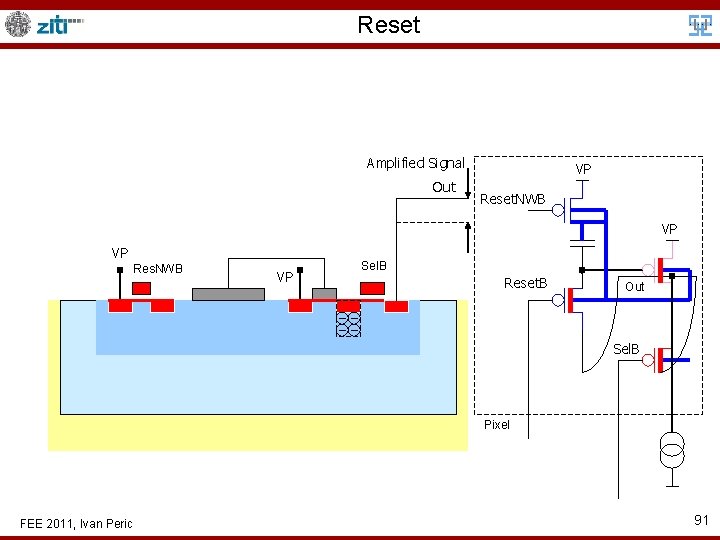

Reset Amplified Signal Out VP Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Out Sel. B Pixel FEE 2011, Ivan Peric 91

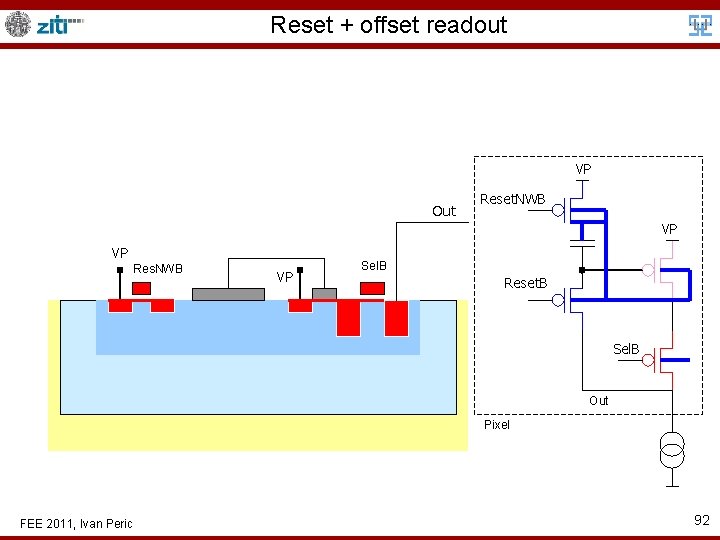

Reset + offset readout VP Out Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Sel. B Out Pixel FEE 2011, Ivan Peric 92

End of readout VP Out Reset. NWB VP VP Res. NWB VP Sel. B Reset. B Sel. B Out Pixel FEE 2011, Ivan Peric 93

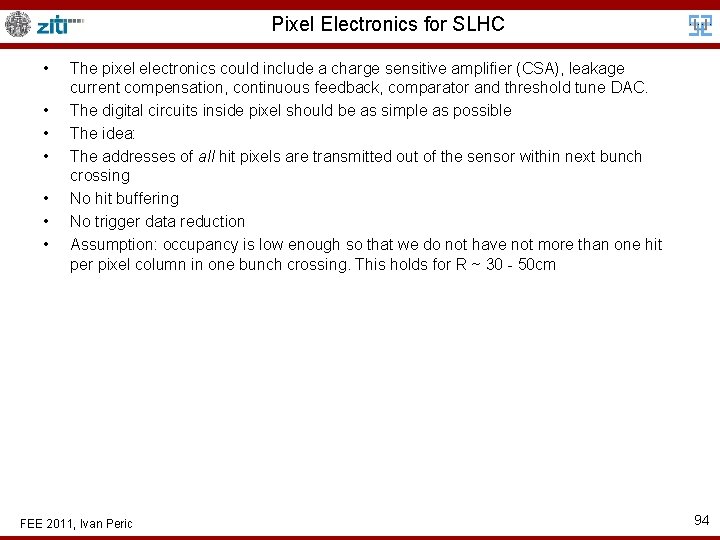

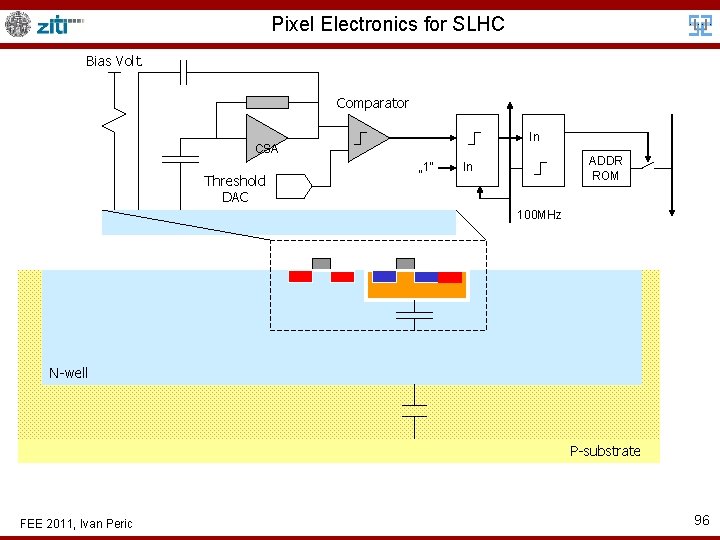

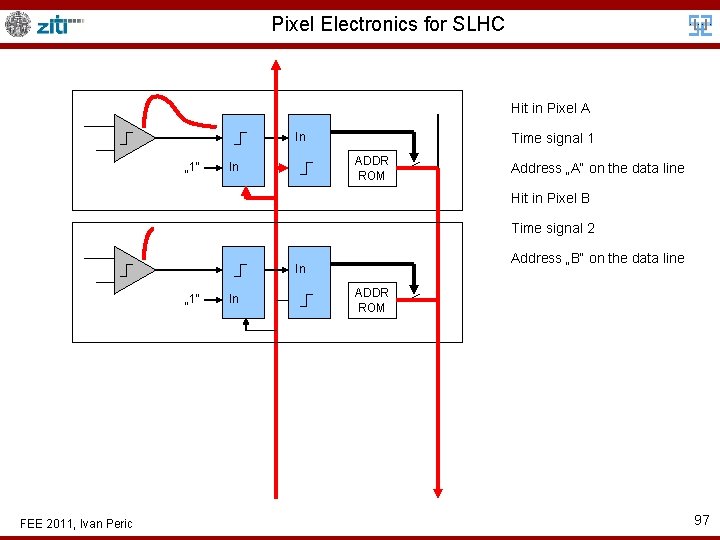

Pixel Electronics for SLHC • • The pixel electronics could include a charge sensitive amplifier (CSA), leakage current compensation, continuous feedback, comparator and threshold tune DAC. The digital circuits inside pixel should be as simple as possible The idea: The addresses of all hit pixels are transmitted out of the sensor within next bunch crossing No hit buffering No trigger data reduction Assumption: occupancy is low enough so that we do not have not more than one hit per pixel column in one bunch crossing. This holds for R ~ 30 - 50 cm FEE 2011, Ivan Peric 94

Capacitance of long pixels Total 700 f. F 400 um 60 um P-well N-well ~200 f. F ~500 f. F (C_area = 0. 014 f. F/um 2) P-substrate FEE 2011, Ivan Peric 95

Pixel Electronics for SLHC Bias Volt. Comparator In CSA Threshold DAC „ 1“ ADDR ROM In 100 MHz N-well P-substrate FEE 2011, Ivan Peric 96

Pixel Electronics for SLHC Hit in Pixel A In „ 1“ Time signal 1 ADDR ROM In Address „A“ on the data line Hit in Pixel B Time signal 2 Address „B“ on the data line In „ 1“ FEE 2011, Ivan Peric In ADDR ROM 97

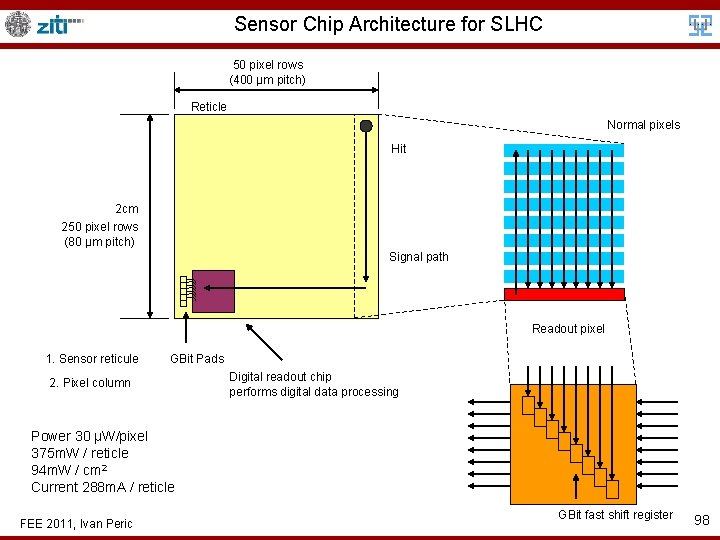

Sensor Chip Architecture for SLHC 50 pixel rows (400 μm pitch) Reticle Normal pixels Hit 2 cm 250 pixel rows (80 μm pitch) Signal path Readout pixel 1. Sensor reticule GBit Pads 2. Pixel column Digital readout chip performs digital data processing Power 30 μW/pixel 375 m. W / reticle 94 m. W / cm 2 Current 288 m. A / reticle FEE 2011, Ivan Peric GBit fast shift register 98

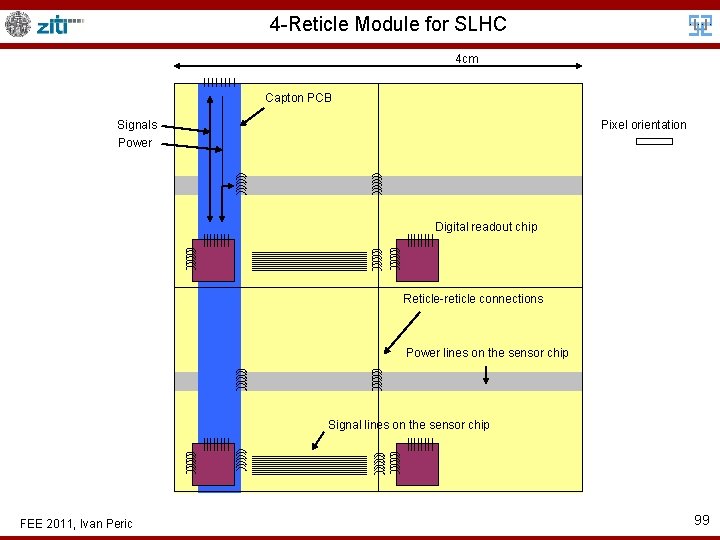

4 -Reticle Module for SLHC 4 cm Capton PCB Signals Pixel orientation Power Digital readout chip Reticle-reticle connections Power lines on the sensor chip Signal lines on the sensor chip FEE 2011, Ivan Peric 99

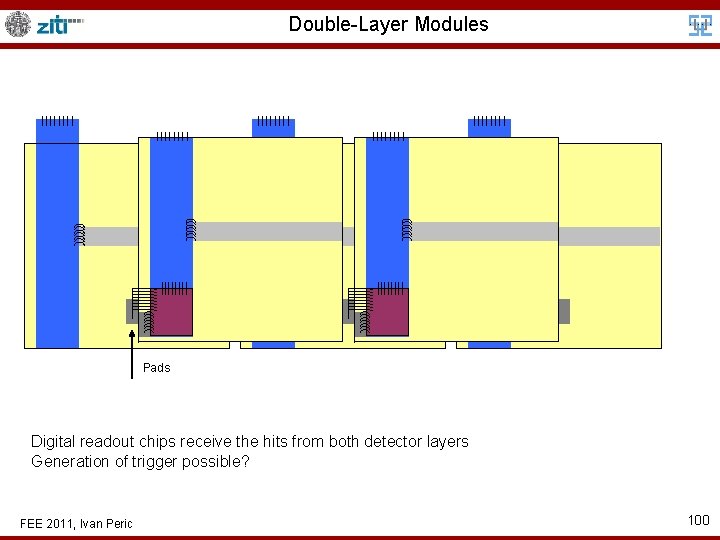

Double-Layer Modules Pads Digital readout chips receive the hits from both detector layers Generation of trigger possible? FEE 2011, Ivan Peric 100

Time Resolution • • • Time resolution is limited by time walk (can be improved by To. T correction!) Time resolution is proportional to preamplifier bias current and power consumption Time resolution is inversely proportional to detector capacitance FEE 2011, Ivan Peric 101

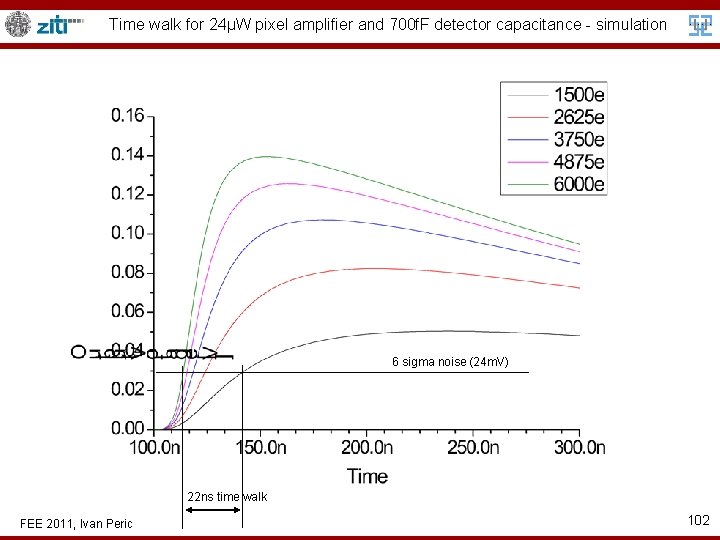

Time walk for 24μW pixel amplifier and 700 f. F detector capacitance - simulation 6 sigma noise (24 m. V) 22 ns time walk FEE 2011, Ivan Peric 102

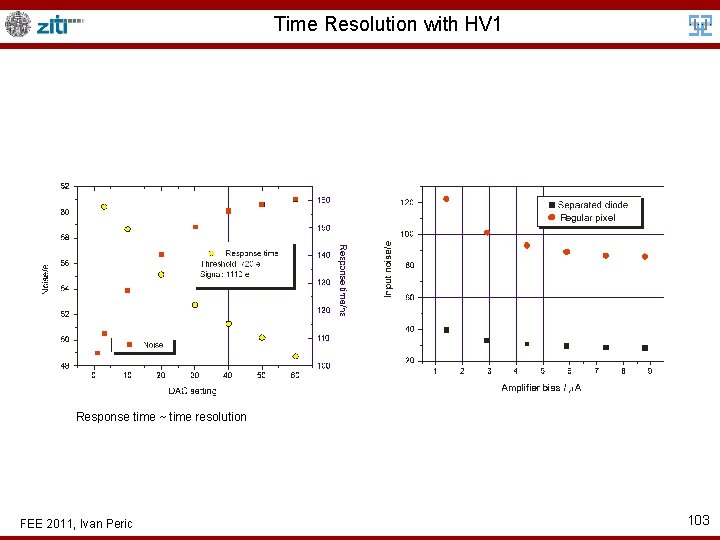

Time Resolution with HV 1 Response time ~ time resolution FEE 2011, Ivan Peric 103

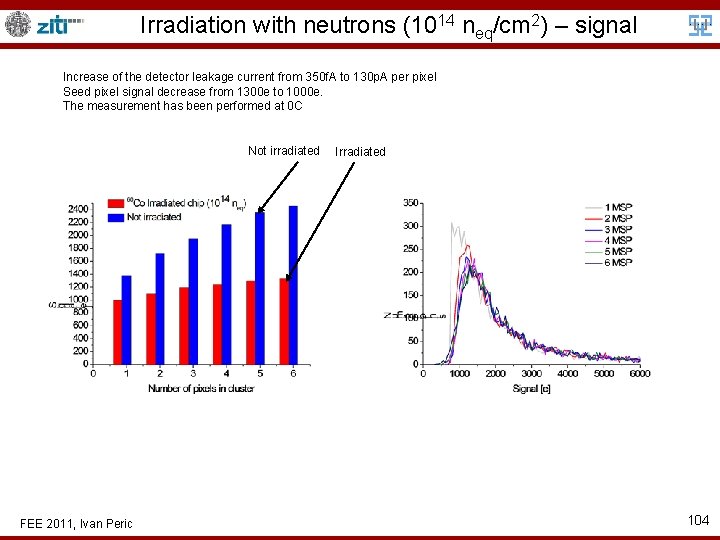

Irradiation with neutrons (1014 neq/cm 2) – signal Increase of the detector leakage current from 350 f. A to 130 p. A per pixel Seed pixel signal decrease from 1300 e to 1000 e. The measurement has been performed at 0 C Not irradiated FEE 2011, Ivan Peric Irradiated 104

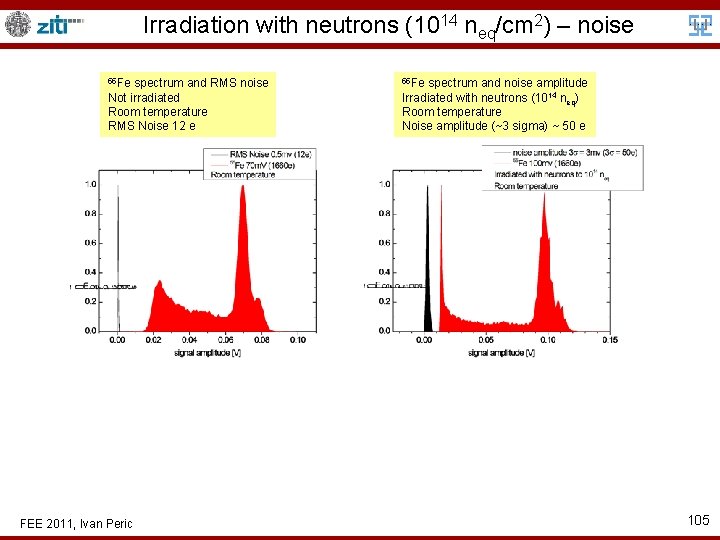

Irradiation with neutrons (1014 neq/cm 2) – noise 55 Fe spectrum and RMS noise Not irradiated Room temperature RMS Noise 12 e FEE 2011, Ivan Peric 55 Fe spectrum and noise amplitude Irradiated with neutrons (1014 neq) Room temperature Noise amplitude (~3 sigma) ~ 50 e 105

Irradiation with protons (1015 neq/cm 2, 300 MRad) 55 Fe spectrum and RMS noise Not irradiated Room temperature RMS Noise 12 e 55 Fe spectrum, RMS noise Irradiated 10 C RMS Noise 77 e FEE 2011, Ivan Peric 55 Fe spectrum and RMS noise Irradiated 20 C RMS Noise 270 e 55 Fe spectrum, RMS noise Irradiated -10 C RMS Noise 40 e 106

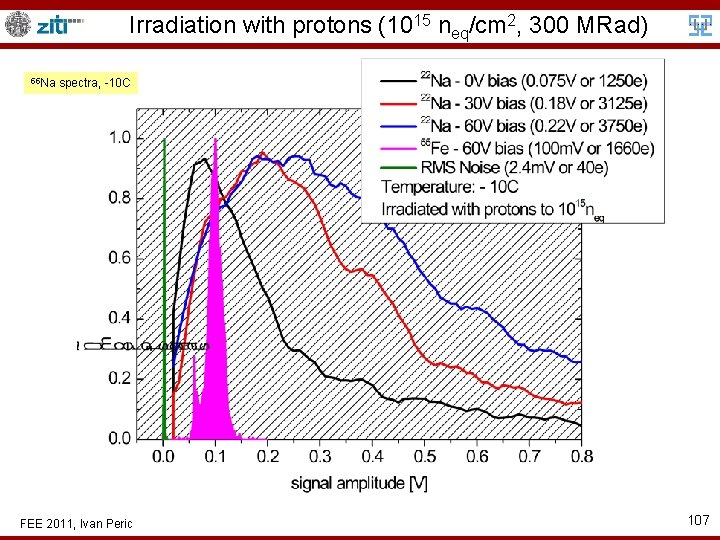

Irradiation with protons (1015 neq/cm 2, 300 MRad) 55 Na spectra, -10 C FEE 2011, Ivan Peric 107

Irradiation with protons (1015 neq/cm 2, 300 MRad) 55 Fe and 22 Na spectrum, RMS noise Irradiated Temperature 10 C RMS Noise 77 e SNR = 64 55 Fe and 22 Na spectrum, RMS noise Irradiated Temperature 20 C RMS Noise 270 e SNR = 15 55 Fe and 22 Na spectrum, RMS noise Irradiated Temperature -10 C RMS Noise 40 e SNR = 93 FEE 2011, Ivan Peric 108

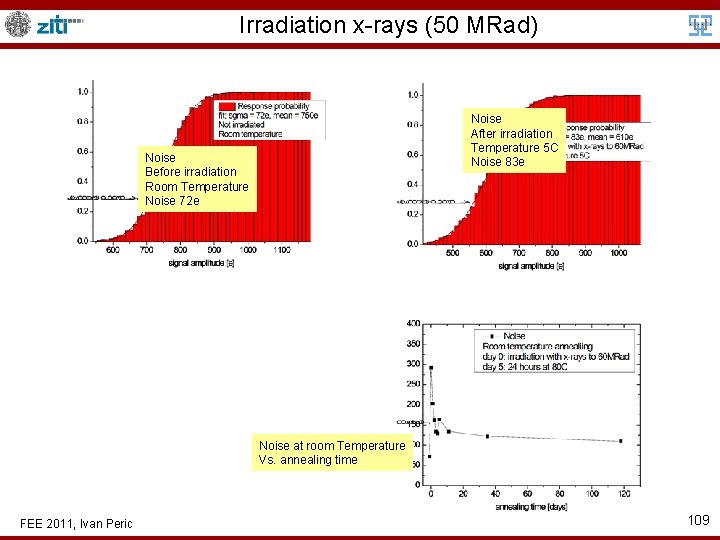

Irradiation x-rays (50 MRad) Noise After irradiation Temperature 5 C Noise 83 e Noise Before irradiation Room Temperature Noise 72 e Noise at room Temperature Vs. annealing time FEE 2011, Ivan Peric 109

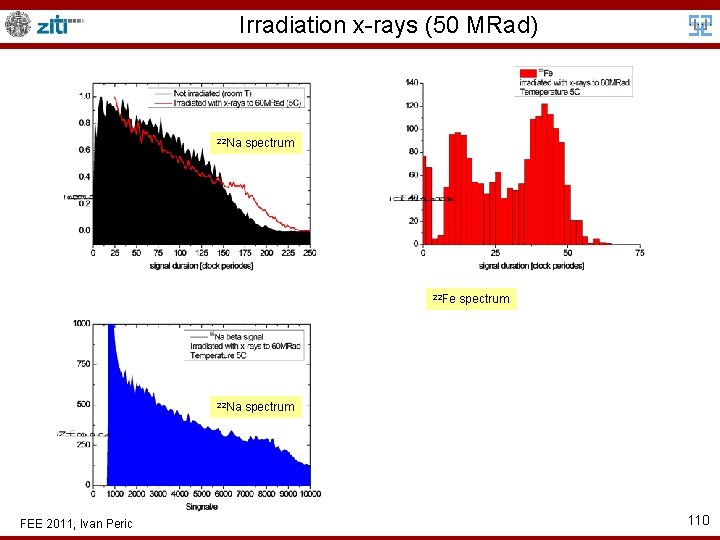

Irradiation x-rays (50 MRad) 22 Na spectrum 22 Fe 22 Na FEE 2011, Ivan Peric spectrum 110

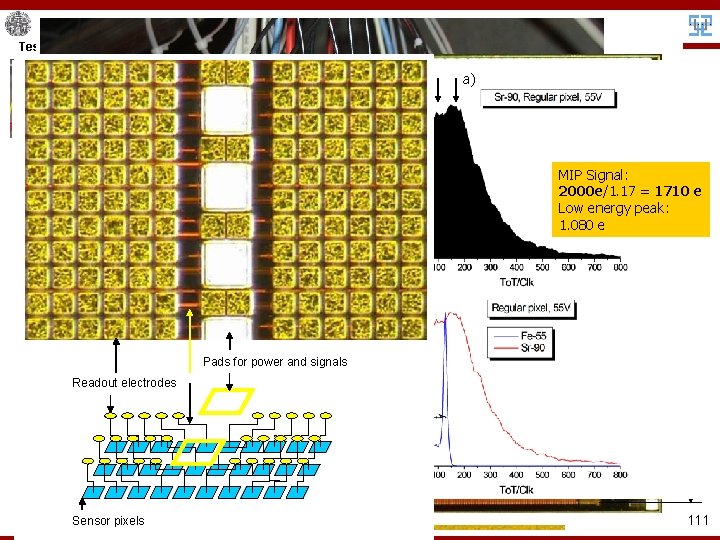

Project overview Testbeam DESY 3. 3 V Efficiency Power supply and cont. signals for the sensor Bumpless hybrid detector DUT EUDET telescope First chip – CMOS pixels a) supply b) Power Hit detection in pixels Trigger ID and cont. signals Binary RO CR-RC Comparator for the readout chip Pixel size 55 x 55μm Noise: Testbeam 60 e DUT CERN MIP seed pixel signal 1800 e 1. 5 mm ADC channel Time resolution 200 ns CSA 60 V bias voltage (3 batteries) Testchip MIP Signal: 2000 e/1. 17 = 1710 e 2. 7 mm Frame readout. Low - monolithic energy peak: Pixel matrix MIP spectrum (CERN Sp. S - 120 Ge. V protons) CCPD 1 Chip PM 1 1. 080 Chip e Bumpless hybrid detector AC coupling -50 V Pixel size 21 x 21μm Based on capacitive chip to chip Frame mode readout signal transfer 4 PMOS pixel electronics PCB Pixel size 78 x 60μm 128 on chip ADCs RO type: capacitive Noise: 90 e Noise: 80 e Test-beam: MIP signal 2200 e/1300 e Readout chip (CAPPIX) MIP signal 1800 e Efficiency > 85% (timing problem) Spatial resolution 7μm Uniform detection Pads for power and signals N-well Chip Readout CCPD 2 electrodes USB Edgeless CCPD connector Pixel size 50 x 50μm PCB with PPGA and analog supply and cluster cut [SNR] Noise: Seed 30 -40 e voltage regulators/DACs PM 2 Chip Time resolution 300 ns Noise: 21 e (lab) - 44 e (test beam) SNR 45 -60 P-substrate Test beam: Detection efficiency 98% Irradiations of test pixels Seed Pixel SNR ~ 27 60 MRad – SNR 22 at 10 C (CCPD 1) Cluster Signal/Seed Pixel Noise ~ 47 15 n 10 Sensor at 10 C (CCPD 2) chip 50(CAPSENSE) eq SNR Spatial resolution ~ 3. 8 m pixels 111 FEE 2011, Sensor Ivan Peric

- Slides: 111