Monolith IC 3 D ICs October 2012 Monolith

Monolith. IC 3 D ICs October 2012 Monolith. IC 3 D Inc. , Patents Pending 1

Chapter 1 Monolithic 3 D Monolith. IC 3 D Inc. Patents Pending 2

3 D ICs at a glance A 3 D Integrated Circuit is a chip that has active electronic components stacked on one or more layers that are integrated both vertically and horizontally forming a single circuit. Manufacturing technologies: -Monolithic -TSV based stacking -Chip Stacking w/wire bonding Monolith. IC 3 D Inc, Patents Pending 3

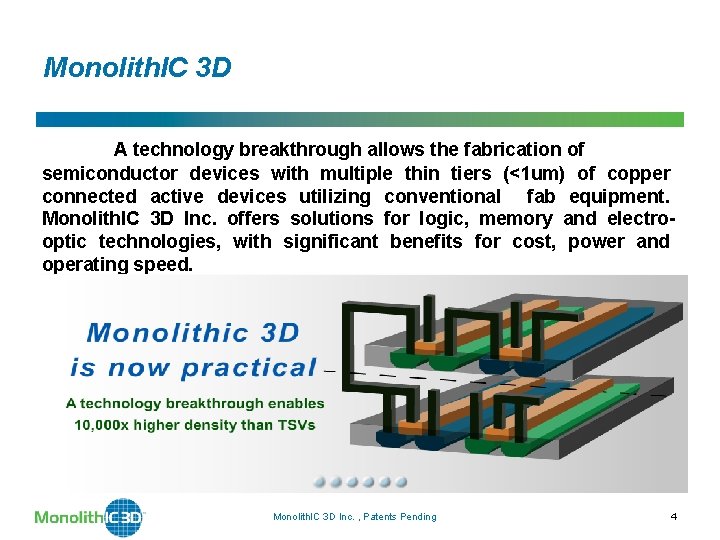

Monolith. IC 3 D A technology breakthrough allows the fabrication of semiconductor devices with multiple thin tiers (<1 um) of copper connected active devices utilizing conventional fab equipment. Monolith. IC 3 D Inc. offers solutions for logic, memory and electrooptic technologies, with significant benefits for cost, power and operating speed. Monolith. IC 3 D Inc. , Patents Pending 4

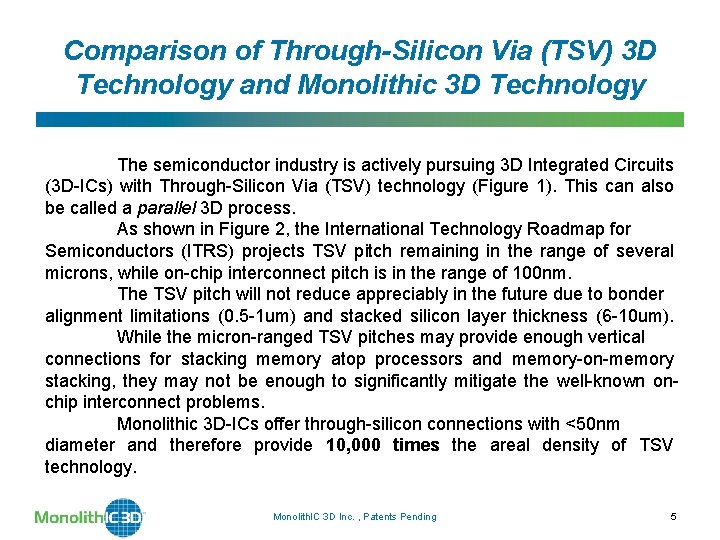

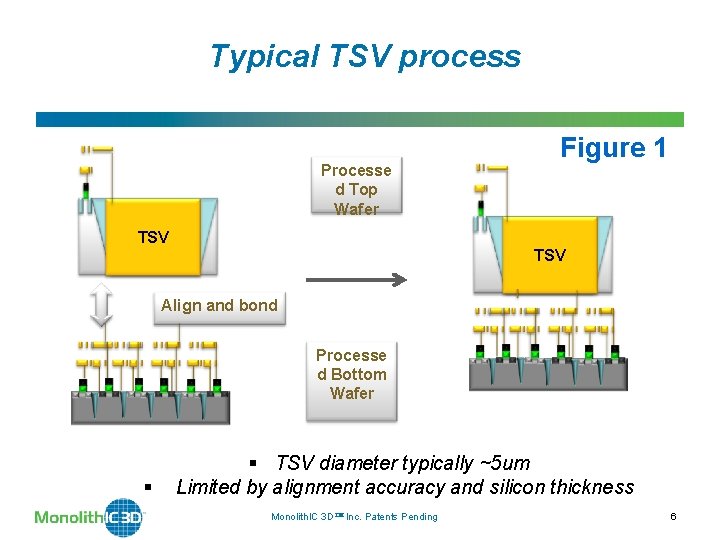

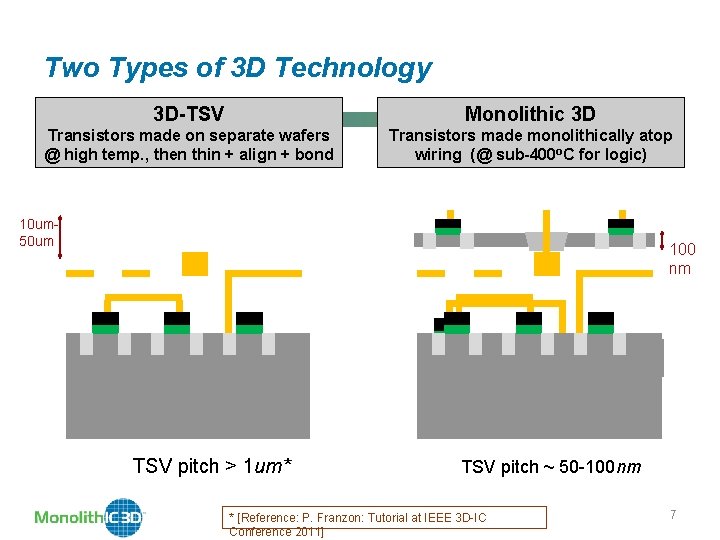

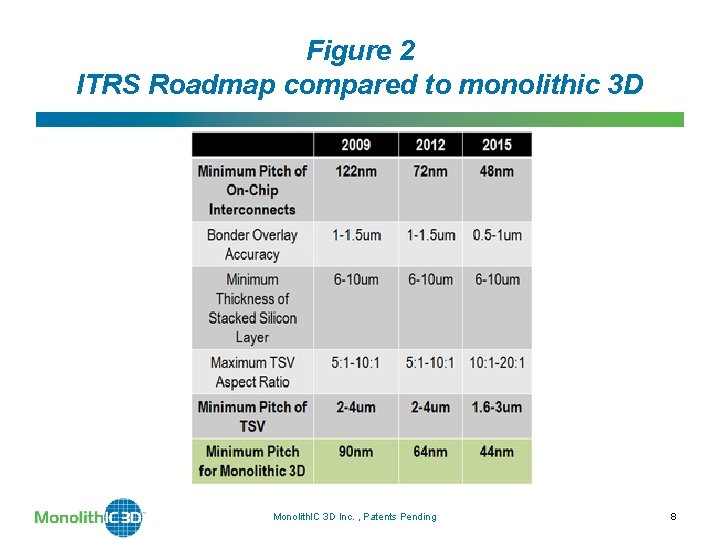

Comparison of Through-Silicon Via (TSV) 3 D Technology and Monolithic 3 D Technology The semiconductor industry is actively pursuing 3 D Integrated Circuits (3 D-ICs) with Through-Silicon Via (TSV) technology (Figure 1). This can also be called a parallel 3 D process. As shown in Figure 2, the International Technology Roadmap for Semiconductors (ITRS) projects TSV pitch remaining in the range of several microns, while on-chip interconnect pitch is in the range of 100 nm. The TSV pitch will not reduce appreciably in the future due to bonder alignment limitations (0. 5 -1 um) and stacked silicon layer thickness (6 -10 um). While the micron-ranged TSV pitches may provide enough vertical connections for stacking memory atop processors and memory-on-memory stacking, they may not be enough to significantly mitigate the well-known onchip interconnect problems. Monolithic 3 D-ICs offer through-silicon connections with <50 nm diameter and therefore provide 10, 000 times the areal density of TSV technology. Monolith. IC 3 D Inc. , Patents Pending 5

Typical TSV process Processe d Top Wafer Figure 1 TSV Align and bond Processe d Bottom Wafer § TSV diameter typically ~5 um § Limited by alignment accuracy and silicon thickness Monolith. IC 3 D Inc. Patents Pending 6

Two Types of 3 D Technology 3 D-TSV Monolithic 3 D Transistors made on separate wafers @ high temp. , then thin + align + bond Transistors made monolithically atop wiring (@ sub-400 o. C for logic) 10 um 50 um 100 nm TSV pitch > 1 um* TSV pitch ~ 50 -100 nm * [Reference: P. Franzon: Tutorial at IEEE 3 D-IC Conference 2011] 7

Figure 2 ITRS Roadmap compared to monolithic 3 D Monolith. IC 3 D Inc. , Patents Pending 8

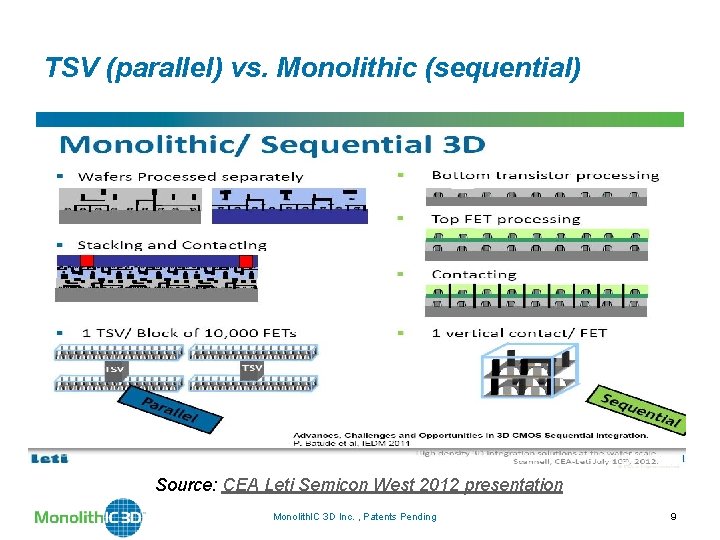

TSV (parallel) vs. Monolithic (sequential) Source: CEA Leti Semicon West 2012 presentation Monolith. IC 3 D Inc. , Patents Pending 9

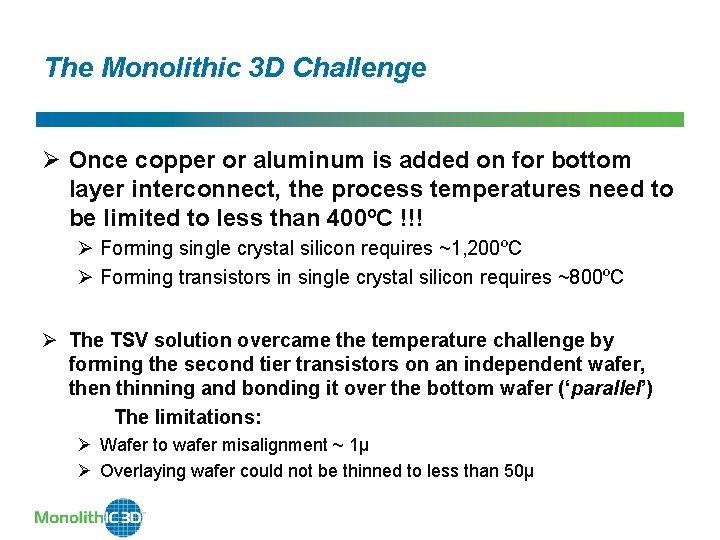

The Monolithic 3 D Challenge Ø Once copper or aluminum is added on for bottom layer interconnect, the process temperatures need to be limited to less than 400ºC !!! Ø Forming single crystal silicon requires ~1, 200ºC Ø Forming transistors in single crystal silicon requires ~800ºC Ø The TSV solution overcame the temperature challenge by forming the second tier transistors on an independent wafer, then thinning and bonding it over the bottom wafer (‘parallel’) The limitations: Ø Wafer to wafer misalignment ~ 1µ Ø Overlaying wafer could not be thinned to less than 50µ

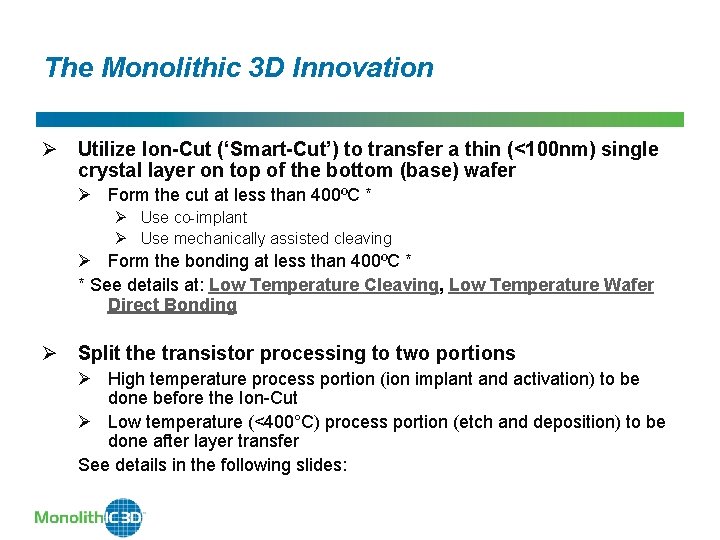

The Monolithic 3 D Innovation Ø Utilize Ion-Cut (‘Smart-Cut’) to transfer a thin (<100 nm) single crystal layer on top of the bottom (base) wafer Ø Form the cut at less than 400ºC * Ø Use co-implant Ø Use mechanically assisted cleaving Ø Form the bonding at less than 400ºC * * See details at: Low Temperature Cleaving, Low Temperature Wafer Direct Bonding Ø Split the transistor processing to two portions Ø High temperature process portion (ion implant and activation) to be done before the Ion-Cut Ø Low temperature (<400°C) process portion (etch and deposition) to be done after layer transfer See details in the following slides:

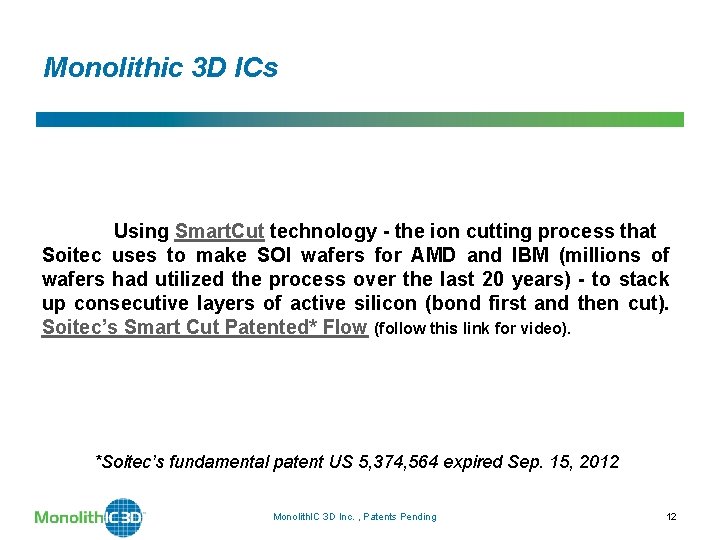

Monolithic 3 D ICs Using Smart. Cut technology - the ion cutting process that Soitec uses to make SOI wafers for AMD and IBM (millions of wafers had utilized the process over the last 20 years) - to stack up consecutive layers of active silicon (bond first and then cut). Soitec’s Smart Cut Patented* Flow (follow this link for video). *Soitec’s fundamental patent US 5, 374, 564 expired Sep. 15, 2012 Monolith. IC 3 D Inc. , Patents Pending 12

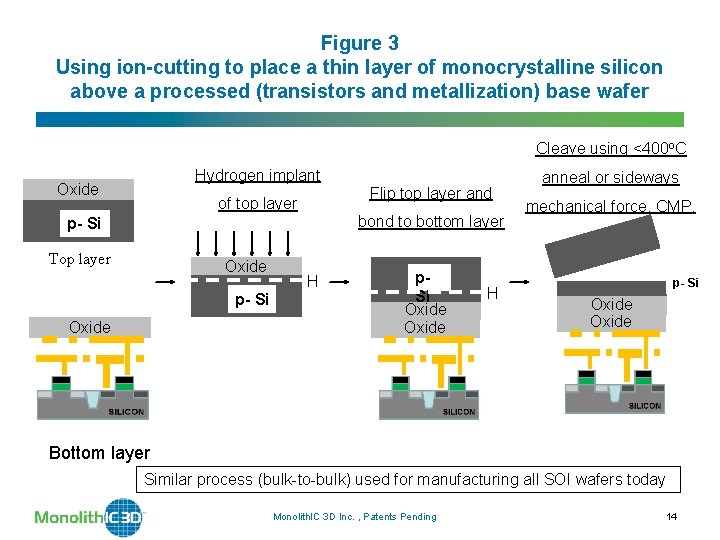

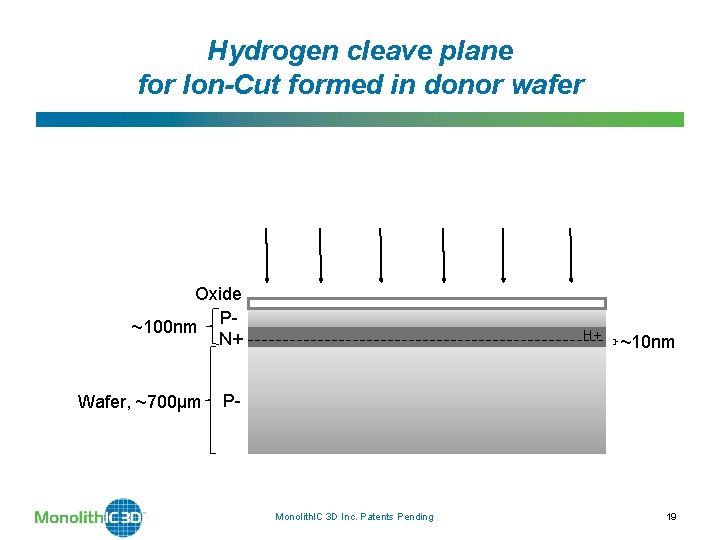

Monolithic 3 D ICs Ion cutting: the key idea is that if you implant a thin layer of H+ ions into a single crystal of silicon, the ions will weaken the bonds between the neighboring silicon atoms, creating a fracture plane (Figure 3). Judicious force will then precisely break the wafer at the plane of the H+ implant, allowing you to in-effect peel off very thin layer. This technique is currently being used to produce the most advanced transistors (Fully Depleted SOI, UTBB transistors – Ultra Thin Body and BOX), forming monocrystalline silicon layers that are less than 10 nm thick. Monolith. IC 3 D Inc. , Patents Pending 13

Figure 3 Using ion-cutting to place a thin layer of monocrystalline silicon above a processed (transistors and metallization) base wafer Cleave using <400 o. C Hydrogen implant Oxide Flip top layer and of top layer bond to bottom layer p- Si Top layer Oxide p- Si Oxide H p. Si Oxide H anneal or sideways mechanical force. CMP. p- Si Oxide Bottom layer Similar process (bulk-to-bulk) used for manufacturing all SOI wafers today Monolith. IC 3 D Inc. , Patents Pending 14

Chapter 2 Monolithic 3 D RCAT Monolith. IC 3 D Inc. Patents Pending 15

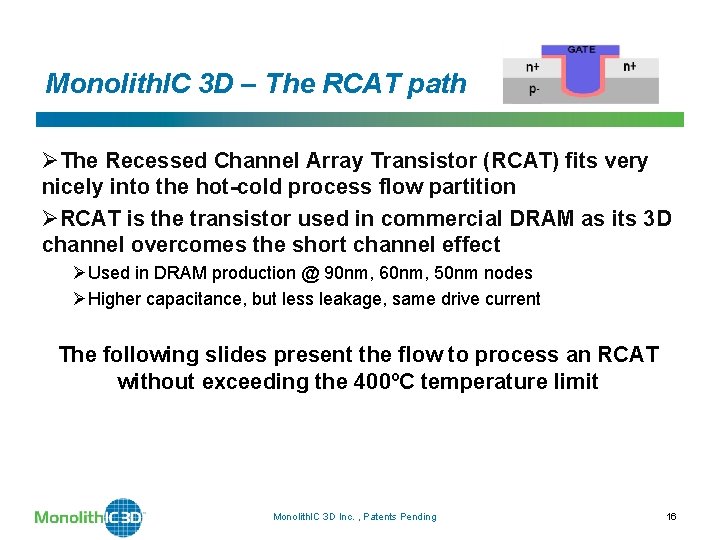

Monolith. IC 3 D – The RCAT path ØThe Recessed Channel Array Transistor (RCAT) fits very nicely into the hot-cold process flow partition ØRCAT is the transistor used in commercial DRAM as its 3 D channel overcomes the short channel effect ØUsed in DRAM production @ 90 nm, 60 nm, 50 nm nodes ØHigher capacitance, but less leakage, same drive current The following slides present the flow to process an RCAT without exceeding the 400ºC temperature limit Monolith. IC 3 D Inc. , Patents Pending 16

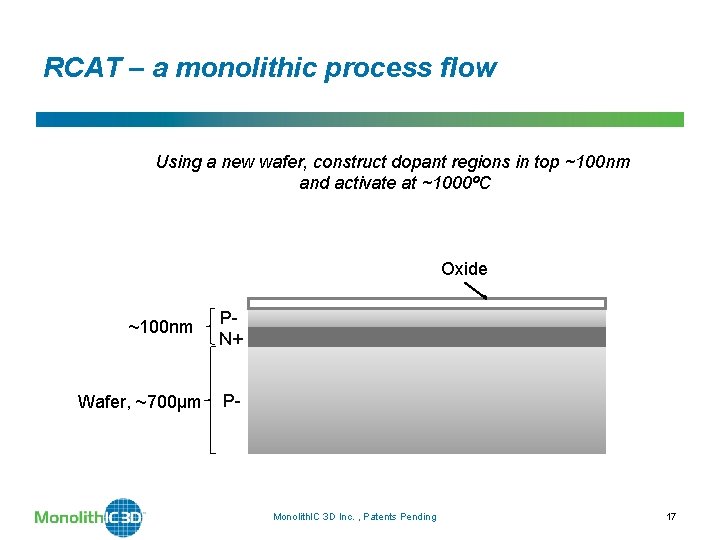

RCAT – a monolithic process flow Using a new wafer, construct dopant regions in top ~100 nm and activate at ~1000ºC Oxide ~100 nm PN+ Wafer, ~700µm P- Monolith. IC 3 D Inc. , Patents Pending 17

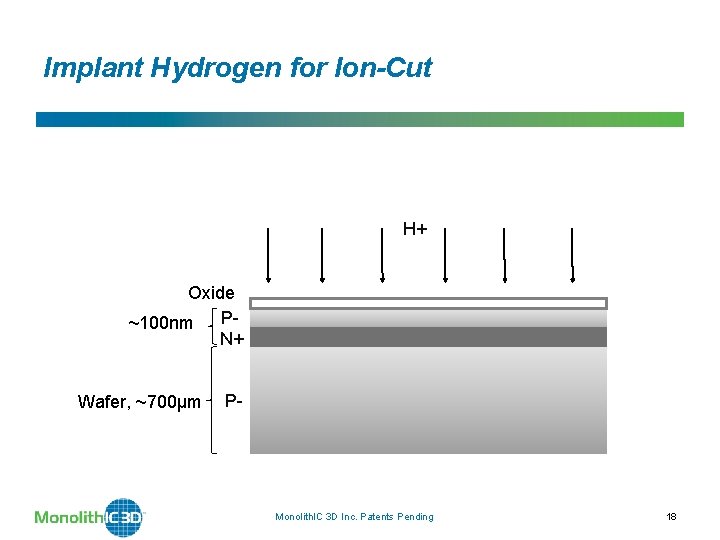

Implant Hydrogen for Ion-Cut H+ Oxide ~100 nm PN+ Wafer, ~700µm P- Monolith. IC 3 D Inc. Patents Pending 18

Hydrogen cleave plane for Ion-Cut formed in donor wafer Oxide P~100 nm N+ Wafer, ~700µm H+ ~10 nm P- Monolith. IC 3 D Inc. Patents Pending 19

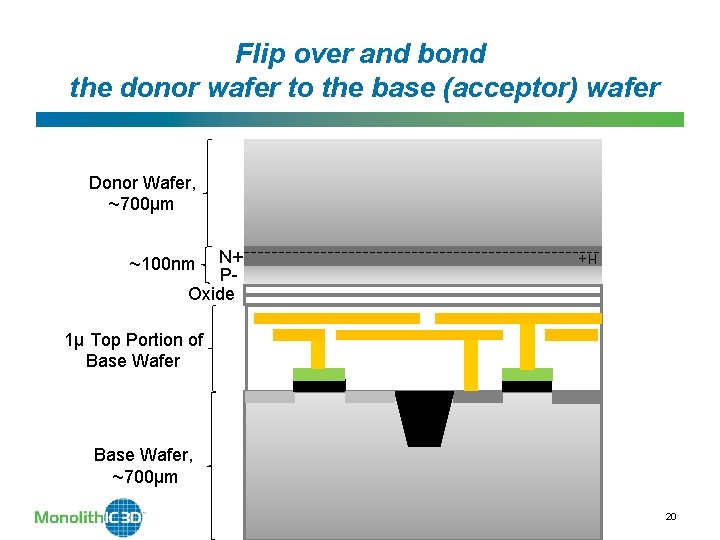

Flip over and bond the donor wafer to the base (acceptor) wafer Donor Wafer, ~700µm N+ POxide H+ ~100 nm 1µ Top Portion of Base Wafer, ~700µm Monolith. IC 3 D Inc. Patents Pending 20

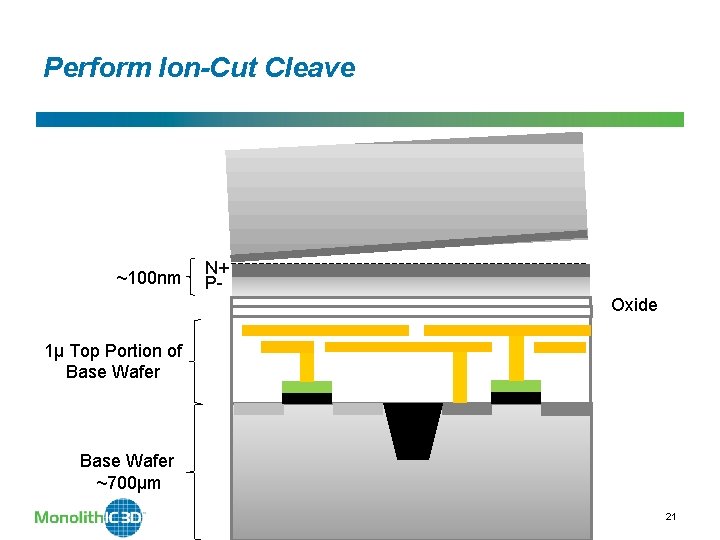

Perform Ion-Cut Cleave ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 21

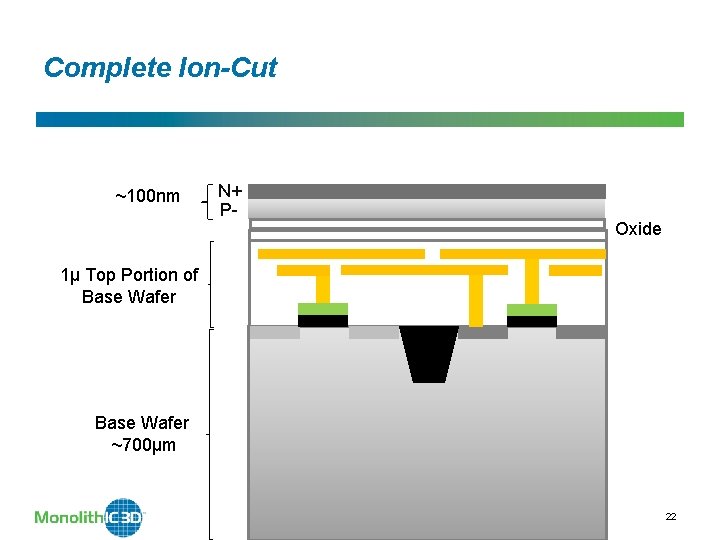

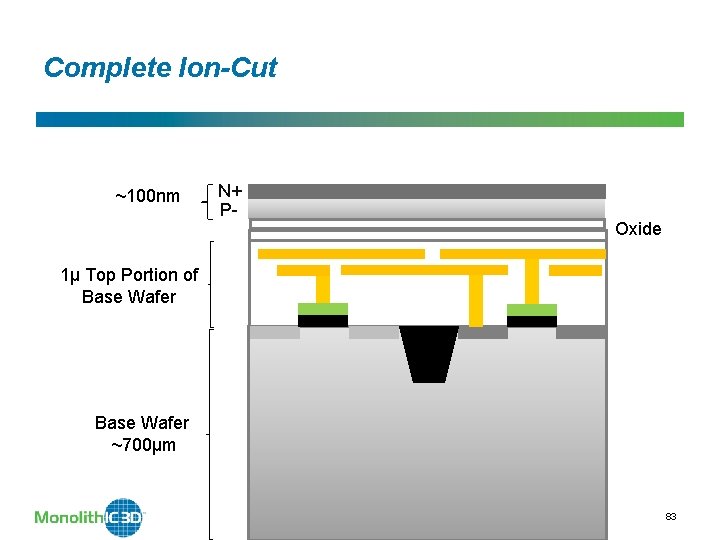

Complete Ion-Cut ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 22

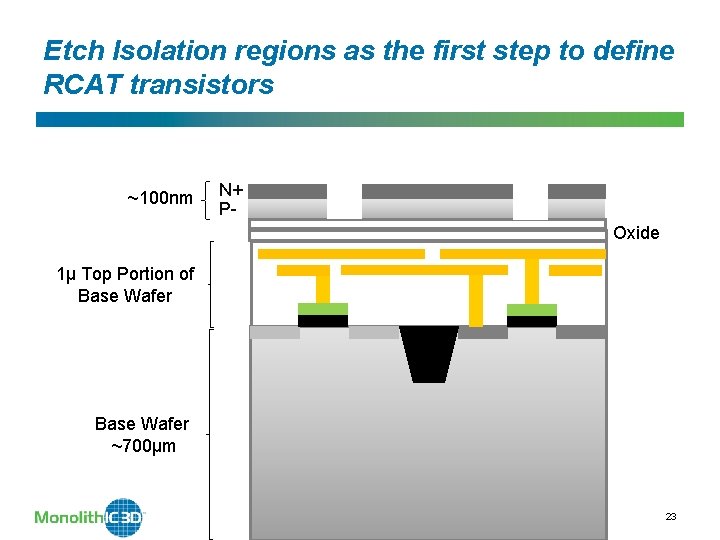

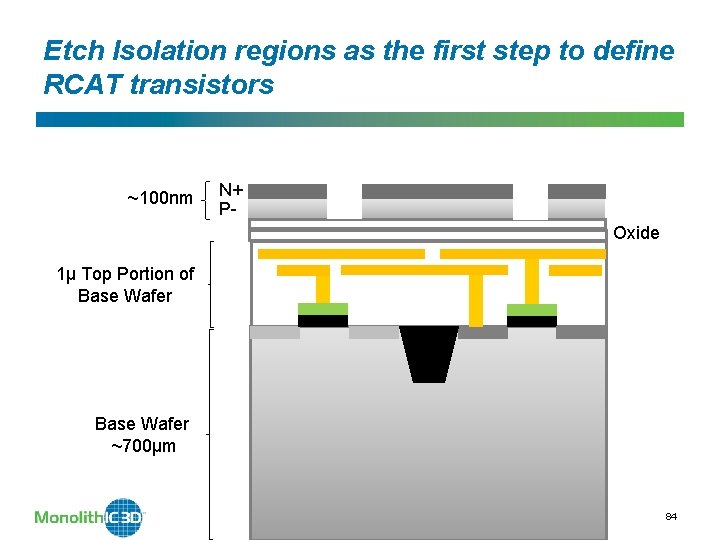

Etch Isolation regions as the first step to define RCAT transistors ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 23

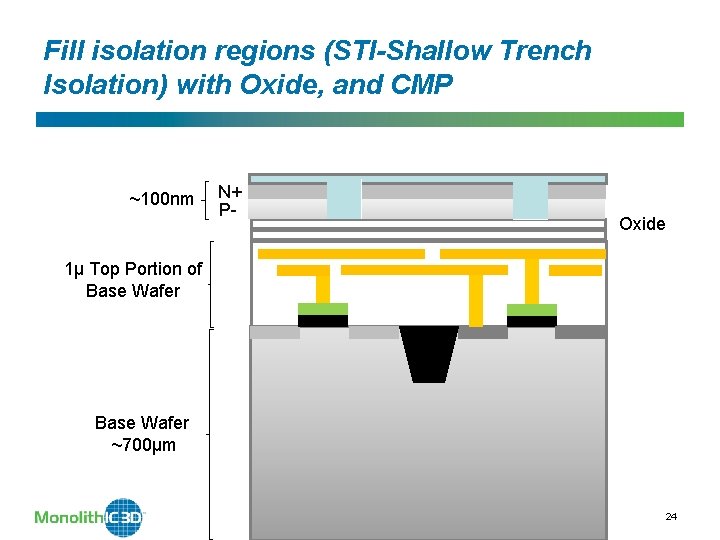

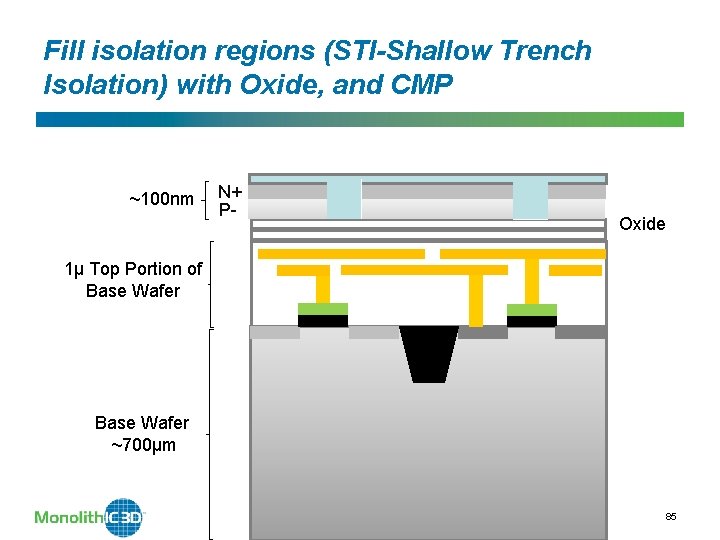

Fill isolation regions (STI-Shallow Trench Isolation) with Oxide, and CMP ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 24

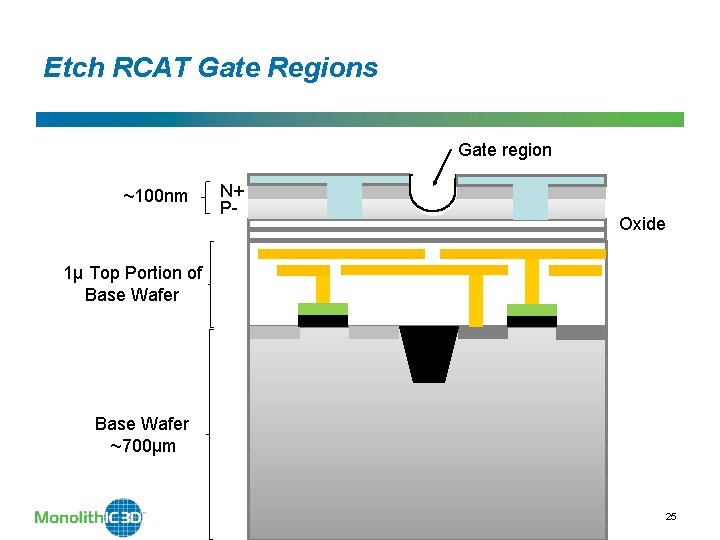

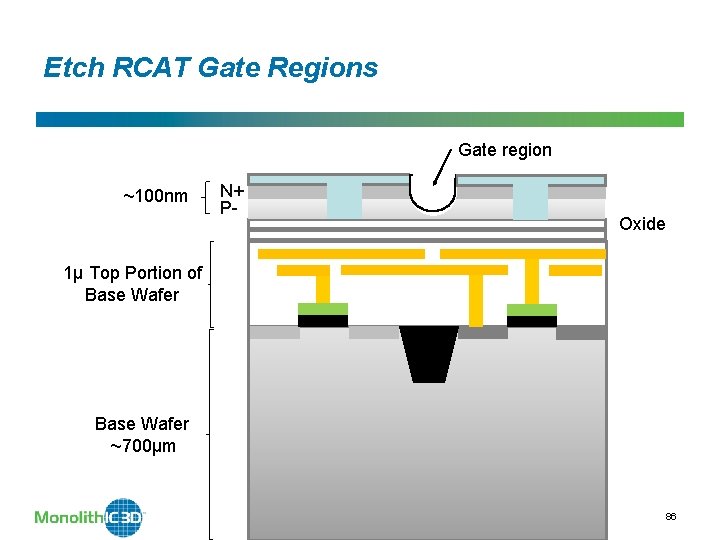

Etch RCAT Gate Regions Gate region ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 25

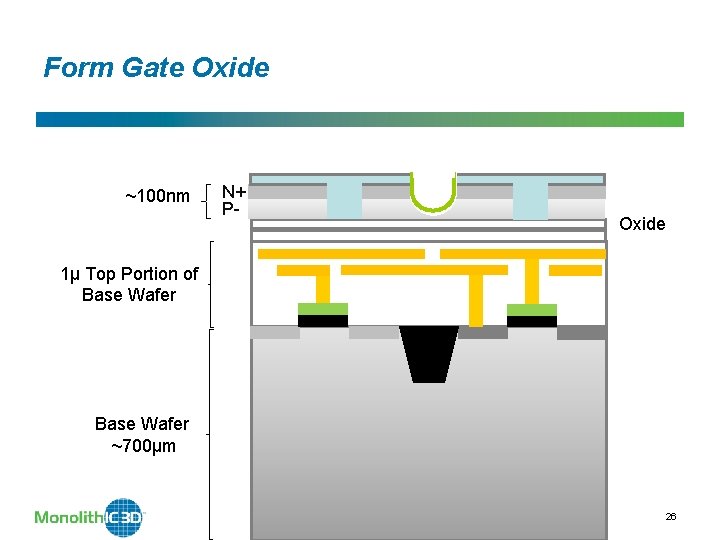

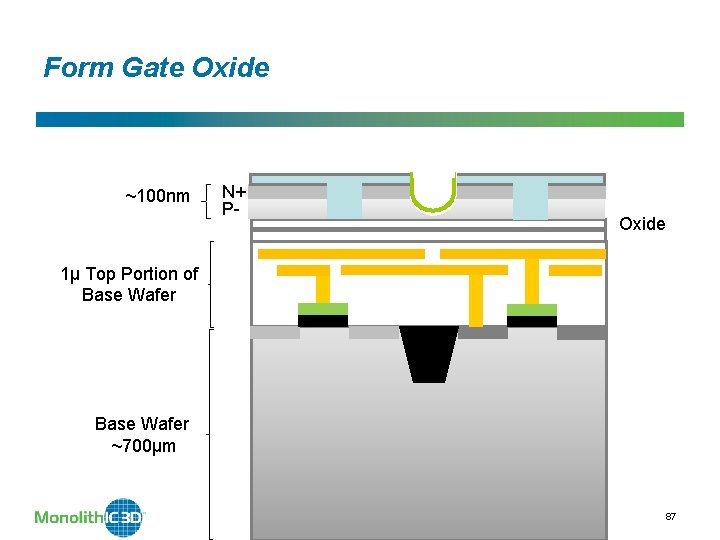

Form Gate Oxide ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 26

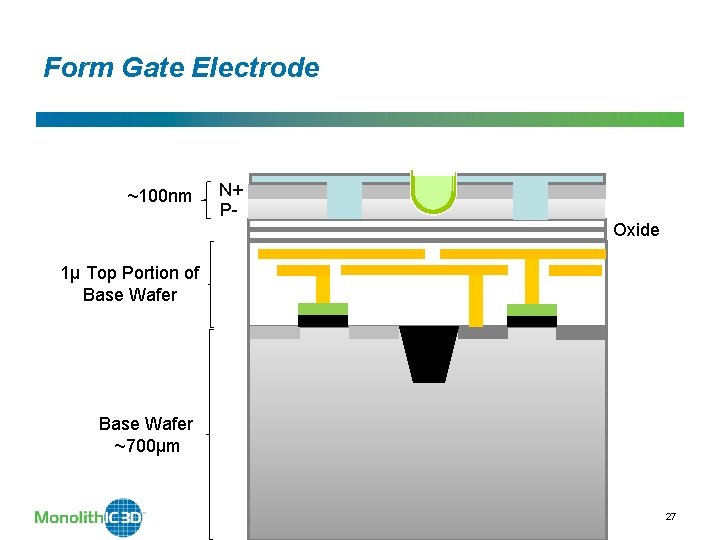

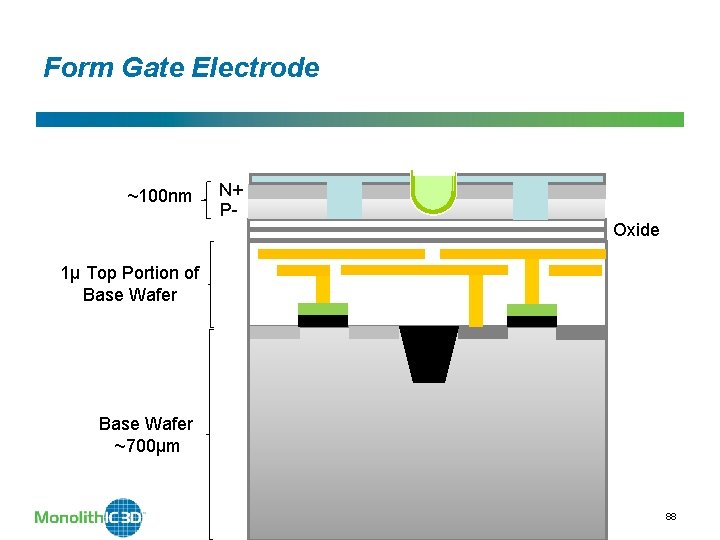

Form Gate Electrode ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 27

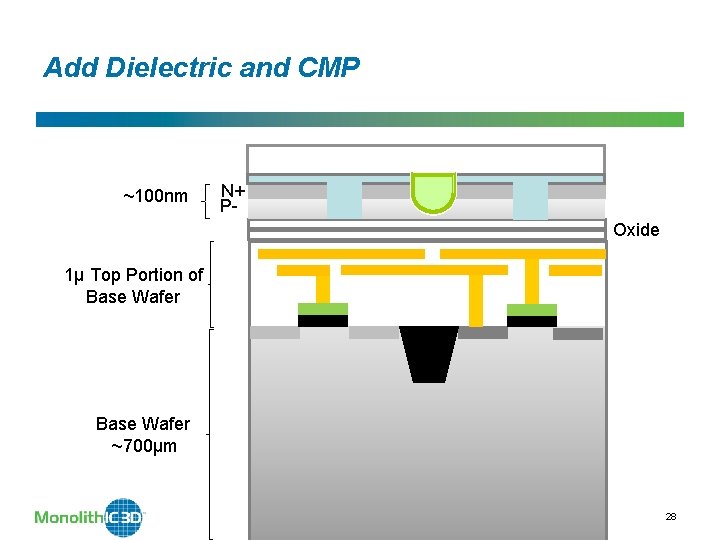

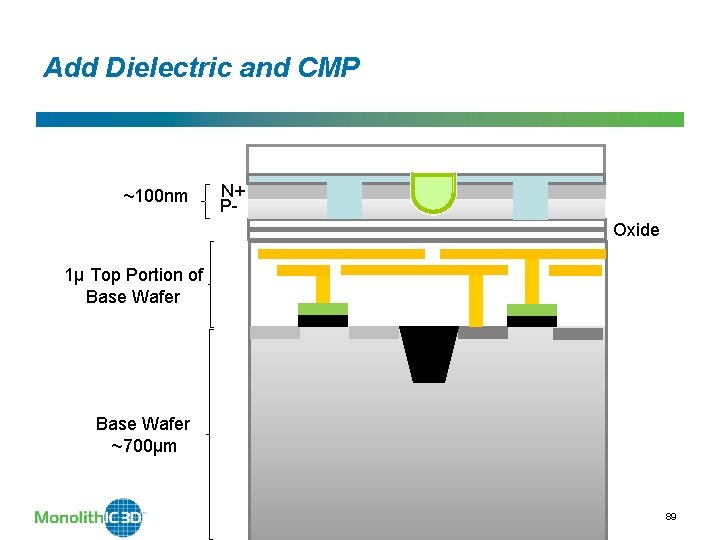

Add Dielectric and CMP ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 28

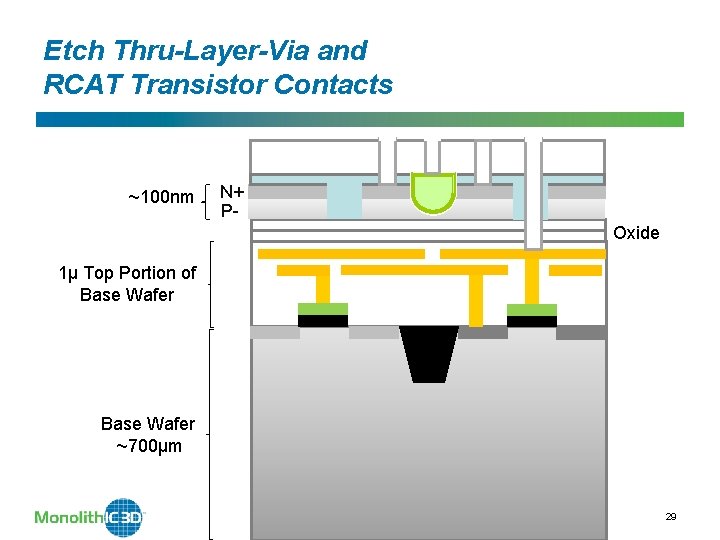

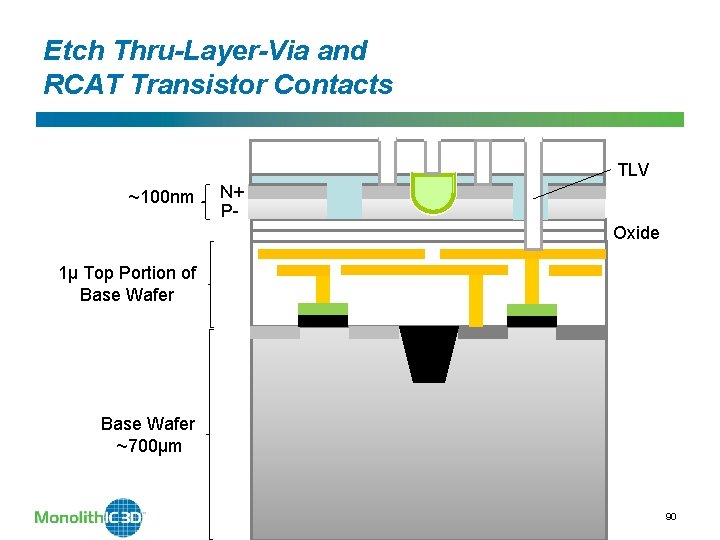

Etch Thru-Layer-Via and RCAT Transistor Contacts ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 29

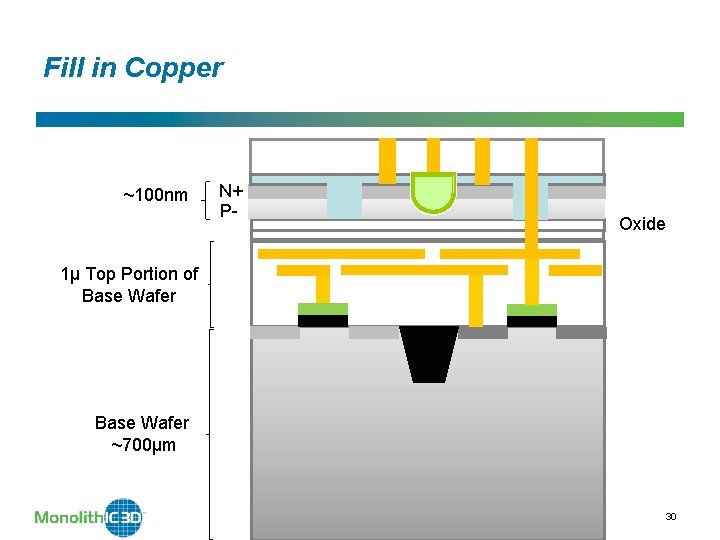

Fill in Copper ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 30

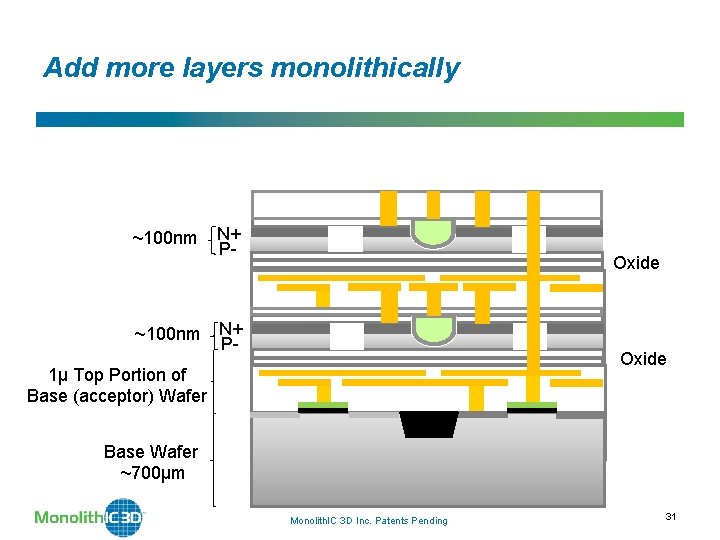

Add more layers monolithically ~100 nm N+ P- Oxide 1µ Top Portion of Base (acceptor) Wafer Base Wafer ~700µm Monolith. IC 3 D Inc. Patents Pending 31

Chapter 3 Monolithic 3 D HKMG Monolith. IC 3 D Inc. Patents Pending 32

Technology The monolithic 3 D IC technology is applied to produce monolithically stacked high performance High-k Metal Gate (HKMG) devices, the world’s most advanced production transistors. 3 D Monolithic State-of-the-Art transistors are formed with ion-cut applied to a gate-last process, combined with a low temperature face-up layer transfer, repeating layouts, and an innovative inter-layer via (ILV) alignment scheme. Monolithic 3 D IC provides a path to reduce logic, SOC, and memory costs without investing in expensive scaling down. Monolith. IC 3 D Inc. Patents Pending 33

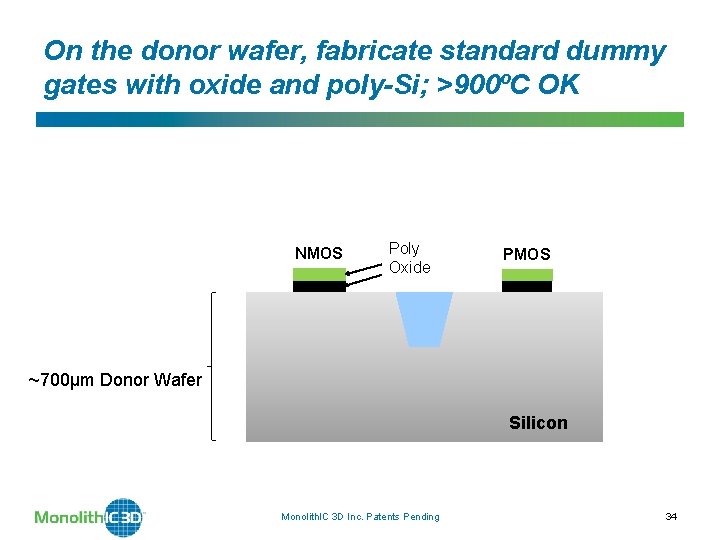

On the donor wafer, fabricate standard dummy gates with oxide and poly-Si; >900ºC OK NMOS Poly Oxide PMOS ~700µm Donor Wafer Silicon Monolith. IC 3 D Inc. Patents Pending 34

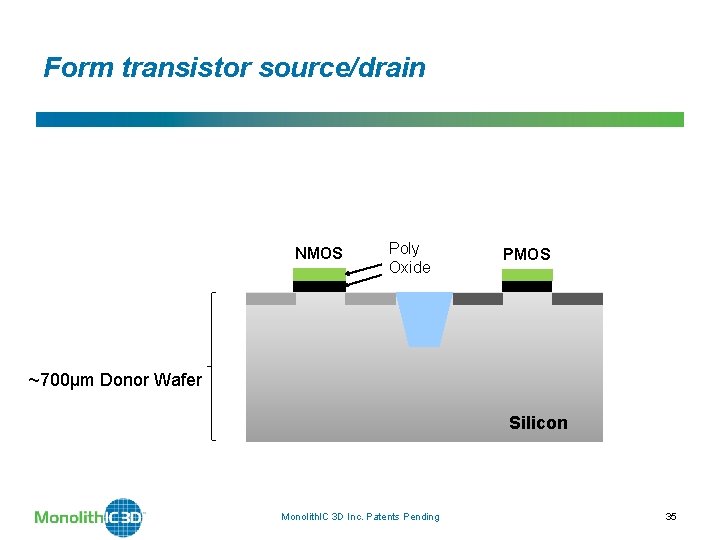

Form transistor source/drain NMOS Poly Oxide PMOS ~700µm Donor Wafer Silicon Monolith. IC 3 D Inc. Patents Pending 35

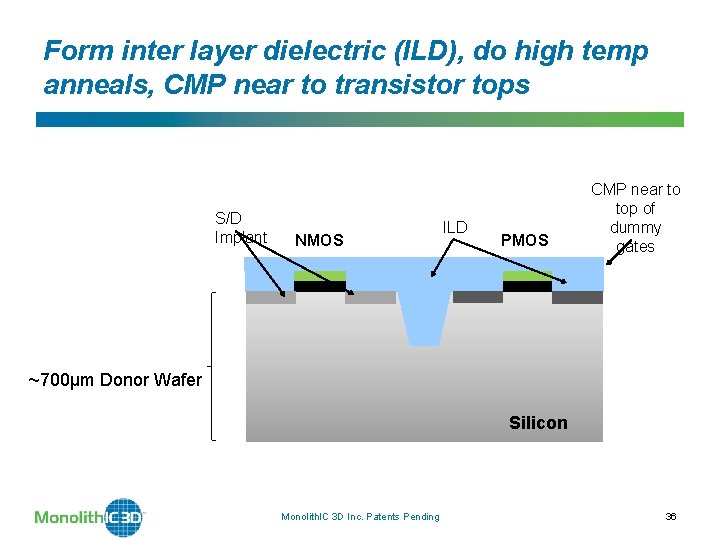

Form inter layer dielectric (ILD), do high temp anneals, CMP near to transistor tops S/D Implant NMOS ILD PMOS CMP near to top of dummy gates ~700µm Donor Wafer Silicon Monolith. IC 3 D Inc. Patents Pending 36

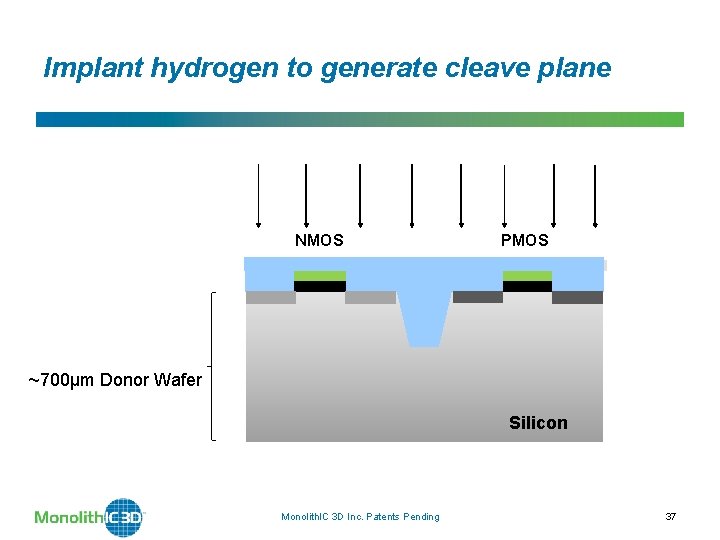

Implant hydrogen to generate cleave plane NMOS PMOS ~700µm Donor Wafer Silicon Monolith. IC 3 D Inc. Patents Pending 37

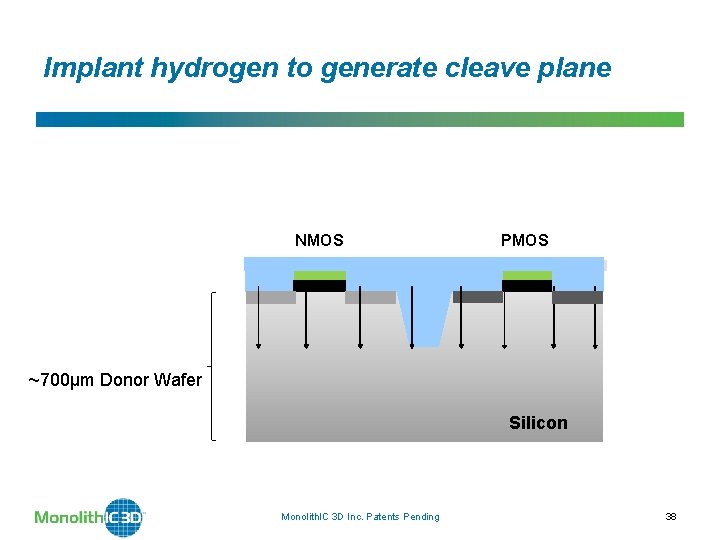

Implant hydrogen to generate cleave plane NMOS PMOS ~700µm Donor Wafer Silicon Monolith. IC 3 D Inc. Patents Pending 38

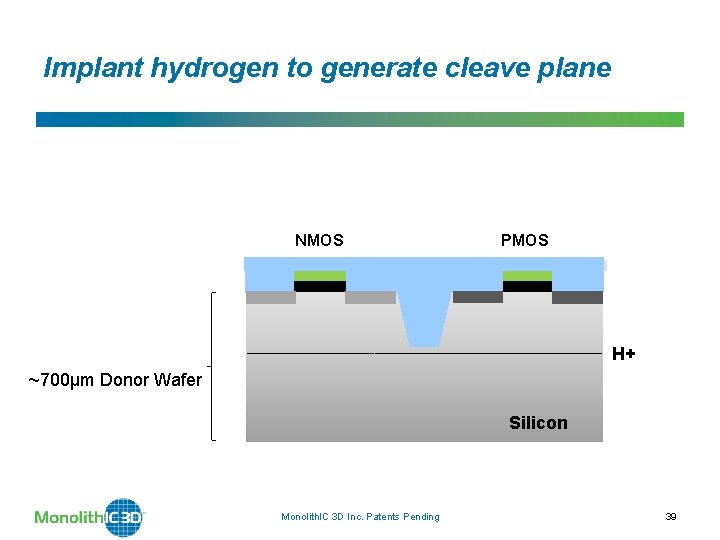

Implant hydrogen to generate cleave plane NMOS PMOS H+ ~700µm Donor Wafer Silicon Monolith. IC 3 D Inc. Patents Pending 39

Bond donor wafer to carrier wafer ~700µm Carrier Wafer H+ ~700µm Donor Wafer Silicon Monolith. IC 3 D Inc. Patents Pending 40

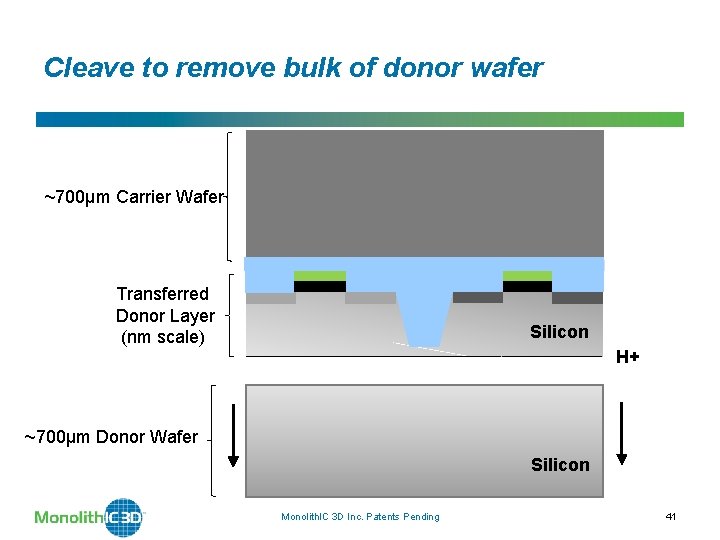

Cleave to remove bulk of donor wafer ~700µm Carrier Wafer Transferred Donor Layer (nm scale) Silicon H+ ~700µm Donor Wafer Silicon Monolith. IC 3 D Inc. Patents Pending 41

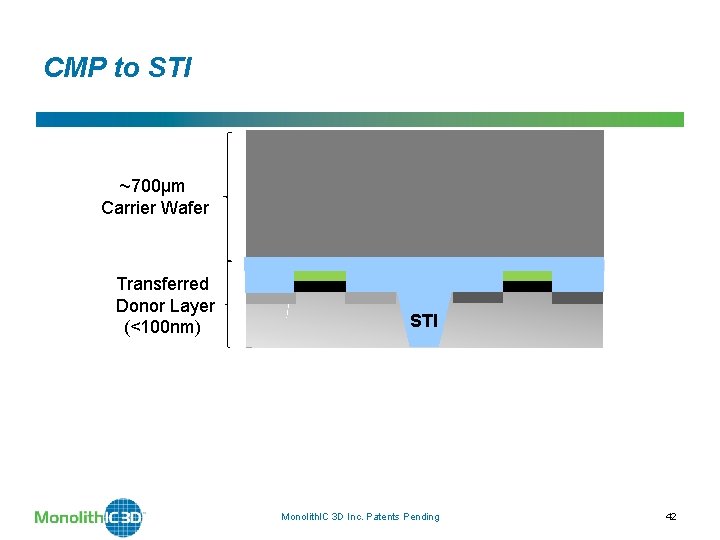

CMP to STI ~700µm Carrier Wafer Transferred Donor Layer (<100 nm) STI Monolith. IC 3 D Inc. Patents Pending 42

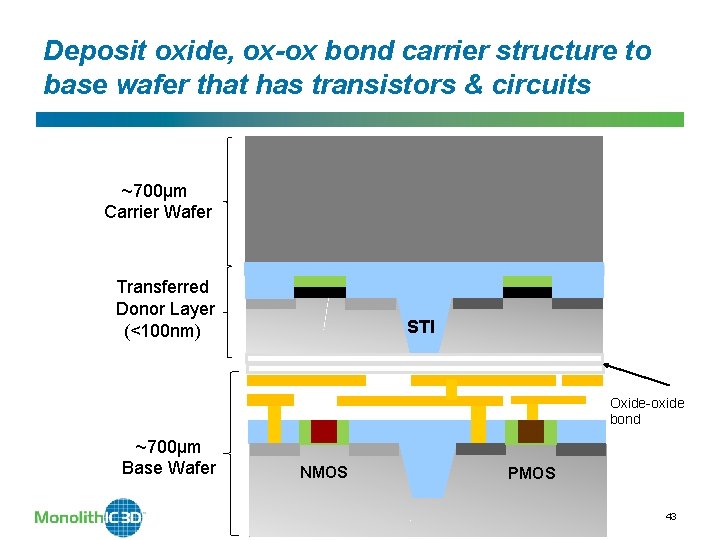

Deposit oxide, ox-ox bond carrier structure to base wafer that has transistors & circuits ~700µm Carrier Wafer Transferred Donor Layer (<100 nm) STI Oxide-oxide bond ~700µm Base Wafer NMOS Monolith. IC 3 D Inc. Patents Pending PMOS 43

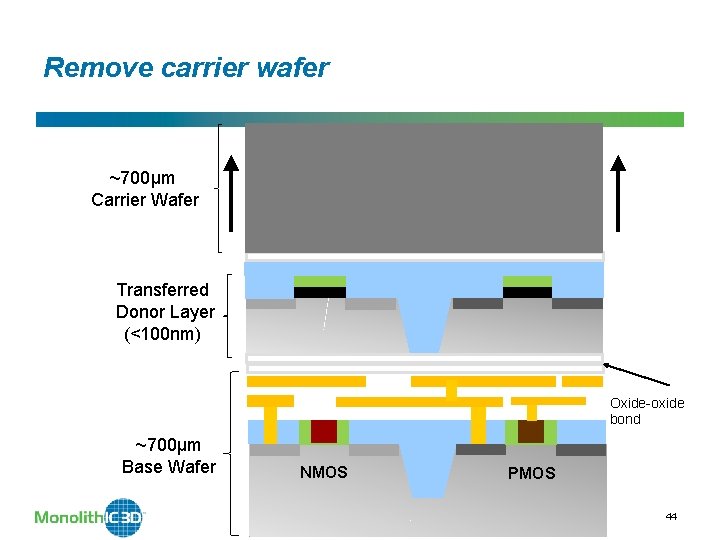

Remove carrier wafer ~700µm Carrier Wafer Transferred Donor Layer (<100 nm) Oxide-oxide bond ~700µm Base Wafer NMOS Monolith. IC 3 D Inc. Patents Pending PMOS 44

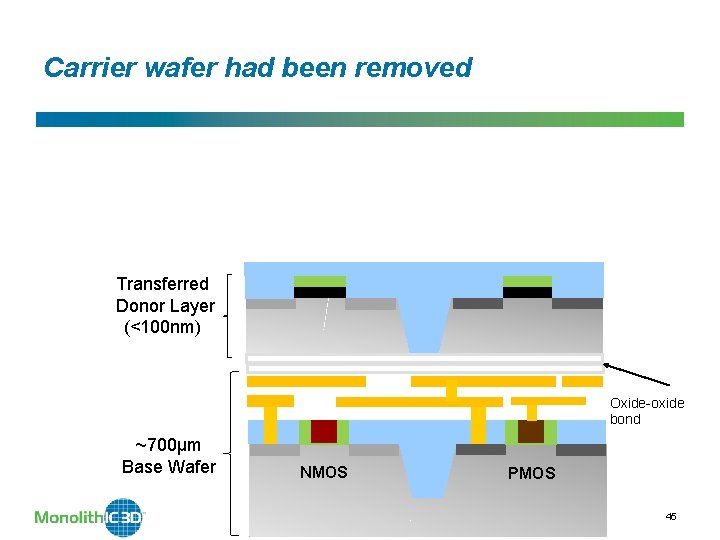

Carrier wafer had been removed Transferred Donor Layer (<100 nm) Oxide-oxide bond ~700µm Base Wafer NMOS Monolith. IC 3 D Inc. Patents Pending PMOS 45

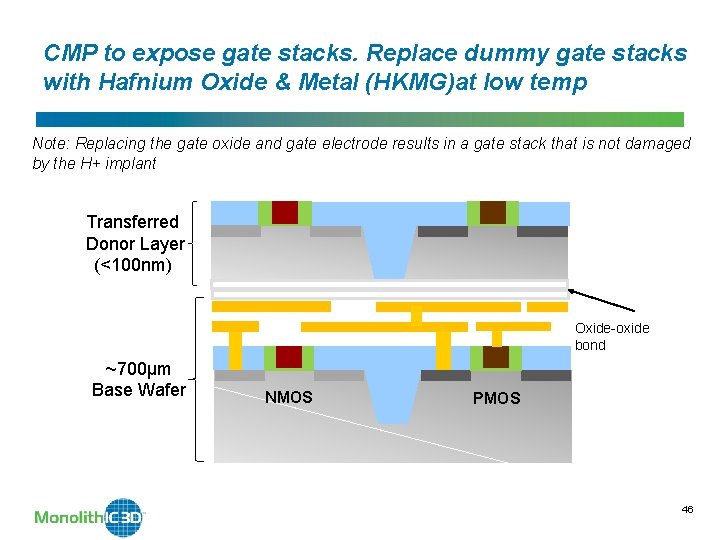

CMP to expose gate stacks. Replace dummy gate stacks with Hafnium Oxide & Metal (HKMG)at low temp Note: Replacing the gate oxide and gate electrode results in a gate stack that is not damaged by the H+ implant Transferred Donor Layer (<100 nm) Oxide-oxide bond ~700µm Base Wafer NMOS PMOS Monolith. IC 3 D Inc. Patents Pending 46

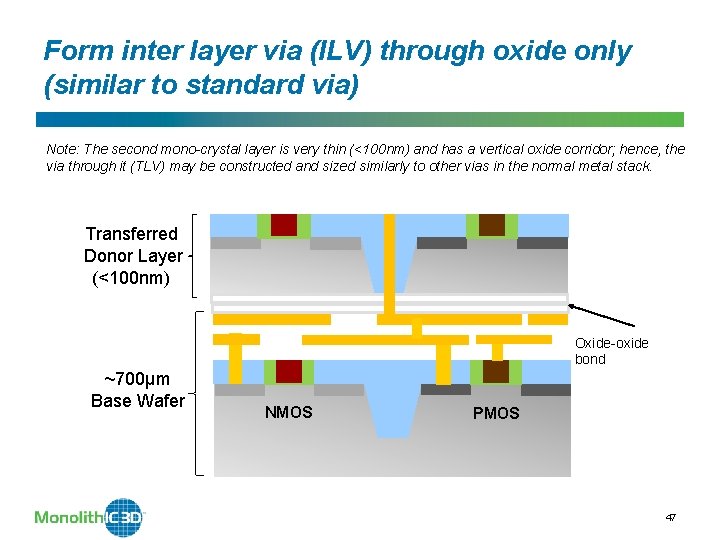

Form inter layer via (ILV) through oxide only (similar to standard via) Note: The second mono-crystal layer is very thin (<100 nm) and has a vertical oxide corridor; hence, the via through it (TLV) may be constructed and sized similarly to other vias in the normal metal stack. Transferred Donor Layer (<100 nm) Oxide-oxide bond ~700µm Base Wafer NMOS PMOS Monolith. IC 3 D Inc. Patents Pending 47

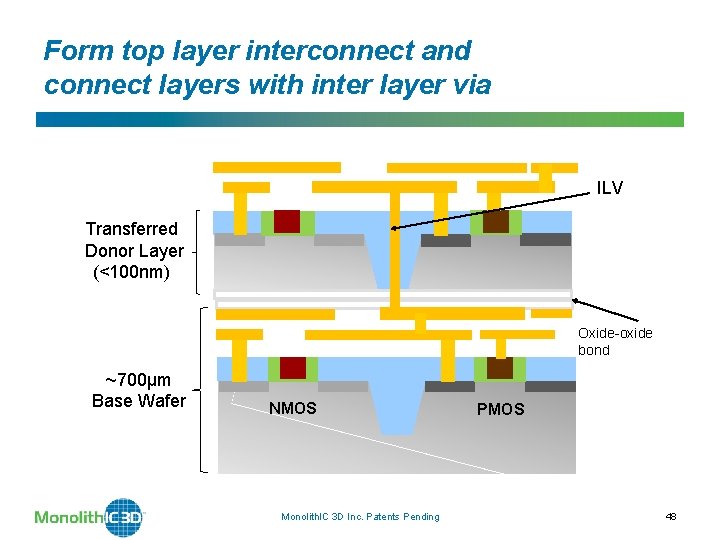

Form top layer interconnect and connect layers with inter layer via ILV Transferred Donor Layer (<100 nm) Oxide-oxide bond ~700µm Base Wafer NMOS PMOS Monolith. IC 3 D Inc. Patents Pending 48

Benefits for RCAT and HKMG • Maximum State-of-the-Art transistor performance on multi-strata • 2 x lower power • 2 x smaller silicon area • 4 x smaller footprint • Performance of single crystal silicon transistors on all layers in the 3 DIC • Scalable: scales normally with equipment capability • Forestalls next gen litho-tool risk • High density of vertical interconnects enable innovative architectures, repair, and redundancy Monolith. IC 3 D Inc. Patents Pending 49

Chapter 4 Monolithic 3 D RC-JLT (Recessed-Channel Junction-Less Transistor) Monolith. IC 3 D Inc. Patents Pending 50

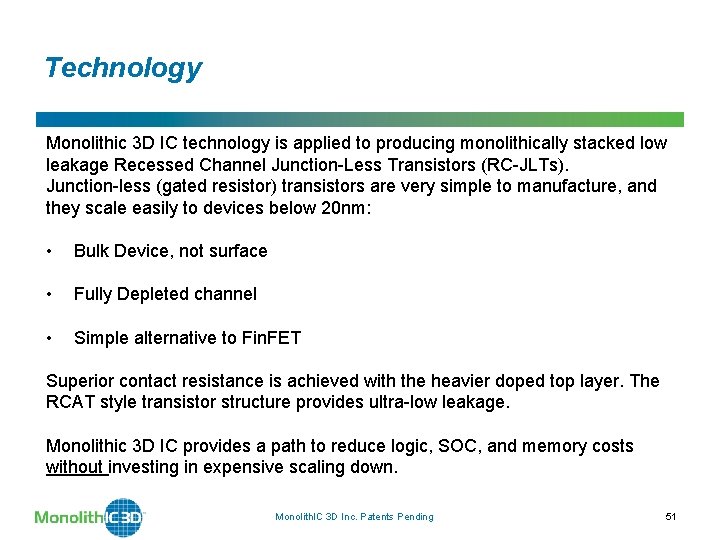

Technology Monolithic 3 D IC technology is applied to producing monolithically stacked low leakage Recessed Channel Junction-Less Transistors (RC-JLTs). Junction-less (gated resistor) transistors are very simple to manufacture, and they scale easily to devices below 20 nm: • Bulk Device, not surface • Fully Depleted channel • Simple alternative to Fin. FET Superior contact resistance is achieved with the heavier doped top layer. The RCAT style transistor structure provides ultra-low leakage. Monolithic 3 D IC provides a path to reduce logic, SOC, and memory costs without investing in expensive scaling down. Monolith. IC 3 D Inc. Patents Pending 51

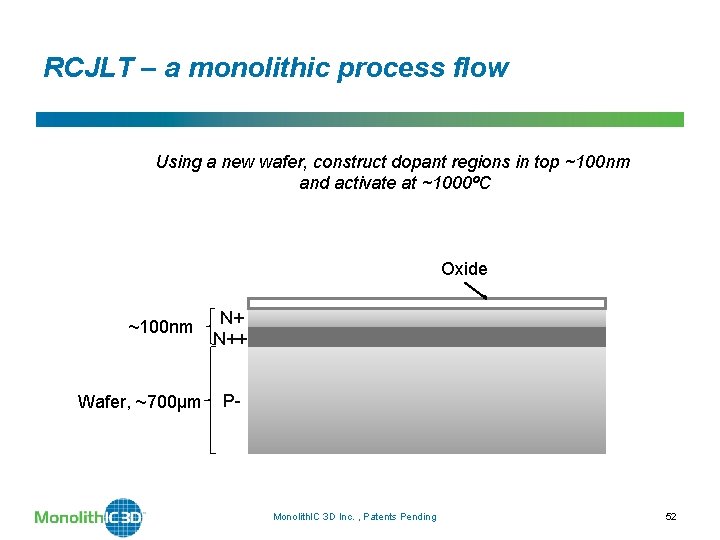

RCJLT – a monolithic process flow Using a new wafer, construct dopant regions in top ~100 nm and activate at ~1000ºC Oxide ~100 nm Wafer, ~700µm N+ N++ P- Monolith. IC 3 D Inc. , Patents Pending 52

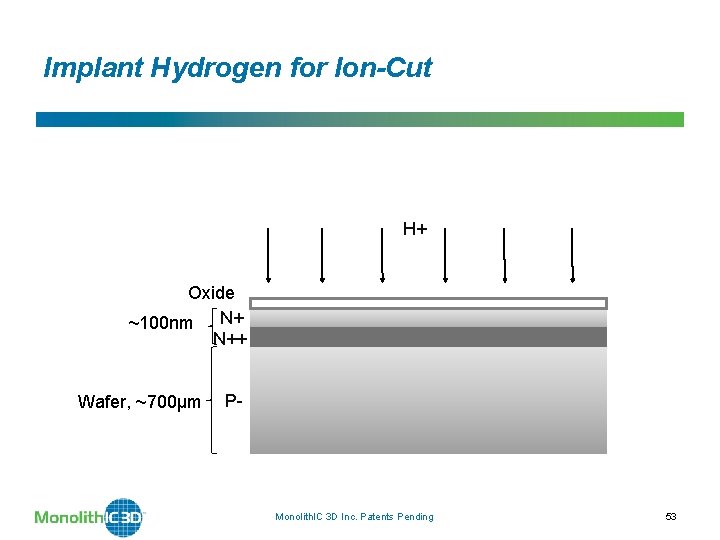

Implant Hydrogen for Ion-Cut H+ Oxide ~100 nm N+ N++ Wafer, ~700µm P- Monolith. IC 3 D Inc. Patents Pending 53

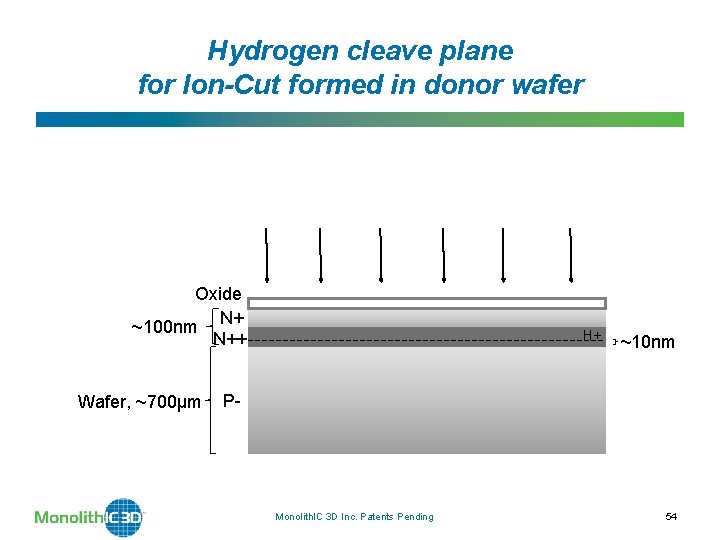

Hydrogen cleave plane for Ion-Cut formed in donor wafer Oxide N+ ~100 nm N++ Wafer, ~700µm H+ ~10 nm P- Monolith. IC 3 D Inc. Patents Pending 54

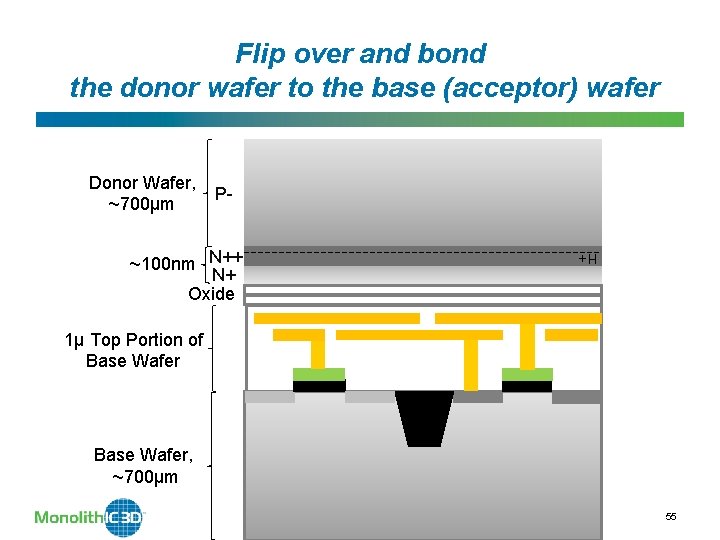

Flip over and bond the donor wafer to the base (acceptor) wafer Donor Wafer, P~700µm ~100 nm N++ N+ Oxide H+ 1µ Top Portion of Base Wafer, ~700µm Monolith. IC 3 D Inc. Patents Pending 55

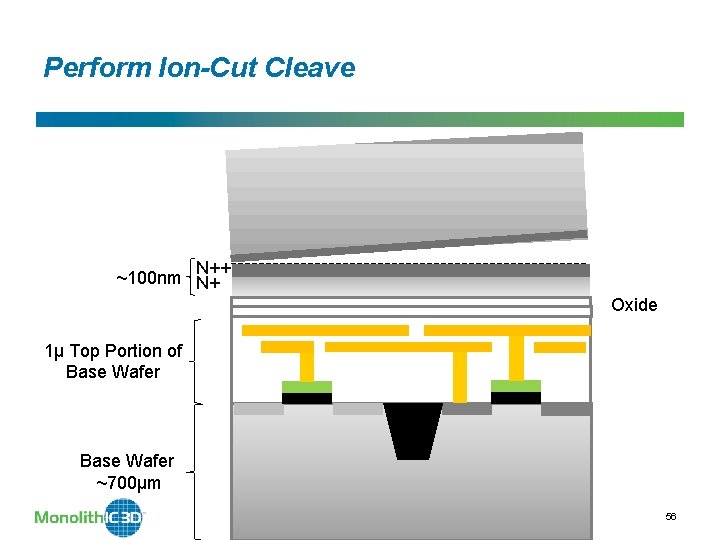

Perform Ion-Cut Cleave N++ ~100 nm N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 56

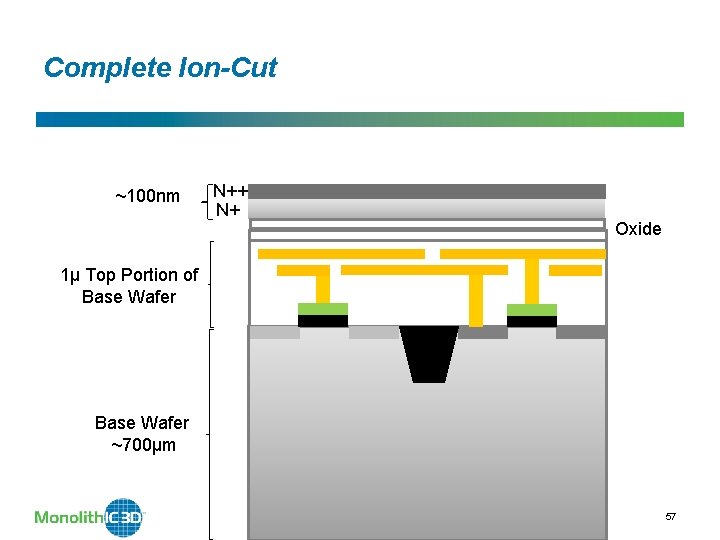

Complete Ion-Cut ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 57

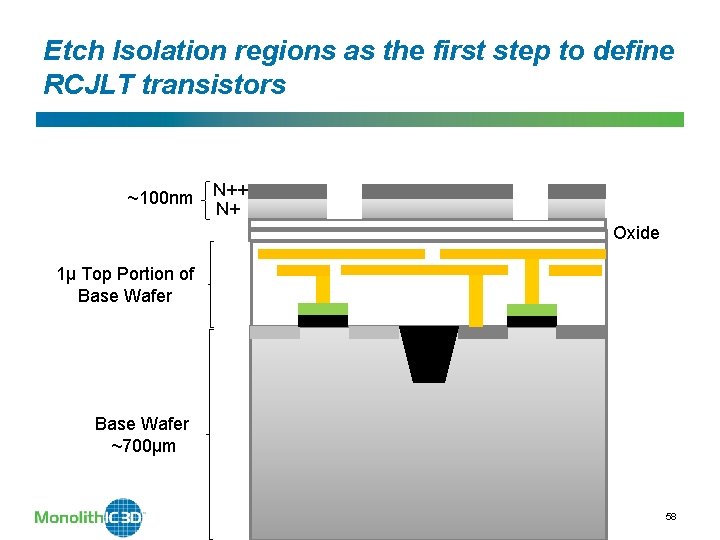

Etch Isolation regions as the first step to define RCJLT transistors ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 58

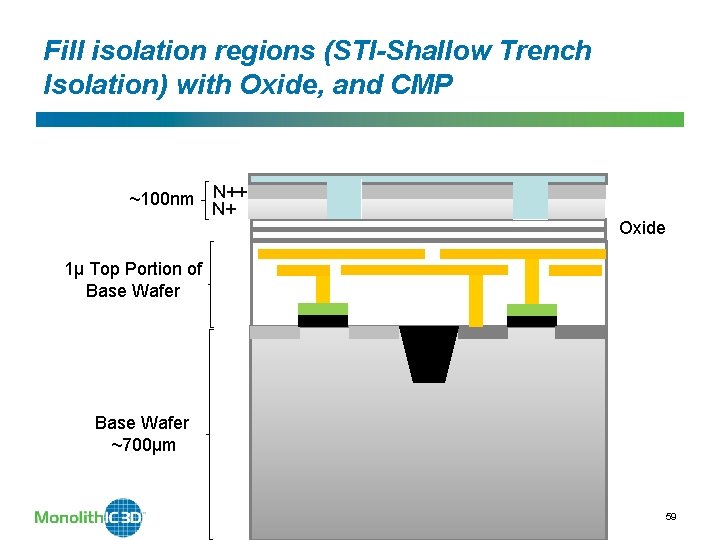

Fill isolation regions (STI-Shallow Trench Isolation) with Oxide, and CMP ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 59

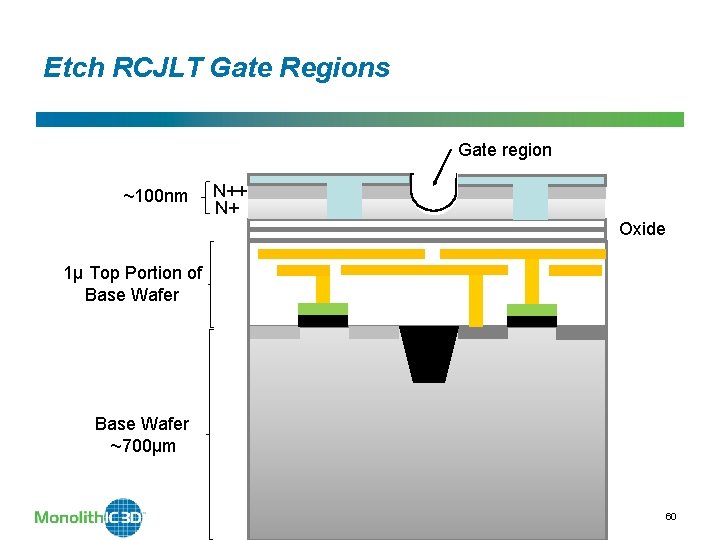

Etch RCJLT Gate Regions Gate region ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 60

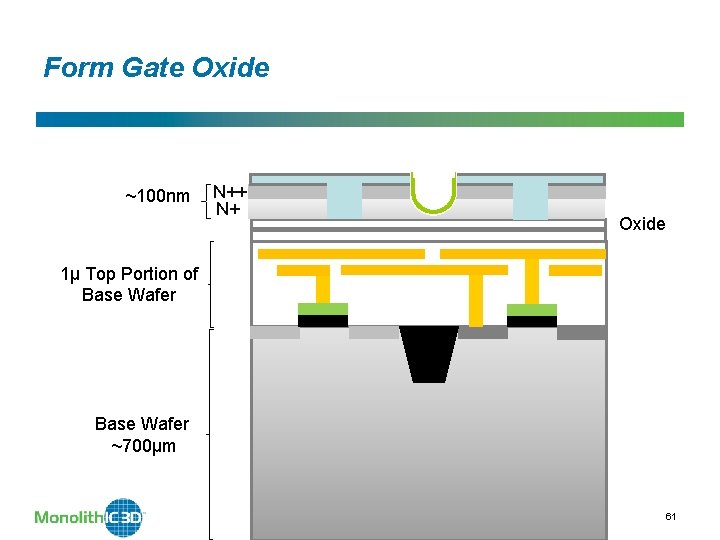

Form Gate Oxide ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 61

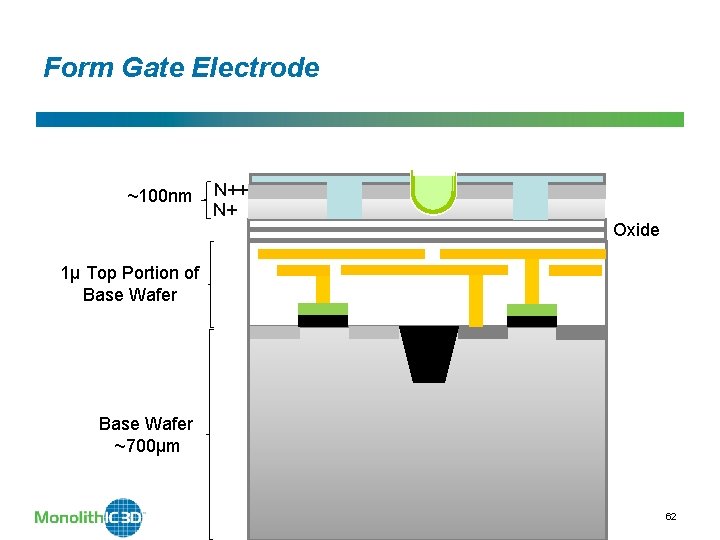

Form Gate Electrode ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 62

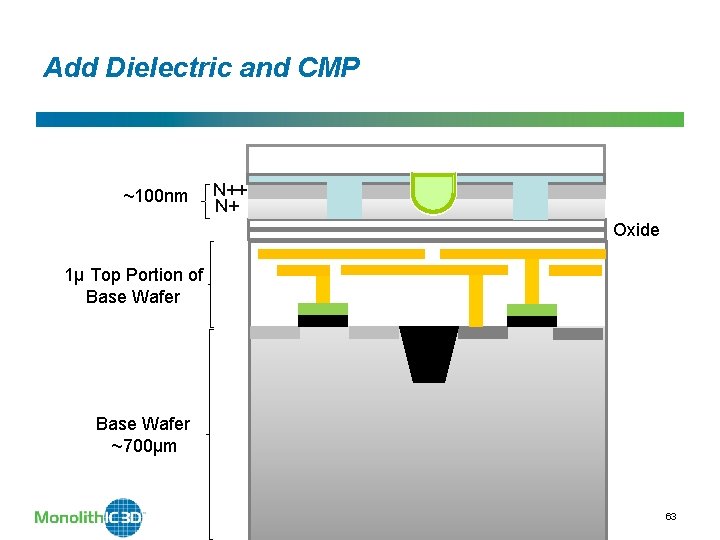

Add Dielectric and CMP ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 63

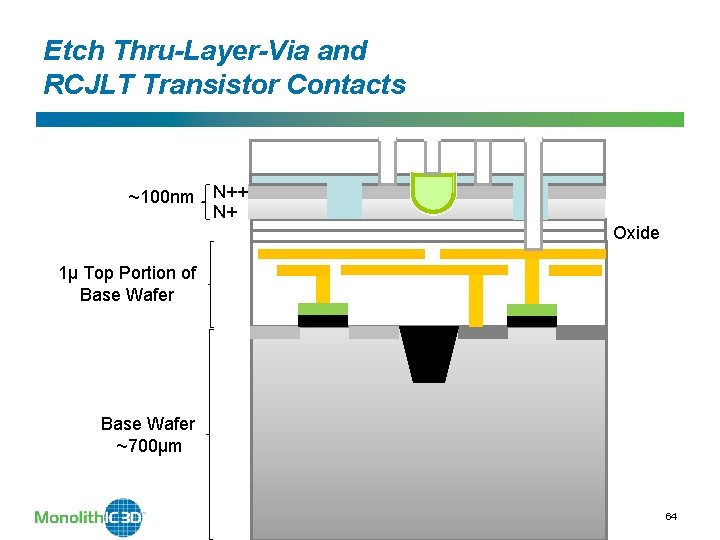

Etch Thru-Layer-Via and RCJLT Transistor Contacts ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 64

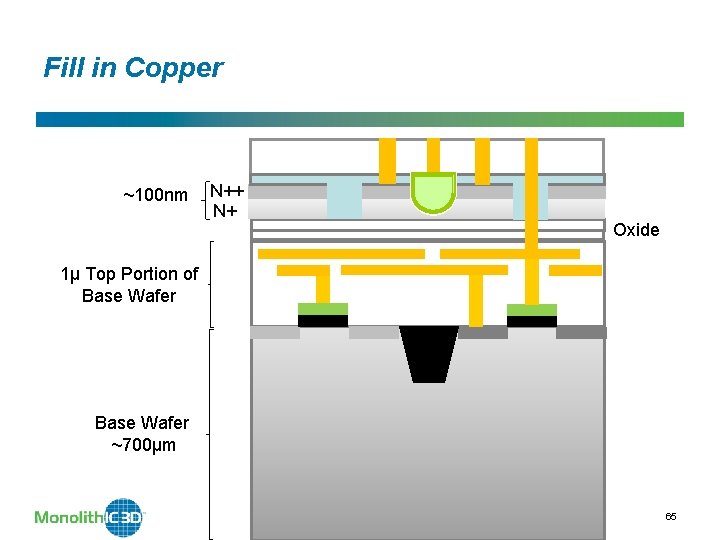

Fill in Copper ~100 nm N++ N+ Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 65

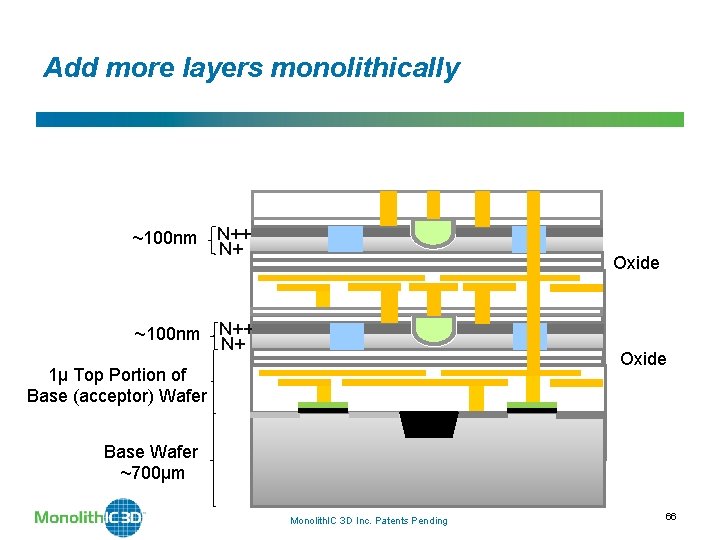

Add more layers monolithically ~100 nm N++ N+ Oxide 1µ Top Portion of Base (acceptor) Wafer Base Wafer ~700µm Monolith. IC 3 D Inc. Patents Pending 66

Benefits for RCJLT • 2 x lower power • 2 x smaller silicon area • 4 x smaller footprint • Layer to layer interconnect density at close to full lithographic resolution and alignment • Performance of single crystal silicon transistors on all layers in the 3 D IC • Scalable: scales naturally with equipment capability • Forestalls next gen litho-tool risk • Also useful as Anti-Fuse FPGA programming transistors: programmable interconnect is 10 x-50 x smaller & lower power than SRAM FPGA • Base logic circuits could be UT-BBOX, Fin. FET, or JLT CMOS logic devices Monolith. IC 3 D Inc. Patents Pending 67

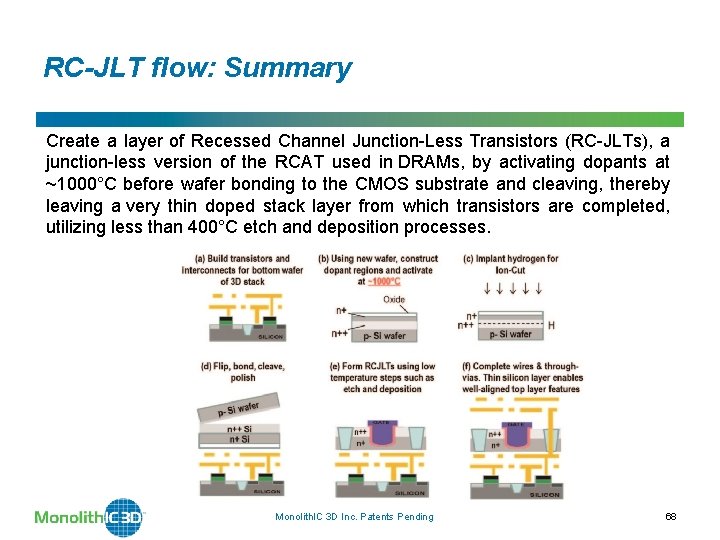

RC-JLT flow: Summary Create a layer of Recessed Channel Junction-Less Transistors (RC-JLTs), a junction-less version of the RCAT used in DRAMs, by activating dopants at ~1000°C before wafer bonding to the CMOS substrate and cleaving, thereby leaving a very thin doped stack layer from which transistors are completed, utilizing less than 400°C etch and deposition processes. Monolith. IC 3 D Inc. Patents Pending 68

Chapter 5 Monolithic 3 D e. DRAM on Logic Monolith. IC 3 D Inc. Patents Pending 69

Monolithic 3 D e. DRAM - Technology Monolithic 3 D IC technology is applied to producing monolithically stacked low leakage Recessed Channel Array Transistors (RCATs) with stacked capacitors (e. DRAM) on top of logic. Cost savings through a footprint reduction of 75% and an active silicon area reduction of 50% can be obtained by monolithically stacking the e. DRAM on top of logic. The e. DRAM and logic device layers can be independently optimized; hence, no more wasting 10 metal layers on DRAM die area. In addition, monolithic stacking enables the use of DRAM for the memory, which is 3 times more area efficient than SRAM. RCATs can be used for memory cells and decoder logic. As well, an independent refresh port allows reduced voltage and power. Short wires and close proximity of the e. DRAM to logic provides maximum performance. Monolith. IC 3 D Inc. Patents Pending 70

So. C Device Architecture (Part 1) Ø Pull out the memory to the second layer Ø About 50% of a typical So. C is embedded memory, and about 50% of the logic area is due to gate sizing buffers and repeaters. Ø Going monolithic 3 D eliminates majority of buffers and repeaters Ø Therefore, 2 stack monolithic: Ø => A Base layer with just the logic (hence, 25% of original So. C area) Ø => 2 nd layer has the e. DRAM with stack capacitor Ø RESULT: 3 D silicon footprint is about 25% of original 2 D! 71

So. C Device Architecture (Part 2) Ø 25% of the area of e. DRAM (1 T) needs to replace 50% of the equivalent SRAM Ø 1 T vs. ½ of 6 T ~ 1: 3, could be used for: Ø Use older node for the e. DRAM, with optional additional port for independent refresh Ø Additional advantage for dedicated layer of e. DRAM Ø Optimized process Ø Only 3 metal layers, no die area wasted on logic 10 metal layers Ø Repetitive memory structure – easy for litho and fab 72

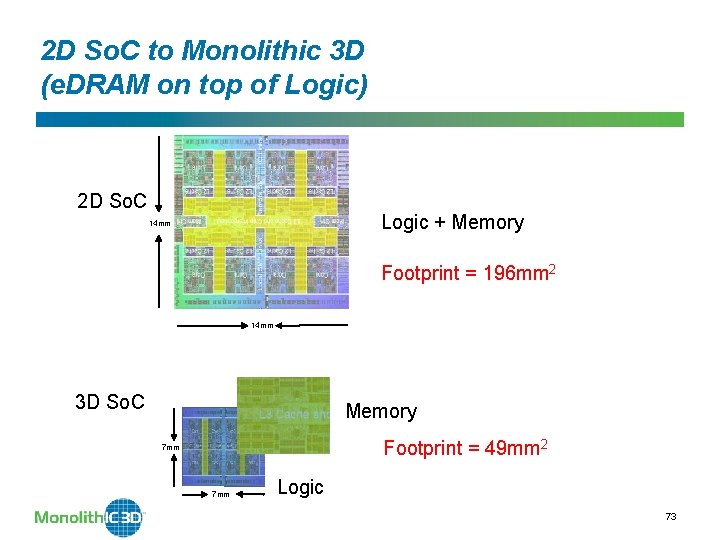

2 D So. C to Monolithic 3 D (e. DRAM on top of Logic) 2 D So. C Logic + Memory 14 mm Footprint = 196 mm 2 14 mm 3 D So. C Memory Footprint = 49 mm 2 7 mm Logic 73

e. RAM portion in So. C Monolith. IC 3 D Inc. Patents Pending 74

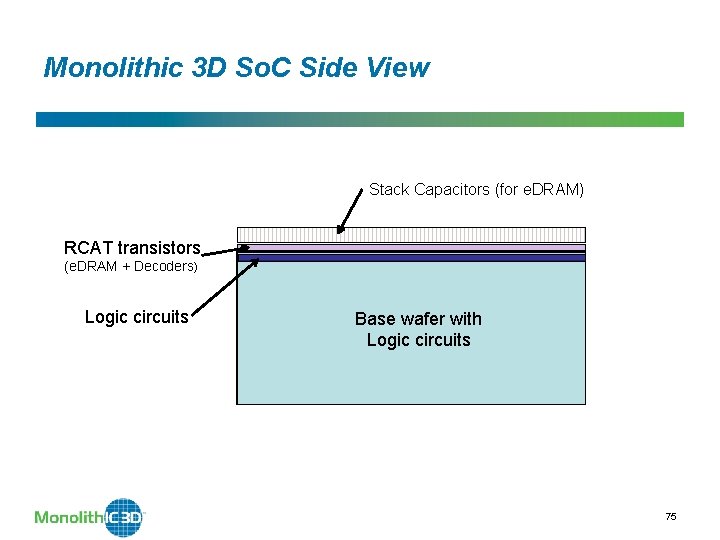

Monolithic 3 D So. C Side View Stack Capacitors (for e. DRAM) RCAT transistors (e. DRAM + Decoders) Logic circuits Base wafer with Logic circuits 75

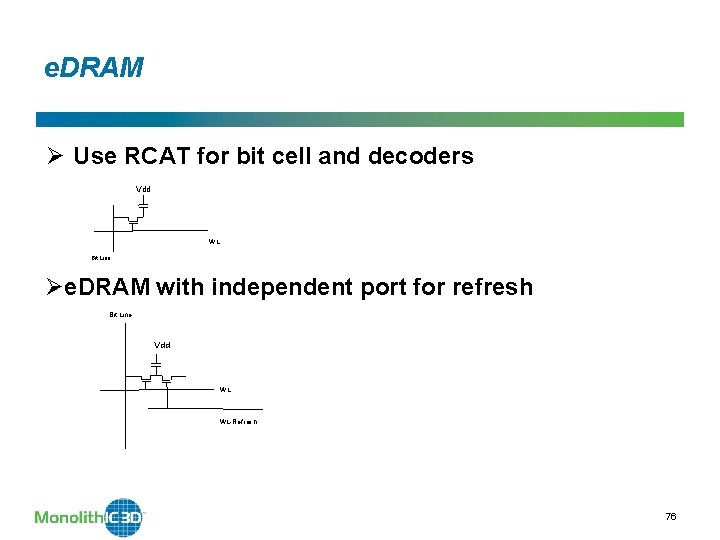

e. DRAM Ø Use RCAT for bit cell and decoders Vdd WL Bit Line Øe. DRAM with independent port for refresh Bit Line Vdd WL WL-Refresh 76

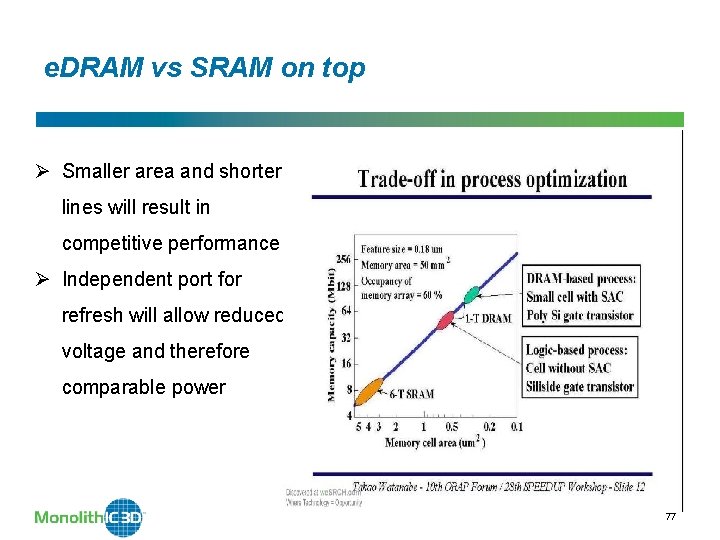

e. DRAM vs SRAM on top Ø Smaller area and shorter lines will result in competitive performance Ø Independent port for refresh will allow reduced voltage and therefore comparable power 77

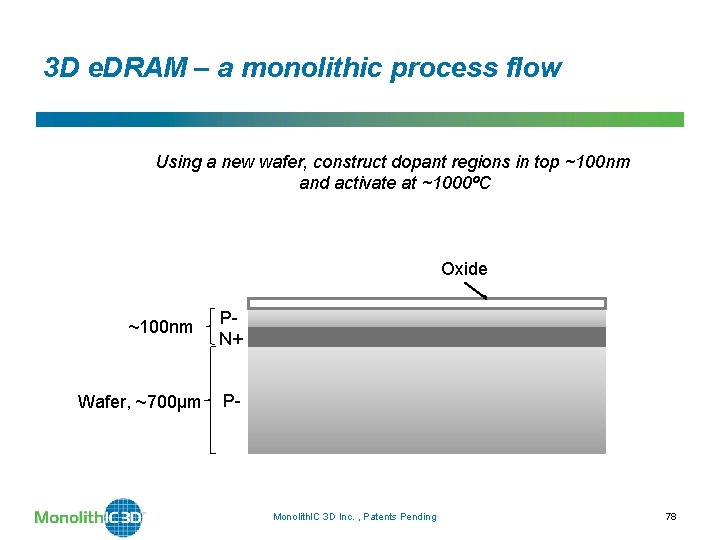

3 D e. DRAM – a monolithic process flow Using a new wafer, construct dopant regions in top ~100 nm and activate at ~1000ºC Oxide ~100 nm PN+ Wafer, ~700µm P- Monolith. IC 3 D Inc. , Patents Pending 78

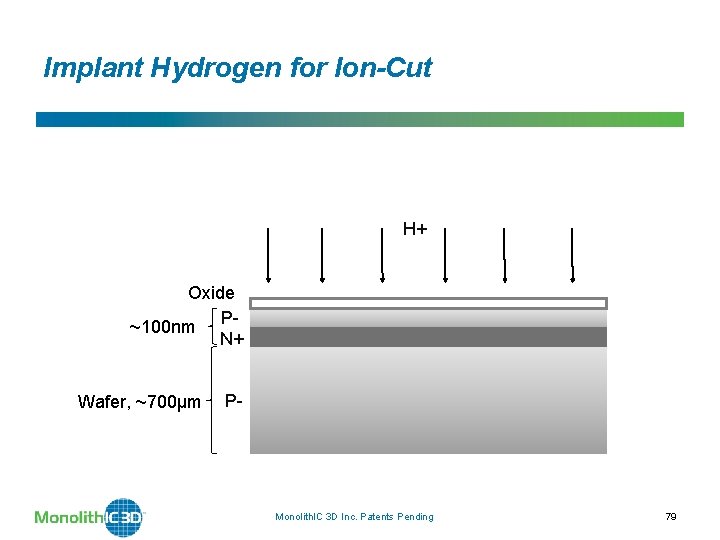

Implant Hydrogen for Ion-Cut H+ Oxide P~100 nm N+ Wafer, ~700µm P- Monolith. IC 3 D Inc. Patents Pending 79

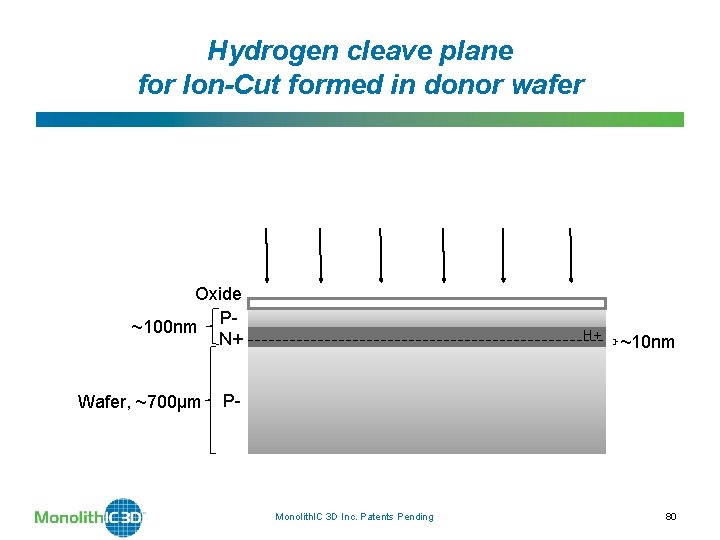

Hydrogen cleave plane for Ion-Cut formed in donor wafer Oxide P~100 nm N+ Wafer, ~700µm H+ ~10 nm P- Monolith. IC 3 D Inc. Patents Pending 80

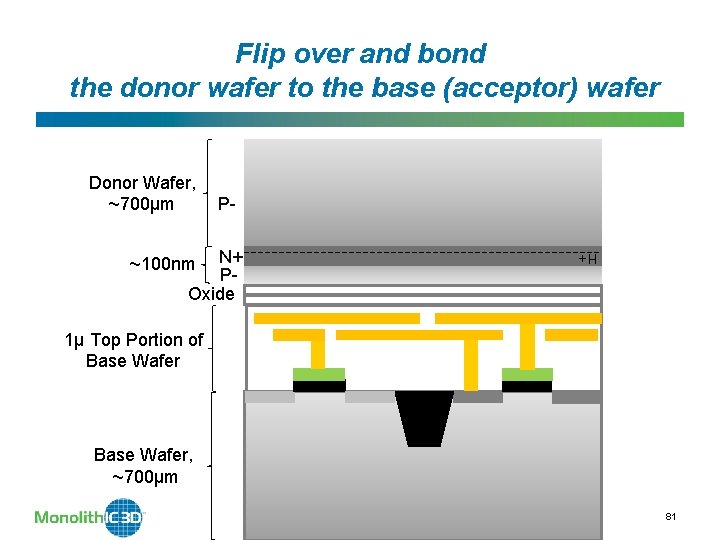

Flip over and bond the donor wafer to the base (acceptor) wafer Donor Wafer, P~700µm N+ POxide H+ ~100 nm 1µ Top Portion of Base Wafer, ~700µm Monolith. IC 3 D Inc. Patents Pending 81

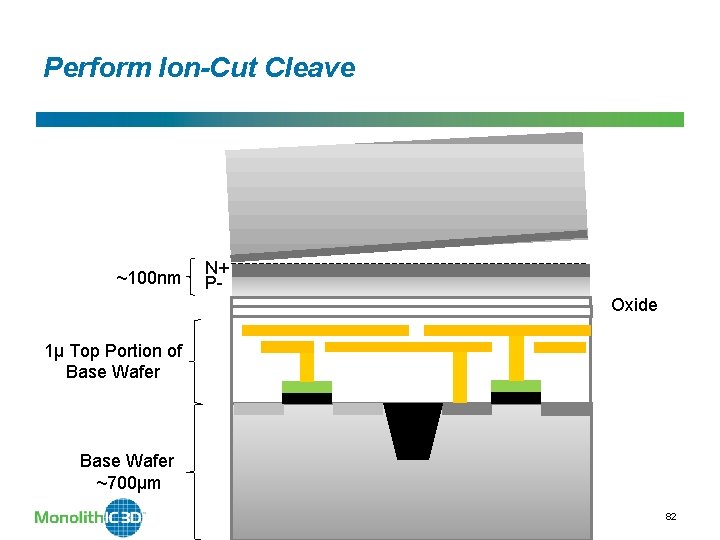

Perform Ion-Cut Cleave ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 82

Complete Ion-Cut ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 83

Etch Isolation regions as the first step to define RCAT transistors ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 84

Fill isolation regions (STI-Shallow Trench Isolation) with Oxide, and CMP ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 85

Etch RCAT Gate Regions Gate region ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 86

Form Gate Oxide ~100 nm N+ P- Oxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 87

Form Gate Electrode ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 88

Add Dielectric and CMP ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 89

Etch Thru-Layer-Via and RCAT Transistor Contacts TLV ~100 nm N+ POxide 1µ Top Portion of Base Wafer Monolith. IC 3 D Inc. Patents Pending Base Wafer ~700µm 90

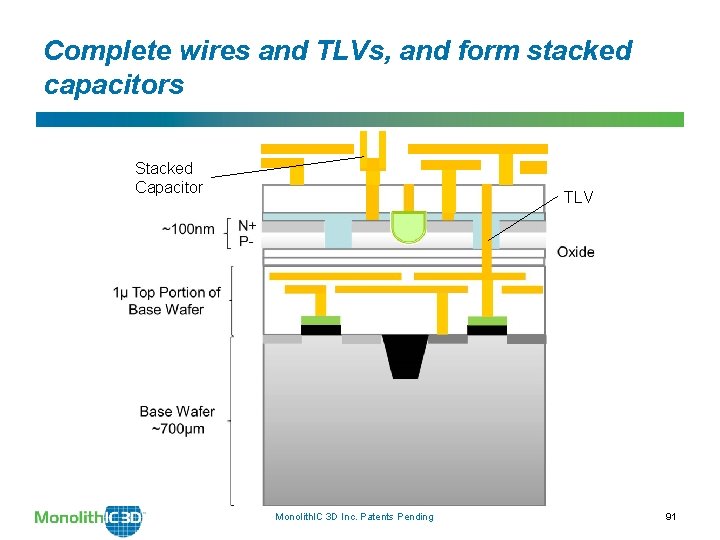

Complete wires and TLVs, and form stacked capacitors Stacked Capacitor TLV Monolith. IC 3 D Inc. Patents Pending 91

e. DRAM on logic flow Create a layer of Recessed Ch. Annel Transistors (RCATs), commonly used in DRAMs, by activating dopants at ~1000ºC before wafer bonding to the CMOS substrate and cleaving, thereby leaving a very thin doped stack layer from which transistors are completed, utilizing less than 400ºC etch and deposition processes. Add stacked caps. Monolith. IC 3 D Inc. Patents Pending 92

Benefits for 3 D e. DRAM • • • 2 x lower power 2 x smaller silicon area 4 x smaller footprint Replacing SRAM with e. DRAM reduces memory costs by up to 2/3 Can use older and cheaper process node for e. DRAM and use optimum number of metal layers, incurring no waste Layer to layer interconnect density at close to full lithographic resolution and alignment Scalable: scales naturally with equipment capability Forestalls next gen litho-tool risk Base logic circuits could be UT-BBOX, Fin. FET, or JLT CMOS logic devices. Logic transistors are untouched by DRAM (such as trench) processing Monolith. IC 3 D Inc. Patents Pending 93

- Slides: 93