ModuloN Counters Lecture L 8 4 Section 8

![Modulo-5 Counter [D 2. . D 0] = [1, 0, 0] Modulo-5 Counter [D 2. . D 0] = [1, 0, 0]](https://slidetodoc.com/presentation_image/54ee34dc5ff438e9dd2fd11cc1c103cf/image-23.jpg)

- Slides: 23

Modulo-N Counters Lecture L 8. 4 Section 8. 2

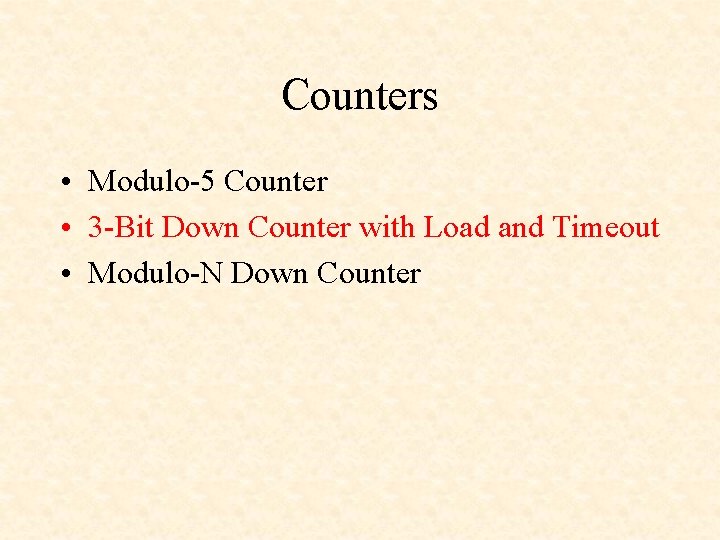

Counters • Modulo-5 Counter • 3 -Bit Down Counter with Load and Timeout • Modulo-N Down Counter

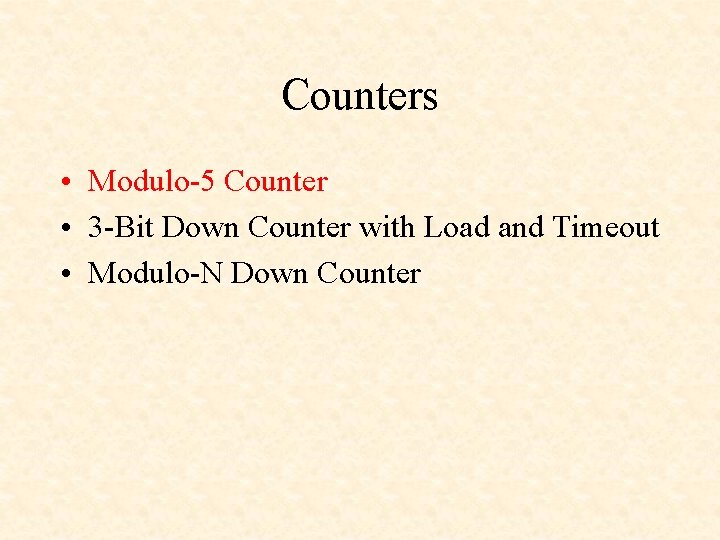

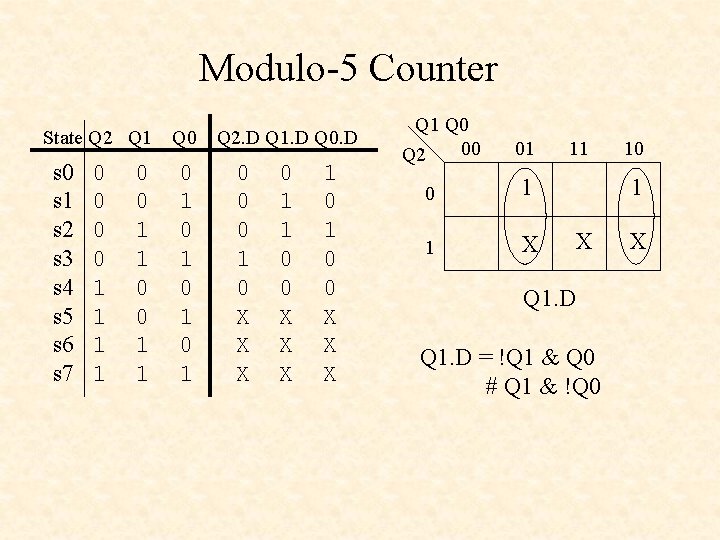

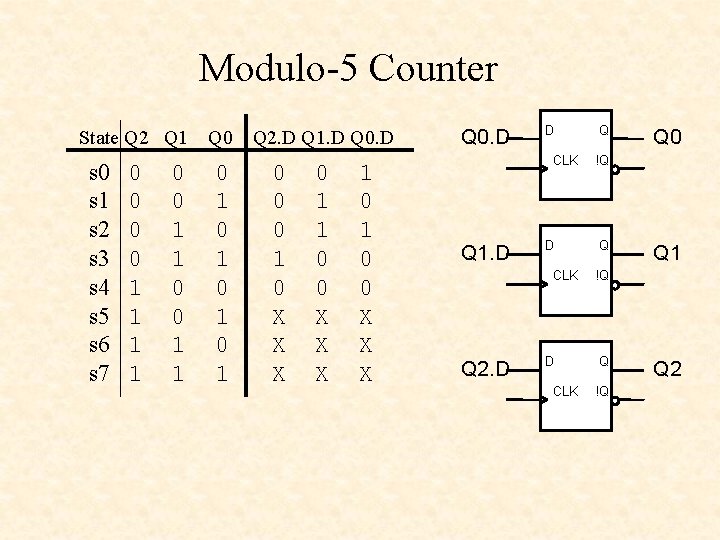

Modulo-5 Counter State Q 2 Q 1 s 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 Q 0 0 1 0 1 Q 2. D Q 1. D Q 0. D 0 0 0 1 0 X X X 0 1 1 0 0 X X X Q 0. D D CLK Q 1. D D CLK Q 2. D D CLK Q Q 0 !Q Q Q 1 !Q Q 2

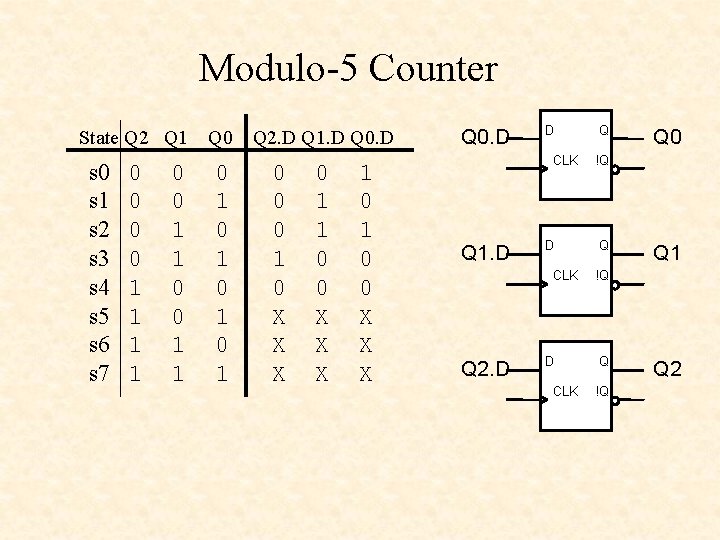

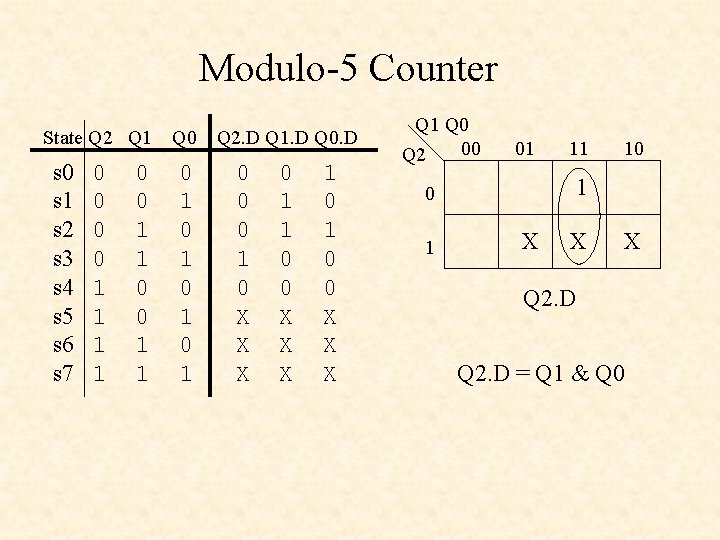

Modulo-5 Counter State Q 2 Q 1 s 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 Q 0 0 1 0 1 Q 2. D Q 1. D Q 0. D 0 0 0 1 0 X X X 0 1 1 0 0 X X X Q 1 Q 0 00 Q 2 01 11 1 0 1 10 X X X Q 2. D = Q 1 & Q 0

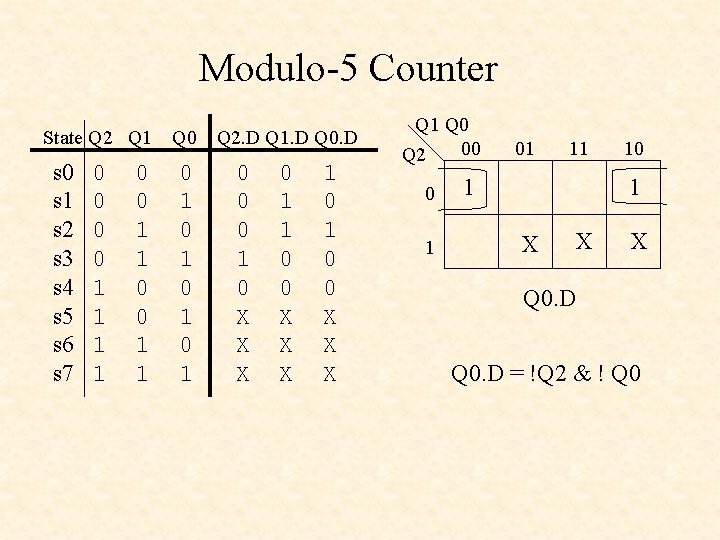

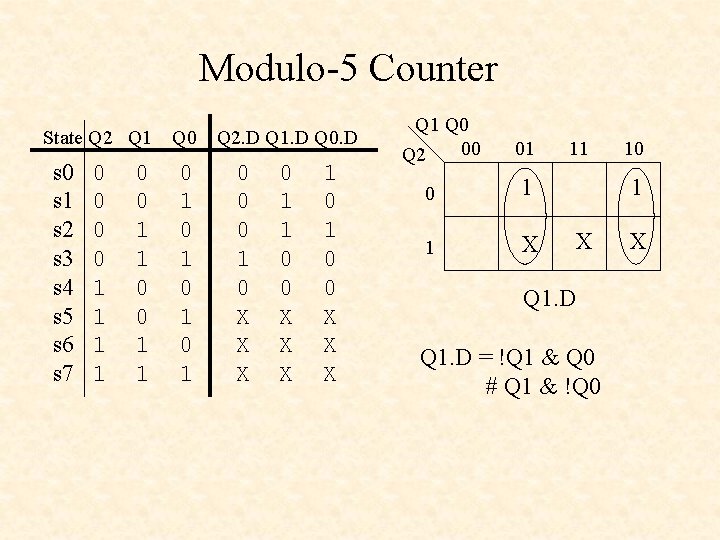

Modulo-5 Counter State Q 2 Q 1 s 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 Q 0 0 1 0 1 Q 2. D Q 1. D Q 0. D 0 0 0 1 0 X X X 0 1 1 0 0 X X X Q 1 Q 0 00 Q 2 01 0 1 1 X 11 10 1 X Q 1. D = !Q 1 & Q 0 # Q 1 & !Q 0 X

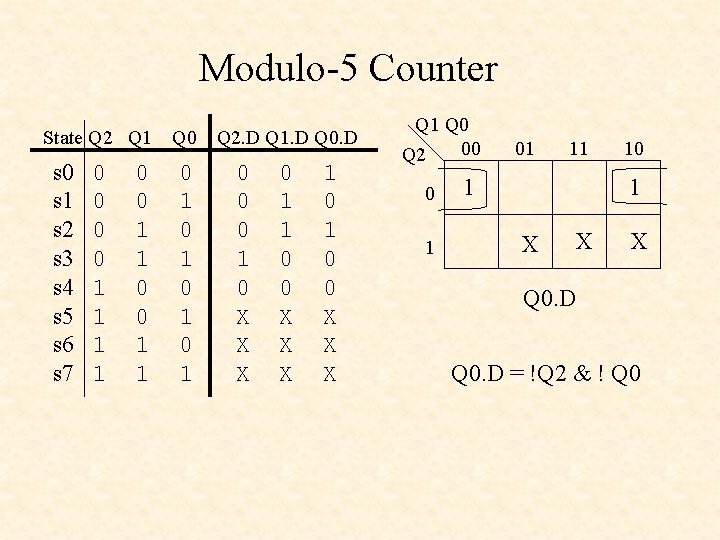

Modulo-5 Counter State Q 2 Q 1 s 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 Q 0 0 1 0 1 Q 2. D Q 1. D Q 0. D 0 0 0 1 0 X X X 0 1 1 0 0 X X X Q 1 Q 0 00 Q 2 0 1 01 11 1 10 1 X X X Q 0. D = !Q 2 & ! Q 0

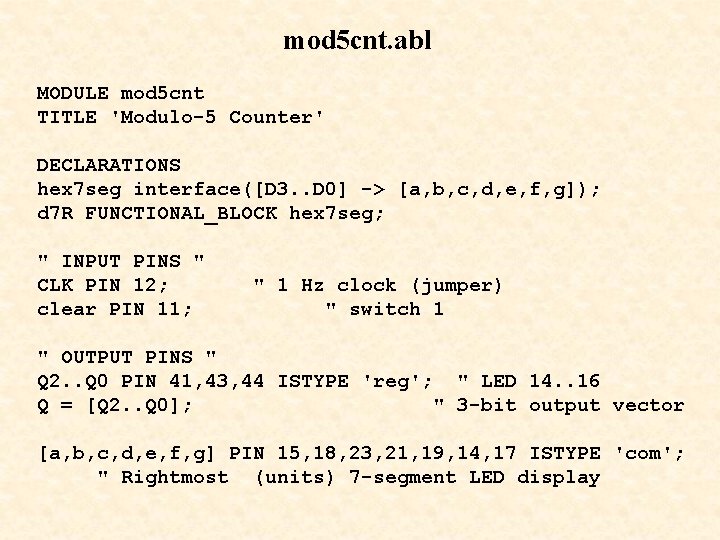

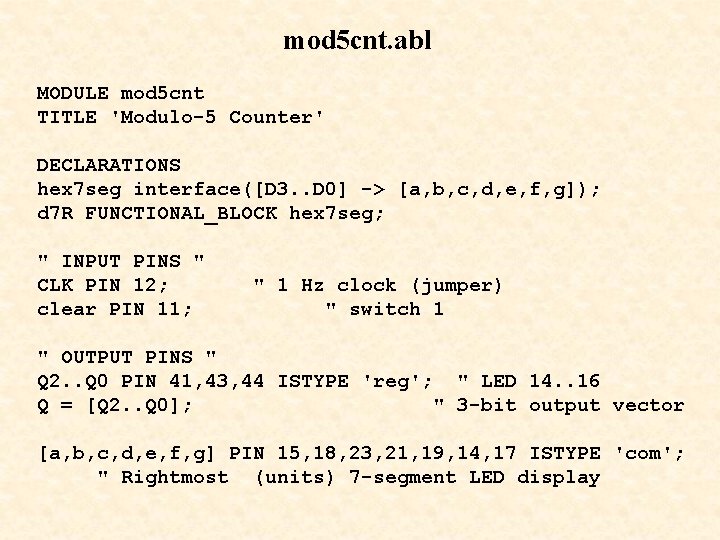

mod 5 cnt. abl MODULE mod 5 cnt TITLE 'Modulo-5 Counter' DECLARATIONS hex 7 seg interface([D 3. . D 0] -> [a, b, c, d, e, f, g]); d 7 R FUNCTIONAL_BLOCK hex 7 seg; " INPUT PINS " CLK PIN 12; " 1 Hz clock (jumper) clear PIN 11; " switch 1 " OUTPUT PINS " Q 2. . Q 0 PIN 41, 43, 44 ISTYPE 'reg'; " LED 14. . 16 Q = [Q 2. . Q 0]; " 3 -bit output vector [a, b, c, d, e, f, g] PIN 15, 18, 23, 21, 19, 14, 17 ISTYPE 'com'; " Rightmost (units) 7 -segment LED display

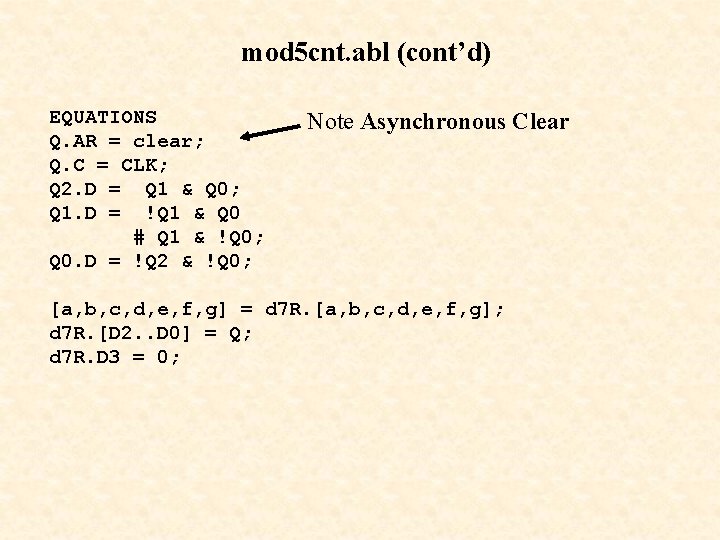

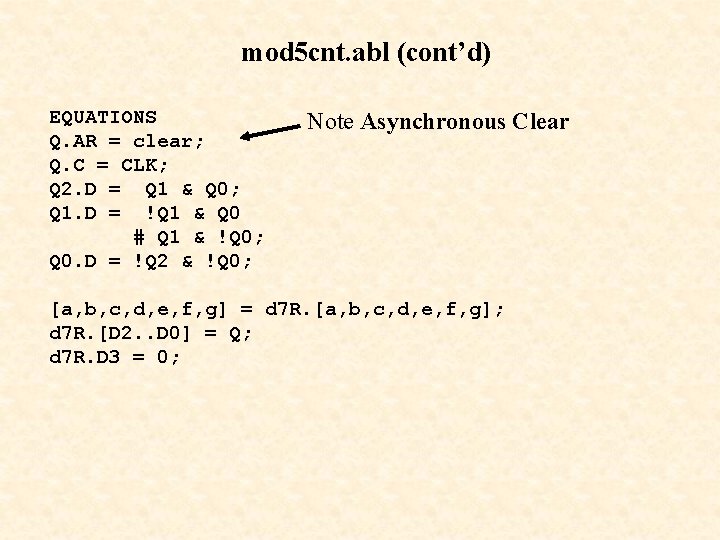

mod 5 cnt. abl (cont’d) EQUATIONS Note Asynchronous Q. AR = clear; Q. C = CLK; Q 2. D = Q 1 & Q 0; Q 1. D = !Q 1 & Q 0 # Q 1 & !Q 0; Q 0. D = !Q 2 & !Q 0; [a, b, c, d, e, f, g] = d 7 R. [a, b, c, d, e, f, g]; d 7 R. [D 2. . D 0] = Q; d 7 R. D 3 = 0; Clear

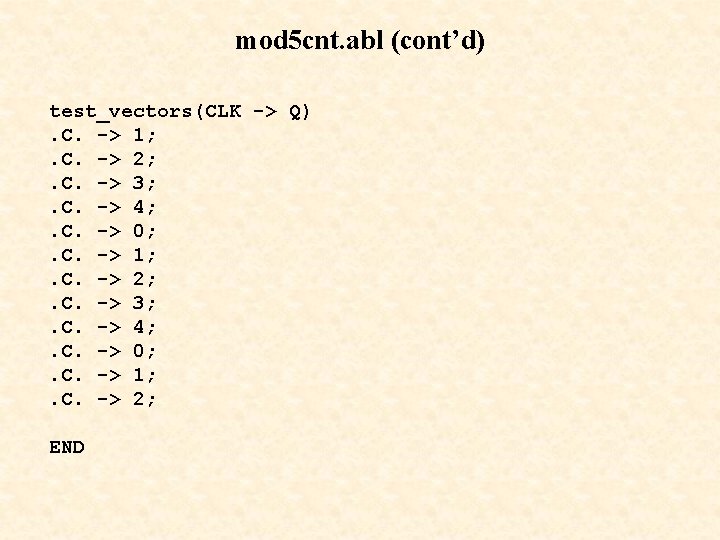

mod 5 cnt. abl (cont’d) test_vectors(CLK -> Q). C. -> 1; . C. -> 2; . C. -> 3; . C. -> 4; . C. -> 0; . C. -> 1; . C. -> 2; END

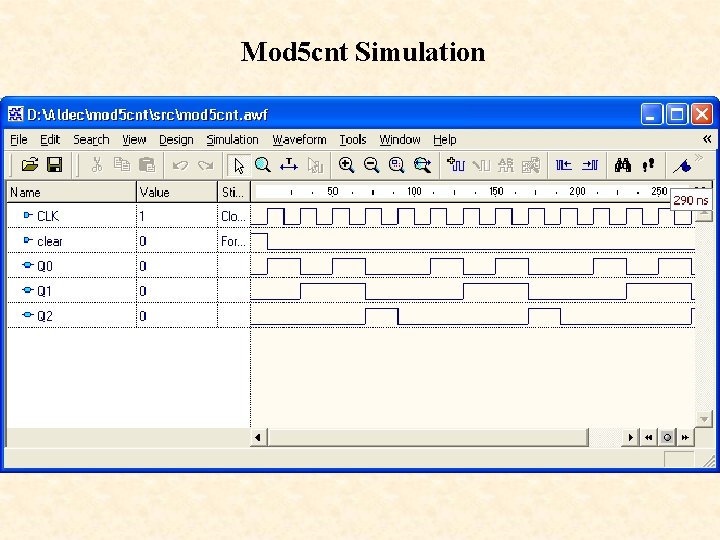

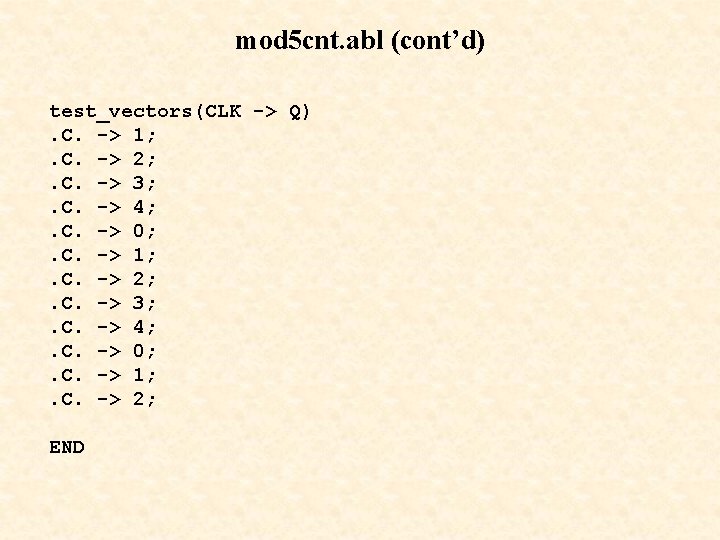

Mod 5 cnt Simulation

Counters • Modulo-5 Counter • 3 -Bit Down Counter with Load and Timeout • Modulo-N Down Counter

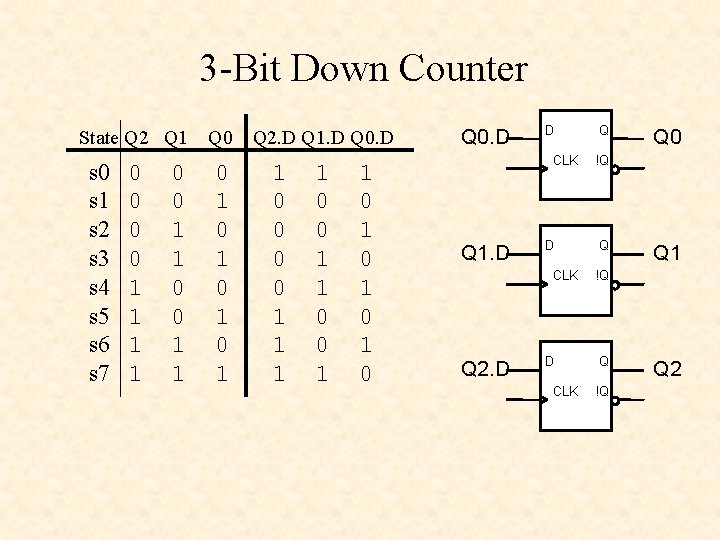

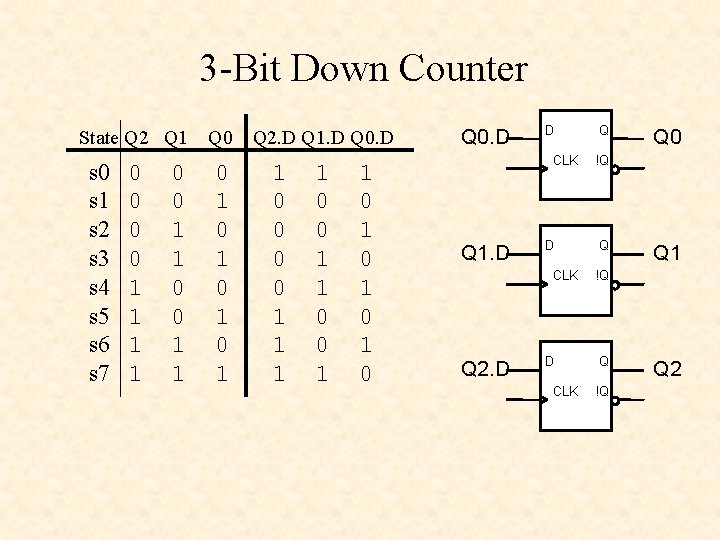

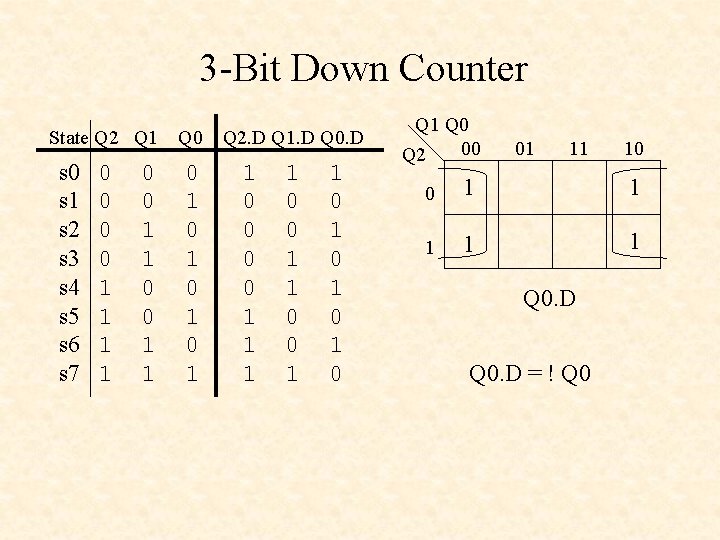

3 -Bit Down Counter State Q 2 Q 1 s 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 Q 0 0 1 0 1 Q 2. D Q 1. D Q 0. D 1 0 0 1 1 0 1 0 1 0 Q 0. D D CLK Q 1. D D CLK Q 2. D D CLK Q Q 0 !Q Q Q 1 !Q Q 2

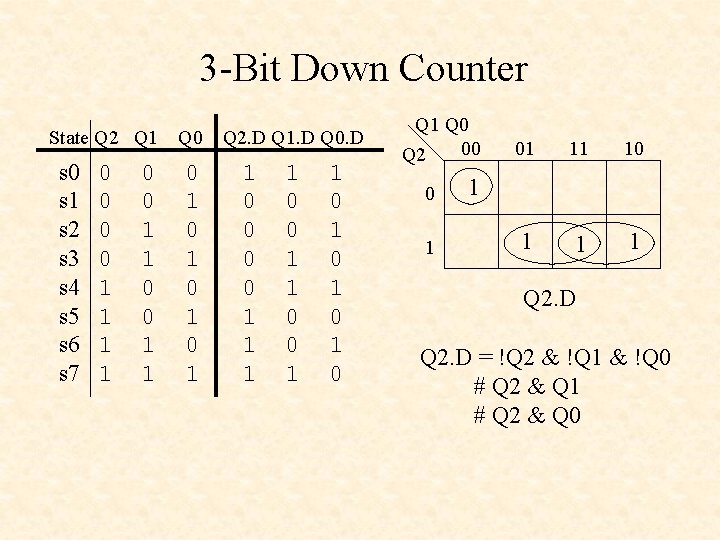

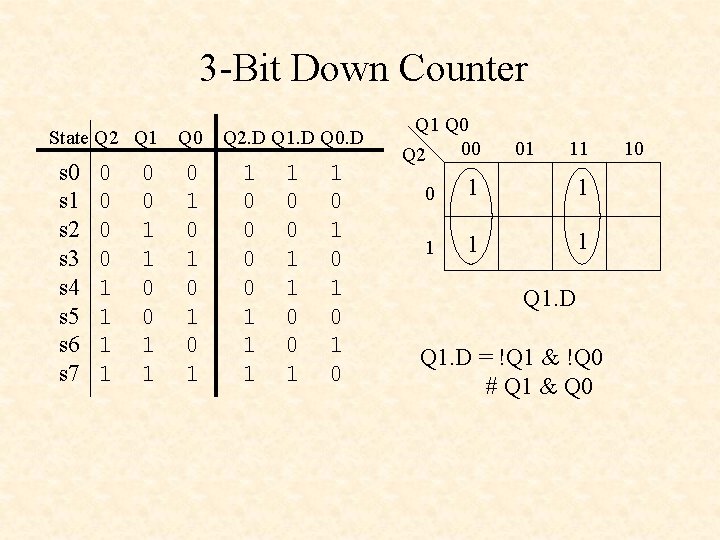

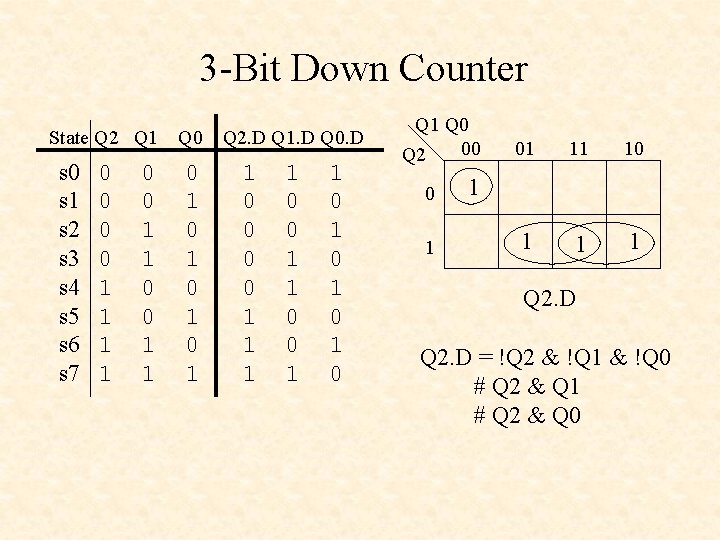

3 -Bit Down Counter State Q 2 Q 1 s 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 Q 0 0 1 0 1 Q 2. D Q 1. D Q 0. D 1 0 0 1 1 0 1 0 1 0 Q 1 Q 0 00 Q 2 0 1 01 11 10 1 1 Q 2. D = !Q 2 & !Q 1 & !Q 0 # Q 2 & Q 1 # Q 2 & Q 0

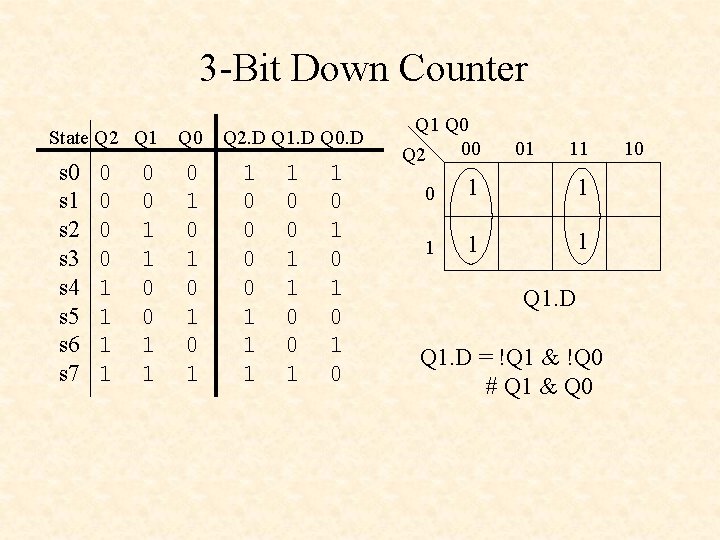

3 -Bit Down Counter State Q 2 Q 1 s 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 Q 0 0 1 0 1 Q 2. D Q 1. D Q 0. D 1 0 0 1 1 0 1 0 1 0 Q 1 Q 0 00 Q 2 01 11 0 1 1 1 Q 1. D = !Q 1 & !Q 0 # Q 1 & Q 0 10

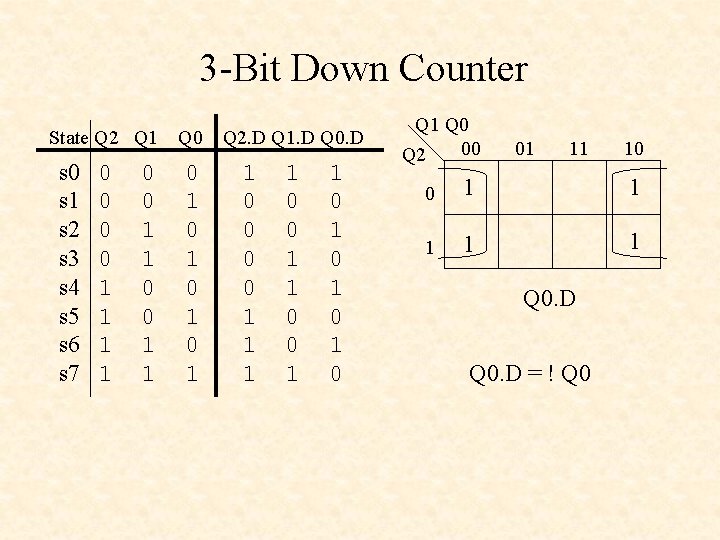

3 -Bit Down Counter State Q 2 Q 1 s 0 s 1 s 2 s 3 s 4 s 5 s 6 s 7 0 0 1 1 Q 0 0 1 0 1 Q 2. D Q 1. D Q 0. D 1 0 0 1 1 0 1 0 1 0 Q 1 Q 0 00 Q 2 01 11 10 0 1 1 1 Q 0. D = ! Q 0

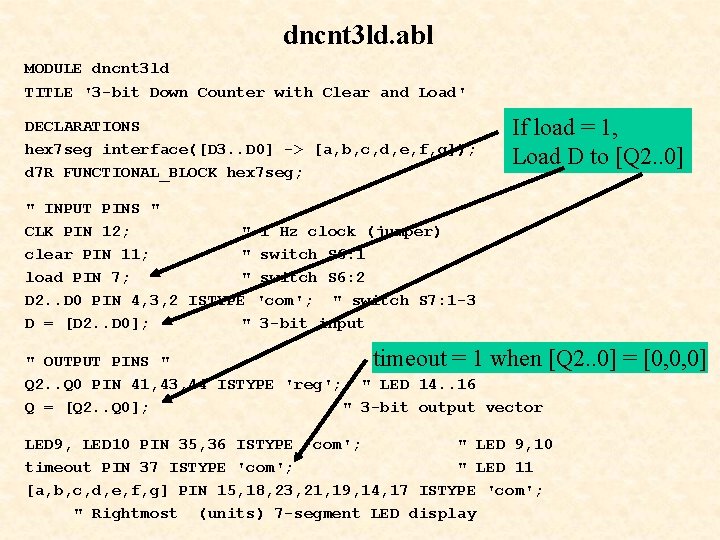

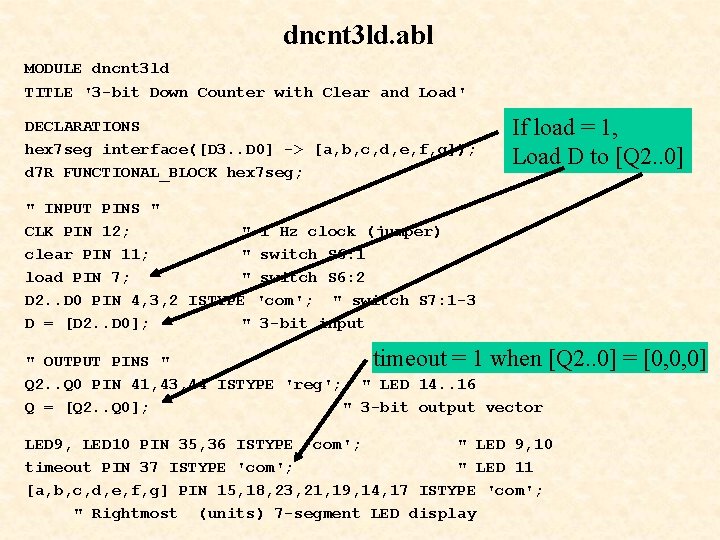

dncnt 3 ld. abl MODULE dncnt 3 ld TITLE '3 -bit Down Counter with Clear and Load' DECLARATIONS hex 7 seg interface([D 3. . D 0] -> [a, b, c, d, e, f, g]); d 7 R FUNCTIONAL_BLOCK hex 7 seg; If load = 1, Load D to [Q 2. . 0] " INPUT PINS " CLK PIN 12; " 1 Hz clock (jumper) clear PIN 11; " switch S 6: 1 load PIN 7; " switch S 6: 2 D 2. . D 0 PIN 4, 3, 2 ISTYPE 'com'; " switch S 7: 1 -3 D = [D 2. . D 0]; " 3 -bit input timeout = 1 when [Q 2. . 0] " OUTPUT PINS " Q 2. . Q 0 PIN 41, 43, 44 ISTYPE 'reg'; " LED 14. . 16 Q = [Q 2. . Q 0]; " 3 -bit output vector LED 9, LED 10 PIN 35, 36 ISTYPE 'com'; " LED 9, 10 timeout PIN 37 ISTYPE 'com'; " LED 11 [a, b, c, d, e, f, g] PIN 15, 18, 23, 21, 19, 14, 17 ISTYPE 'com'; " Rightmost (units) 7 -segment LED display = [0, 0, 0]

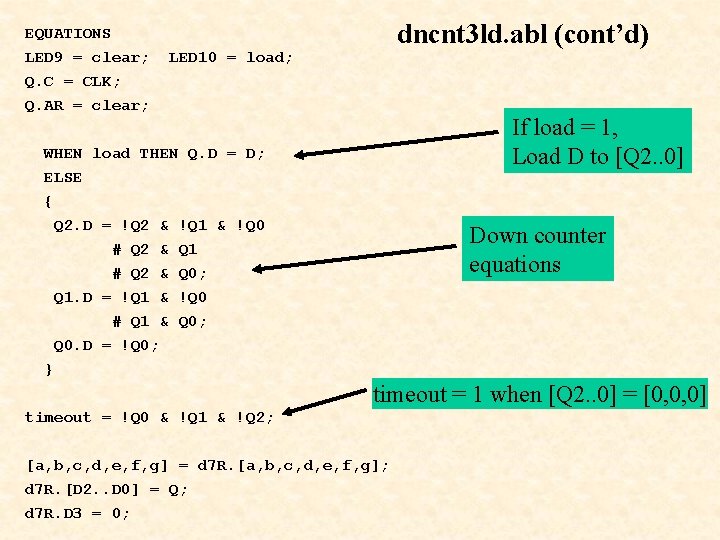

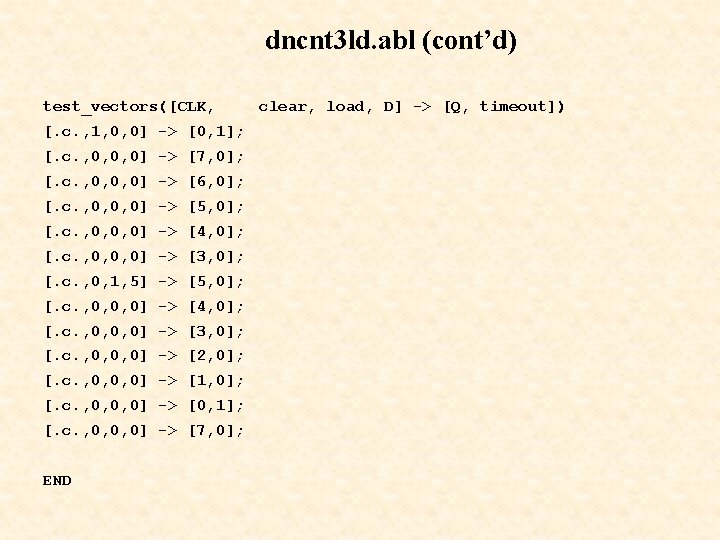

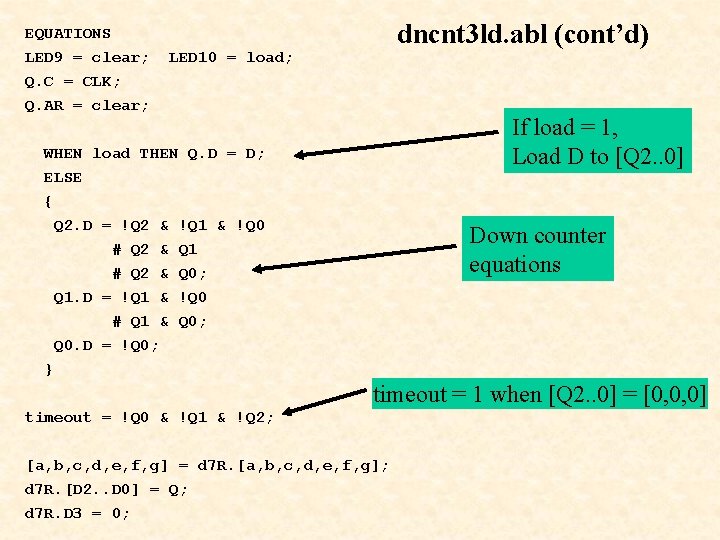

dncnt 3 ld. abl (cont’d) EQUATIONS LED 9 = clear; LED 10 = load; Q. C = CLK; Q. AR = clear; If load = 1, Load D to [Q 2. . 0] WHEN load THEN Q. D = D; ELSE { Q 2. D = !Q 2 & !Q 1 & !Q 0 Down counter equations # Q 2 & Q 1 # Q 2 & Q 0; Q 1. D = !Q 1 & !Q 0 # Q 1 & Q 0; Q 0. D = !Q 0; } timeout = 1 when [Q 2. . 0] = [0, 0, 0] timeout = !Q 0 & !Q 1 & !Q 2; [a, b, c, d, e, f, g] = d 7 R. [a, b, c, d, e, f, g]; d 7 R. [D 2. . D 0] = Q; d 7 R. D 3 = 0;

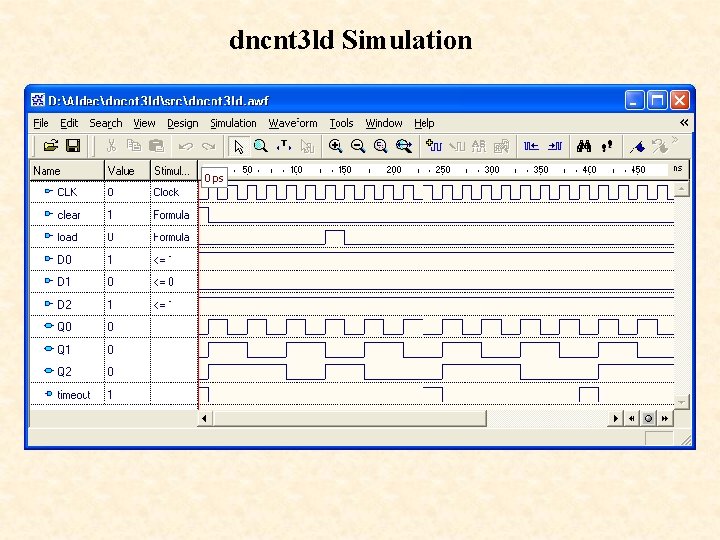

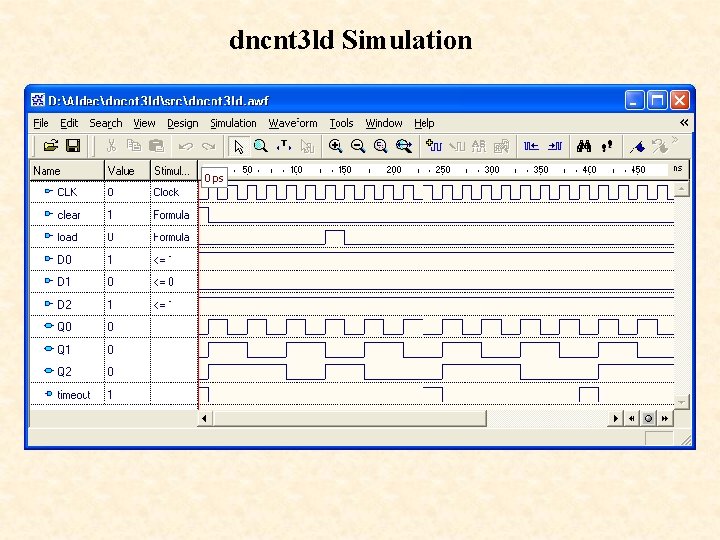

dncnt 3 ld Simulation

Counters • Modulo-5 Counter • 3 -Bit Down Counter with Load and Timeout • Modulo-N Down Counter

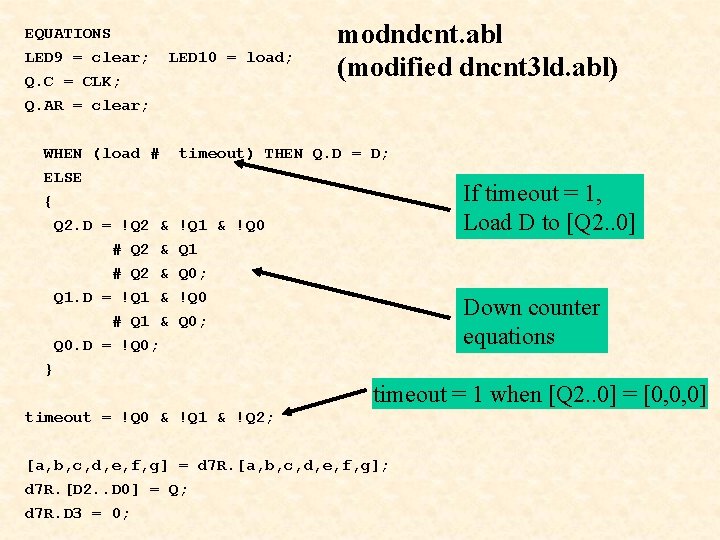

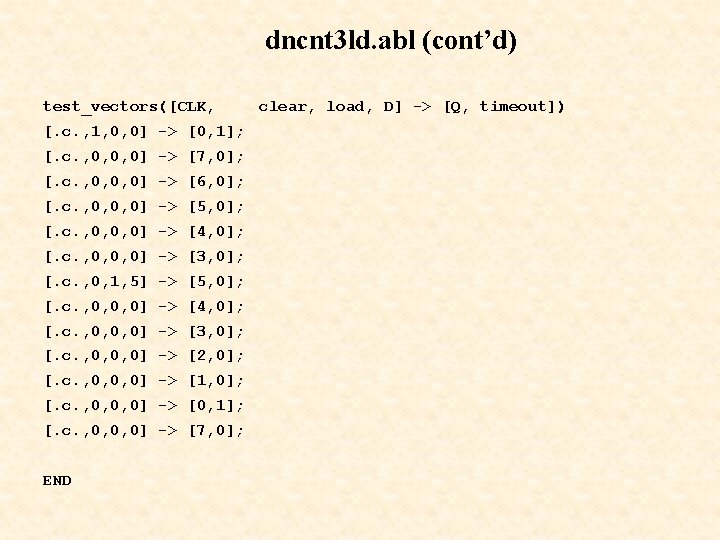

3 -Bit Down Counter with Load and Timeout To make a modulo-N counter, load I 2. . I 0 with N-1 when timeout = 1

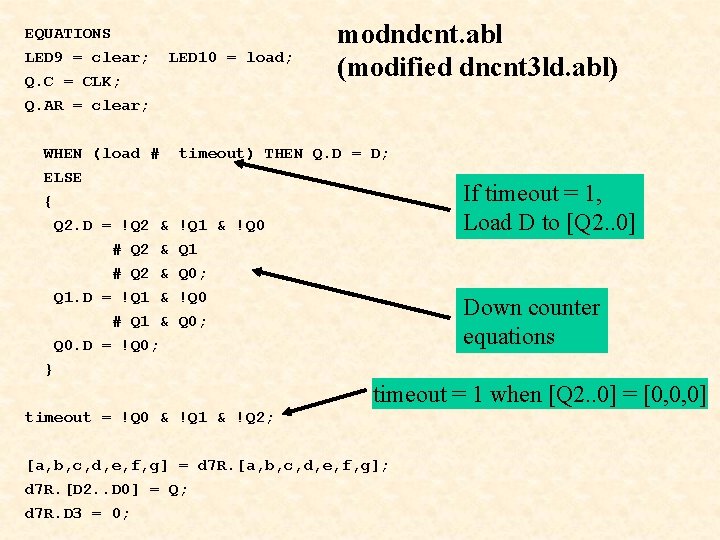

EQUATIONS LED 9 = clear; LED 10 = load; Q. C = CLK; modndcnt. abl (modified dncnt 3 ld. abl) Q. AR = clear; WHEN (load # timeout) THEN Q. D = D; ELSE If timeout = 1, Load D to [Q 2. . 0] { Q 2. D = !Q 2 & !Q 1 & !Q 0 # Q 2 & Q 1 # Q 2 & Q 0; Q 1. D = !Q 1 & !Q 0 # Q 1 & Q 0; Q 0. D = !Q 0; } Down counter equations timeout = 1 when [Q 2. . 0] = [0, 0, 0] timeout = !Q 0 & !Q 1 & !Q 2; [a, b, c, d, e, f, g] = d 7 R. [a, b, c, d, e, f, g]; d 7 R. [D 2. . D 0] = Q; d 7 R. D 3 = 0;

![Modulo5 Counter D 2 D 0 1 0 0 Modulo-5 Counter [D 2. . D 0] = [1, 0, 0]](https://slidetodoc.com/presentation_image/54ee34dc5ff438e9dd2fd11cc1c103cf/image-23.jpg)

Modulo-5 Counter [D 2. . D 0] = [1, 0, 0]