Module Verilog HDL l l Statement terminator semicolon

![Multi Bit 선언 l 신호 선언 [MSB: LSB] ¡ l 한 비트의 선택 ¡ Multi Bit 선언 l 신호 선언 [MSB: LSB] ¡ l 한 비트의 선택 ¡](https://slidetodoc.com/presentation_image/33b99efcaa95fe278fd1c159be98acc6/image-18.jpg)

![기술방법 l Explicit description module 8 bit_or_gate(y, a, b); input [7: 0]a, b; output 기술방법 l Explicit description module 8 bit_or_gate(y, a, b); input [7: 0]a, b; output](https://slidetodoc.com/presentation_image/33b99efcaa95fe278fd1c159be98acc6/image-21.jpg)

- Slides: 44

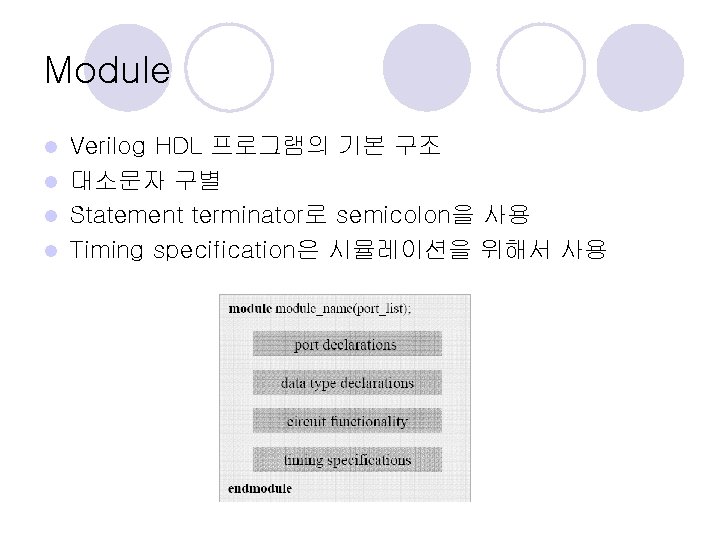

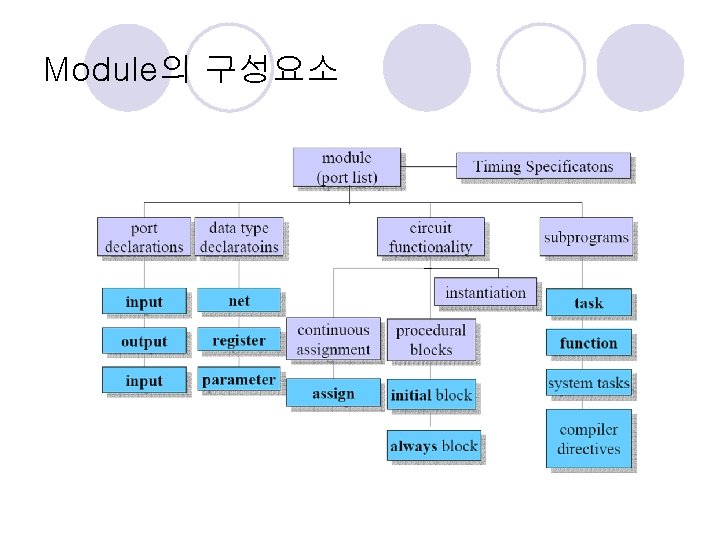

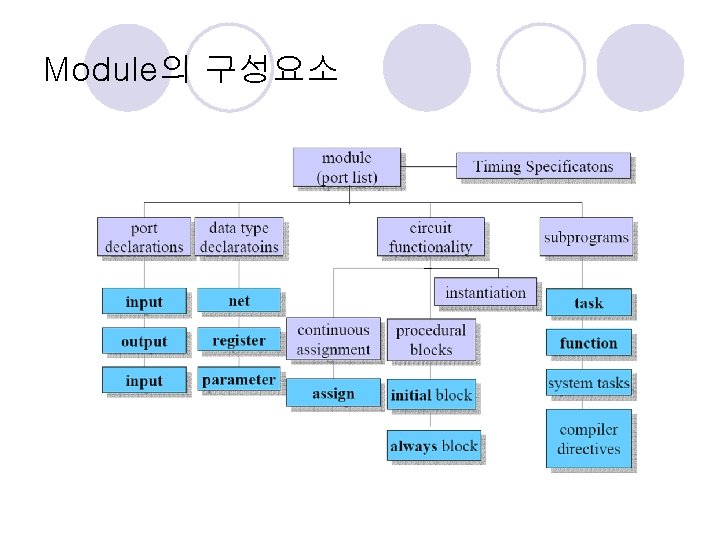

Module Verilog HDL 프로그램의 기본 구조 l 대소문자 구별 l Statement terminator로 semicolon을 사용 l Timing specification은 시뮬레이션을 위해서 사용 l

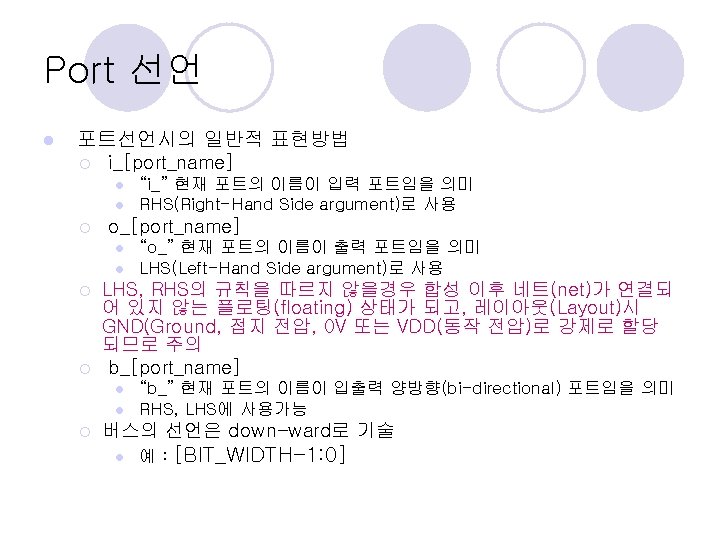

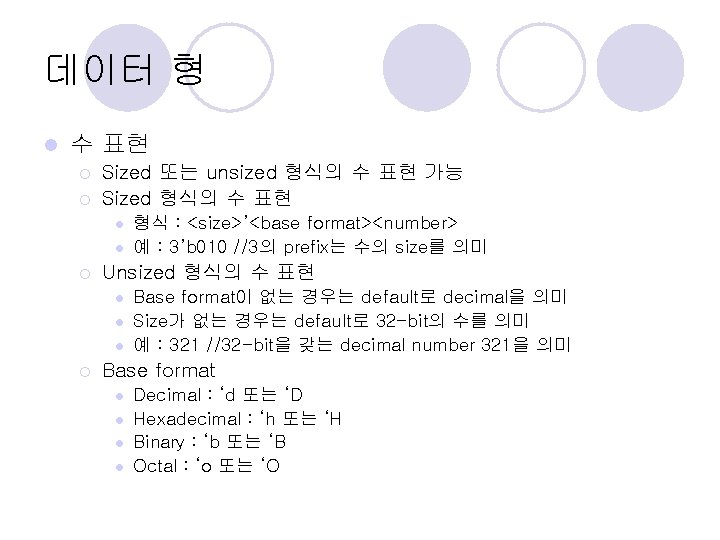

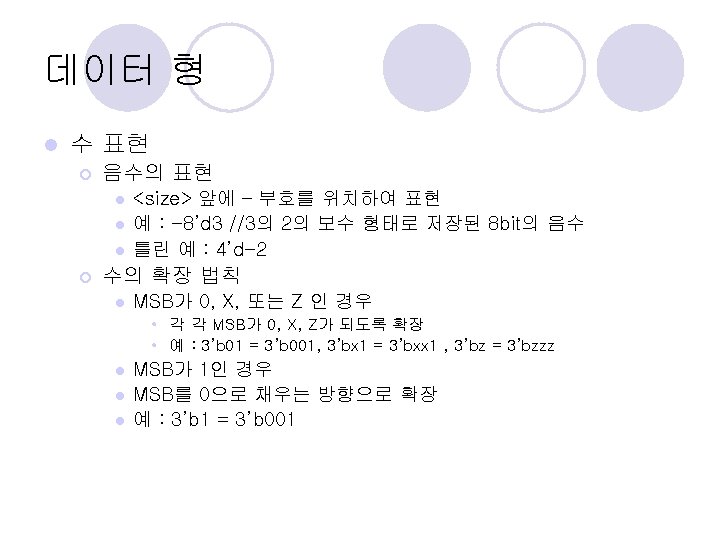

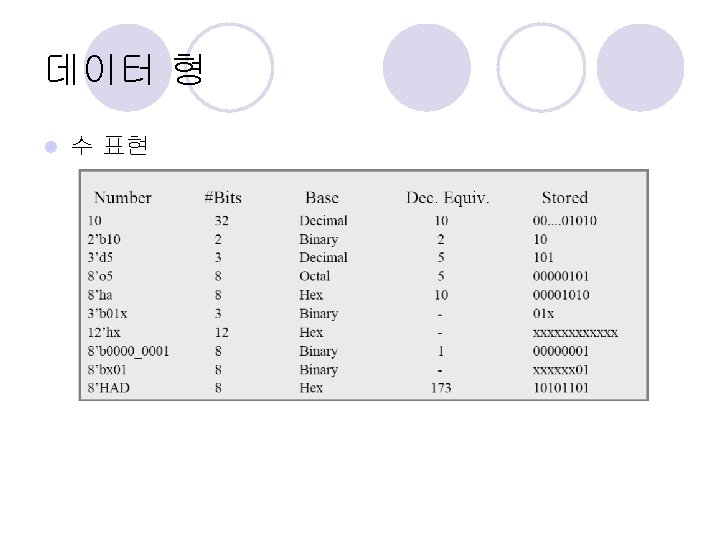

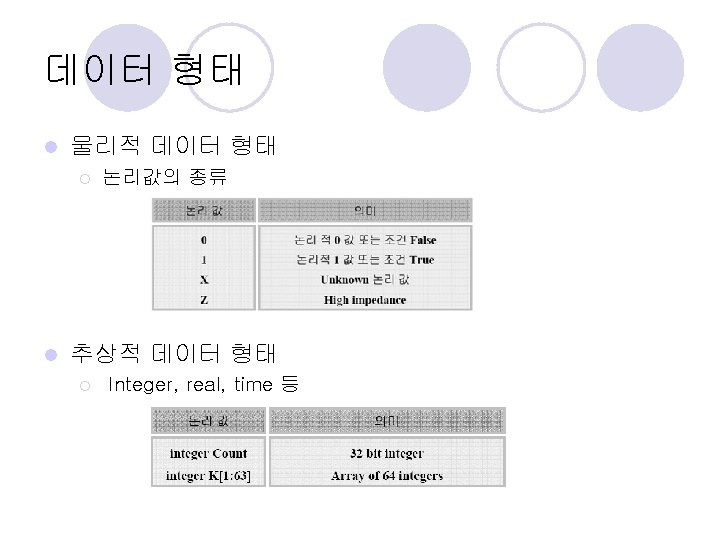

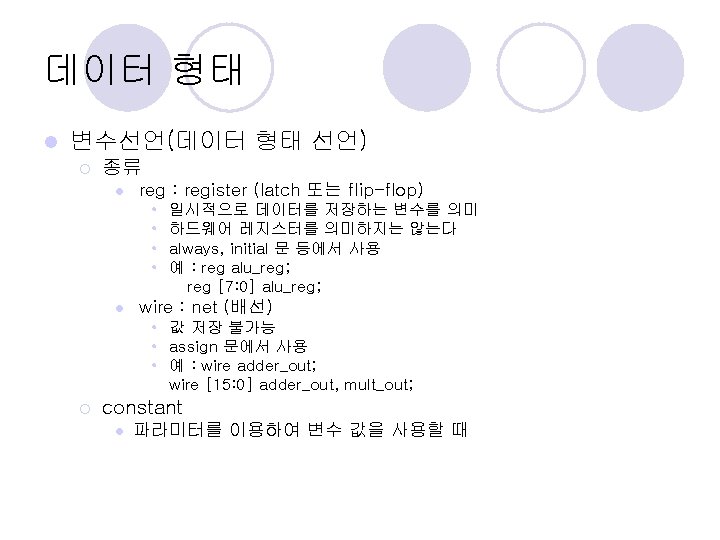

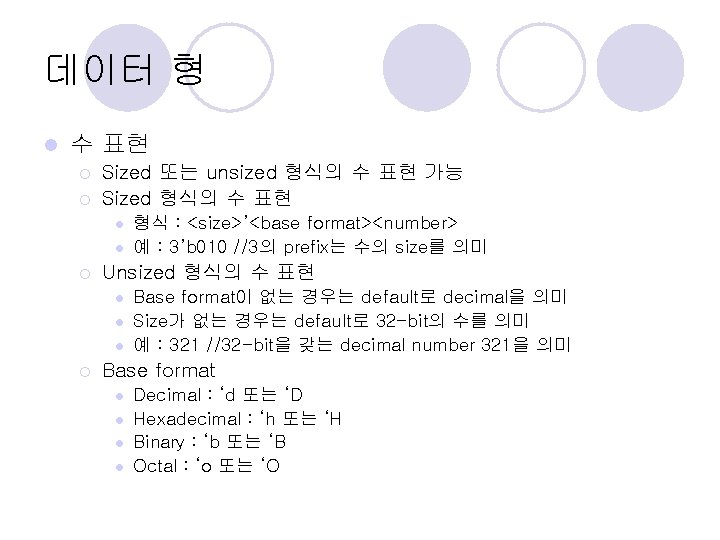

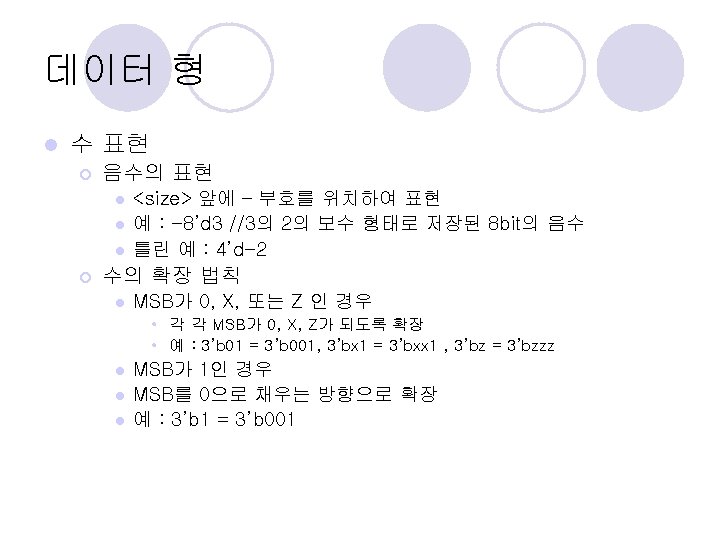

데이터 형 l 수 표현 ¡ ¡ Sized 또는 unsized 형식의 수 표현 가능 Sized 형식의 수 표현 l l ¡ Unsized 형식의 수 표현 l l l ¡ 형식 : <size>’<base format><number> 예 : 3’b 010 //3의 prefix는 수의 size를 의미 Base format이 없는 경우는 default로 decimal을 의미 Size가 없는 경우는 default로 32 -bit의 수를 의미 예 : 321 //32 -bit을 갖는 decimal number 321을 의미 Base format l l Decimal : ‘d 또는 ‘D Hexadecimal : ‘h 또는 ‘H Binary : ‘b 또는 ‘B Octal : ‘o 또는 ‘O

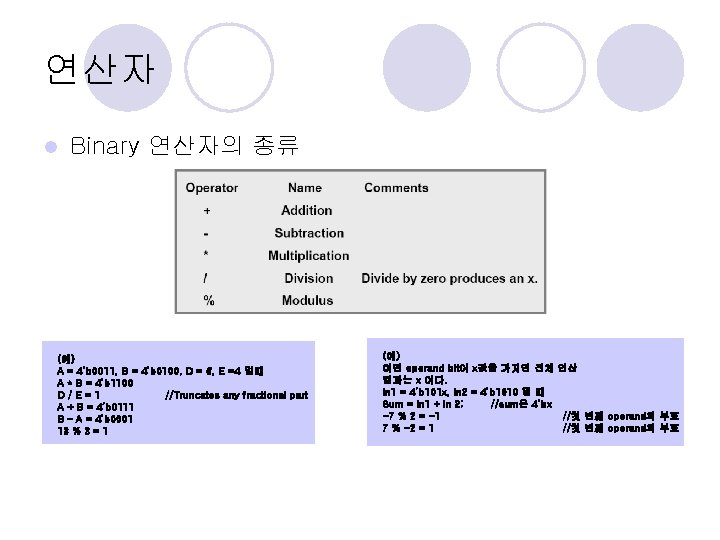

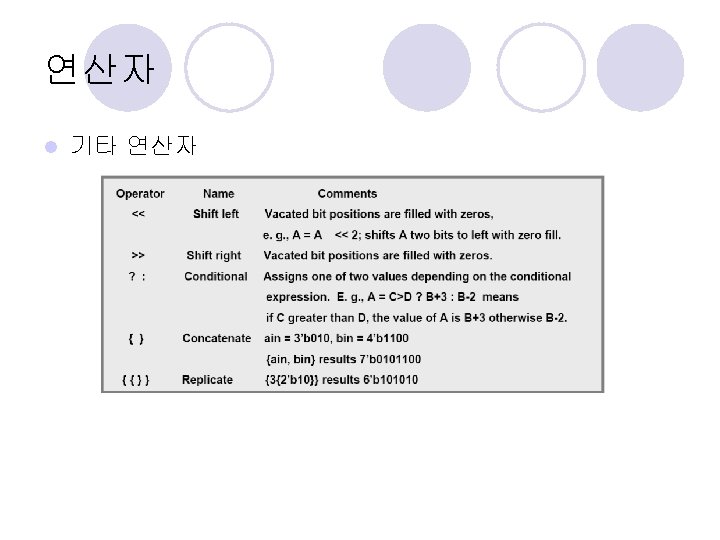

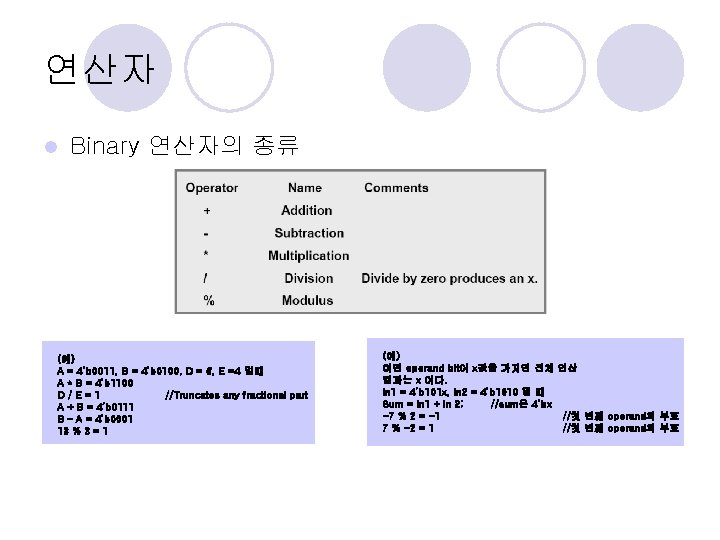

연산자 l Binary 연산자의 종류 (예) A = 4’b 0011, B = 4’b 0100, D = 6, E =4 일때 A * B = 4’b 1100 D/E=1 //Truncates any fractional part A + B = 4’b 0111 B – A = 4’b 0001 13 % 3 = 1 (예) 어떤 operand bit이 x값을 가지면 전체 연산 결과는 x 이다. in 1 = 4’b 101 x, in 2 = 4’b 1010 일 때 Sum = in 1 + in 2; //sum은 4’bx -7 % 2 = -1 //첫 번째 operand의 부호 7 % -2 = 1 //첫 번째 operand의 부호

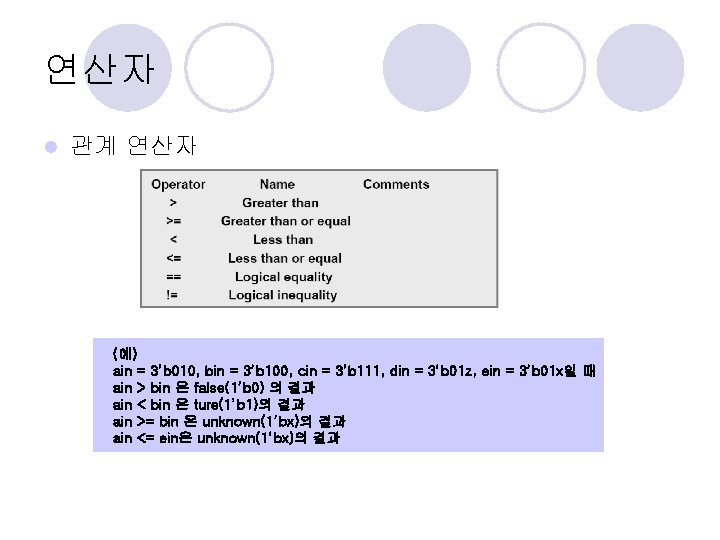

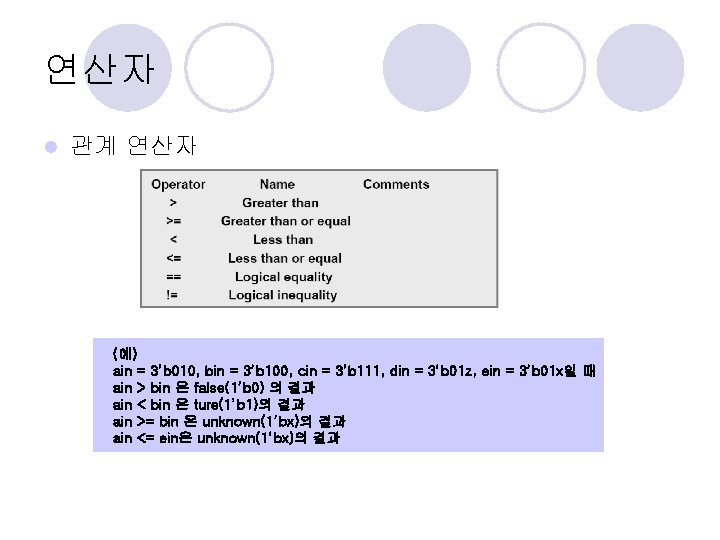

연산자 l 관계 연산자 (예) ain = 3’b 010, bin = 3’b 100, cin = 3’b 111, din = 3’b 01 z, ein = 3’b 01 x일 때 ain > bin 은 false(1’b 0) 의 결과 ain < bin 은 ture(1’b 1)의 결과 ain >= bin 은 unknown(1’bx)의 결과 ain <= ein은 unknown(1’bx)의 결과

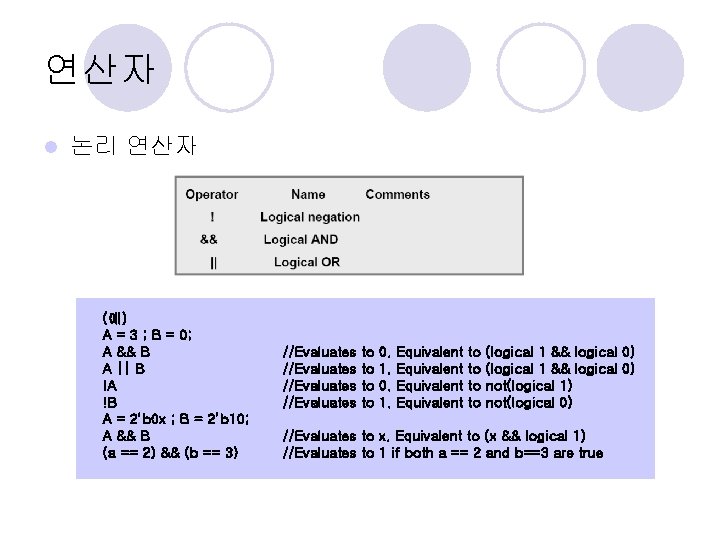

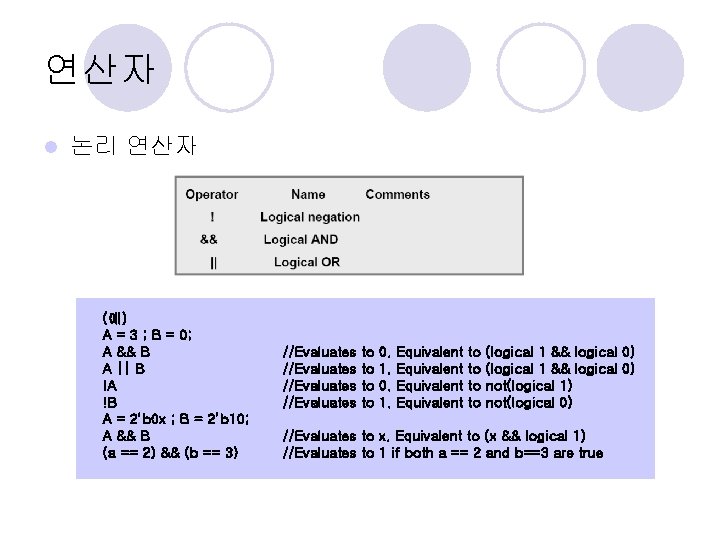

연산자 l 논리 연산자 (예) A = 3 ; B = 0; A && B A || B !A !B A = 2’b 0 x ; B = 2’b 10; A && B (a == 2) && (b == 3) //Evaluates to to 0. 1. Equivalent to to (logical 1 && logical 0) not(logical 1) not(logical 0) //Evaluates to x. Equivalent to (x && logical 1) //Evaluates to 1 if both a == 2 and b==3 are true

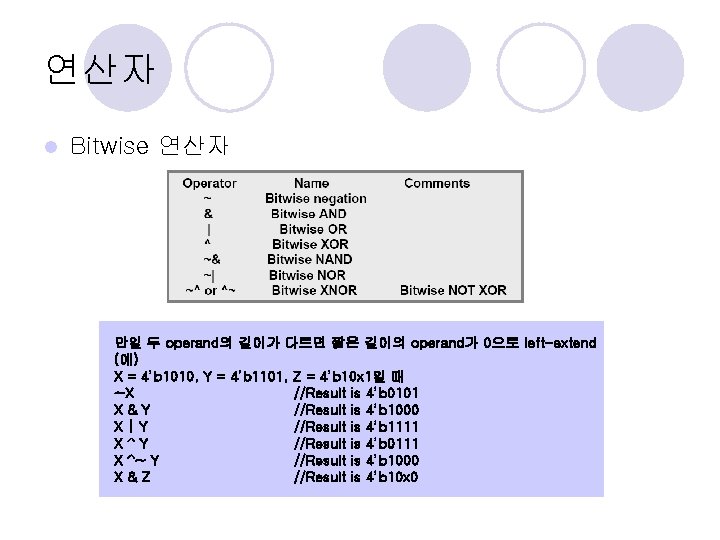

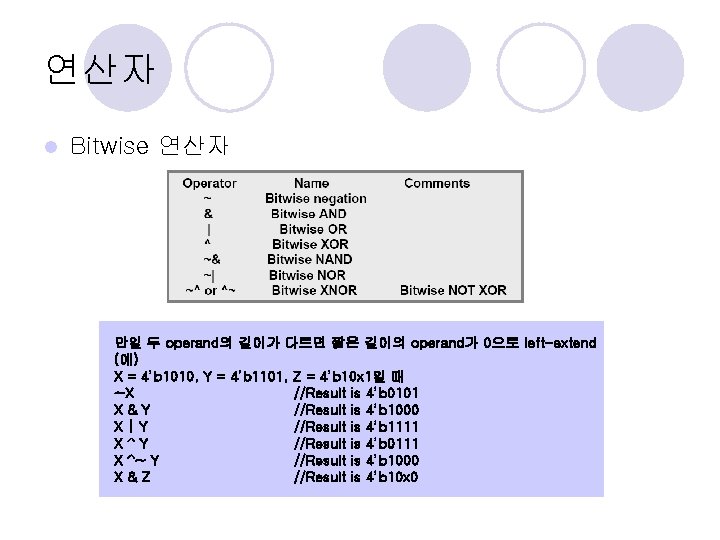

연산자 l Bitwise 연산자 만일 두 operand의 길이가 다르면 짧은 길이의 operand가 0으로 left-extend (예) X = 4’b 1010, Y = 4’b 1101, Z = 4’b 10 x 1일 때 ~X //Result is 4’b 0101 X&Y //Result is 4’b 1000 X|Y //Result is 4’b 1111 X^Y //Result is 4’b 0111 X ^~ Y //Result is 4’b 1000 X&Z //Result is 4’b 10 x 0

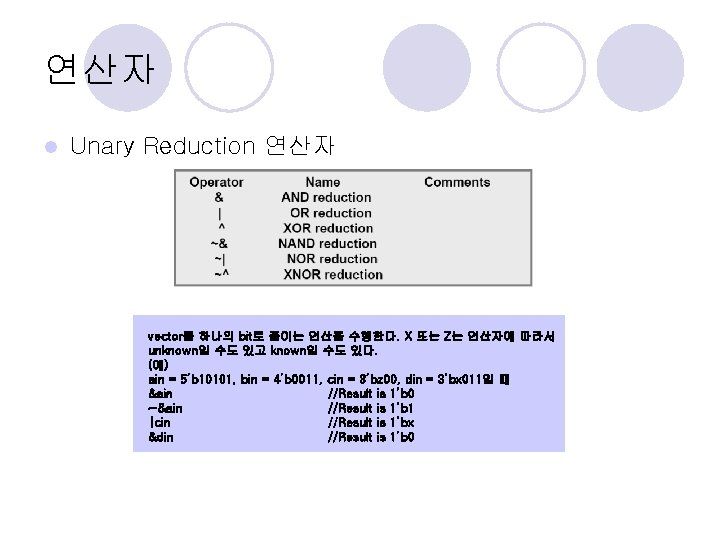

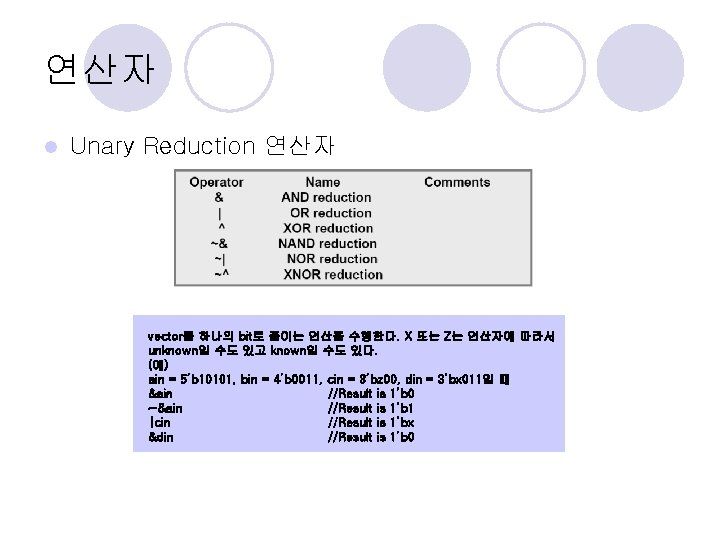

연산자 l Unary Reduction 연산자 vector를 하나의 bit로 줄이는 연산을 수행한다. X 또는 Z는 연산자에 따라서 unknown일 수도 있고 known일 수도 있다. (예) ain = 5’b 10101, bin = 4’b 0011, cin = 3’bz 00, din = 3’bx 011일 때 &ain //Result is 1’b 0 ~&ain //Result is 1’b 1 |cin //Result is 1’bx &din //Result is 1’b 0

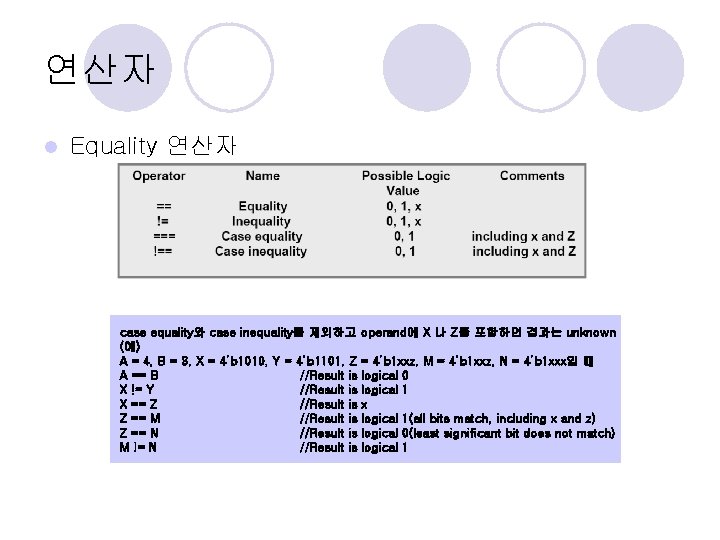

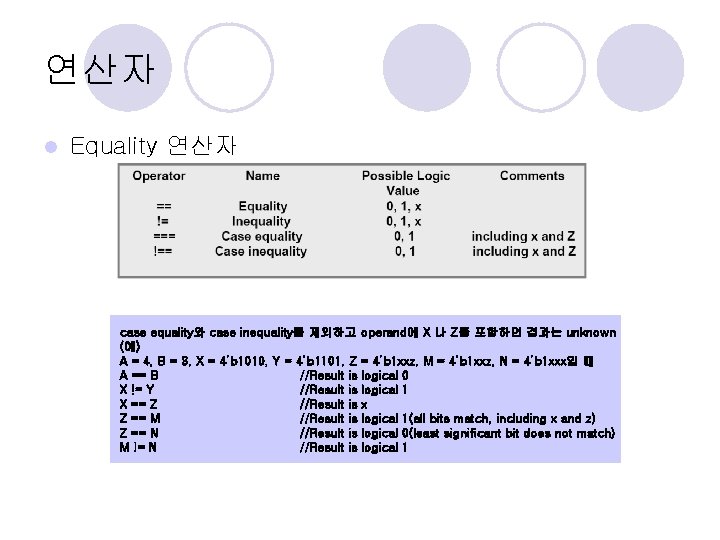

연산자 l Equality 연산자 case equality와 case inequality를 제외하고 operand에 X 나 Z를 포함하면 결과는 unknown (예) A = 4, B = 3, X = 4’b 1010, Y = 4’b 1101, Z = 4’b 1 xxz, M = 4’b 1 xxz, N = 4’b 1 xxx일 때 A == B //Result is logical 0 X != Y //Result is logical 1 X == Z //Result is x Z == M //Result is logical 1(all bits match, including x and z) Z == N //Result is logical 0(least significant bit does not match) M != N //Result is logical 1

![Multi Bit 선언 l 신호 선언 MSB LSB l 한 비트의 선택 Multi Bit 선언 l 신호 선언 [MSB: LSB] ¡ l 한 비트의 선택 ¡](https://slidetodoc.com/presentation_image/33b99efcaa95fe278fd1c159be98acc6/image-18.jpg)

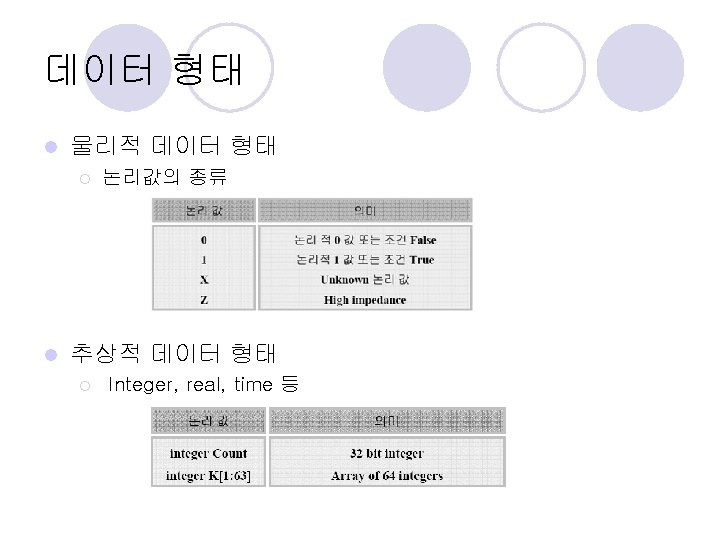

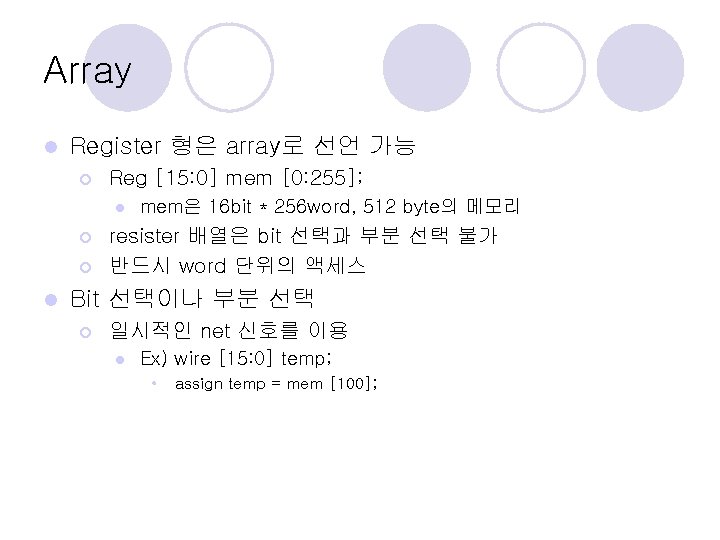

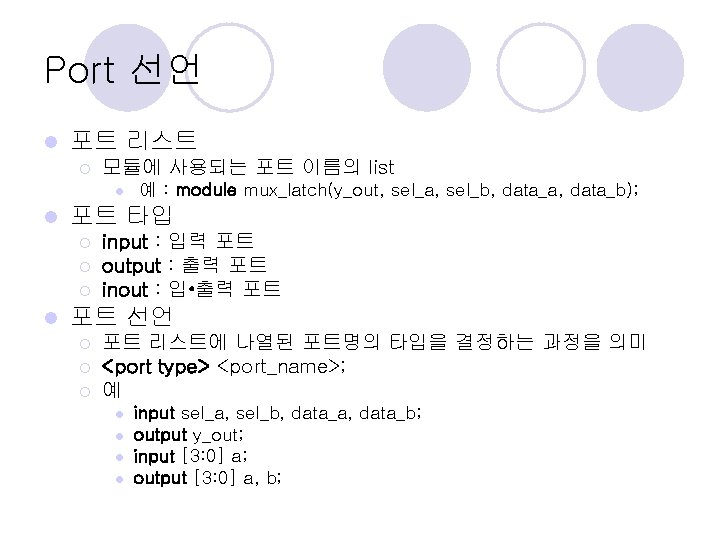

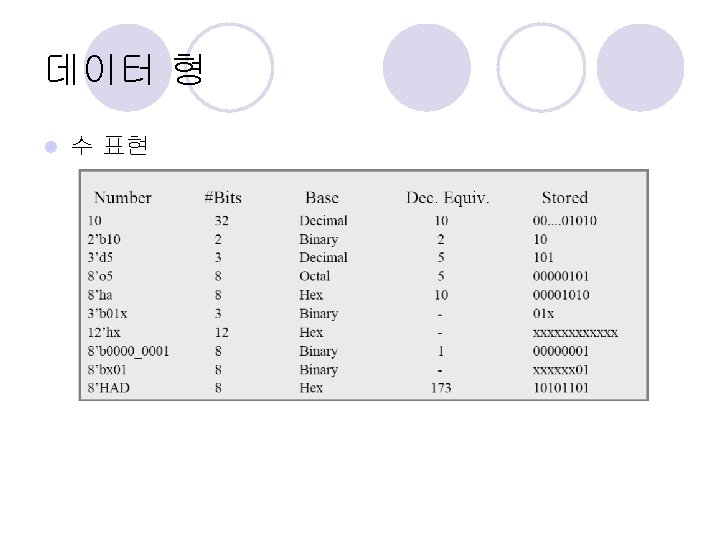

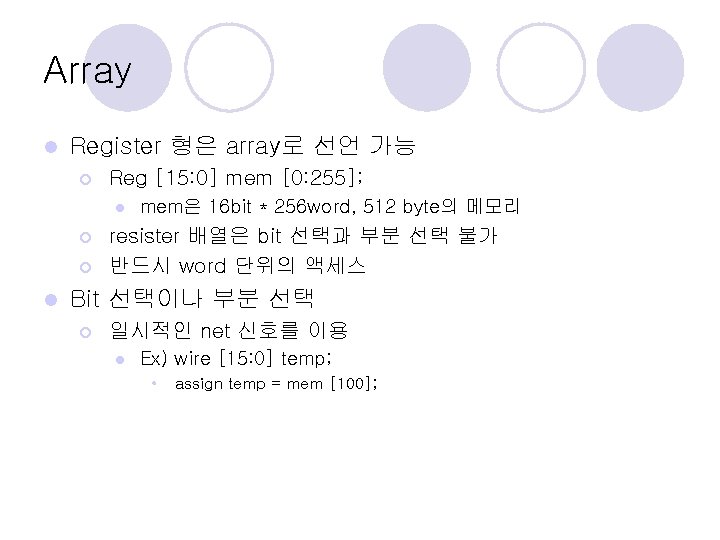

Multi Bit 선언 l 신호 선언 [MSB: LSB] ¡ l 한 비트의 선택 ¡ l Input [7: 0] abus; reg [15: 8] add; assign abc = abus[5] ; assign abus[5] = abc ; 여러 신호를 하나의 신호로 할당 ¡ assign abcd[15: 0] = {abus[7: 0], add[15: 8]} ;

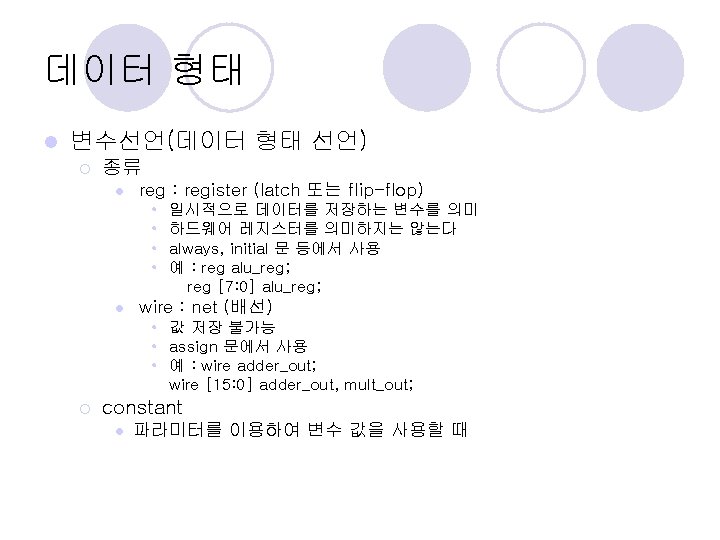

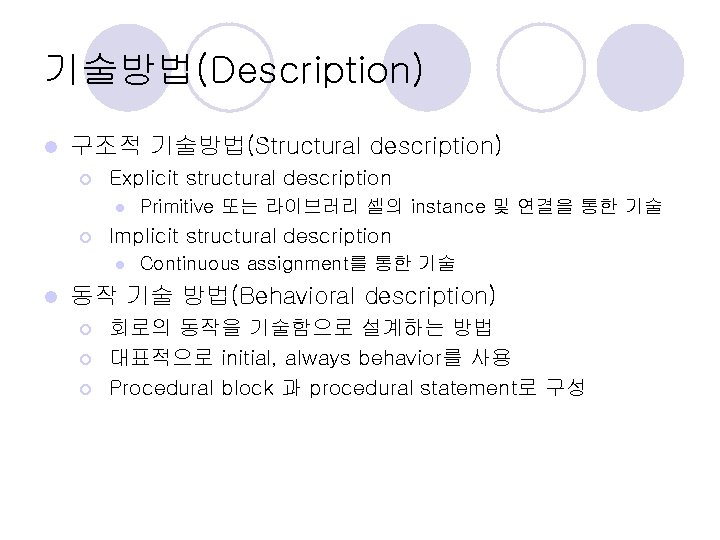

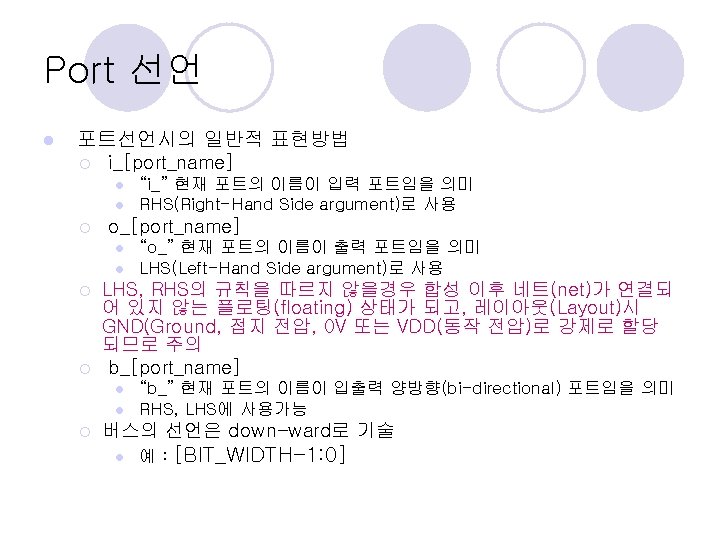

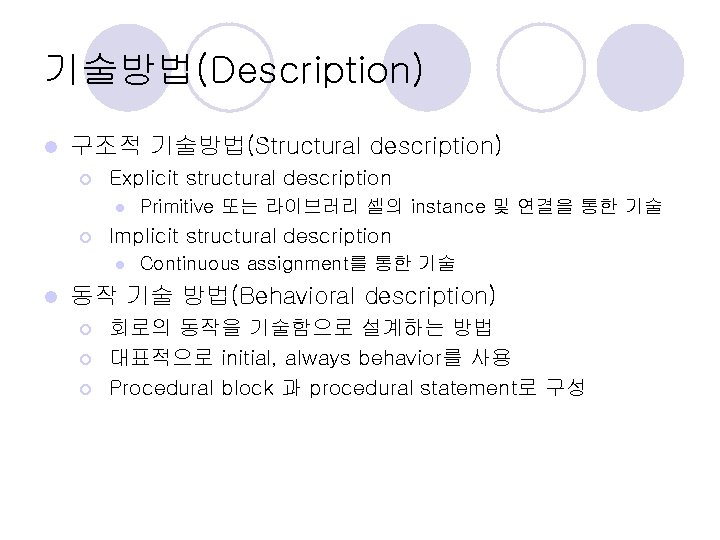

기술방법(Description) l 구조적 기술방법(Structural description) ¡ Explicit structural description l ¡ Implicit structural description l l Primitive 또는 라이브러리 셀의 instance 및 연결을 통한 기술 Continuous assignment를 통한 기술 동작 기술 방법(Behavioral description) ¡ ¡ ¡ 회로의 동작을 기술함으로 설계하는 방법 대표적으로 initial, always behavior를 사용 Procedural block 과 procedural statement로 구성

![기술방법 l Explicit description module 8 bitorgatey a b input 7 0a b output 기술방법 l Explicit description module 8 bit_or_gate(y, a, b); input [7: 0]a, b; output](https://slidetodoc.com/presentation_image/33b99efcaa95fe278fd1c159be98acc6/image-21.jpg)

기술방법 l Explicit description module 8 bit_or_gate(y, a, b); input [7: 0]a, b; output y; or G 1(y, a, b); endmodule or 8 bit(y, a, b); endmodule Primitive를 이용한 기술 l Implicit description module 8 bit_or_gate(y, a, b); input [7: 0]a, b; output y; assign y = a | b; endmodule 라이브러리를 이용한 기술

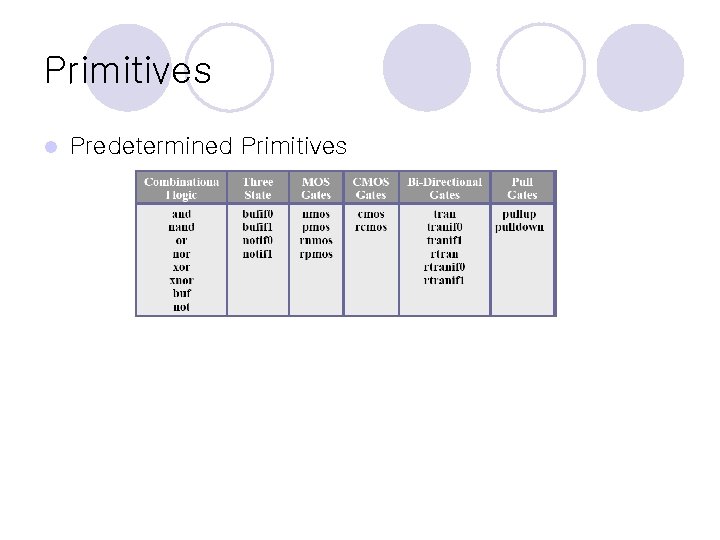

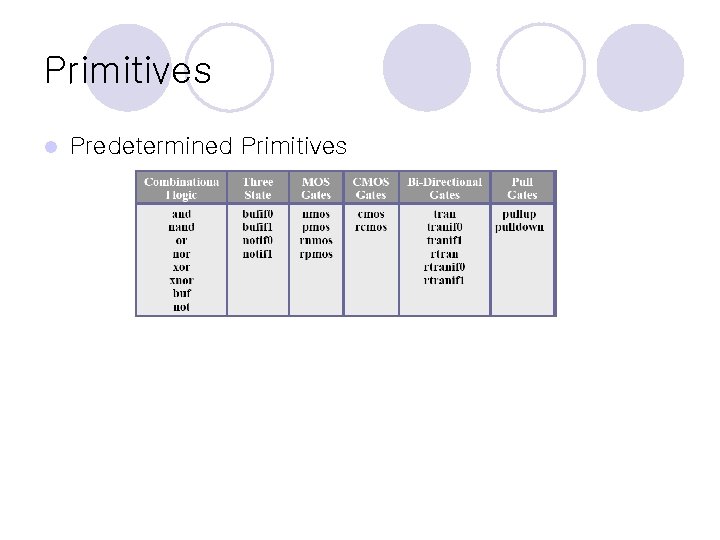

Primitives l Predetermined Primitives

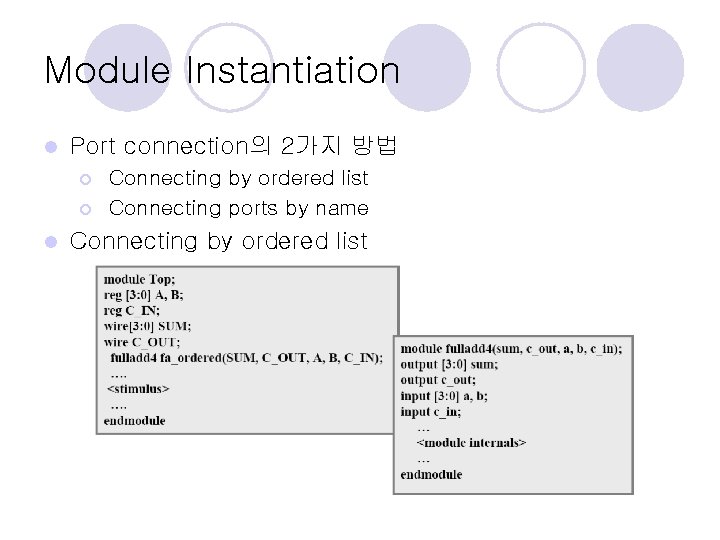

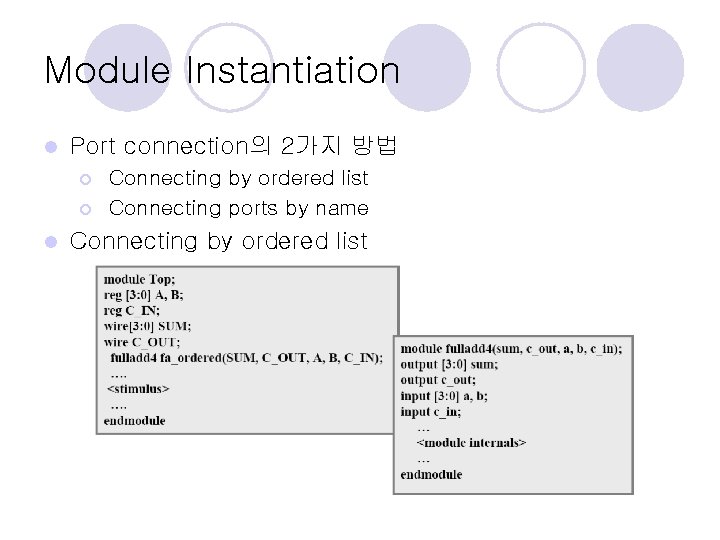

Module Instantiation l Port connection의 2가지 방법 ¡ ¡ l Connecting by ordered list Connecting ports by name Connecting by ordered list

Module Instantiation l Connecting ports by name

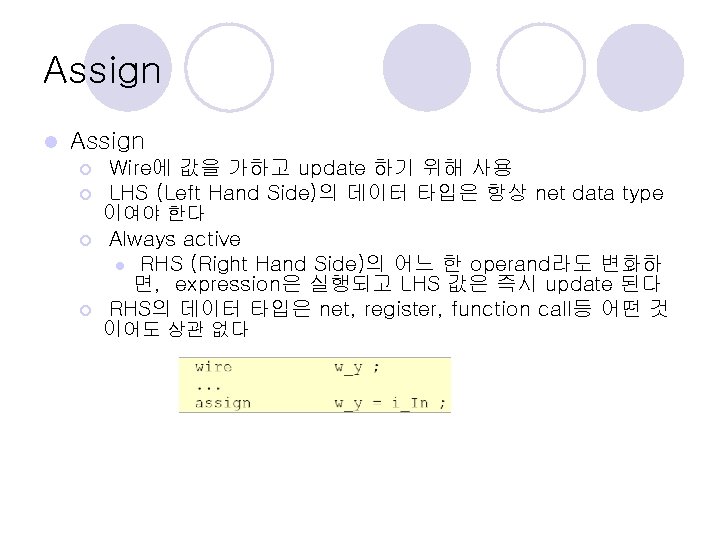

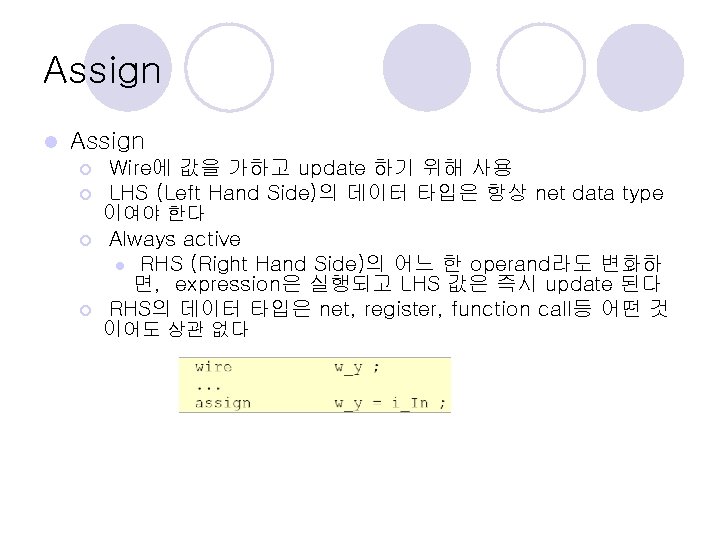

Assign l Assign ¡ ¡ Wire에 값을 가하고 update 하기 위해 사용 LHS (Left Hand Side)의 데이터 타입은 항상 net data type 이여야 한다 Always active l RHS (Right Hand Side)의 어느 한 operand라도 변화하 면, expression은 실행되고 LHS 값은 즉시 update 된다 RHS의 데이터 타입은 net, register, function call등 어떤 것 이어도 상관 없다

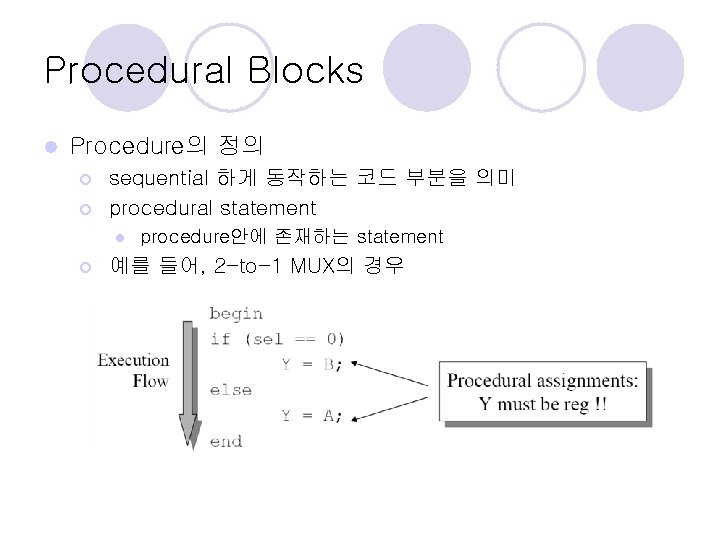

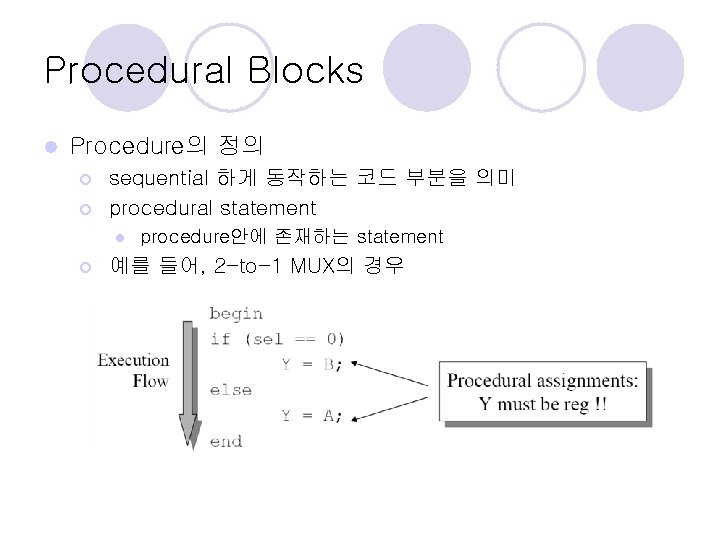

Procedural Blocks l Procedure의 정의 ¡ ¡ sequential 하게 동작하는 코드 부분을 의미 procedural statement l ¡ procedure안에 존재하는 statement 예를 들어, 2 -to-1 MUX의 경우

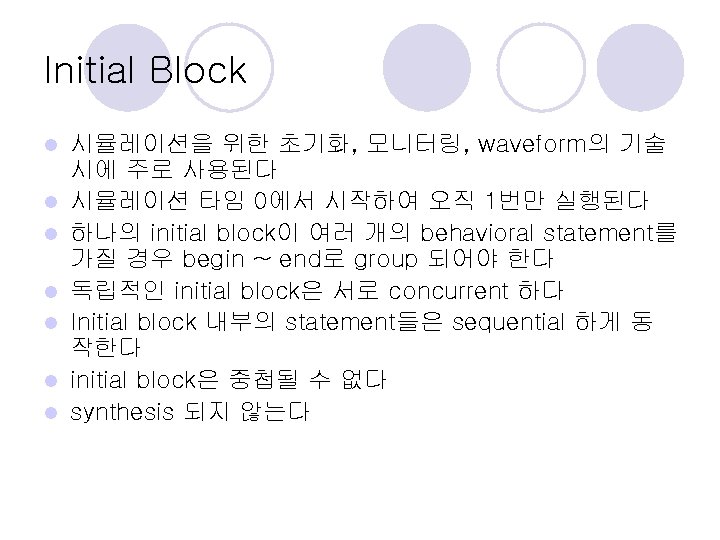

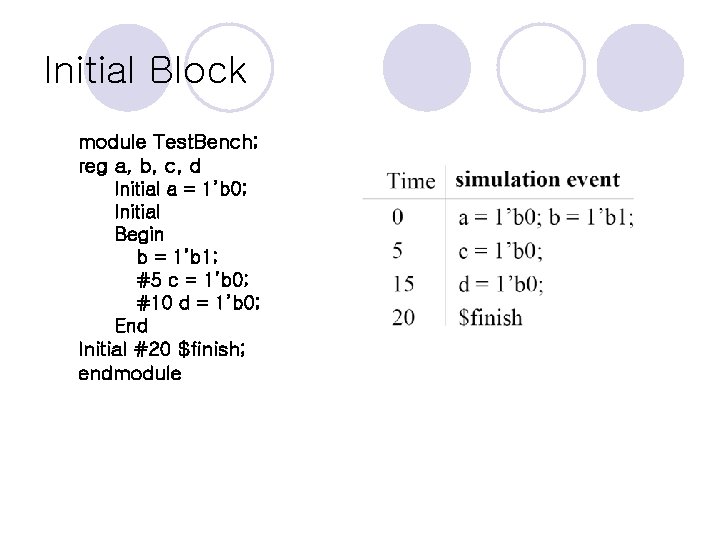

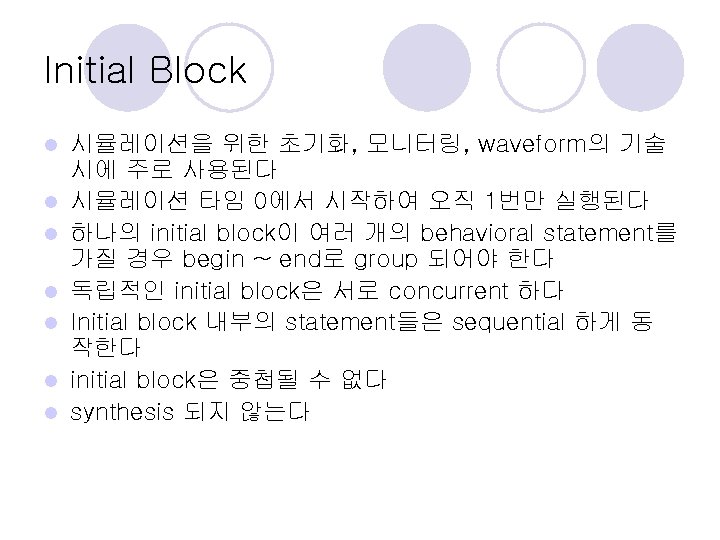

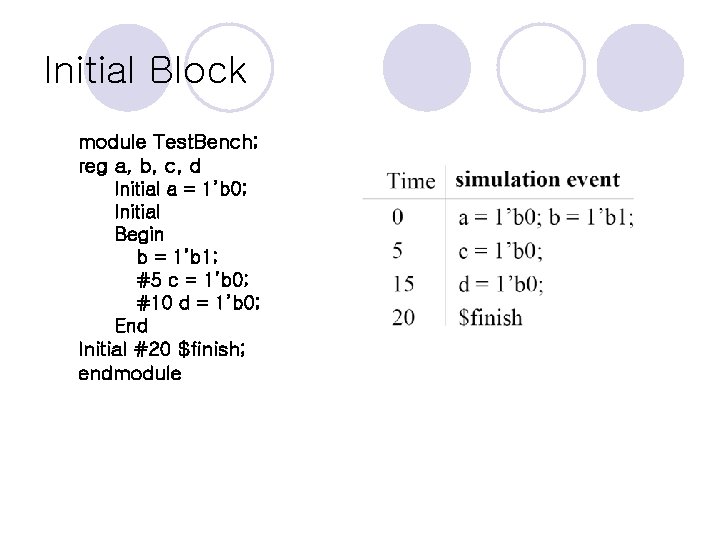

Initial Block module Test. Bench; reg a, b, c, d Initial a = 1’b 0; Initial Begin b = 1’b 1; #5 c = 1’b 0; #10 d = 1’b 0; End Initial #20 $finish; endmodule

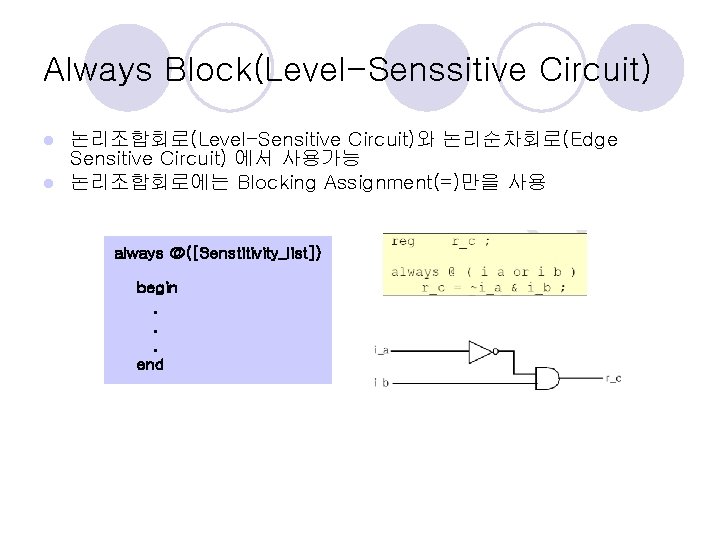

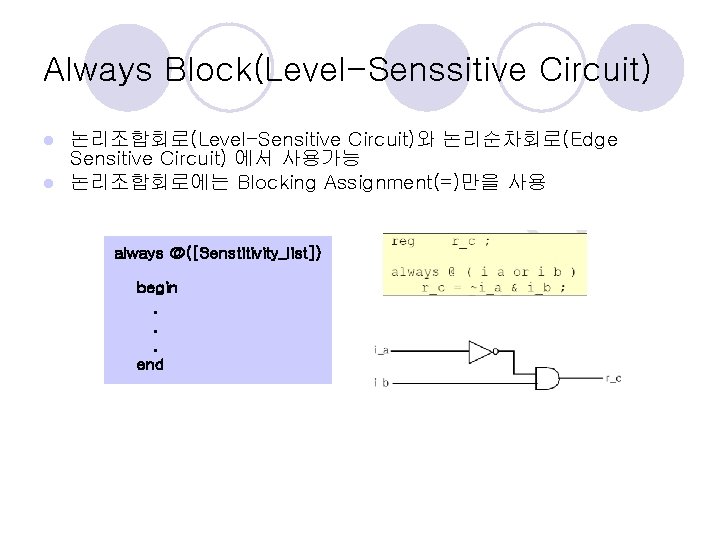

Always Block(Level-Senssitive Circuit) 논리조합회로(Level-Sensitive Circuit)와 논리순차회로(Edge Sensitive Circuit) 에서 사용가능 l 논리조합회로에는 Blocking Assignment(=)만을 사용 l always @([Senstitivity_list]) begin. . . end

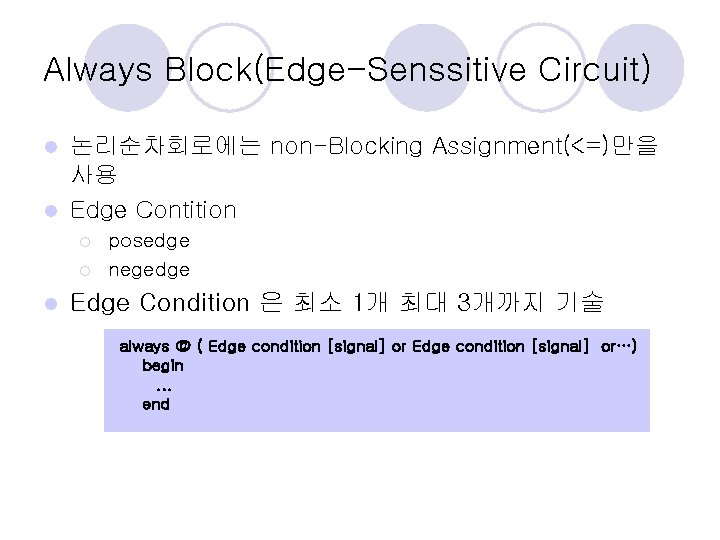

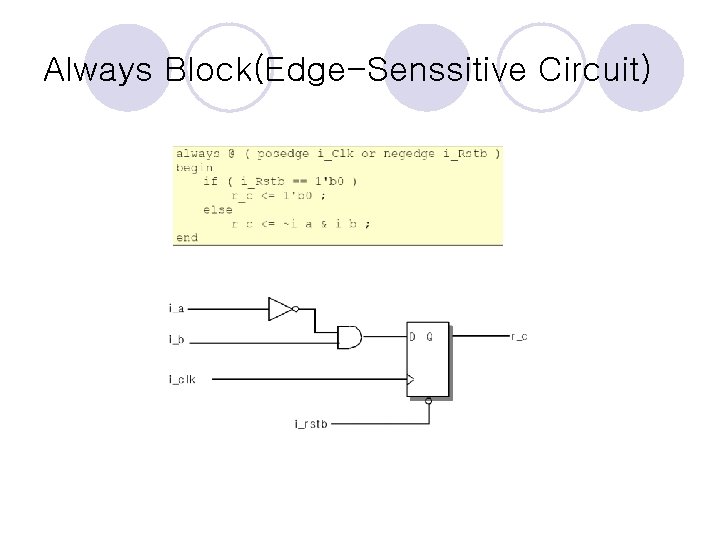

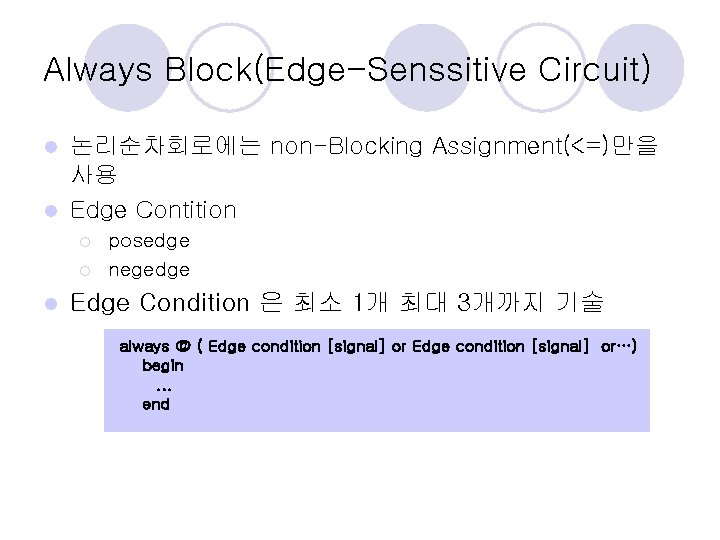

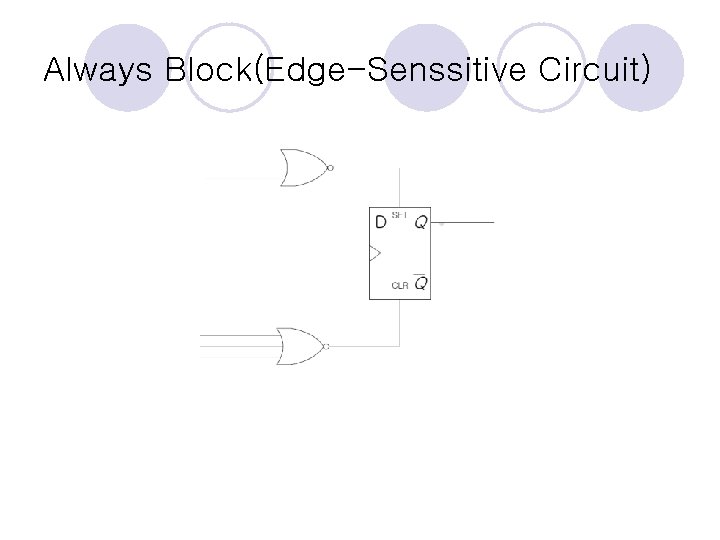

Always Block(Edge-Senssitive Circuit) 논리순차회로에는 non-Blocking Assignment(<=)만을 사용 l Edge Contition l ¡ ¡ l posedge negedge Edge Condition 은 최소 1개 최대 3개까지 기술 always @ ( Edge condition [signal] or…) begin. . . end

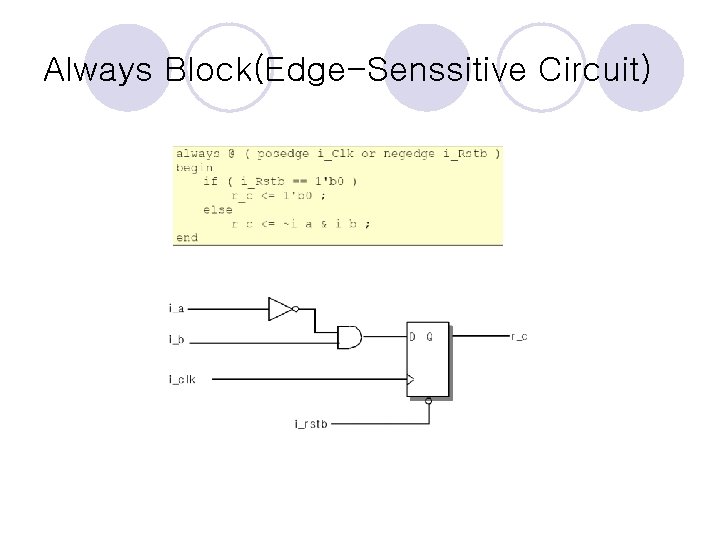

Always Block(Edge-Senssitive Circuit)

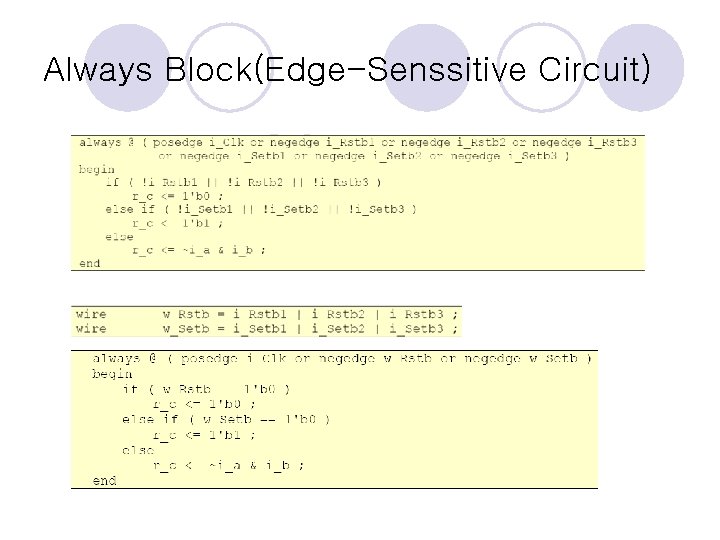

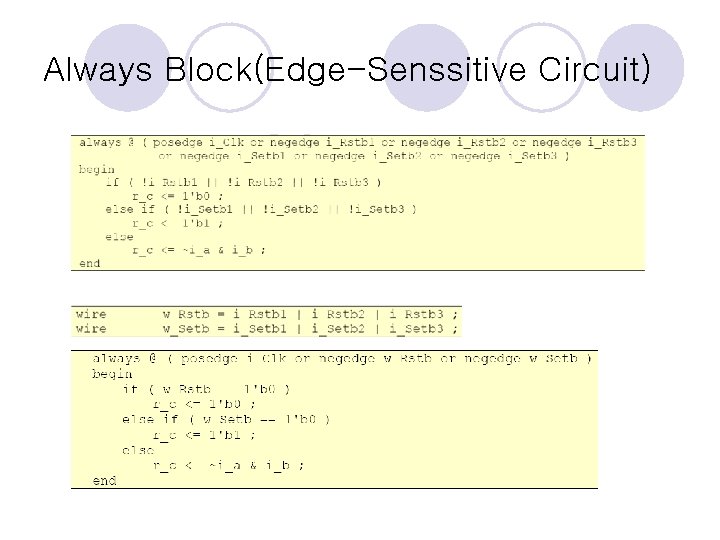

Always Block(Edge-Senssitive Circuit)

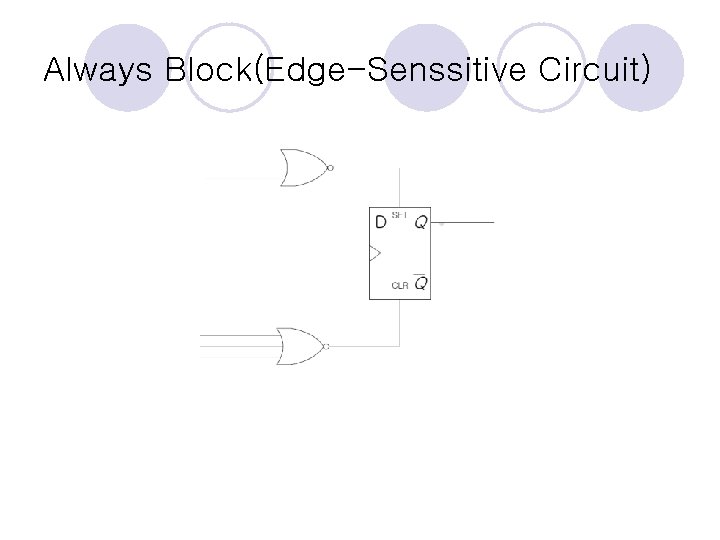

Always Block(Edge-Senssitive Circuit)

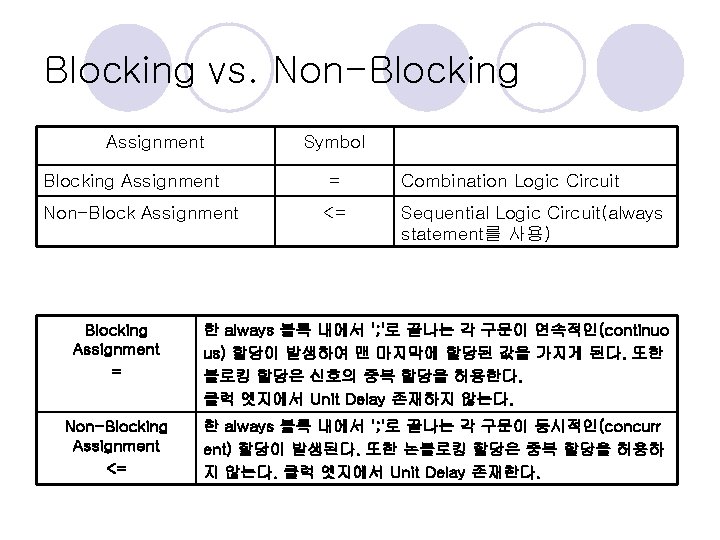

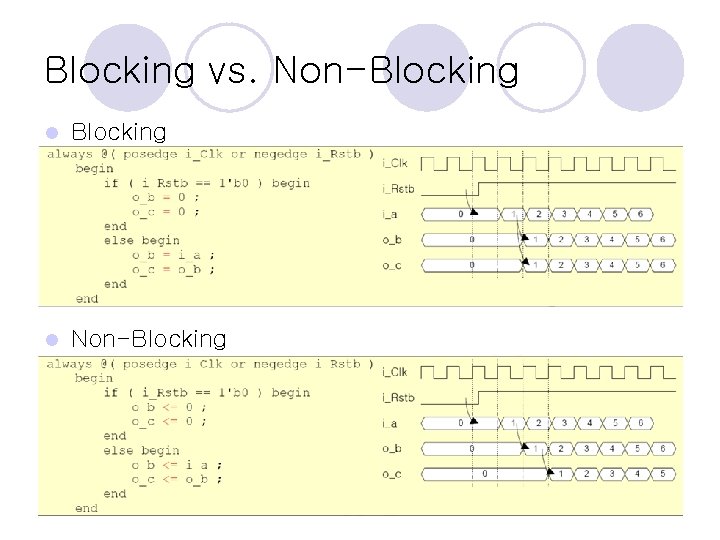

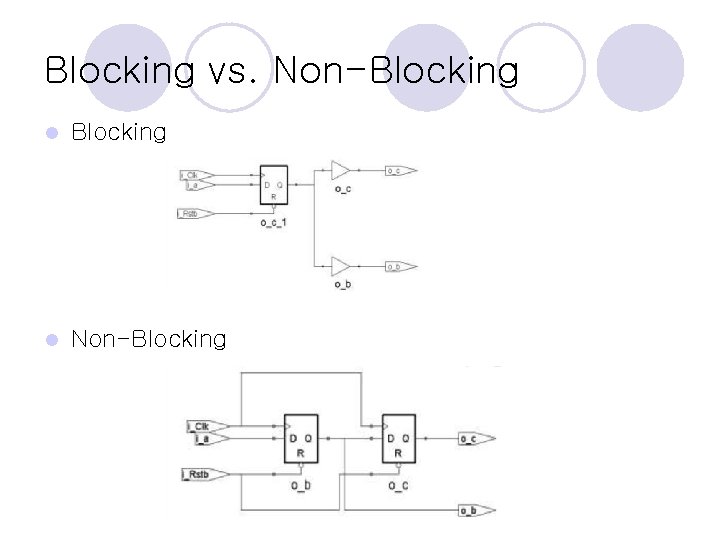

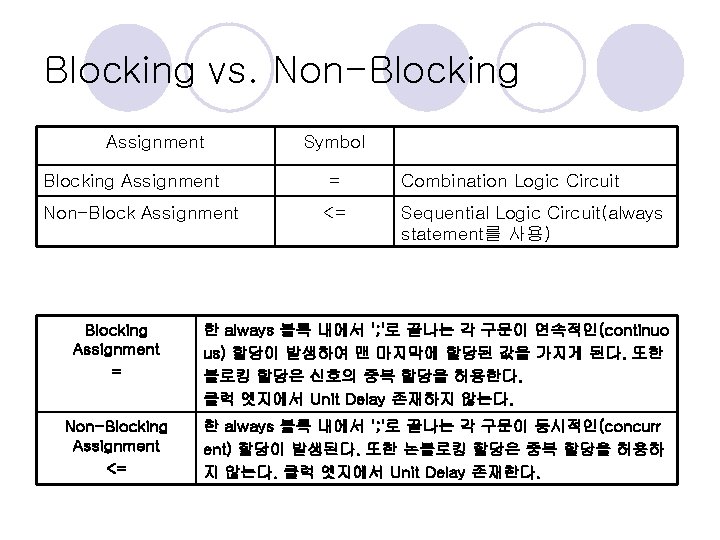

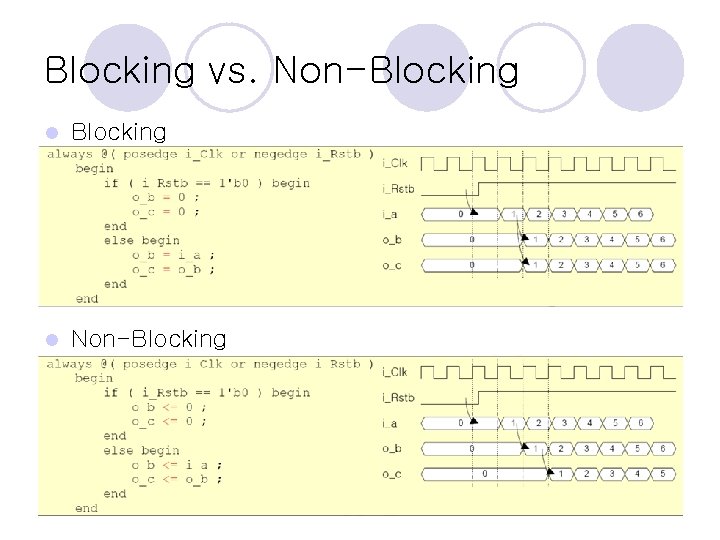

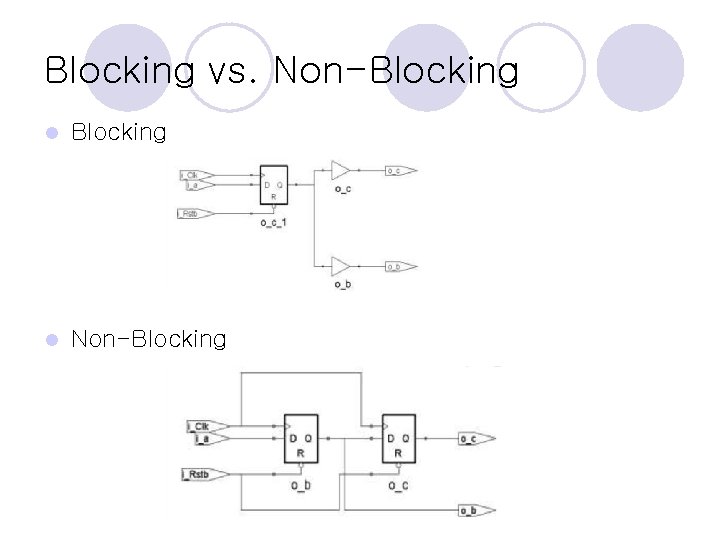

Blocking vs. Non-Blocking l Non-Blocking

Blocking vs. Non-Blocking l Non-Blocking

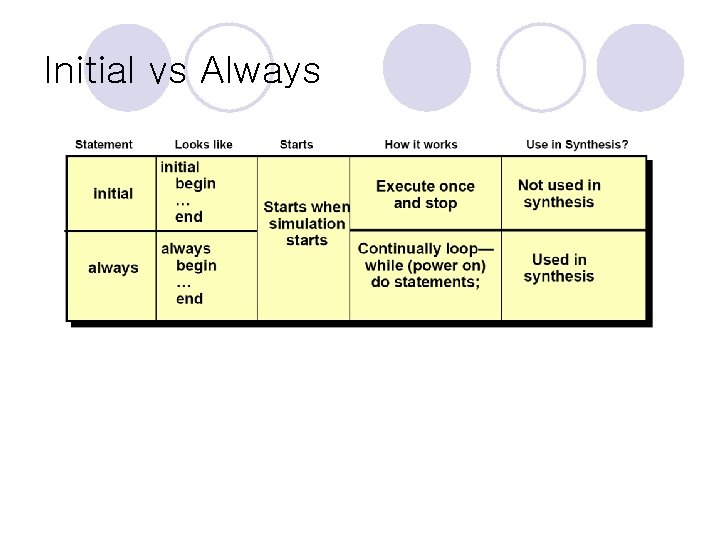

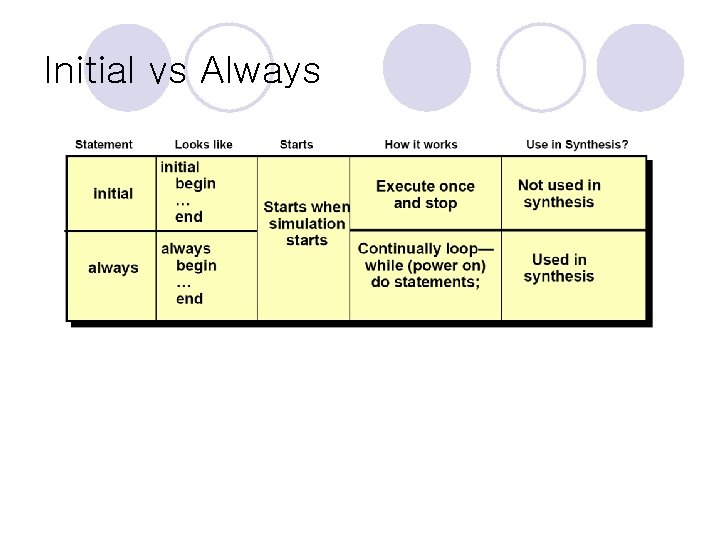

Initial vs Always

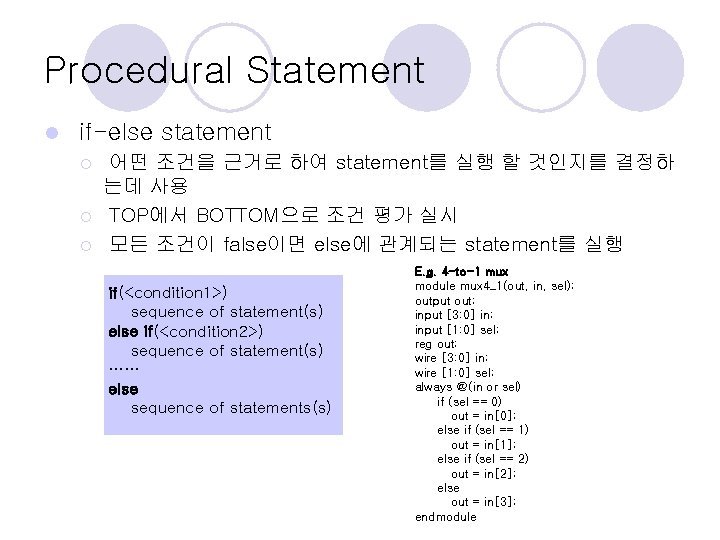

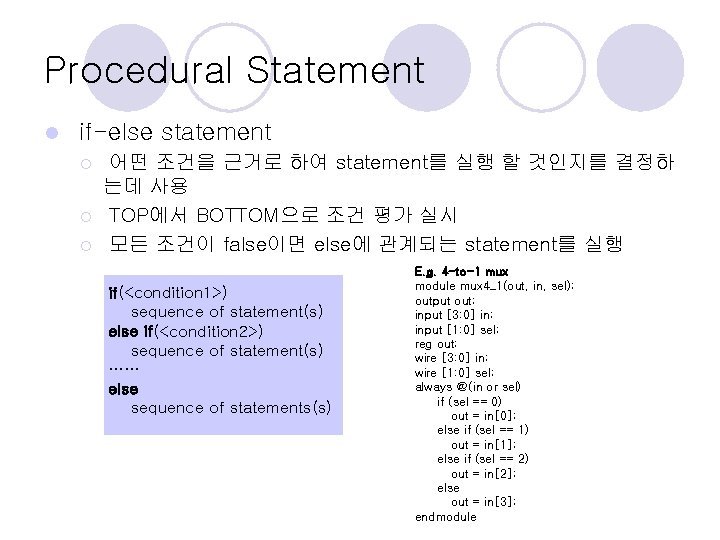

Procedural Statement l if-else statement ¡ ¡ ¡ 어떤 조건을 근거로 하여 statement를 실행 할 것인지를 결정하 는데 사용 TOP에서 BOTTOM으로 조건 평가 실시 모든 조건이 false이면 else에 관계되는 statement를 실행 if(<condition 1>) sequence of statement(s) else if(<condition 2>) sequence of statement(s) …… else sequence of statements(s) E. g. 4 -to-1 mux module mux 4_1(out, in, sel); output out; input [3: 0] in; input [1: 0] sel; reg out; wire [3: 0] in; wire [1: 0] sel; always @(in or sel) if (sel == 0) out = in[0]; else if (sel == 1) out = in[1]; else if (sel == 2) out = in[2]; else out = in[3]; endmodule

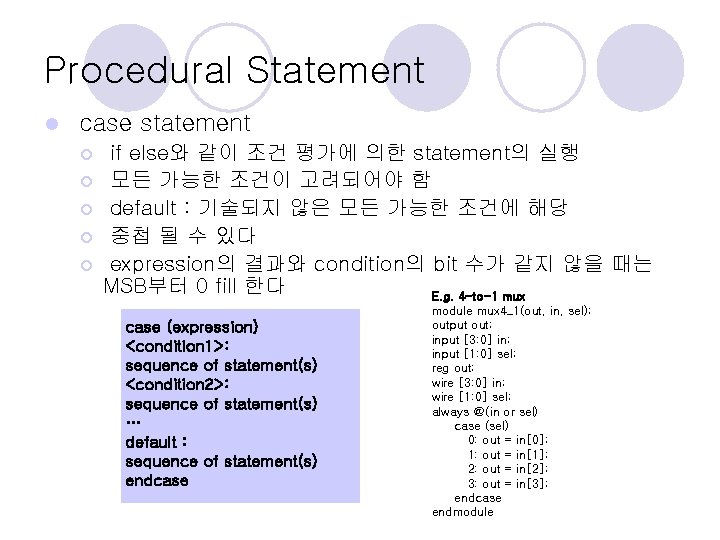

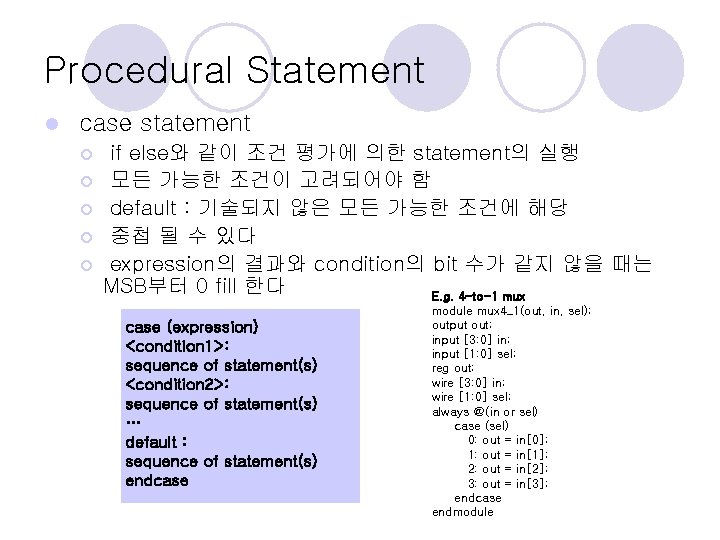

Procedural Statement l case statement ¡ ¡ ¡ if else와 같이 조건 평가에 의한 statement의 실행 모든 가능한 조건이 고려되어야 함 default : 기술되지 않은 모든 가능한 조건에 해당 중첩 될 수 있다 expression의 결과와 condition의 bit 수가 같지 않을 때는 MSB부터 0 fill 한다 E. g. 4 -to-1 mux case (expression) <condition 1>: sequence of statement(s) <condition 2>: sequence of statement(s) … default : sequence of statement(s) endcase module mux 4_1(out, in, sel); output out; input [3: 0] in; input [1: 0] sel; reg out; wire [3: 0] in; wire [1: 0] sel; always @(in or sel) case (sel) 0: out = in[0]; 1: out = in[1]; 2: out = in[2]; 3: out = in[3]; endcase endmodule

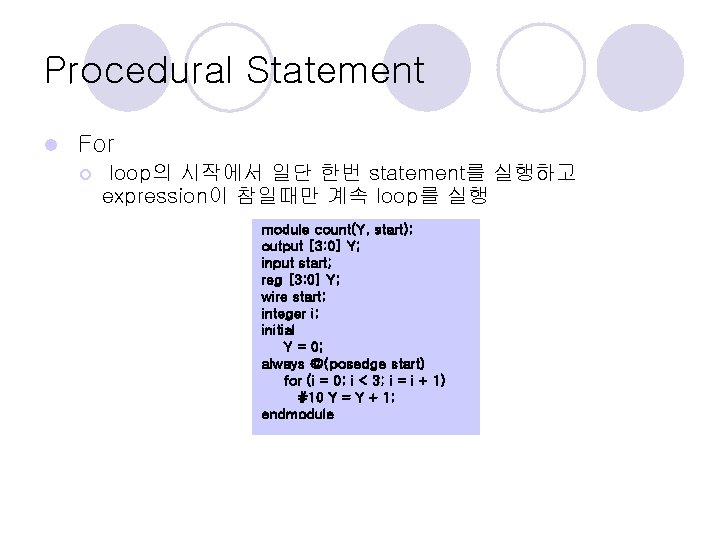

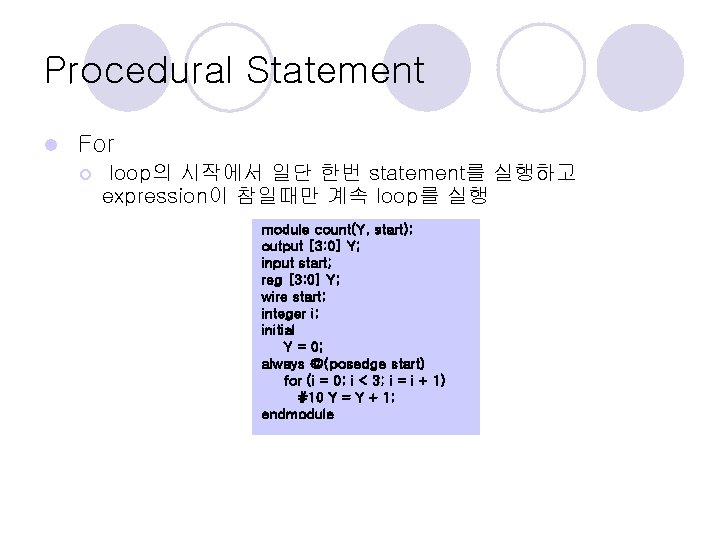

Procedural Statement l For ¡ loop의 시작에서 일단 한번 statement를 실행하고 expression이 참일때만 계속 loop를 실행 module count(Y, start); output [3: 0] Y; input start; reg [3: 0] Y; wire start; integer i; initial Y = 0; always @(posedge start) for (i = 0; i < 3; i = i + 1) #10 Y = Y + 1; endmodule

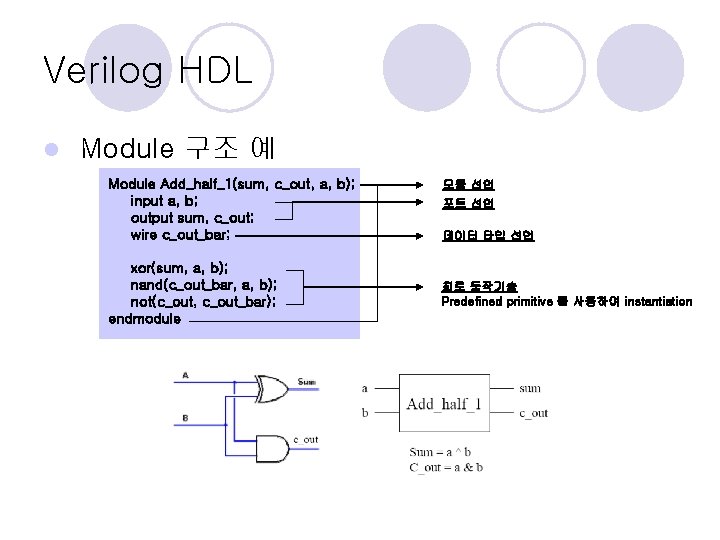

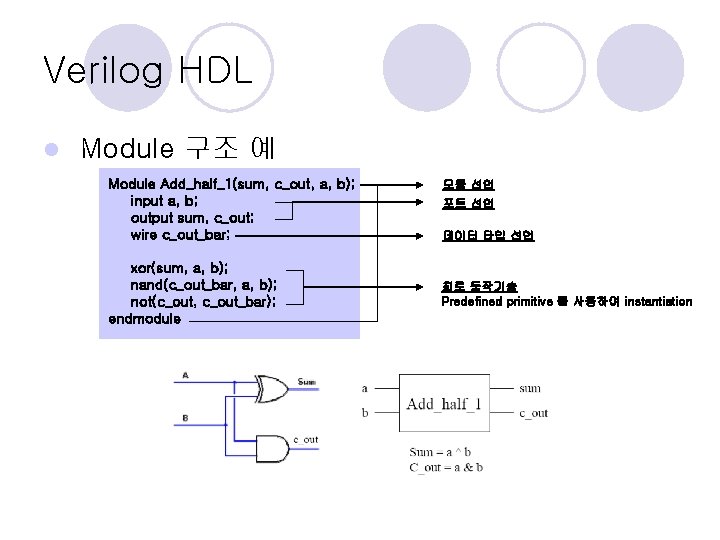

Verilog HDL l Module 구조 예 Module Add_half_1(sum, c_out, a, b); input a, b; output sum, c_out; wire c_out_bar; xor(sum, a, b); nand(c_out_bar, a, b); not(c_out, c_out_bar); endmodule 모듈 선언 포트 선언 데이터 타입 선언 회로 동작기술 Predefined primitive 를 사용하여 instantiation

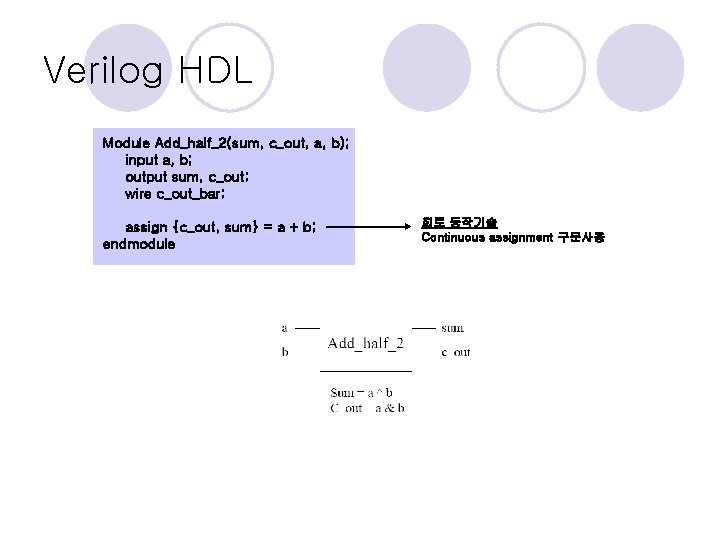

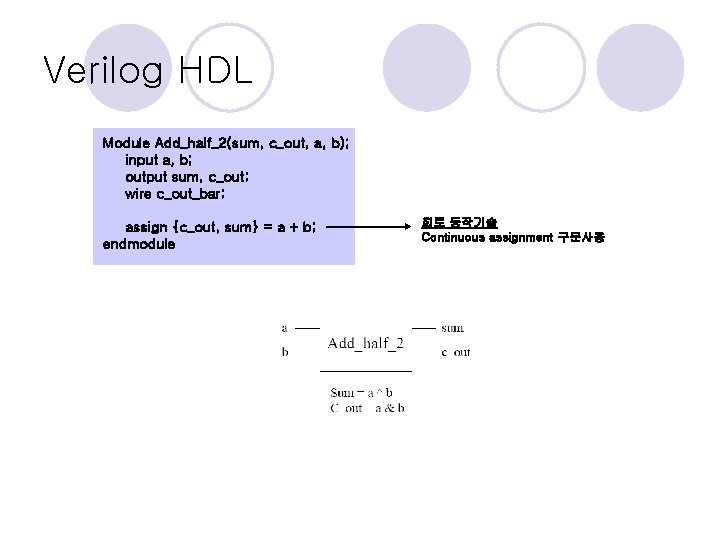

Verilog HDL Module Add_half_2(sum, c_out, a, b); input a, b; output sum, c_out; wire c_out_bar; assign {c_out, sum} = a + b; endmodule 회로 동작기술 Continuous assignment 구문사용

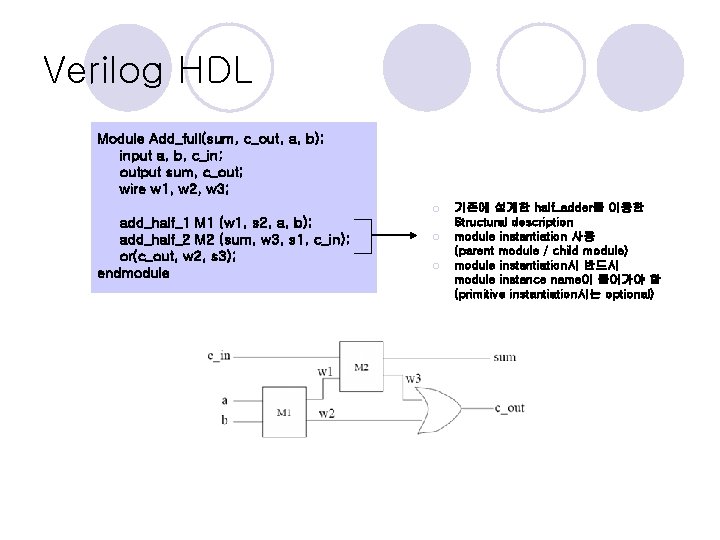

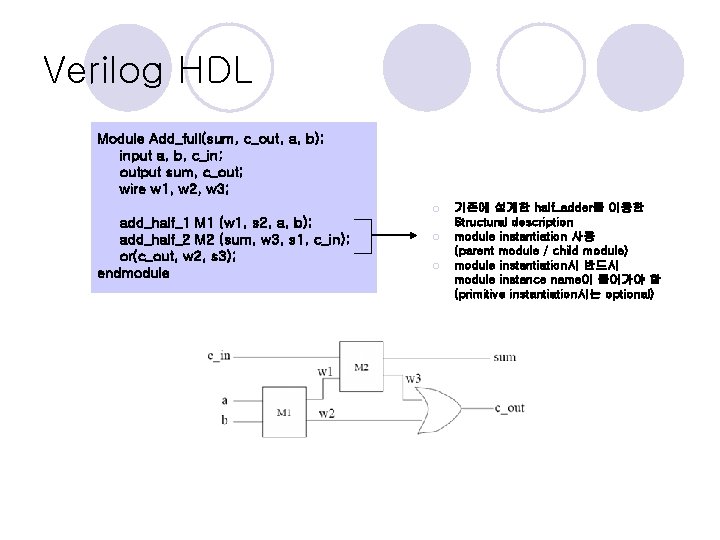

Verilog HDL Module Add_full(sum, c_out, a, b); input a, b, c_in; output sum, c_out; wire w 1, w 2, w 3; ¡ add_half_1 M 1 (w 1, s 2, a, b); add_half_2 M 2 (sum, w 3, s 1, c_in); or(c_out, w 2, s 3); endmodule ¡ ¡ 기존에 설계한 half_adder를 이용한 Structural description module instantiation 사용 (parent module / child module) module instantiation시 반드시 module instance name이 들어가야 함 (primitive instantiation시는 optional)

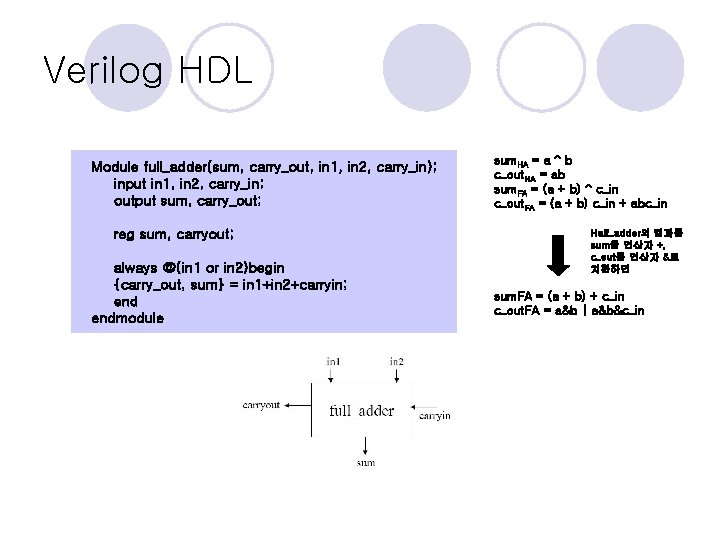

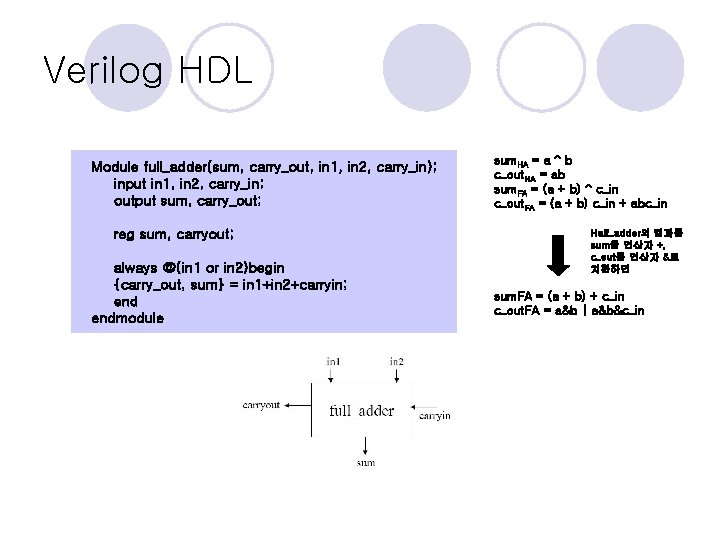

Verilog HDL Module full_adder(sum, carry_out, in 1, in 2, carry_in); input in 1, in 2, carry_in; output sum, carry_out; reg sum, carryout; always @(in 1 or in 2)begin {carry_out, sum} = in 1+in 2+carryin; endmodule sum. HA = a ^ b c_out. HA = ab sum. FA = (a + b) ^ c_in c_out. FA = (a + b) c_in + abc_in Half_adder의 결과를 sum을 연산자 +, c_out를 연산자 &로 치환하면 sum. FA = (a + b) + c_in c_out. FA = a&b | a&b&c_in